Silicon Laboratories Si2400-BS, Si2400-KS Datasheet

Si2400

V.22

BIS

ISO

MODEM

™

WITH INTEGRATED

Features

!

Data Modem Formats

"

2400 bps: V.22bis

"

1200 bps: V.22, V.23, Bell 212A

"

300 bps: V.21, Bell 103

"

V.25 Fast Connect and V.23 Reversing

"

SIA and other security protocols

!

Caller ID Detection and Decode

!

DTMF Tone Gen./Detection

!

3.3 V or 5.0 V Power

!

UART with Flow Control

!

Integrated DAA

"

Capacitive Isolation

"

Parallel Phone Detect

"

Globally Compliant Line Interface

"

Overcurrent Protection

!

AT Command Set Support

!

Integrated Voice Codec

!

PCM Data Pass-Through Mode

!

HDLC Framing in Hardware

!

Call Progress Support

Applications

!

Set Top Boxes

!

Power Meters

!

Security Systems

!

ATM Terminals

!

Medical Monitoring

!

Point-of-Sale

Description

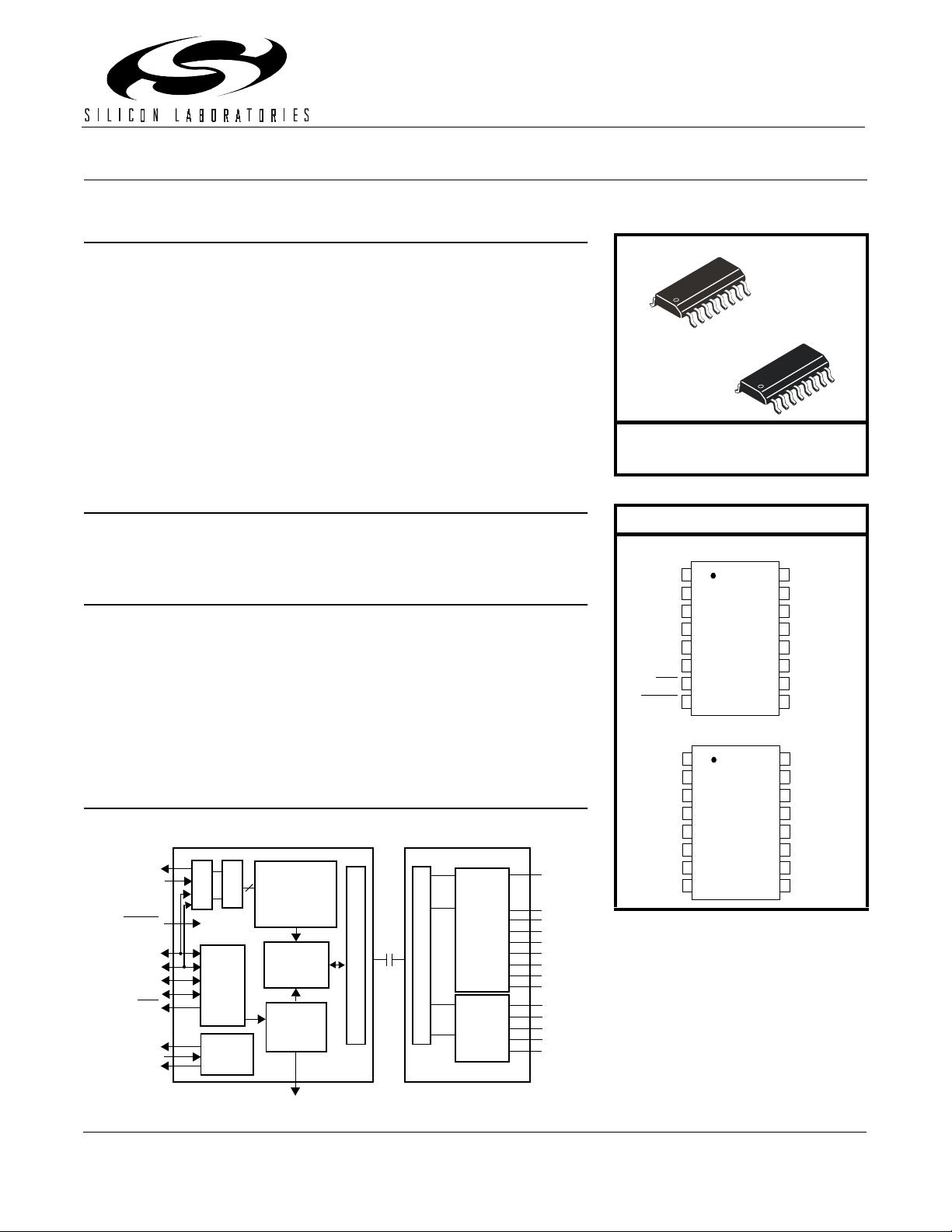

The Si2400 ISOmodem™ i s a complete modem chipset with integr ated

direct access arrangement (DAA) that provides a programmable line

interface to meet global te lephon e line r equir emen ts. Available in two 16pin small outline (SOIC) packag es, it eliminates the need for a se parate

DSP data pump, modem controller, analog front end (AFE), isolation

transformer, relays, opto-isolators, 2- to 4-wire hybrid, and voice codec.

The Si2400 is ideal for embedd ed modem applications due to its small

board space, low power consumption, and global compliance.

Functional Block Diagram

Si2400 Si3015

TXD

RXD

RESET

EOFR/GPIO1

AIN/GPIO2

ESC/GPIO3

ALERT/GPIO4

CTS

CLKOUT

XTALI

XTALO

MUX

Control

Interface

Clock

Interface

UART

µ

Controller

(AT Decode r

Call Progress)

DSP

(Data Pump)

Audio

Codec

Hybrid

and

DC

T ermination

Isolation Interface

Isolation Interface

Ring Detect

Off-Hook

RX

FILT

FILT2

REF

DCT

VREG2

REXT

REXT2

RNG1

RNG2

QB

QE

QE2

G

LOBAL

Si2400

Ordering Information

See page 71.

Pin Assignments

Si2400

XTALI

XTALO

CLKOUT

RESET

RNG1

RNG2

Patents pending

V

TXD

RXD

CTS

QE2

DCT

IGND

C1B

QB

QE

1

2

3

4

D

5

6

7

8

Si3015

1

2

3

4

5

6

7

8

DAA

Si3015

EOFR/GPIO1

16

AIN/GPIO2

15

ESC/GPIO3

14

ISOB

13

GND

12

C1A

11

ALERT/GPIO4

10

AOUT

9

FILT2

16

FILT

15

RX

14

REXT

13

REXT2

12

REF

11

VREG2

10

VREG

9

AOUT

Rev. 0.95 4/00 Copyright © 2000 by Silicon Laboratories Si2400-DS095

Si2400

2 Rev. 0.95

Si2400

T

ABLE OF

C

ONTENTS

Section Page

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

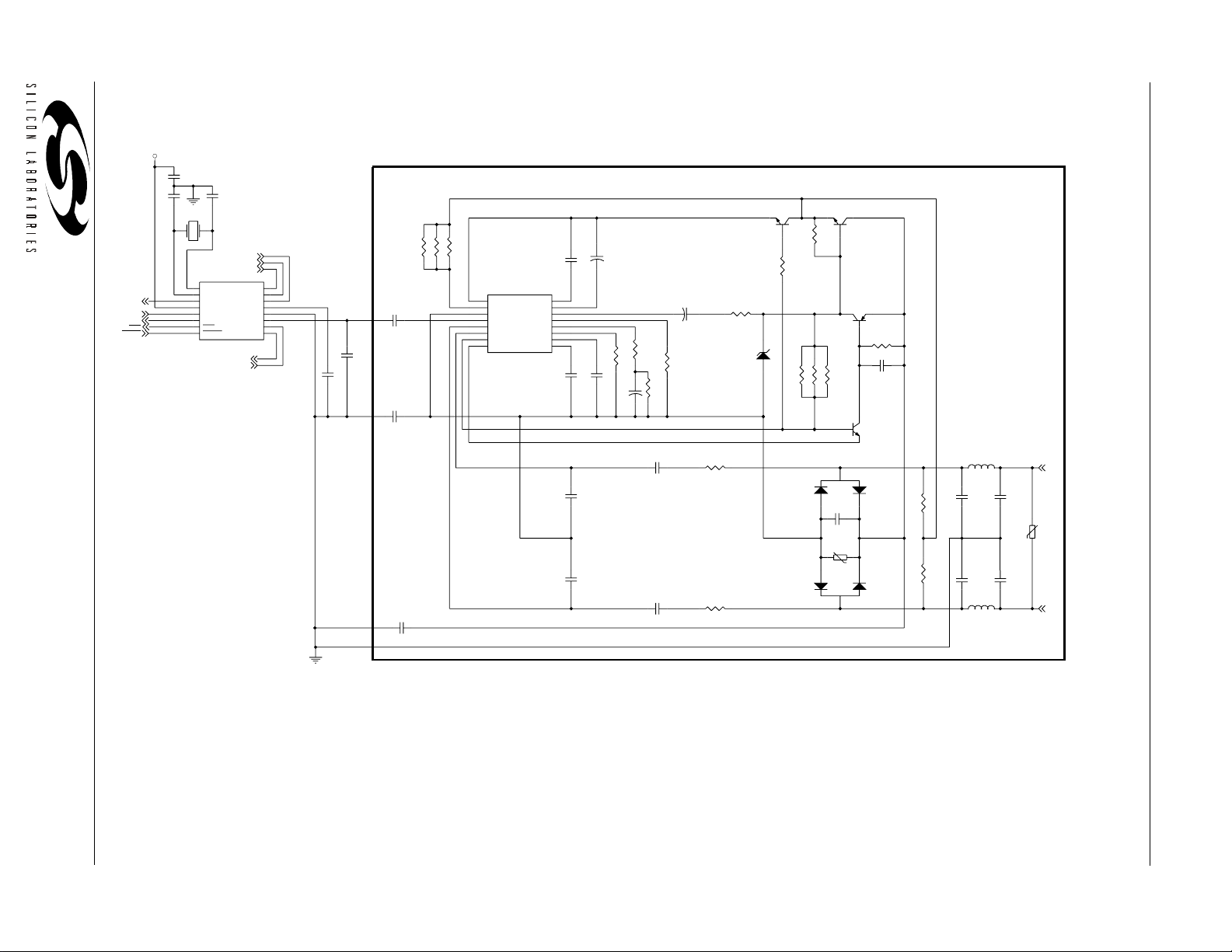

Typical Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Typical Application Circuit Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Bill of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Analog Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Digital Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Configurations and Data Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Low Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Global DAA Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Parallel Phone Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Carrier Detect/Loss . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Overcurrent Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Caller ID Decoding Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Tone Generation and Tone Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

PCM Data Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Analog Codec . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

V.23 Operation/V.23 Reversing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

V.42 HDLC Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Fast Connect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Clock Generation Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

AT Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Command Line Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

< CR > End Of Line Character . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

AT Command Set Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Extended AT Commands for the Alarm Industry . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Modem Result Codes and Call Progress . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Low Level DSP Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

S Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Appendix A—DAA Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Appendix B—Typical Modem Applications Examples . . . . . . . . . . . . . . . . . . . . . . . . . 67

Appendix C—UL1950 3rd Edition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Rev. 0.95 3

Si2400

Electrical Specifications

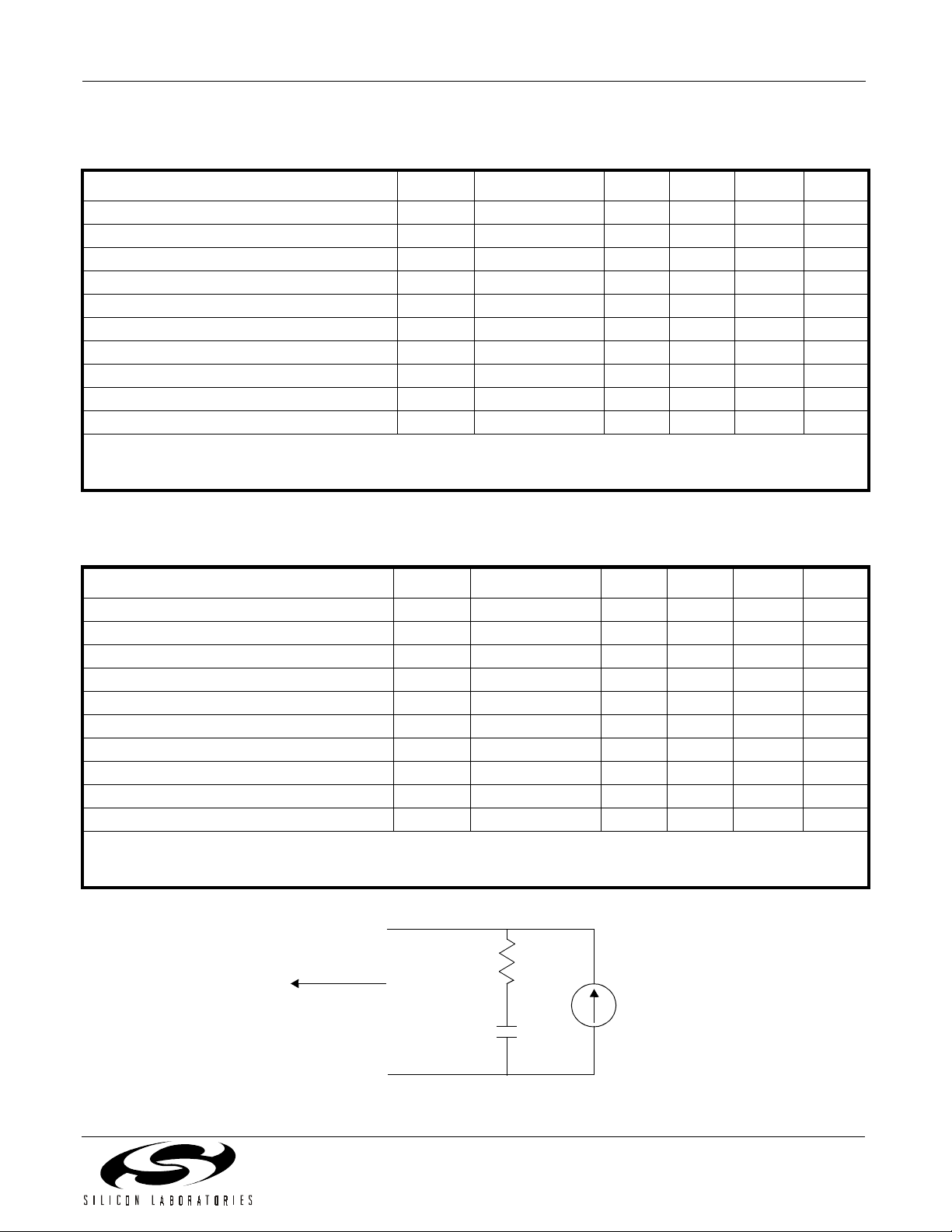

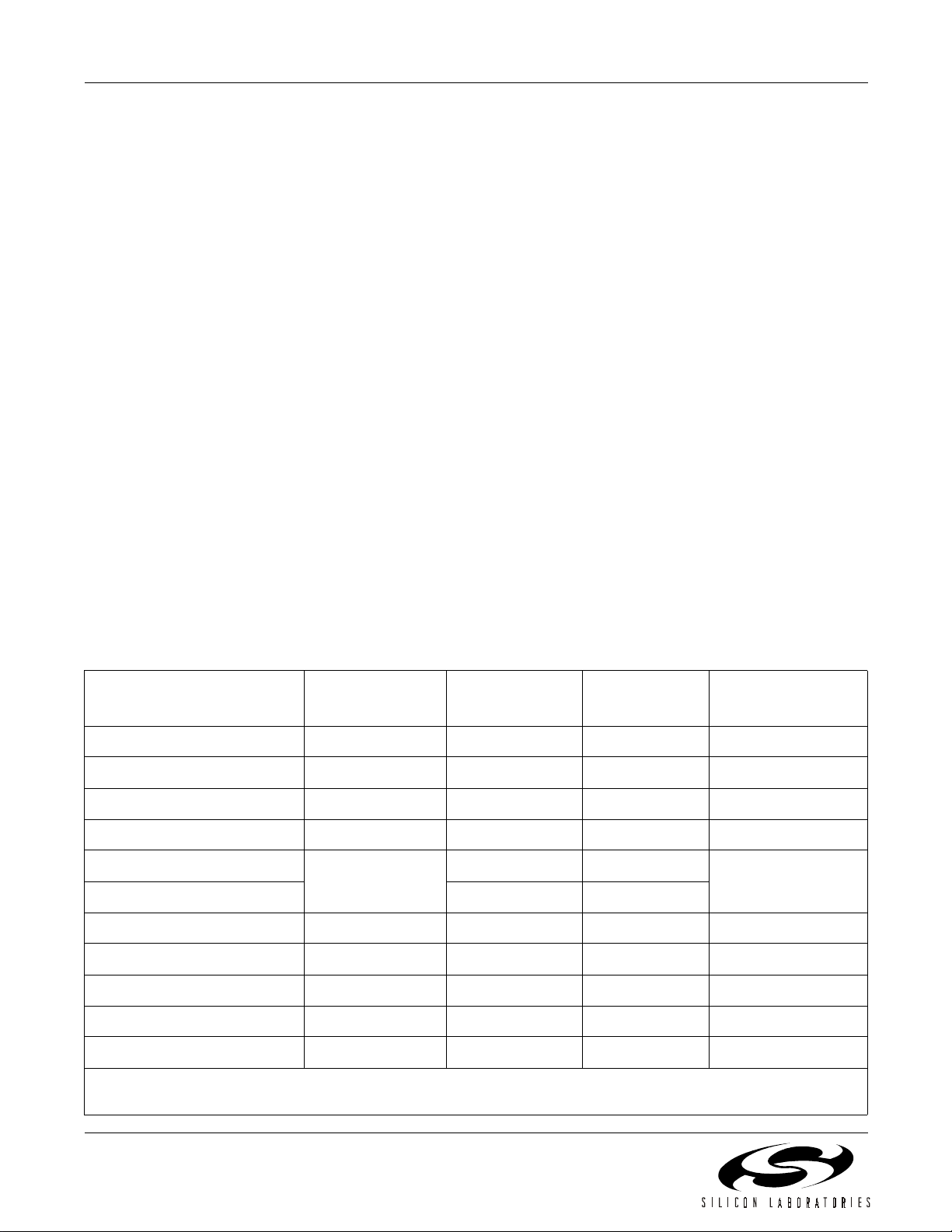

Table 1. Recommended Operating Conditions

Parameter

1

Ambient Temperature T

Ambient Temperature T

Si2400 Supply Voltage, Digital

Notes:

1. The Si2400 specifications are guaranteed when the typical application circuit (including component tolerance) and any

Si2400 and any Si3015 are used. See Figure3 on page 9 for typical application circuit.

2. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

3. The digital supply, V

from 3.3 V. The 3.3V operation applies to both the serial port and the digital signals CTS

.

RESET

3

, can operate from eit her 3.3 V or 5.0 V. The Si 2400 inte rface suppo rts 3.3V logic when operating

D

Symbol Test Condition

A

A

V

D

K-Grade 0 25 70 °C

B-Grade –40 25 85 °C

Min

2

Typ

Max

2

3.0 3.3/5.0 5.25 V

, CLKOUT, GPIO1–4, and

Unit

Table 2. DAA Loop Characteristics

(VD = 3.0 to 3.6 V or 4.75 to 5.25 V, TA = 0 to 70°C

for K-Grade, TA = –40

to 85°C for B-Grade)

Parameter Symbol Test Condition Min Typ Max Unit

DC Termination Voltage V

DC Termination Voltage V

DC Termination Voltage V

DC Termination Voltage V

DC Termination Voltage V

DC Termination Voltage V

DC Termination Voltage V

DC Termination Voltage V

On Hook Leakage Current I

Operating Loop Current I

Operating Loop Current I

TR

TR

TR

TR

TR

TR

TR

TR

LK

LP

LP

DC Ring Current — — 20 µA

Ring Detect Voltage V

Ring Detect Voltage V

Ring Frequency F

RD

RD

R

Ringer Equivalence Number* REN — — 0.2

*Note:C15, R14, Z2, and Z3 not installed.

IL = 20 mA, ACT = 1

——7.5V

DCT = 11 (CTR21)

IL = 42 mA, ACT = 1

— — 14.5 V

DCT = 11 (CTR21)

IL = 50 mA, ACT = 1

——40 V

DCT = 11 (CTR21)

IL = 60 mA, ACT = 1

40 — — V

DCT = 11 (CTR21)

IL = 20 mA, ACT = 0

——6.0V

DCT = 01 (Japan)

IL = 100 mA, ACT = 0

11 — — V

DCT = 01 (Japan)

IL = 20 mA, ACT = 0

——7.5V

DCT = 10 (FCC)

IL = 100 mA, ACT = 0

12 — — V

DCT = 10 (FCC)

V

= –48 V — — 1 µA

BAT

FCC/Japan Modes 13 — 120 mA

CTR21 13 — 60 mA

RT = 0 11 — 22 V

RT = 1 17 — 33 V

15 — 68 Hz

RMS

RMS

4 Rev. 0.95

Si2400

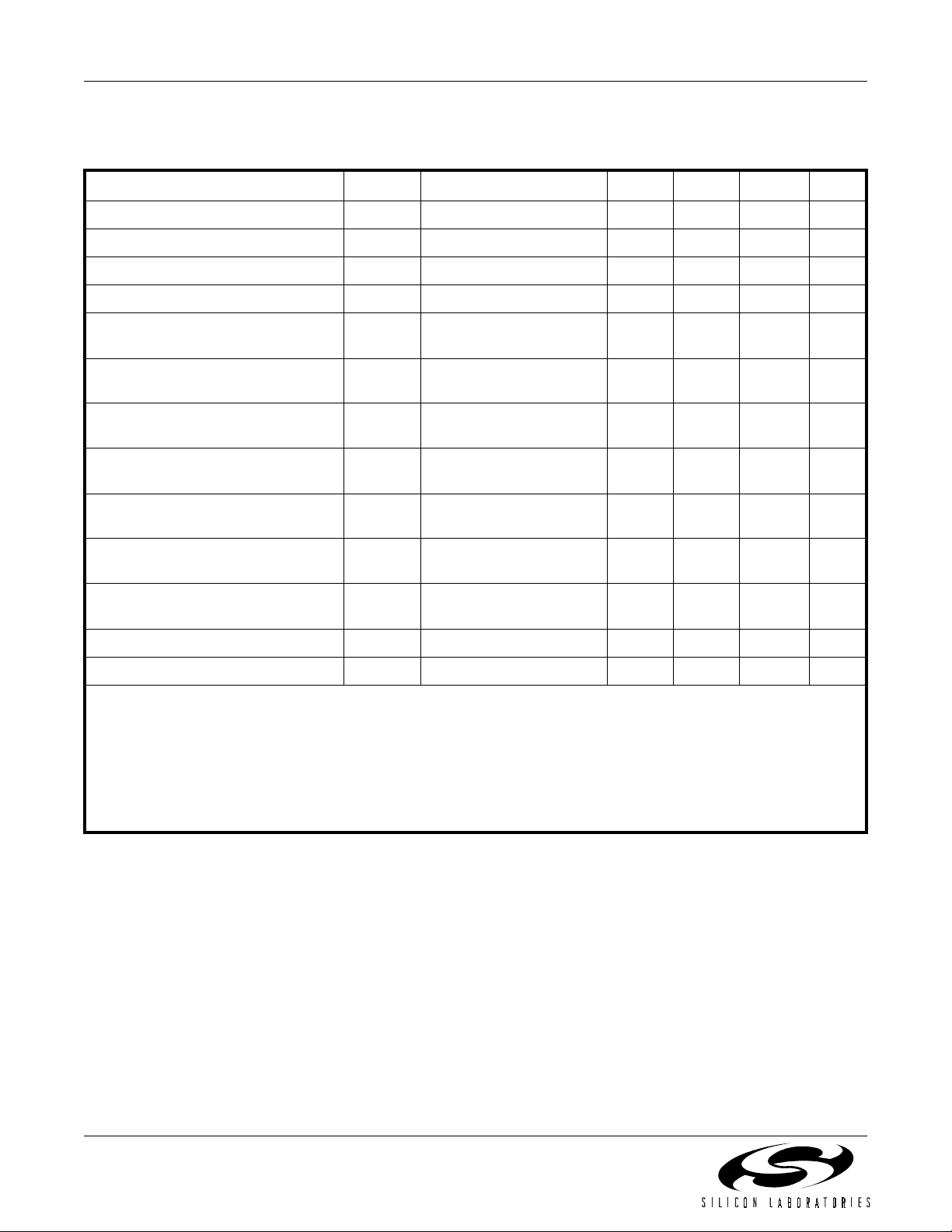

Table 3. DC Characteristics

(VD = 4.75 to 5.25 V, TA = 0 to 70°C

Parameter Symbol Test Condition Min Typ Max Unit

for K-Grade, TA = –40

to 85°C for B-Grade)

High Level Input Voltage V

Low Level Input Voltage V

High Level Output Voltage V

Low Level Output Voltage V

Low Level Output Voltage, GPIO1–4 V

Input Leakage Current I

Power Supply Current, Digital* I

Power Supply Current, DSP Power Down* I

Power Supply Current, Wake-On-Ring (ATZ) I

Power Supply Current, Total Power Down I

*Note: Specifications assume MCKR = 0 (default). Typical value is 4 mA lower when MCKR = 1 and 6 mA lower when

MCKR = 2,3.

Measurements are taken with inputs at rails and no loads on outputs.

IH

IL

OH

OL

OL

L

D

D

D

D

IO = –2 mA 2.4 — — V

IO = 2 mA — — 0.4 V

IO = 40 mA — — 0.6 V

VD pin — 28 32 mA

VD pin — 16 19 mA

VD pin — 10 11 mA

VD pin — 60 105 µA

3.5 — — V

——0.8V

–10 — 10 µA

Table 4. DC Characteristics

(VD = 3.0 to 3.6 V, TA = 0 to 70°C

for K-Grade, TA = –40

to 85°C for B-Grade)

Parameter Symbol Test Condition Min Typ Max Unit

High Level Input Voltage V

Low Level Input Voltage V

High Level Output Voltage V

Low Level Output Voltage V

Low Level Output Voltage, GPIO1–4 V

Input Leakage Current I

Power Supply Current, Digital I

Power Supply Current, DSP Power Down I

Power Supply Current, Wake-On-Ring I

Power Supply Current, Total Power Down I

*Note: Specifications assume MCKR = 0 (default). Typical value is 2 mA lower when MCKR = 1 and 3 mA lower when

MCKR = 2,3.

Measurements are taken with inputs at rails and no loads on outputs.

IH

IL

OH

OL

OL

L

D

D

D

D

IO = –2 mA 2.4 — — V

IO = 2 mA — — 0.35 V

IO = 20 mA — — 0.6 V

VD pin — 15 21 mA

VD pin — 9 14 mA

VD pin — 5 8 mA

VD pin — 40 55 µA

2.1 — — V

——0.8V

–10 — 10 µA

TIP

+

Ω

600

Si3015

V

TR

I

L

10 µF

–

RING

Figure 1. Test Circuit for Loop Characterist ics

Rev. 0.95 5

Si2400

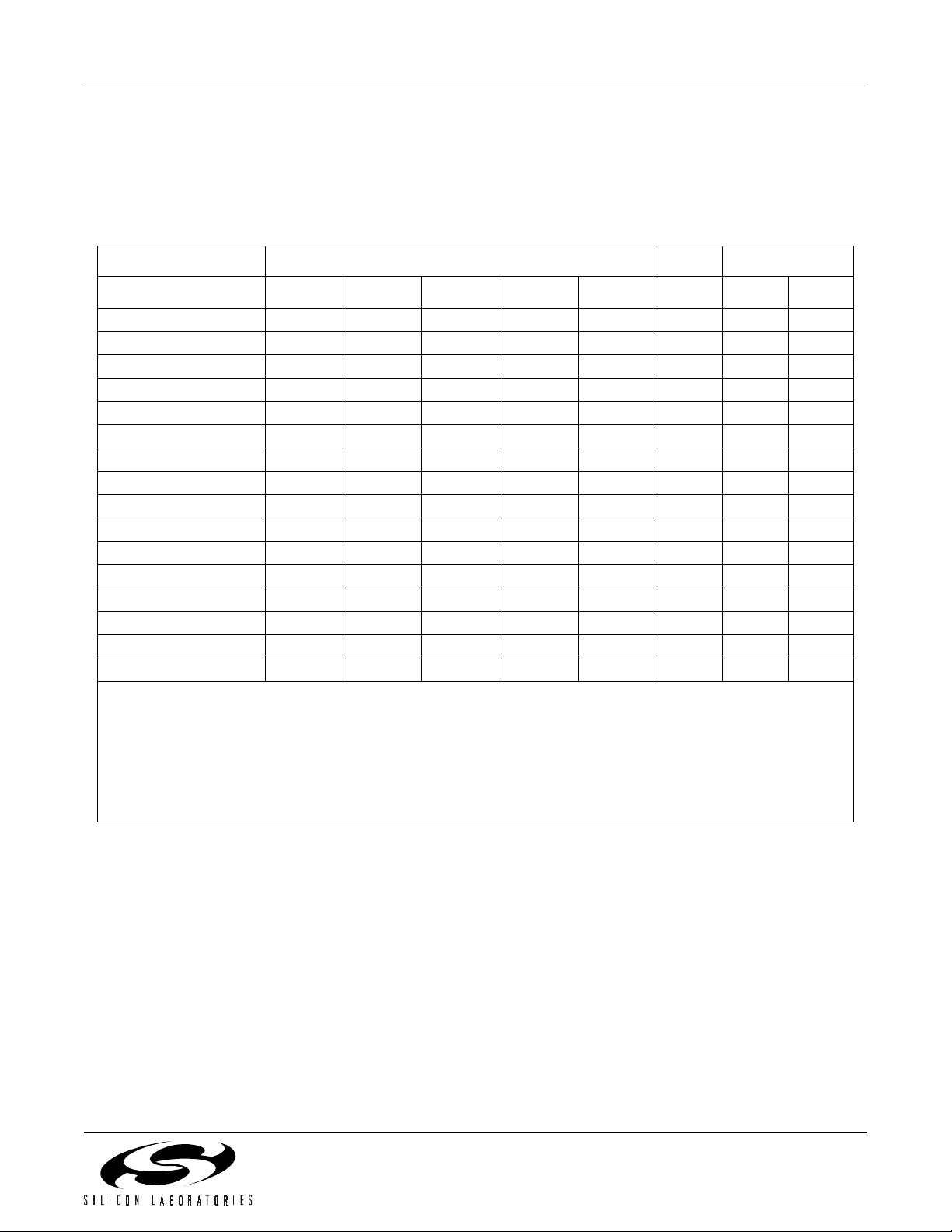

Table 5. DAA AC Characteristics

(VD = 3.0 to 3.6 V or 4.75 to 5.25 V, TA = 0 to 70°C

Parameter Symbol Test Condition Min Typ Max Unit

Transmit Frequency Response Low –3 dB Corner — 5 — Hz

Receive Frequency Response Low –3 dB Corner — 5 — Hz

Transmit Full Scale Level

Receive Full Scale Level

Dynamic Range

Dynamic Range

Dynamic Range

3,4

3,5

3

Transmit Total Harmonic Distortion

Transmit Total Harmonic Distortion

Receive Total Harmonic Distortion

Receive Total Harmonic Distortion

Dynamic Range (Caller ID mode) DR

Caller ID Full Scale Level (0 dB gain)

Notes:

1.

Measured at TIP and RING with 600 Ω termination.

2. Receive full scale level will produce –0.9 dBFS at TXD.

3. DR = VIN + 20*log (RMS signal/RMS noise). Measurement is 300 to 3400 Hz. Applies to both transmit and receive

paths. Vin = 1 kHz, –3dBFS, Fs = 10300 Hz

4. Vin = 1 KHz, –3 dB

5. Vin = 1 KHz, –9 dB

6.

THD = 20*log (RMS distortion/RMS signal). Vin = 1 kHz, –3 dBFS, Fs = 10.3 kHz

1

1,2

4,6

5,6

4,6

4,6

1

for K-Grade, TA = –40

V

FS

V

FS

to 85°C for B-Grade)

DR ACT = 0, DCT = 10 (FCC)

=100mA

I

L

DR ACT = 0, DCT = 01 (Japan)

I

=20mA

L

DR ACT= 1, DCT = 11(CTR21)

=60mA

I

L

THD ACT = 0, DCT = 10 (FCC)

=100mA

I

L

THD ACT = 0, DCT = 01 (Japan)

I

=20mA

L

THD ACT = 0, DCT = 01 (Japan)

=20mA

I

L

THD ACT = 1, DCT = 1 1 (CTR21)

=60mA

I

L

CID

V

CID

VIN = 1 kHz, –13 dB — 60 — dB

—0.6—dBm

—0.6—dBm

—82—dB

—82—dB

—82—dB

—–75—dB

—–75—dB

—–75—dB

—–75—dB

—2.7—V

PEAK

6 Rev. 0.95

Si2400

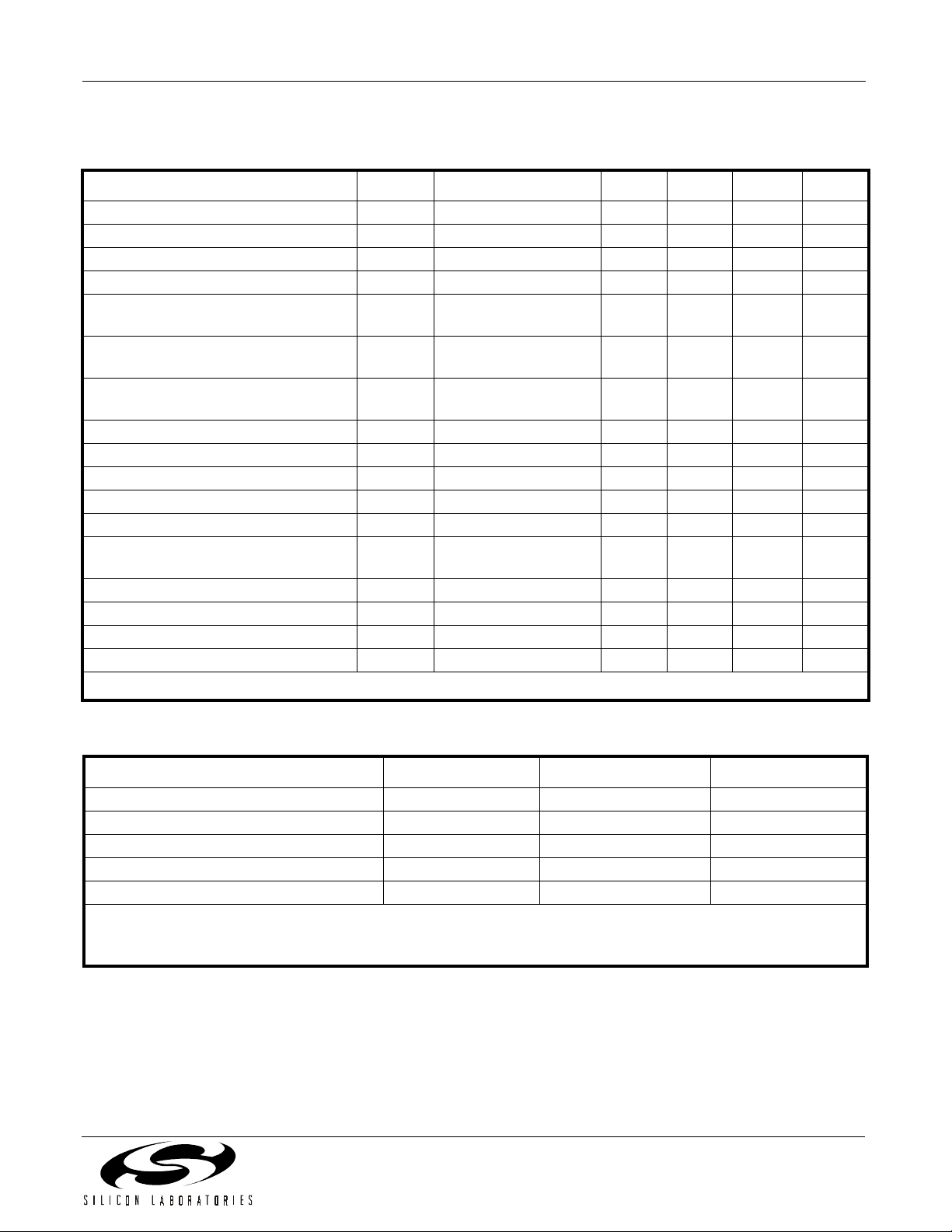

Table 6. Voice Codec AC Characteristics

(VD = 3.0 to 3.6 V or 4.75 to 5.25 V, TA = 0 to 70°C

Parameter Symbol Test Condition Min Typ Max Unit

AOUT Dynamic Range, APO = 0 VIN = 1 kHz — 40 — dB

AOUT THD, APO = 0 VIN = 1 kHz — –40 — dB

AOUT Full Scale Level, APO = 0 — 0.7*V

AOUT Mute Level, APO = 0 — 60 — dB

AOUT Dynamic Range, APO = 1,

V

= 4.75 to 5.25 V

D

AOUT Dynamic Range, APO = 1,

V

= 3 to 3.6 V

D

AOUT THD, APO = 1, V

5.25 V

AOUT THD, APO = 1, V

AOUT Full Scale Level, APO = 1 — 1.5 — V

AOUT Mute Lev el, APO = 1 — –65 — dB

AOUT Resistive Loading, APO = 1 10 — — kΩ

AOUT Capacitive Loading, APO = 1 — — 20 pF

AIN Dynamic Range, V

5.25 V

AIN Dynamic Range, V

AIN THD, V

AIN THD, V

= 4.75 to 5.25 V VIN = 1 kHz, –3 dB –55 –60 — dB

D

= 3 to 3.6 V VIN = 1 kHz, –3 dB –40 –60 — dB

D

AIN Full Scale Level

*Note: Receive full scale level will produce –0.9 dBFS at TXD.

= 4.75 to

D

= 3 to 3.6 V VIN = 1 kHz, –3 dB –40 –60 — dB

D

= 4.75 to

D

= 3 to 3.6 V VIN = 1 kHz, –3 dB 55 65 — dB

D

*

for K-Grade, TA = –40

VIN = 1 kHz, –3 dB 60 65 — dB

VIN = 1 kHz, –3 dB 55 65 — dB

VIN = 1 kHz, –3 dB –55 –60 — dB

VIN = 1 kHz, –3 dB 60 65 — dB

to 85°C for B-Grade)

—2.8—V

DD

—V

PP

PP

PP

Table 7. Absolute Maximum Ratings

Parameter Symbol Value Unit

DC Supply Voltage V

Input Current, Si2400 Digital Input Pins I

Digital Input Voltage V

Operating Temperature Range T

Storage Temperature Range T

Note: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation

should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

D

IN

IND

A

STG

Rev. 0.95 7

–0.5 to 6.0 V

±10 µA

–0.3 to (VD + 0.3) V

–10 to 100 °C

–40 to 150 °C

Si2400

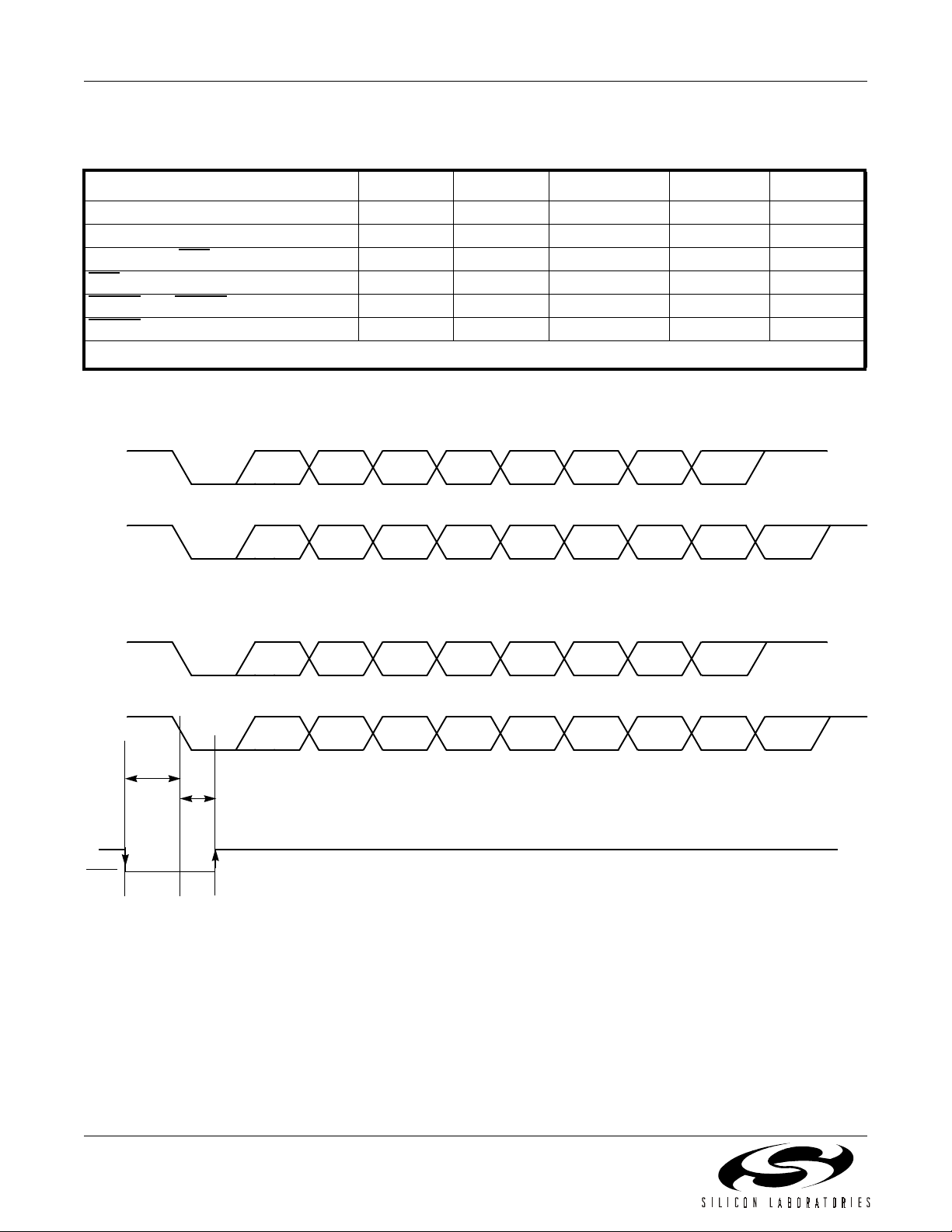

Table 8. Switching Characteristics

(VD = 3.0 to 3.6 V or 4.75 to 5.25 V, TA = 0 to 70°C

Parameter Symbol Min Typ Max Unit

CLKOUT Output Clock Frequency 2.4576 — 39.3216 MHz

Baud Rate Accuracy t

Start Bit ↓ to CTS

CTS

↓ Active to Start Bit↓ t

RESET

RESET

Note:

↓ to RESET

↑ Rise Time t

All timing is referenced to the 50% level of the waveform. Input test levels are VIH = VD – 0.4 V, VIL = 0.4 V

TXD

↑ t

↑ t

for K-Grade, TA = –40

bd

sbc

csb

rs

rs2

–1 — 1 %

— 1/(2*Baud Rate) — ns

10 — — ns

5.0 — — msec

— — 100 ns

Transmit Timing

to 85°C for B-Grade)

8-Bit Data

Mode (Default)

TXD

9-Bit Data

Mode

RXD

8-Bit Data

Mode(Default)

RXD

9-Bit Data

Mode

t

csb

CTS

StartD0D1D2D3D4D5D6D7Stop

StartD0D1D2D3D4D5D6D7 Stop

D8

Receive Timing

StartD0D1D2D3D4D5D6D7Stop

StartD0D1D2D3D4D5D6D7 Stop

t

sbc

D8

Note: Baud rates (programmed through register SE0) are as follows: 300, 1200, 2400, 9600, 19200,

230400, 245760, and 307200 Hz.

Figure 2. Asynchronous UART Serial Interface Timing Diagram

8 Rev. 0.95

Typical Application Circuit

VCC

C10

C27

C26

X1

12

GPIO3/AIN/ESC

GPI O2/ AIN/ RXD2

GPI O1/ AIN/ TXD2/ EO FR

U1

CLKOUT

RESET

1

XTALI

2

XTALO

3

CLKOUT

4

VD

TXD

RXD

CTS

5

TXD

6

RXD

7

CTS

89

RESET AOUT

GPIO4/AIN/ALERT

Si2400

AOUT

GPIO1

GPIO2

GPIO3

ISOB

GND

GPIO4

16

15

14

13

12

11

C1A

10

C30

C3

Rev. 0.95 9

No Ground Plane I n DAA S ection

R8

R7

R15

1

2

3

4

5

6

C1

C2

C4

7

89

U2

TSTA/Q E2

TX/FILT2

TSTB/ DCT

NC/FI LT

IGND

C1B

REXT

RNG1

DCT/REX T2

RNG2

NC/REF

QB

NC/VREG2

QE VREG

5

Si301

Q4

C12

C13

+

16

15

14

RX

13

12

11

10

R11

C6

C19

C18

R12

C16

C14

+

+

C5

R2

R13

C8

C7

R10

R9

R24

R18

Z1

Q1

R5

Q2

R6

C20

R16

R19

R17

Q3

FB2

D2

C9

RV2

D1

R26

R25

C25

C24

FB1

RING

C32

RV1

C31

TIP

Note 1:R12 R13 and C14 are onl requiredif complexAC terminationis used ACT bit 1 .

Note 2:See "Ringer Impedance" section foroptional Czech Republicsupport.

Note 3:See "BillingTone Immunit " sectionfor optional billing tone filter German S itzerland South Africa .

Note 4:See Appendix for applications requiring UL1950 3rd editioncompliance.

Figure 3. Typical Application Circuit Schematic

Si2400

Si2400

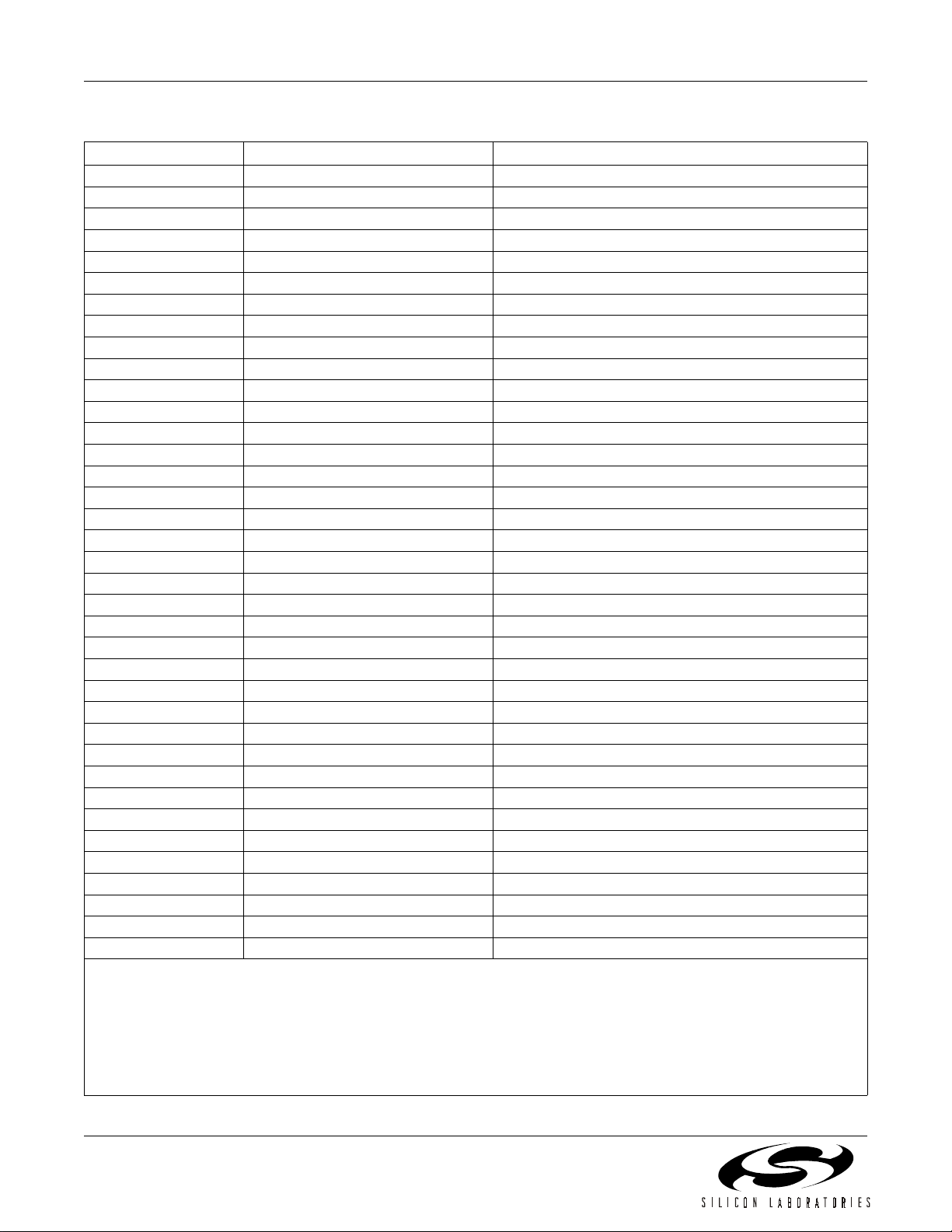

Bill of Materials

Table 9. Global Component Values—Si2400 Chipset

Component Value Suppliers

C1,C4 150 pF, 3 kV, X7R,±20% Novacap, Venkel, Johanson, Murata, Panasonic

1

C2

C3 0.22 µF, 16 V, X7R, ±20%

2

C5

C6,C10,C13,C 16 0.1 µF, 16 V, X7R, ±20%

C7,C8 1800 pF, 250 V, X7R, ±20% Novacap, Venkel, Johanson, M ur at a, Panasonic

C9 22 nF, 250 V, X7R, ±20% Novacap, Venkel, Johanson, Murata, Panasonic

C12 1.0 µF, 16 V, Tant/X7R, ±20%

2

C14

C18,C19 12 nF, 16 V, X7R, ±20%

C20 0.01 µF, 16 V, X7R, ±20%

C24,C25 1000 pF, 3 kV, X7R, ±10% Nova cap, Venkel, Johanson, Murata, Panasonic

C26,C27 33 pF, 16 V , NPO, ±5%

3

C30

3

C31,C32

4

D1,D2

FB1,FB2 Ferrite Bead, BLM31A601S Murata

Q1,Q3 A42, NPN, 300 V OnSemiconductor, Fairchild, Zetex

Q2 A92, PNP, 300 V OnSemiconductor, Fairchild, Zetex

5

Q4

RV1 Sidactor, 275 V, 100 A Teccor, ST Microelectronics, Microsemi, TI

6

RV2

2

R2

R5 100 kΩ, 1/16 W, ±1%

R6 120 kΩ, 1/16 W, ±5%

R7,R8,R15,R16,R17,R19

R9,R10 15 kΩ, 1/10 W, ±5%

R11 10 kΩ, 1/16 W, ±1%

2

R12

2

R13

R18 2.2 kΩ, 1/10 W, ±5%

R24 150 Ω, 1/16 W, ±5%

R25,R26 10 MΩ, 1/1 6 W, ±5%

U1 Si2400 Silicon Labs

U2 Si3015 Silicon Labs

Y1 4.9152 MHz, 20 pF, 50 ppm, 150 ESR Not Installed

2

Z1

8

Notes:

1. C2 was included in previous revisions of the data sheet. Replacing C2 with C4 improves longitudinal balance.

2. For FCC-only designs: C14, R12, and R13 are not required; R2 may be ±5%; with Z1 rated at 18 V, C5 may be rated at 16 V; also see note 7.

3. C30, C31, C32 may provid e an additio nal improvement in emissions/immunity and/or voice performance, depending on design and layout. Population

option recommended. See "Emissions/Immunity‚" on page 62.

4. Several diode bridge configurations are acceptable (suppliers include General Semi., Diodes Inc.).

5. Q4 may require copper on board to meet 1/2 W power requirement. (Contact manufacturer for details.)

6. RV2 can be installed to improve performance f rom 2500 V to 3500V for multiple longit udinal surges (240 V, MOV).

7. The R7, R8, R15, and R16, R17, R19 resistors may each be replaced with a single resistor of 1.62 kΩ, 3/4 W, ±1%. For FCC-only designs, 1.62 kΩ, 1/16

W, ±5% resistors may be used.

150 pF, 3 kV, X7R,±20% Not Installed

0.1 µF, 50 V, Elec/Tant/X7R, ±20%

0.68 µF, 16 V, X7R/Elec/Tant, ±20%

10 pF, 16 V, NPO, ±10% Not Installed

1000 pF, 3 kV, X7R, ±10% Not Installed

Dual Diode, 300 V, 225 mA Central Semic onductor

BCP56, NPN, 60 V, 1/2 W OnSemiconductor, Fairchild

240 V, MOV Not Installed

402 Ω, 1/16 W, ±1%

4.87 kΩ, 1/4 W, ±1%

78.7 Ω, 1/16 W, ±1%

215 Ω, 1/16 W, ±1%

Zener Diode, 43 V, 1/2 W Vishay, Motorola, Rohm

10 Rev. 0.95

Si2400

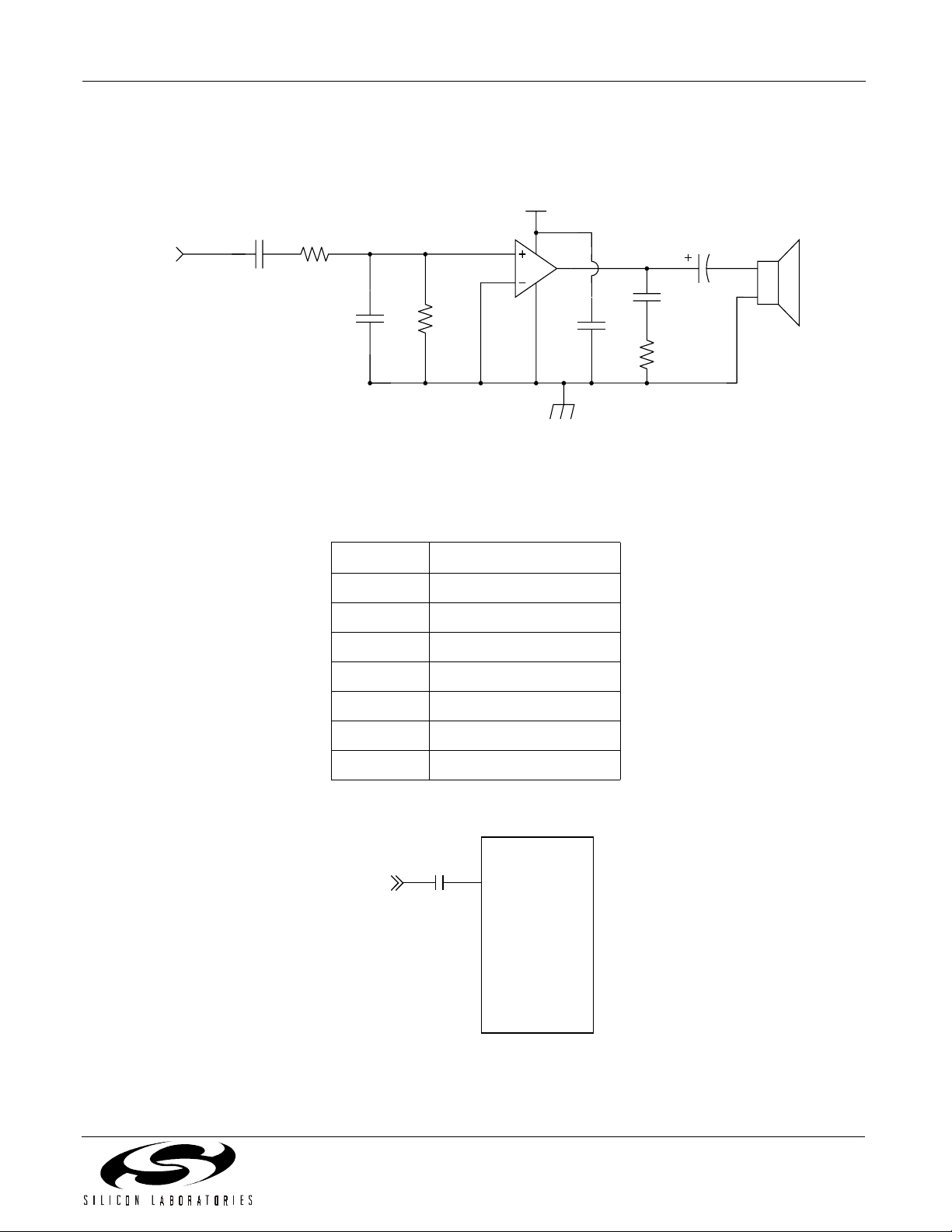

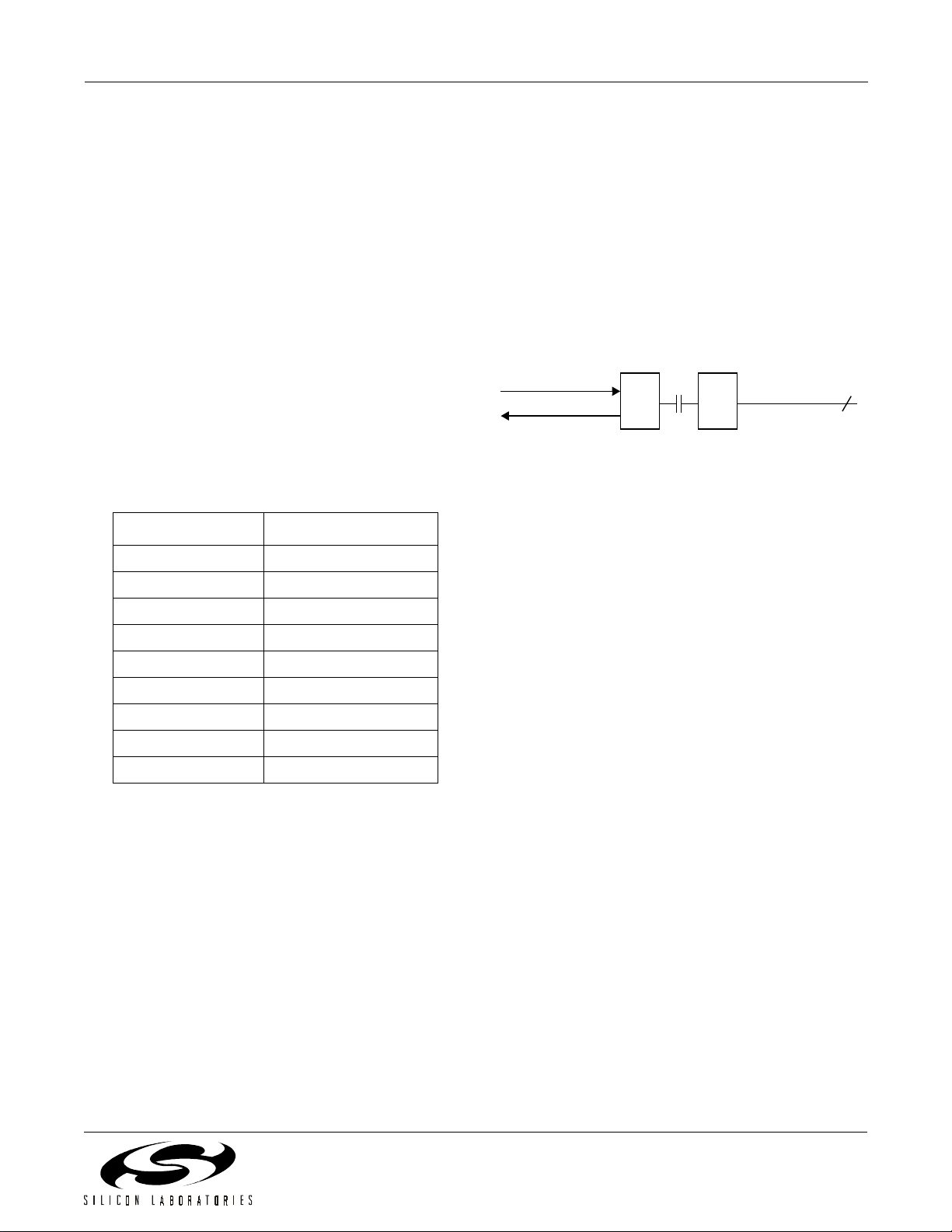

Analog Input/Output

Figure 4 illustrates a n optional application circuit to support the analog output ca pability of the Si2400 for voi ce

monitoring purposes.

+5V

C2

AOUT

R3

C6

R1

6

3

2

5

U1

4

C3

C4

C5

Speaker

R2

Figure 4. Optional Connection to AOUT for a Monitoring Speaker

‘

Table 10. Component Va lues—Optional Connection to AOUT

Symbol Value

C2, C3, C5 0.1 µF, 16 V, ±20%

C4 100 µF, 16 V, Elec. ±20%

C6 820 pF, 16 V, ±20%

R1 10 kΩ, 1/10 W, ±5%

Analog Input

Figure 5. Analog Input Circuit

R2 10 Ω, 1/10 W, ±5%

R3 47 kΩ, 1/10 W, ±5%

U1 LM386

Si2400

AIN/GPIO

0.1 µF

1 Vrms

Rev. 0.95 11

Si2400

Functional Description

The Si2400 ISOmodem is a complete modem chipset

with integrated direct access arrangement (DAA) that

provides a programmable line interface to meet global

telephone line requirements. Available in two 16-pin

small outline pa cka ge s, this sol ut io n inc lud es a D SP dat a

pump, a modem co ntroller, an analog fron t end (AFE), a

DAA, and an audio co de c.

The modem, which accepts simple modem AT

commands, provides connect rates of up to 2400 bps,

full-duplex over the Public Switched Telephone Network

(PSTN) with V.42 hardware support through HDLC

framing. To minimize handshake times, the Si2 400 can

implement a V.25-based fast connect feature. The

modem also su pp or ts the V.23 reversing pr oto col a s we ll

as SIA and other al ar m sta nd ard fo rma t s.

As well as suppor ting the modem si gnallin g proto cols, th e

ISOmodem provides numerous additional features for

embedded mode m ap pl ic a ti on s. T he S i 24 00 in c lu de s full

caller ID detection and decoding for the US, UK, and

Japanese caller ID formats. Both DTMF decoding and

generation are prov ided on chip a s well. Call pro gres s is

supported both at a high level through echoing result

codes and at a low level through user-programmable

biquad filters and parameters such as ring period, ring

on/off time, and dialing interdigit time.

This device is ideal for embedded modem applications

due to its small board space, low power consumption,

and global compliance. The Si2400 solution integrates a

silicon DAA using Silicon Laboratories’ proprietary

ISOcap™ technology. This highly integrated DAA can be

programmed to meet worldwide PTT specifications for

AC termination, DC termination, ringer impedance, and

ringer thresh old. The DAA a lso can mon itor l ine st atu s for

parallel handset detection and for overcurrent conditions.

The Si2400 is designed so that it may be rapidly

assimilated into existing modem applications. The device

interfaces directly through a UART to either a

microcontroller or a standard RS-232 connection. This

simple interfa ce allows for PC evalua tion of the modem

immediately up on po we rup v i a t he AT commands across

a standard hyperterminal.

The chipset can be fully programmed to meet

international telephone line interface requirements with

full compliance to FCC, CTR21 , JATE, and other countryspecific PTT specifications. In addition, the Si2400 has

been designed to meet the most stringent worldwide

requirements for out-of-band energy, billing-tone

immunity, lightning surges, and safe ty re qu ire me nts .

The Si2400 solut ion needs only a few low-cost disc rete

components to achieve global compliance. See Figure 3

on page 9 for a typi cal ap pli cati on cir cu it .

Table 11. Selectable Configurations

Configuration Modulation

V.21 FSK 1080/1750 300 Full

V.22 DPSK 1200/2400 1200 Full

V.22bis (1200 fallback) DPSK 1200/2400 1200 Full

V.22bis QAM 1200/2400 2400 No retrain*

V.23

FSK

V.23 1300/1700 600/75

Bell 103 FSK 1170/2125 300 Full

Bell 212A DPSK 1200/2400 1200 Full

Security DTMF — 40 Full

SIA—Pulse Pulse — Low Full

SIA Format FSK 1 170/2125 300 half-duplex 300 bps only

*Note: The Si2400 only adjusts its baud ra te for li ne condi tions during the in itiali zation of the ca ll. Retra ining to a ccommo date

changes in line conditions which occur during a call must be implemented by terminating the call and redialing.

Carrier

Frequency (Hz)

1300/2100 1200/75

Data Rate

(bps)

Standard

Compliance

Full; plus reversing

(Europe)

12 Rev. 0.95

Si2400

Digital Interface

The Si2400 has an asynchronous serial port (UART)

that supports st andard microcontroller interfaces. After

reset, the baud rate defaults to 2400 bps with the 8-bit

data format described bel ow. Immediately after powerup, the device must be progr ammed using the primary

serial port because the secondary serial port is disabled

by default. The CLKOUT clock will be running with a

frequency of 9.8304 MHz.

The baud rate of the serial l ink is e stablished by writin g

S register SD (SE0.2:0). It may be set for 300, 1200,

2400, 9600, 19200, 228613, 245760, or 307200 bps.

Immediately after the ATSE0=xx string is sent, the user

must reprogram the host UART to matc h the selected

new baud rate. The higher baud rate settings (>230400)

can be used for tra nsferring PCM d ata from the host to

the Si2400 for transmission of voice data over the

phone line or through the voice codec.

Table 12. Register S07 Examples: DTMF = 0,

HDEN = 0, BD = 0

Modem Protocol Register S07 Values

data bits, and the line data fo rmat is 8 data bits (8N1),

then the MSB from the l ink will be dropped as the 9-bit

word is passed from the link sid e to the line si de. In this

case, the dropped ninth bit can then be used as an

escape mechanism. However, if the link data format is 8

data bits and the line data fo rm at i s 9 data b its , an MSB

equal to 0 will be added to the 8- bit wor d as it is pas se d

from the link side to the line side.

The Si2400 UART does not continuou sly c heck for sto p

bits on the incom ing digital data. Ther efore, if the RXD

pin is not high, the TXD pin may transmit mean ingless

characters to the host UART. This requires the host

UART to flush its receiver FIFO upon initialization.

RXD UART

TXD

Link Line

Data Rate: SD (SE0.2:0)

Data Format: ND (SE0.3)

Si2400 Si3015

RJ11

Data Rate: S07

Data Format: S15

Figure 6. Link and Line Data Formats

V.21 0x03

Bell 103 0x01

V.22 0x02

Bell 212A 0x00

V.22bis 0x06

V.23 (75 tx, 1200 rx) 0x24

V.23 (1200 tx, 75 rx) 0x14

V.23 (75 tx, 600 rx) 0x20

V.23 (600 tx, 75 rx) 0x 10

Configurations and Data Rates

The Si2400 can be configured to any of the Bell and

CCITT operation modes. This device also suppo rts SIA

and other security modes for the security industry.

Table 11 provides the modulation method, the carrier

frequencies, the data rate, the baud rate and the notes

on standard complianc e for each modem configuratio n

of the Si2400. Table 12 shows example register settings

(SO7) for some of the modem configurations.

As shown in Figure 6, 8-bit a nd 9-bit data modes refer

to the link data format over the UART. Line data formats

are configured through registers S07 and S15. If the

number of bits specified by the link data format differs

from the number of bits specified by the line data

format, the MSBs will either be dropped or bit-stuffed,

as appropriate. For ex ample, if th e link data forma t is 9

Command/Data Mode

Upon reset, the modem will be in command mode and

will accept AT-style commands. An outgoing modem

call can be made using the “ATDT#” (tone dial) or

“ATDP#” (pulse dial) command after the device is

configured. If the handshake is successful, the modem

will respond with the “c”, “ d”, o r “v ” str i ng an d en ter data

mode. (The byte following the “ c”, “d”, or “v” will be the

first data byte.) At this point, A T-style commands are not

accepted. There a re thre e meth ods whic h may be u sed

to return the Si2400 to command mode:

!

Use the ESC pin—To program the GPIO3 pin to

function as an ESCAPE input, set GPIO3

(SE2.5:4) = 3. In this setting, a positive edge

detected on this pin will return the modem to

command mode. The “AT O” string can be used to reenter data mode.

!

Use 9-bit data mode—If 9-bit data format with

escape is programmed, a 1 detected on bit 9 will

return the modem to command mode. (See Figure 2

on page 8.) This is enabled by setting ND (SE0.3) =

1 and NBE (S15.0) = 1. The “ATO” string can be

used to reenter data mode.

!

Use TIES—The time independent escape sequence

is a sequence of three escape characters ("+"

characters by default). Once these characters have

been recognized, the modem enters the Command

state without sending a confirming result code to the

terminal. The modem then starts an internal prompt

Rev. 0.95 13

Si2400

delay timer. From that point on if an AT<CR>

(attention) command is received before the timer

expires, the timer is stopped and the “O” response

code is sent to the terminal. This indicates that the

Si2400 is in command mode.

If any other data is received while the timer is

running, the timer is stopped, the device returns to

the online state, and the data received through the

UART RXD is sent to the other modem.

If the timer expires, a confirming “O” response code

is sent to the terminal indicating that the modem is in

command mode.

TIES can be enabled by writing register TED

(S14.5)=1. Both the escape character “+” and the

escape time-out period are programmable via

registers TEC (S0F) and TDT (S10), respectively.

Note: TIES is not the recommended escape solution for the

most robust designs. Any data strings that actually

contain the escape character three times in a row will

interrupt a data sequence erroneously.

Whether using an escape method or not, when the

carrier is lost, the modem will automatically return to

command mode and report “N”.

8-Bit Data Mode

This mode is asynchronous, full-duplex, and uses a

total of 10 bits (shown in Figure 2 on page 8). To

program 8-Bit Data mode, set ND (SE0.3) = 0. (Note

that 8-Bit Data mode is the defa ult.) The 10 bi ts consist

of a start bit (logic 0), 8 data bits, and 1 stop bit (logic 1).

Data transmission from the Si2400 to the host takes

place on the TXD pin. It beg ins whe n th e Si 24 00 l owers

TXD, placing the start bit on the pin. Data is then shifted

out onto the pin, LSB fi rst. After 8 data bits, th e stop bit

follows. All bits are s hi fted out a t the ra te d etermi ne d by

the baud rate register.

Once the baud rate register SD (SE0.2:0) is written,

reception by the Si2400 may begin at any time. The

falling edge of a start bit will signal to the Si2400 that the

reception process has begun. Data should be shifted

onto RXD at the selected baud rate.

After the middle of the stop-bit time, the receiver will go

back to looking for a 1 to 0 transition on the RXD pin.

9-Bit Data Mode

This mode uses a total of 11 bits in UART

communication. To program 9-Bit Data mode, set ND

(SE0.3) = 1. The 11 bits consist of one start bit (logic 0),

9 data bits, and 1 stop bit (logic 1, see Figure 2 on page

8). As in 8-Bit Data mode, the trans missions occur on

the TXD signal pin and receptions on the RXD pin.

Data transmission from the Si2400 to the host takes

place on the TXD pin. It beg ins whe n th e Si 24 00 l owers

TXD, placing the start bit on the pin. Data is then shifted

out onto the pin, LSB fi rst. After 9 data bits, t he stop bit

follows. All bits are shifted out a t the rate d eterm ine d by

the baud rate register.

Once the baud rate register SD (SE0.2:0) is written,

reception may begin at any tim e. The falling edge of a

start bit on the RXD pin will begin the reception process.

Data must be shifted in at the selected baud rate.

The ninth data bit may be used to indicate an escape by

setting NBE (S15.0) = 1. If so, this bi t will normally be

set to 0 when the modem is online. To go offline into

command mode, se t th is b it to 1. The next fram e wi ll b e

interpreted as a command. Data mode can be

reentered using the ATO command.

After the middle of the stop-bi t time, the rece iver will go

back to looking for a 1 to 0 transition on the RXD pin.

Flow Control

If a higher serial link line (UART) data rate is

programmed than the baud rate of the modem, flow

control is required to prevent loss of data to the

transmitter. No flow control is nee ded if the same baud

rate as modem rate is programmed. Note that in

compliance with the V.22bis algorithm, the V.22bis

(2400 baud) modem will connect at 1200 baud if it

cannot make a 2400 baud connection.

To control flow, the CTS

Figure 2 on page 8, the CTS

pin is used. As shown in

pin will normal ly be high,

and will be lo w whenever the m odem is able t o accept

new data. The CTS

pin will go high again a s soon as a

start bit is detected on the RXD pin and will remain high

until the modem is ready to accept another character.

Low Power Modes

The Si2400 has three low power modes. These are

described below:

!

DSP Powerdown. The DSP processor can be

powered down by setting register PDDE (SEB.3) =1.

In this mode the serial interface still functions as

normal, and the modem will be able to detect ringing

and intrusion. No modem modes or tone detection

features will function.

!

Wake Up On Ring. By issuing the “z” command, the

Si2400 goes into a low power mode where both the

microcontroller and DSP are powered down. Only

incoming ringing or a total reset will power up the

chip again.

!

Total Powerdown. By writing registers PDN (SF1.6)

and PDL (SF1.5), the Si2400 will be put into a total

powerdown mode. In this mode, all logic is powered

down, including the crystal oscillator and clock-out

pin. Only a hardware reset can restart the Si2400.

14 Rev. 0.95

Si2400

Global DAA Operation

The Si2400 chipset co ntains an in tegrated sil icon direc t

access arrangement (silicon DAA) that provides a

programmable line interface to meet international

telephone line interface requirements. Table 13 gives

the DAA register setti ngs required t o meet internati onal

PTT standards. A detailed description of the r egisters in

Table 13 can be found in "Appendix A—DAA

Operation‚" on page 62.

Table 13. Country-Specific Register Settings

Register SF5 SF7 SF6

Country OHS ACT DCT RZ RT LIM VOL FNM

Australia 112 0000 0

Bulgaria 01200000

CTR21

Czech Republic 0 1 2 0 0 0 0 0

FCC 002 0000 0

Hungary 002 0000 0

Japan 001 0000 0

Malaysia

New Zealand 0 1 2 0 0 0 0 0

Philippines 001 00001

Poland

Singapore

Slovakia 01200000

Slovenia 01200000

South Africa

South Korea

1

2

3

2

3

3

013 0010 0

001 0000 0

002 1100 0

001 0000 0

112 1000 0

001 1000 0

Note:

1. CTR21 includes the following countries: Austria, Belgium, Cyprus, Denmark, Finland, France,

Germany, Greece, Iceland, Ireland, Israel, Italy, Liechtenstein, Luxembourg, Netherlands, Norway,

Portugal, Spain, Sweden, Switzerland, and the United Kingdom.

2. Supported for loop current ≥ 20mA.

3. The RZ register (SF5.1) should only be set for Poland, South Africa and South Korea if the ringer

impedance network (C15, R14, Z2, Z3) is not populated.

Parallel Phone Detection

The Si2400 has the abilit y to detect another phone that

is off hook on a shared li ne. This all ows the ISO modem

both the ability to avoid interrupting another call on a

shared line and to intelligently handle an interruption

when the Si2400 is using the line. An automatic

algorithm to detect paralle l phone intrusion (defined as

an off-hook parallel handset) is provided by default.

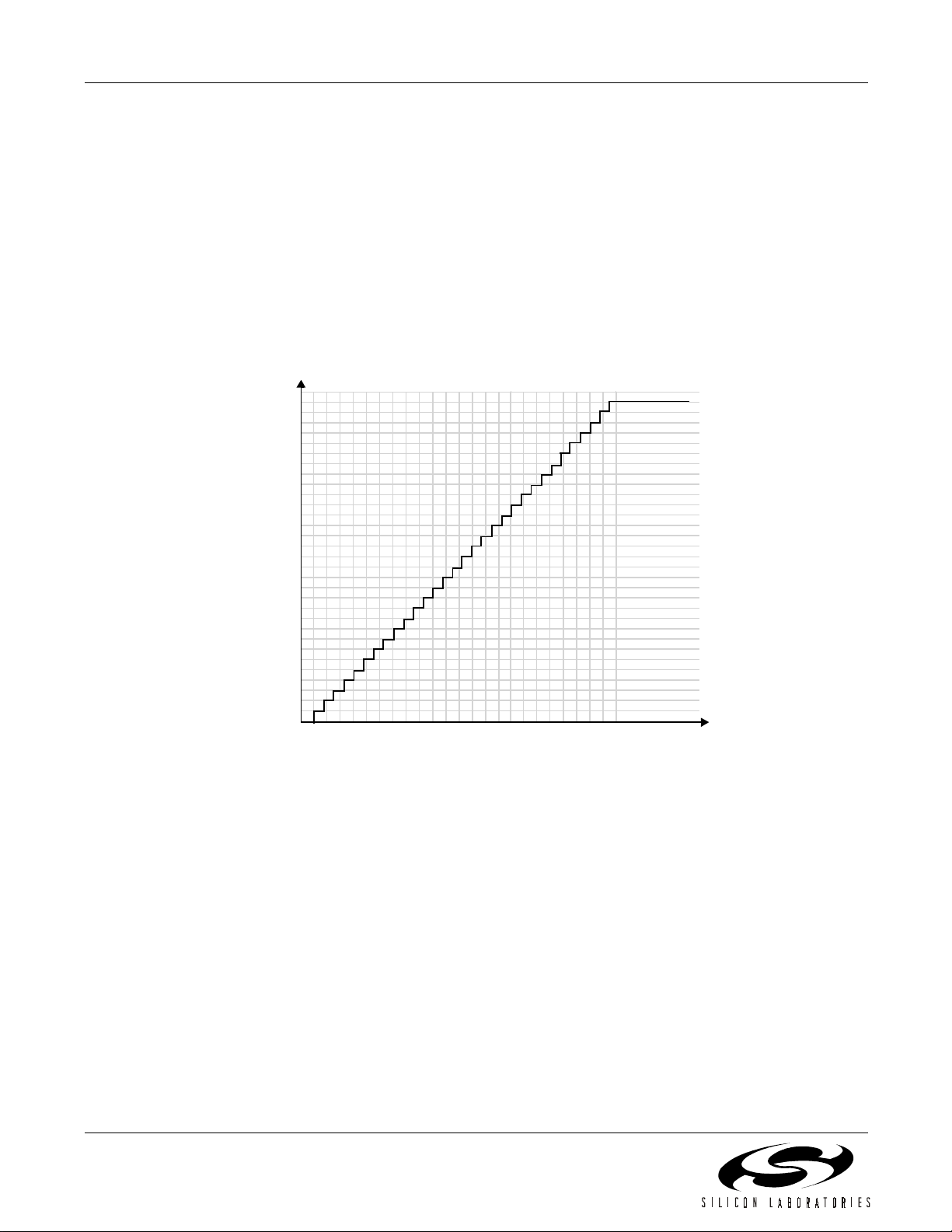

On-Hook Intrusion Detection

The on-hook intrusion detection allows the user to avoid

interrupting another ca ll on a shared line. To implement

the intrusion detecti on, the Si2400 uses a loop vol tage

sense (register LVCS (SDB)). When on hook, LVCS

monitors the line voltage. ( When off hook, it measures

current.) LVCS has a full scale of 70 V with an LSB of

2.25 V. The first code (0 → 1) is skewed such that a 0

indicates that the line voltage is < 3.0 V. The voltage

accuracy of LVCS is ±20%. The user can read these

bits directly when on hook through register LVCS.

The automatic on-hook detector algorithm can be

tripped by either an absolute level or by a voltage

differential by selecting ONHD (S13.3). If the absolut e

detector is chosen, th e Si2400 algorithm will d etect an

intrusion if LVCS is less than the on-hook intrusion

Rev. 0.95 15

Si2400

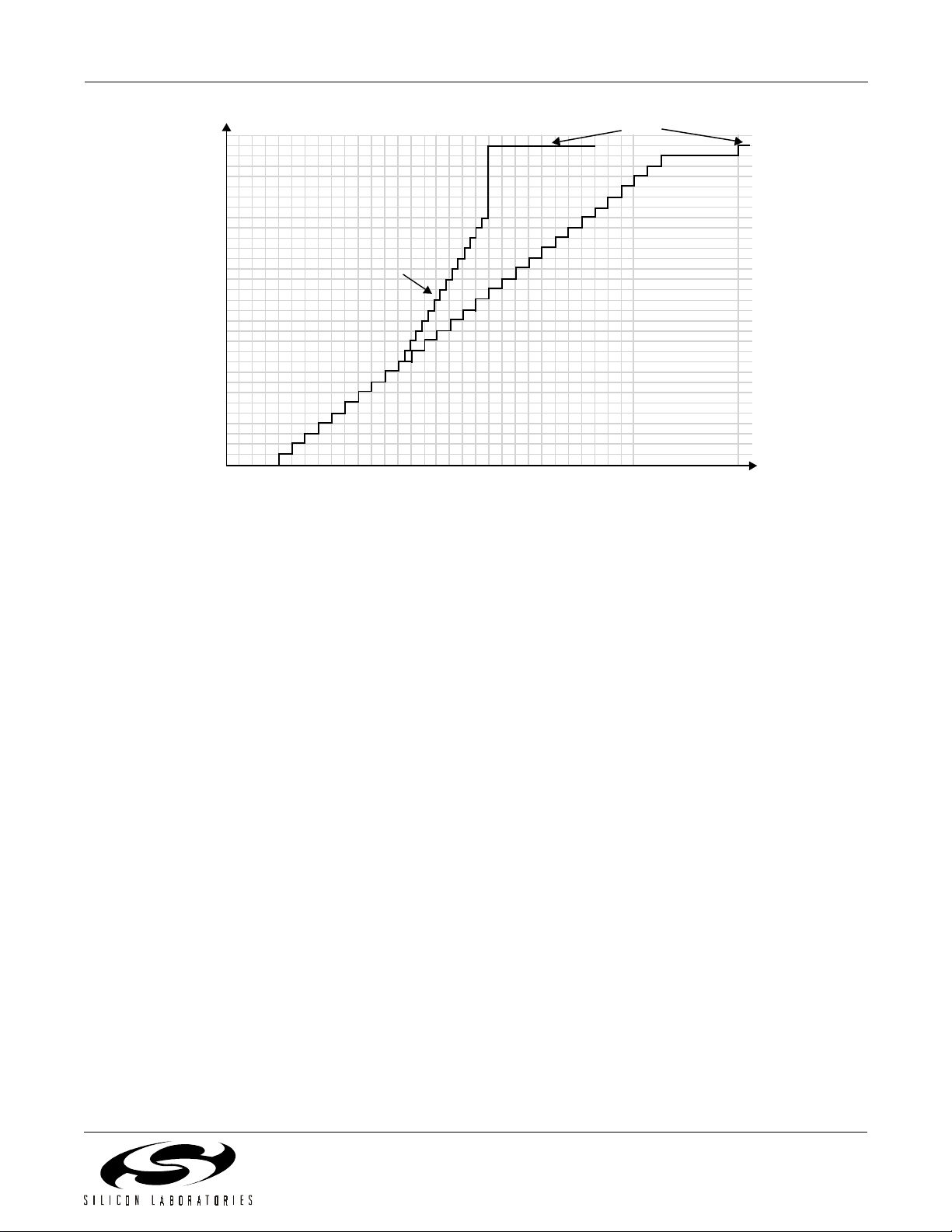

threshold, register AVL (S11.4:0). In other words, it is

determined that an intrusion has occurred if LVCS <

AVL.

AVL defaults to 0x0D, or 30 V on powerup. The

absolute detector is the co rrect method to use for FCC

and most other countries. T he absolu te detector sho uld

also be used to de tect the presence (or abs ence) of a

line connection.

Under the condition of a ver y short line and a currentlimiting telephone off hook, the off-hook line vo ltage can

be as high as 40 V. The minimum on-hook voltage may

not be much greater. This condition can occur on phone

30

25

20

LVCS

BIT

15

lines with current-li mi tin g s pec if ic ations s uch as Fra nce.

For these lines, a differential detector is more

appropriate.

The differential detector method checks the status of the

line every 26.66 ms. The detec tor compares (LVCS (t –

0.02666) – LVCS (t)) to the differential threshold level

set in register DVL (S11.7:5). The default for DVL is

0x02 (5.25 V). If the threshold is ex ceeded (LVCS (t –

0.02666) – LVCS (t) > D VL), an in trusion is detected. If

(LVCS (t) – LVCS (t – 0.02666) > DVL), then the

intrusion is said to have terminated.

10

5

0

0

36 33302724211815129 3639424548

Loop Voltage

Figure 7. Loop Voltage—LVCS T ransfer Function

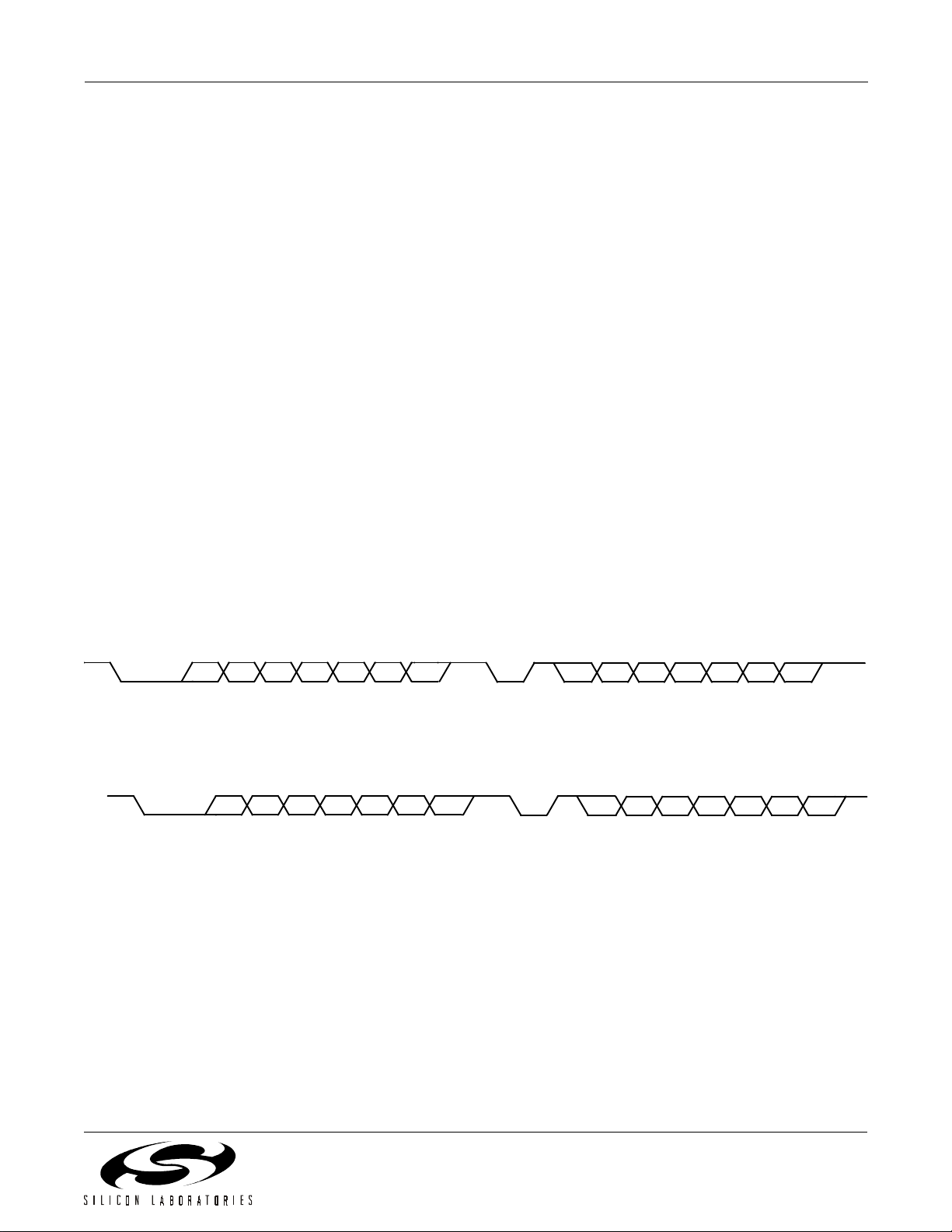

Off-Hook Intrusion Detection

When the Si2400 is off hook, it can detect another

phone going off hook by monitoring the DC loop current.

The loop current sense transfer function is shown in

Figure 8 with the upper curve representing CTR21

(current limiting) operation and the lower curve

representing all other modes. The overload points

indicate excessive current draw. The user can read

these bits directly through register LVCS (SDB). Note

that as in the line voltage sense, there is hysteresis

between codes (0.375 mA for CTR21 mode and

0.75 mA for ROW).

7269666360575451

100

16 Rev. 0.95

Si2400

Overload

30

25

LCS

BIT

20

15

10

5

0

0

36 33302724211815129 3639424548

CTR21

Loop Current (mA)

Figure 8. Loop Current—LVCS Transfer Function

The off-hook algorithm can be chosen to use eithe r a

differential current detector or an absolute current

detector via setting OFHD (S13.4).

Because of the extra code and host processing required

by the absolute current method, the differe ntial current

method is chosen to be the defau lt. This method uses

two techniques to detect an intrusion. The first

technique is described as follows:

If (LVCS (t – 400 ms) – LVCS (t)) > DCL, then an

intrusion is deem ed to have taken place. If (LVCS (t) –

L VCS (t – 400 ms)) > DCL, then the intrusion is deemed

to have completed. Default DCL is 2.

The second technique takes advantage of the DC

holding circuit. If a parallel phone suddenly goes off

hook, the DC holding circuit will not reac t immediately,

therefore the loop c urrent through the Si2400 will drop

briefly to zero. Thus, an i ntrusion is als o reported when

LVCS = 0.

If the absolute detector is chosen, the Si2400 will detect

an intrusion under the condi tion that LVCS is less than

the off-hook intrusion threshol d, regi ster A CL (S12.4: 0).

In other words, it is determined that an intrusion has

occurred if LVCS < ACL. ACL defaults to 3 (15.5 mA) on

powerup. Because the loop current can vary from

20 mA to 100 mA, depending on the line, a factory

preset threshold is not useful.

If the host wishes to use this absolute mode, the host

must measure the line current and then set the

threshold accordingly. A measurement of the loop

7269666360575451 75 78 81 84 87 90 93

140

current is accomplished by going off-hook (issuing the

“ATDT;” command), reading LVCS after 50 ms, and

going back on hook using the “ATH” command. This

measured value of LVCS should be used to determine

the threshold register ACL. If this method is used, the

loop current should b e measur ed on a pe riodic bas is to

account for drift in line resistance.

The absolute curren t method is the most accu rate, and

it is necessary to use thi s method in order to determ ine

if another phone goes off hook simultaneous with or

immediately (< 400 ms) af ter the Si 240 0 phon e goe s off

hook. It does, however, require processi ng by the host,

including periodic off-hook events to measure the loop

current.

If an intrusion event is detected while in command

mode, an “i” is echoed to the host; When it is terminated

an “I” is echoed. The host may also be notified of an

intrusion when in data mo de through the A LERT pin by

setting GPIO4 (SE2.7:6) = 3. Upon intrusion, the

ALERT pin will go high, and the host may then read

register IND (S14.1) to confirm an intrusion.

The host may use the automatic intrusion detection

algorithm (the default ) by monitoring the ALERT pin or

waiting for the character echoes. The host may also use

the LVCS, AVL, and DVL registers as a basis for a

custom algorithm. Note that LVCS only acts as a line

voltage sense when on hook. When off hook, it

becomes the line current sense register.

Rev. 0.95 17

Si2400

Carrier Detect/Loss

The Si2400 can provide the functionality of a loss-ofcarrier pin similar t o the CD pin functionality in an R S232 connection. If programmed as an ALERT, GPIO4

will go high in online mod e when either parallel phone

intrusion or a loss-of- carrier is detected. When used in

this manner, the host detects a low-to-high trans ition on

GPIO4 (ALERT), escapes into command mode, and

reads register IND (S14.1). If high, IND indicates

intrusion. If low, IND indicates loss-of-carrier.

Overcurrent Protection

The Si2400 has built in prote ction to avoid damage to

the device due to overcurrent situations. An example

situation occurs when plugging the m ode m i nto a d igital

PBX outlet and attempting to go off-hook. Digital PBX

systems vary, but many can provide a DC feed vol tage

of up to 70 V and therefore have the ability to deliver

hundreds of milliamps of current into the DAA.

The Si2400 will always go off hook with the currentlimiting mode enabled. This allows no possibility of

damage for voltages up to about 48 V. However, at

higher voltages the 43 V Zener protection device will

begin to conduct and co uld be damaged if the power is

applied for too long.

The Si2400 will det ect the v alue of the lo op cur rent at a

programmable time after going off-hook (default =

20 ms) via register OHT (S32). If the loop current is too

high, an “x” will be echoed back to the host to indi ca te a

fault condition. The host may then check register OD

(S14.3) to confirm an overcurrent condition and go back

on hook if necessary.

The user can optionally enable another protection

feature, the overcurrent protection, via register AOC

(S14.4). This protection feature can automatically detect

an overcurrent condition and put the Si2400 into a lower

drive mode, which is si milar to the current-limi ting mod e

but has reduced hoo kswitch drive. This feature allows

the Si2400 to remain off-hook on a digital line for a

longer period of time without damage. If the Si2400

does not detect over current aft er the time s et by OCDT

(S32), then the c orrect line terminat ion is applied. This

method of going off hook in current-limiting mode can

be disabled by clearing OFHE (S13.5).

Caller ID Decoding Operation

The Si2400 supports ful l cal le r ID d etecti on a nd dec od e

for US Bellco re, UK, and Japanese standards. To use

the caller ID decoding feature, the following set-up is

necessary:

1. Set ND (SEO.3) = 0 (Set modem to 8N1 configuration)

2. Set CIDU (S13.1) = 1(Set modem to Bellcore type caller

ID) or CIDB (S13.2) = 1 (Set modem to UK type caller ID)

or JID (S13.7) = 1 (Set modem to Japanese type caller ID)

3. Set baud rate either to 1200 bps without flow control or

greater than 1200 bps with flow control.

Bellcore Caller ID Operation

The Si2400 will d etect the fir st ring burst sig nal and will

echo an “R” to the host. The device will then start

searching for the call er ID preamb le sequen ce after the

appropriate time-out. When 50 continuous mark bits

have been detected, the “m” res pon se will be ec hoe d to

indicate that the mark has been detected and that caller

ID data will follow.

At this point the algorith m will look for the first start bi t,

assemble the characters, and then transmit them out of

the UART as they are detected. When the caller ID

burst finishes, the carrier will be lost and the modem will

echo an “N” to indicate that the carrier is lost.

At this point the Si2400 will continue detecting ring

bursts and echoing “R” for each burst, and will

automatically answer after the correct number of rings.

UK Caller ID Operation

When the Si2400 detect s a line reversa l, it will echo an

“f” to the host. It will then start searching for the Idle

State Tone Alert Signal. When this signal has been

detected, the Si2400 will transmit an “a” to the host.

After the Idle State Tone Alert Signal is completed, the

Si2400 will apply the wetting pulse for the required

15 ms by quickly going o ff hook and o n hook . From th is

point on, the algorithm is identical to that of B ellcore in

that it will search f or the chan nel seizu re signal and the

marks before echoing an “m” and will then report the

decoded caller ID data.

Japan Caller ID Operation

After a polarity reversal and the first ring burst are

detected, the Si2400 is taken off hook. After 40 1s

(marks) have been det ected, the Si24 00 will search for

a start bit, echo an “m” for mar k, and begin asse mbling

characters and tra nsmitting them out through the s erial

port. When the carrier is lost, the Si2400 immediately

hangs up and echoes “N” . Al so, if no ca rrie r is d etecte d

for three seconds, the line hangs up and echoes “N”.

Force Caller ID Monitor

The Si2400 may be used to continuously monitor the

phone line for the caller ID mark signal s. This can be

useful in systems that require dete cti on of calle r ID data

before the ring sign al, voice mail indic ator signals, and

Type II caller ID support. To force the Si2400 into caller

ID monitor mode, set CIDM (S0C.5).

18 Rev. 0.95

Si2400

Tone Generation and Tone Detection

The Si2400 provides comprehensive and flexible tone

generation and detection. This includes all tones

needed to establish a circuit connection and to se t up

and control a communication session. The tone

generation furnishes the DTMF tones for PSTN auto

dialing and the supervisory tone s for cal l establi shmen t.

The tone detection provides support for call progress

monitoring. The detect or can a lso be user- programme d

to recognize up to 16 DTMF tones and two tone

detection bandpass filters.

DTMF tones may be dete cted and generated by using

the “ATA0” and “AT!0” c ommands described in the AT

command section. A description of the userprogrammable tones can be found in "Modem Result

Codes and Call Progress‚" on page 30.

PCM Data Mode

The Si2400 has the ability to bypass the modem

algorithm and send 14-bit PCM data, sampled at

9600 Hz, across the DAA. To use this mode, it is

necessary to set the serial link baud rate to at least

228613 bps (SE0), set PCM (S13.0) = 1, and set MCKR

(E1.7:6) = 0. The data format (Figure 9) requires that

the high byte be sent first contain ing bits D13–D7. The

LSB (B0) must e qual zero. The low by te must be sent

next containing bits D6–D0; the LSB (B0) must equal

one. The receive data format is the same.

In PCM data mode, the line can be answ ered using th e

“ATA;” command or a call can be origina ted using the

“A TDT#;” command. (The “;” is used to keep the modem

from leaving the command mode.) When PCM data

mode is enabled (set PCM (S13.0) = 1 and DRT

(SE4.5:4) = 0 (default)), data will immediately begin

streaming into and out of the serial port at a 9600 H z*2

word rate. In this mode, the controller will not detect dial

tones or other ca ll progress tones. If desi red, the user

can monitor these tones using manual call progress

detection prior to entering the PCM data mode.

To exit the PCM data mode, an escape must be

performed either by p ulsing the ES C pin or by using 9bit data mode and setting th e ninth bit. (TIES c annot b e

used in PCM data mode.) The escape command will

disable PCM streaming, and the controller will again

accept AT style commands.

Note: PCM data mode is the format that must also be used

when the Si2400 is configured to run as a voice codec

(DRT = 3).

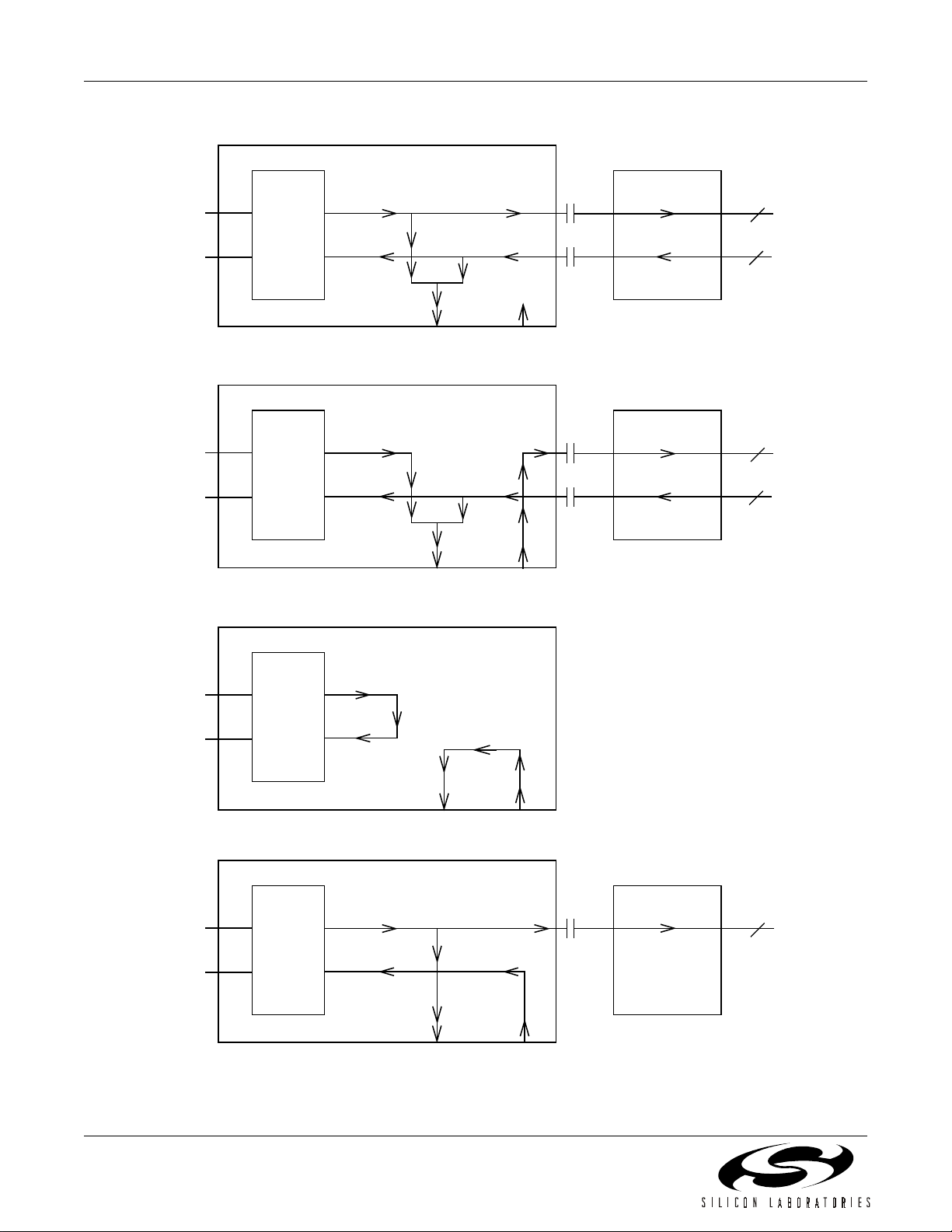

PCM Receive Timing

8-Bit Data

TXD

Start

D7 D8 D9 D10 D11 D12 D13 D0 D1 D2 D3 D4 D5 D6

B0

B1

B2 B3 B4 B5 B6 B7

High-Byte

Stop

Start

Low-Byte

B0

B1 B2 B3 B4 B5 B6 B7

PCM Transmit Timing

8-Bit Data

RXD

Start B1

Note: Baud rates (programmed through register SE0) can be set to the following: 228613, 245760, and 307200.

D7 D8 D9 D10 D11 D12 D13 D0 D1 D2 D3 D4 D5 D6

B0

High-Byte

B2 B3 B4 B5 B6 B7

Stop

Start

Low-Byte

B0

B1 B2 B3 B4 B5 B6 B7

Figure 9. PCM Timing

Stop

Stop

Rev. 0.95 19

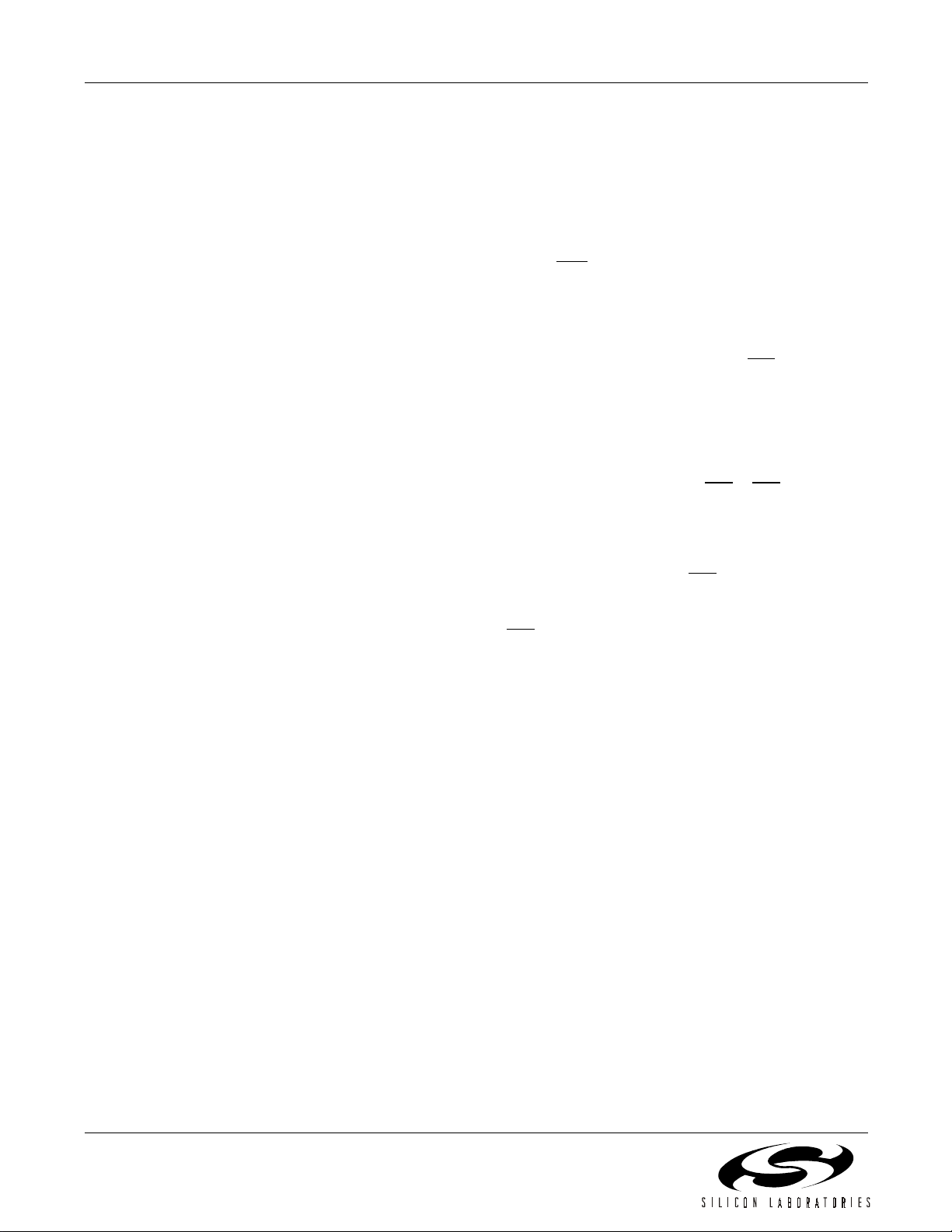

Si2400

A.

TX

RX

RXD

TXD

DSP

DSPOUT

DSPIN

Data Mode (DRT = 0)

Si2400

Si3015

RJ11

RJ11

B.

C.

TX

RX

TX

RX

RXD

TXD

RXD

TXD

DSP

DSPOUT

DSPIN

DSP

DSPOUT

DSPIN

AOUT

(Call Progress)

Voice Mode (DRT = 1)

Si2400

AIN

AOUT

(Voice Out)

(Voice In)

Loopback Mode (DRT = 2)

Si2400

AIN

Si3015

RJ11

RJ11

AIN

AOUT

Codec Mode (DRT = 3)

Si2400

DSP

RXD

TX

D.

20 Rev. 0.95

RX

TXD

DSPOUT

DSPIN

AIN

AOUT

(Voice Out)

Figure 10. Signal Routing

AIN

Si3015

RJ11

AIN

(Voice In)

Si2400

Analog Codec

The Si2400 features an on-chip, voice quality codec.

The codec consists of a digital to analog converter

(DAC) and an analog to digital converter (ADC). The

sample rate for the codec is set to 9.6 kHz. Wh en the

codec is powered on (s et register APO (SE 4.1)=1), the

output of the DAC is always present on the Si2400

AOUT pin. When the c ode c is po wer ed off (APO = 0), a

PWM output is present on the AOUT pin instead. In

order to use the ADC , one of the four GPIO pins must

be selected as an analog input ( AIN) by programming

the GPIO register (SE2).

Figure 10 shows the various signal routing modes for

the Si2400 voice codec, which are programmed through

register DRT (SE4.5:4). Figure 10A shows the data

routing for data mode. This is the default mode, which is

used for the modem data forma ts. In this configurat ion,

AOUT produces a mixed sum of the DSPOUT and

DSPIN signals and is typically used for call progress

monitoring through an external speaker. The relative

levels of the DSPOUT and DSPIN signals that are

output on the AOUT pin can be set through registers

ATL (SF4.1:0) and ARL (SF4.3:2).

Figure 10B shows the format for sending analog v oice

across the DAA to the PSTN. AIN is routed directly

across the DAA to the telephone line. In this

configuration, AOUT produces a mixed sum of the

DSPOUT and DSPIN signals . The relative levels of the

DSPOUT and DSPIN signals that are output on the

AOUT pin can be set through registers ATL (SF4.1:0)

and ARL (SF4.3:2). Note that the DSP may process

these signals if i t is not in PCM data mode. Thus, th e

DSP may be used in this configuration, for exam ple, to

decode DTMF tones. This is the mode used with the “!0”

and “A0” commands.

Figure 10C shows the loopback format, which can be

used for in-circuit t esting. A detailed description of the

in-circuit test modes is des cribed in the "Appendix A—

DAA Operation‚" on page 62.

Figure 10D shows the codec mode. This format is

useful, for example, in voice prompting, speaker

phones, or any systems involving digital signal

processing. In this mode, DSPOUT is routed to both the

AOUT pin and to the telephone li ne, and AIN is routed

directly to DSPIN.

Note that in all the DRT formats, the DSP must be in

PCM mode in order to pass DSPIN and DSPOUT

directly to and from TXD and RXD.

V.23 Operation/V.23 Reversing

The Si2400 supports full V.23 operation including the

V.23 reversing procedure. V.23 operation is enabled by

setting MF8 (S07) = xx10xx00 or xx01xx00. If V23R

(S07.5) = 1, then the Si2400 will transmit data at 75 bps

and receive data at either 600 or 1200 bps. If V23T

(S07.4) = 1, then the S i2400 will receive da ta at 75 bps

and transmit data at either 600 or 1200 bps. BAUD

(S07.2) is the 1200 or 600 bps ind icator. BAUD = 1 will

enable the 1200/600 V.23 channel to run at 1200 bps

while BAUD = 0 will enable 600 bps operation.

When a V.23 connection is successfully established, the

modem will respond with a “c” character if the

connection is made with the modem transmitting at

1200/600 bps and receivi ng at 75 bps. The m odem will

respond with a “v” character if a V.23 connection is

established with the modem transmitting at 75 bps and

receiving at 1200/600 bps.

The Si2400 supports a V.23 turnaround procedure. This

allows a modem th at is tran smitting at 75 bps to init iate

a “turnaround” procedure so that it can begin

transmitting data at 1200/600 bps an d receiv ing data a t

75 bps. The modem is define d as being in V.23 master

mode if it is transmi tting at 75 bps and it is defi ned as

being in slave mode if the modem is transmitting at

1200/600 bps. The f ollowi ng pa ra gr aph s gi ve a d etai le d

description of the V.23 turnaround procedure.

Modem in master mode

To perform a direct turnaround once a modem

connection is established, the host goes into onlinecommand-mode by sending an escape command

(Escape pin activation, TI ES, or ninth bit esc ape) to the

master modem. (Note that the host can initiate a

turnaround only if the Si2400 is the master.) The host

then sends the ATRO command to the Si2400 to initiate

a V.23 turnaround and to go bac k to the online (data)

mode.

The Si2400 will then change its carrier frequency (from

390 Hz to 1300 Hz), and wait for detecting a 390 Hz

carrier for 440 ms. If the modem detects more than

40 ms of a 390 Hz carrier into a time window of 440 ms,

it will echo the “c” response character. If the modem

does not detect more than 40 ms of a 390 Hz carrier

into a time window of 44 0 ms, it will hang up and ech o

the “N” (no carrier) character as a response

Modem in slave mode

The Si2400 performs a reverse turnaround when it

detects a carrier drop longer than 20 ms. The Si2400

then reverses (it changes its carrier from 1300 Hz to

390 Hz) and waits to detect a 1300 Hz carrier for

220 ms. If the Si2400 detects more than 40 ms of a

Rev. 0.95 21

Si2400

1300 Hz carrier in a time window of 22 0 ms, then it will

set the ALERT pin (GPIO4 must be configured as

ALERT) and the next charac ter echoed by the Si2400

will be a “v”.

If the Si2400 does not detect more than 40 ms of the

1300 Hz carrier in a time window of 220 ms, then it

reverses again and waits to detect a 3 90 Hz carrier for

220 ms. Then, if the Si2400 detec ts mo re than 40 ms of

a 390 Hz carrier in a time window of 220 ms, it will set

the ALERT pin and the next character echoed by the

Si2400 will be a “c”.

At this point, if the Si2400 does not detect more than

40 ms of the 390 Hz carrier in a time window of 220 ms,

then it will hang up, set the ALERT pin, and the next

character echoed by the Si2400 will be an “N” (no

carrier).

Successful completion of a turnaround procedure in

either master or slave will automatically update V23T

(S07.4) and V23R (S07 .5) to indicate the new statu s of

the V.23 connection.

In order to avoid using the ALERT pin, the host may

also be notified of t he ALERT condition by using 9-bit

data mode. Setting NB E (S15.0) = 1 a nd 9BF (C .3) = 0

will configure the ninth bit on the Si2400 TXD path to

function exactly as the ALERT pin has been described.

V.42 HDLC Mode

The Si2400 supports V.42 through HDLC framing in

hardware in all modem data modes. Frame packing and

unpacking, including opening and closing flag

generation and detection, CRC computation and

checking, zero inse rtion and deletio n, and modem data

transmission and reception are all performed by the

Si2400. V.42 error correction and data compression

must be performed by the host.

The digital link interface in this mode uses the same

UART interface (8-Bit Data and 9-Bit Data formats) as in

the asynchronou s modes and the nin th data bit may b e

used as an escape b y setting NBE (S15.0) = 1. When

using HDLC in 9-Bit Data mode, if the ninth bit is not

used as an escape, it is ignored.

To use the HDLC feature on the Si2400, the hos t must

first enable HDLC operation by setting HDEN

(S07.7) = 1. Next, the host may initiate the call or

answer the call using either the “ATDT#”, the “ATA”

command, or the auto- answer mode . (The auto -answer

mode is implemented by se tting register NR (S0) to a

non-zero value.) When the call is connected, a “c”, “ d”,

or a “v” is echoed to the host controller. The host may

now send/receive data across the UART using either

the 8-Bit Data or 9-Bit Data formats with flow control.

At this point, the Si24 00 will begin framing da ta into the

HDLC format. On the transmit side, if no data is

available from the host, the HDLC flag pattern is sent

repeatedly. When data is available, the Si2400

computes the CRC code throughout the frame and the

data is sent with the HDLC zero-bit insertion algorithm.

HDLC flow control operates in a similar manner to

normal asynchronous flow control across the UART and

is shown in Figure 11. In order to operate flow control

(using the CTS

pin to indicate when the Si2400 is ready

to accept a character), a higher serial link baud rate

than the transmission line rate should be selec ted. The

method of transmitting HDLC frames is as follows:

1. After the call is connected, the host should begin sending

the frame data to the Si2400, using the CTS

ensure data synchronicity. A 1-deep character FIFO is

implemented in the Si2400 to ensure that data is alway s

available to transmit.

2. When the frame is complete, the host should simply stop

sending data to th e Si240 0. As sho wn i n Figure11B, since

the Si2400 does not yet recognize the end-of-frame, it will

expect an extra byte and assert CTS

cause a host interrupt, then this final interrupt should be

ignored by the host.

3. When the Si2400 is ready to send the next byte, if it has

not yet received any data from the host, it will recognize

this as an end-of-frame, raise CTS

code, transmit the code, and begin transmitting stop flags.

4. After transmitting the first stop flag, the Si2400 will lower

CTS indicating that it is ready to receive the next frame

from the host. At this point the process repeats as in

step 1.

, calculate the final CRC

flow control to

. If CTS is used to

The method of receiving HDLC frames is as follows:

1. After the call is connected, the Si2400 searches for flag

data. Then, once the first non-flag word is detected, the

CRC is continuously computed, and the data is sent

across the UART (8-Bit Data or 9-Bit Data mode) to the

host after removing the HDLC zer o-bi t in sertio n. The baud

rate of the host must be at least as high as that of data

transmission. HDLC mode only works with 8-bit data

words; the ninth bit is used only for escape on RXD and

EOFR on TXD.

2. When the Si2400 detects the stop flag, it will send the last

data word in the frame as well as the two CRC bytes and

determine if the CRC checksum matches or not. Thus, the

last two bytes are not frame data, but are the CRC bytes,

which can be discarded b y the host. If the checksum

matches, then the Si2400 echoes “G” (good). If the

checksum does not match, the Si2400 echoes “e” (error).

Additionally, if the Si2400 detects an abort (seven or more

contiguous ones), then it will echo an “A”.

When the “G”, “e”, or “A” (referred to as a frame result

word) is sent, the Si2400 raises the EOFR (end of frame

receive) pin (see Figure 10B). The GPIO1 pin must be

configured as EOFR by setting GPE (SE4.3) = 1. In

addition to using the EOFR pin to indicate that the by te is a

22 Rev. 0.95

Si2400

frame result word, if in 9-bit data mode (se t NBE (S15.0) =

1), the ninth bit will be raised if the byte is a frame result

word. To program this mode, set 9BF (S0C.3) = 1 and ND

(SEO.3) = 1.

3. When the next frame of data is detec ted, EOFR is low ered

and the process repeats at step 1.

To summarize, the host will begin receiving data

asynchronously from the Si2400. When each byte is

received, the host sh ould check the EOFR pin (or the

ninth bit). If the pin (or the ninth bit) is low, then the data

is valid frame data. If the pin (or the ninth bit) is high,

then the data is a frame result word.

Fast Connect

In modem applications that require fast connection

times, it is possible to expedite the handshaking by

bypassing the answer tone. The No Answer Tone (NAT)

bit (S33.1) is intende d to provid e a method to decreas e

the time needed to complete modem handshaking. If

the NAT bit is set, the Si2400 will bypa ss transmi tting a

2100 Hz or 2225 Hz ans wer tone whe n recei ving a call .

Instead, the modem will immediately begin the

handshaking sequence that normally follows answer

tone transmission. For example, when the modem is

configured as a V.22 answering modem, activating the

NAT bit will cause the mod em to immediately transmit

unscrambled ones at 1200 bps after the modem

connects to the line. In addition, register UNL (S20) may

be used to set the length of time that the modem

transmits unscrambled ones. Setting UNL to a value

lower than the default may also shorten the answer

sequence.

When the modem is set up to originate a call, setting the

NAT bit causes the modem to bypass the normal

answer tone search . Instead, the modem will sen d the

transmit sequence t hat normally occurs after receiv ing

the answer tone within 20 ms of th e start of the answ er

tone. For example, when the m odem is config ured as a

V.22 originating modem, activating the NAT bit will

cause the modem to start transmi tting scrambled ones

at 1200 bps within 20 ms of the start of an answer tone.

When NAT=0, additional modem handshaking control

can be adjusted through registers TATL (S1E), ATTD

(S1F), UNL (S20), TSOD (S21), TSOL (S22), VDDL

(S23), VDDH (S24), SPTL (S25), VTSO (S26), VTSOL

(S27), VTSOH (S28), RSO (S2A), FCD (S2F), FCDH

(S30), RATL (S31), TASL (S34), and RSOL (S35).

These registers c an be esp ecially us eful if t he user has

control of both the originating and answer modems.

Clock Generation Subsystem

The Si2400 contai ns an on-chip cl ock generator. Using

a single master clock input, the Si2400 can genera te all

modem sample rates necessary to support V.22bis,

V.22/Bell212A, and V.21/Bell103 standards as well a s a

9.6 kHz rate for audio playback. Either a 4.9152 MHz

clock on XTALI or a 4.9152 MHz crystal ac ross XTALI

and XTALO form the master clock for the S i2400. This

clock source is sent to an internal phase-locked loop

(PLL) which generates all necessary internal system

clocks. The PLL has a settlin g time of ~1 ms. Data on

RXD should not be sent to the dev ice pri or to se ttling of

the PLL.

A CLKOUT pin exists whereby a 78.6 432 MHz /(N + 1)

clock is produced which may be used to clock a

microcontroller or other devices in the system. N may

be programmed via CLKD (SE1.4:0) to any value from 1

to 31, and N defaults to 7 on power-up. The clock may

be stopped by setting N = 0.

The MCKR (microc ontroller clock rate r egister SEI.7:6)

allows the user to co ntrol the m icrocontrol ler cloc k rate.

On powerup, the Si2400 UART baud rate is set to

2400 bps, given that the clock inp ut is 4.91 52 MH z. Th e

MCKR register conserves power via slower clocking of

the microcontroller for specific applications where

power conservation is required. Table 14 shows the

configurations for different values of MCKR.

Note that if MCKR = 0, then all of the serial interface link

rates will run at either half (MCKR = 1) or quarter

(MCKR = 2,3) speed.

Table 14. MCKR Configurations

MCKR Modes Working

0

(9.8304 MHz)

1

(4.9152 MHz)

2,3

(2.4576 MHz)

All modes

All modes except

PCM streaming

and V22bis

Command modes

only

Rev. 0.95 23

Loading...

Loading...