Datasheet C8051F310, C8051F311, C8051F312, C8051F313, C8051F314 Datasheet (Silicon Laboratories)

...Page 1

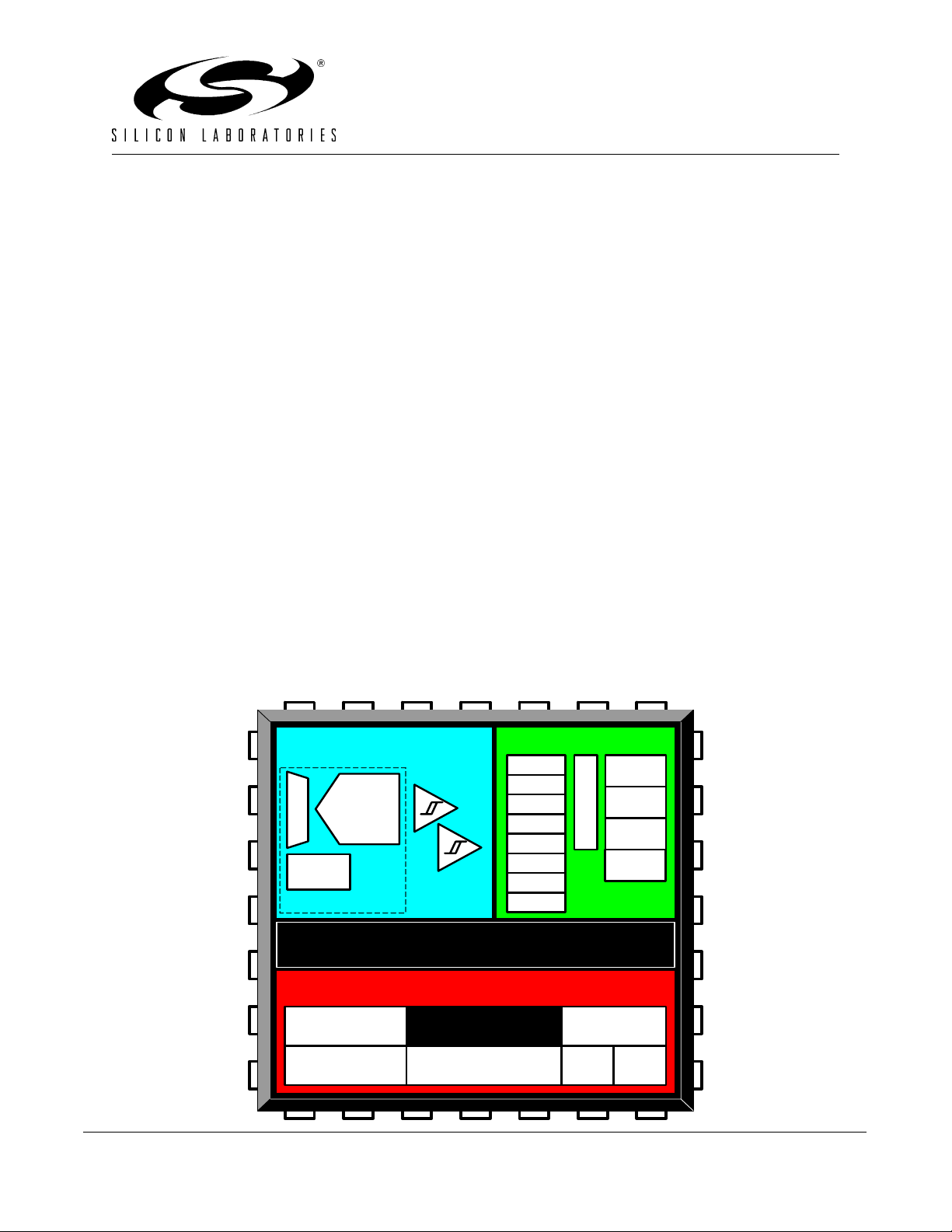

C8051F310/1/2/3/4/5/6/7

8/16 kB ISP Flash MCU Family

Analog Peripherals

- 10-Bit ADC (C8051F310/1/2/3/6 only)

• Up to 200 ksps

• Up to 21, 17, or 13 external single-ended or differen-

tial inputs

• VREF from external pin or V

• Built-in temperature sensor

• External conversion start input

DD

- Comparators

• Programmable hysteresis and response time

• Configurable as interrupt or reset source

(Comparator0)

• Low current (< 0.5 µA)

On-Chip Debug

- On-chip debug circuitry facilitates full speed,

non-intrusive in-system debug

(no emulator required)

- Provides breakpoints, single stepping,

inspect/modify memory and registers

- Superior performance to emulation systems using

ICE-Chips, target pods, and sockets

- Complete development kit

Supply Voltage 2.7 to 3.6 V

- Typical operating current: 5 mA at 25 MHz;

11 µA at 32 kHz

- Typical stop mode current: 0.1 µA

- Temperature range: –40 to +85 °C

High Speed 8051 µC Core

- Pipelined instruction architecture; executes 70% of

instructions in 1 or 2

system clocks

- Up to 25 MIPS throughput with 25 MHz clock

- Expanded int errupt hand ler

Memory

- 1280 bytes internal data RAM (1024 + 256)

-

16 kB (C8051F310/1/6/7) or 8 kB (C8051F312/3/4/5)

Flash; In-system programmable in 512-byte sectors

Digital Peripherals

- 29/25/21 Port I/O;

All 5 V tolerant with high sink current

- Hardware enhanced UART, SMBus™, and SPI™

serial ports

- Four general purpose 16-bit counter/timers

- 16-bit programmable counter array (PCA) with five

capture/compare modules

- Real time clock capability using PCA or timer and

external clock source

Clock Sources

- Internal oscillator: 24.5 MHz with ±2% accuracy

supports crystal-less UART operation

- External oscillator: Crystal, RC, C, or clock (1 or 2

pin modes)

- Can switch between clock sources on-the-fly; useful

in power saving modes

Packages

- 32-pin LQFP (C8051F310/2/4)

- 28-pin QFN (C8051F311/3/5)

- 24-pin QFN (C8051F316/7)

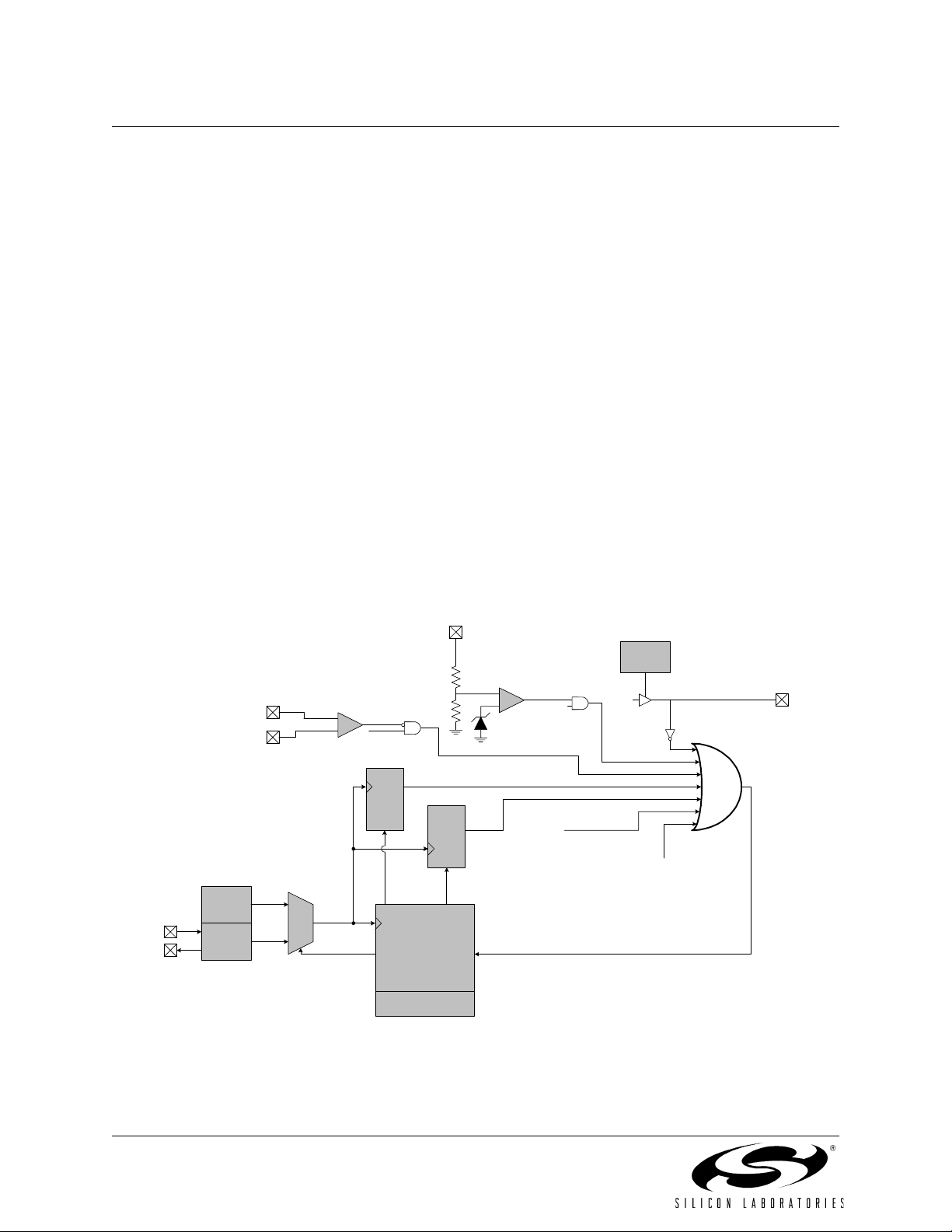

ANALOG

PERIPHERALS

A

M

U

X

TEMP

SENSOR

C8051F310/1/2/3/6 only

10-bit

200ksps

ADC

+

-

+

-

VOLTAGE

COMPARATORS

DIGITAL I/O

UART

SMBus

SPI

PCA

Timer 0

Timer 1

Timer 2

Timer 3

CROSSBAR

Port 0

Port 1

Port 2

Port 3

PROGRAMMABLE PRECISION INTERNAL

OSCILLATOR

HIGH-SPEED CONTROLLER CORE

16 kB/8 kB

ISP FLASH

14

INTERRUPTS

Rev. 1.7 8/06 Copyright © 2006 by Silicon Laboratories C8051F31x

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

8051 CPU

(25MIPS)

DEBUG

CIRCUITRY

1280 B

SRAM

POR

WDT

Page 2

C8051F310/1/2/3/4/5/6/7

NOTES:

2 Rev. 1.7

Page 3

C8051F310/1/2/3/4/5/6/7

Table Of Contents

1. System Overview.................................................................................................... 17

1.1. CIP-51™ Microcontroller Core.......................................................................... 27

1.1.1. Fully 8051 Compatible.............................................................................. 27

1.1.2. Improved Throughput............................................................................... 27

1.1.3. Additional Features......................... .... ................................. ..... ............... 28

1.2. On-Chip Memory............................................................................................... 29

1.3. On-Chip Debug Circuitry................................................................................... 30

1.4. Programmable Digital I/O and Crossbar........................................................... 31

1.5. Serial Ports ....................................................................................................... 32

1.6. Programmable Counter Array........................................................................... 32

1.7. 10-Bit Analog to Digital Converter..................................................................... 33

1.8. Comparators..................................................................................................... 34

2. Absolute Maximum Ratings .................................................................................. 35

3. Global DC Electrical Characteristics.................................................................... 36

4. Pinout and Package Definitions............................................................................ 39

5. 10-Bit ADC (ADC0, C8051F310/1/2/3/6 only) ........................................................ 51

5.1. Analog Multiplexer ............................................................................................ 51

5.2. Temperature Sensor......................................................................................... 52

5.3. Modes of Operation..........................................................................................54

5.3.1. Starting a Conversion............................................................................... 54

5.3.2. Tracking Modes........................................................................................ 55

5.3.3. Settling Time Requirements..................................................................... 56

5.4. Programmable Window Detector...................................................................... 61

5.4.1. Window Detector In Single-Ended Mode................................................. 63

5.4.2. Window Detector In Differential Mode...................................................... 64

6. Voltage Reference (C8051F310/1/2/3/6 only)........................................................ 67

7. Comparators........................................................................................................... 69

8. CIP-51 Microcontroller .......................................................................................... 79

8.1. Instruction Set................................................................................................... 80

8.1.1. Instruction and CPU Timing..................................................................... 80

8.1.2. MOVX Instruction and Program Memory ................................................. 81

8.2. Memory Organization................................................. ..... ................................. . 85

8.2.1. Program Memory...................................................................................... 85

8.2.2. Data Memory............................................................................................ 86

8.2.3. General Purpose Registers...................................................................... 86

8.2.4. Bit Addressable Locations........................................................................ 86

8.2.5. Stack ....................................................................................................... 86

8.2.6. Special Function Registers.............. .... ................................. ..... ............... 87

8.2.7. Register Descriptions............................................................................... 90

8.3. Interrupt Handler............................................................................................... 93

8.3.1. MCU Interrupt Sources and Vectors........................................................ 94

8.3.2. External Interrupts.................................................................................... 95

8.3.3. Interrupt Priorities..................................................................................... 95

Rev. 1.7 3

Page 4

C8051F310/1/2/3/4/5/6/7

8.3.4. Interrupt Latency...................................................................................... 95

8.3.5. Interrupt Register Descriptions................................................................. 97

8.4. Power Management Modes............................................................................ 102

8.4.1. Idle Mode................................................................................................ 102

8.4.2. Stop Mode.............................................................................................. 103

9. Reset Sources....................................................................................................... 105

9.1. Power-On Reset .......................................... ..... ..... ................................ ..... ....106

9.2. Power-Fail Reset / V

9.3. External Reset................................................................................................ 107

9.4. Missing Clock Detector Reset........................... ..... .... ..... ................................108

9.5. Comparator0 Reset......................................................................................... 108

9.6. PCA Watchdog Timer Reset...........................................................................108

9.7. Flash Error Reset............................................................................................ 108

9.8. Software Reset ............................................................................................... 108

10.Flash Memory ..................................................................................................... 111

10.1.Programming The Flash Memory................................................................... 111

10.1.1.Flash Lock and Key Functions............................................................... 111

10.1.2.Flash Erase Procedure.......................................................................... 111

10.1.3.Flash Write Procedure........................................................................... 112

10.2.Non-volatile Data Storage.............................................................................. 112

10.3.Security Options.............................................................................................113

10.4.Flash Write and Erase Guidelines.................................................................. 115

10.4.1.VDD Maintenance and the VDD Monitor ................................................. 115

10.4.2.PSWE Maintenance............................................................................... 115

10.4.3.System Clock.................................. .... ..... ................................. .... ......... 116

11.External RAM ........................................................................................................ 119

12.Oscillators............................................................................................................. 121

12.1.Programmable Internal Oscillator................................................................... 121

12.2.External Oscillator Drive Circuit......................................................................124

12.3.System Clock Selection.................................................................................. 124

12.4.External Crystal Example...................................... ................................ ..... ....126

12.5.External RC Example................................................................... ..... ............. 127

12.6.External Capacitor Example.................................. .... ................................. ....127

13.Port Input/Output .................................................. ..... .... ..... ................................ 129

13.1.Priority Crossbar Decoder.............................................................................. 131

13.2.Port I/O Initialization....................................................................................... 133

13.3.General Purpose Port I/O.......................................... ................................. ....135

14.SMBus ................................................................................................................... 145

14.1.Supporting Documents................................................................................... 146

14.2.SMBus Configuration...................................................................................... 146

14.3.SMBus Operation...........................................................................................146

14.3.1.Arbitration............................................................................................... 147

14.3.2.Clock Low Extension.............................................................................. 148

14.3.3.SCL Low Timeout................................................................................... 148

14.3.4.SCL High (SMBus Free) Timeout.......................................................... 148

Monitor...................................................................... 106

DD

4 Rev. 1.7

Page 5

C8051F310/1/2/3/4/5/6/7

14.4.Using the SMBus.............................................. ................................. .... ......... 149

14.4.1.SMBus Configuration Register............................... ..... ........................... 150

14.4.2.SMB0CN Control Register..................................................................... 153

14.4.3.Data Register.................................. .... ................................. ..... ............. 156

14.5.SMBus Transfer Modes.................................................................................. 157

14.5.1.Master Transmitter Mode....................................................................... 157

14.5.2.Master Receiver Mode........................................................................... 158

14.5.3.Slave Receiver Mode............................................................................. 159

14.5.4.Slave Transmitter Mode......................................................................... 160

14.6.SMBus Status Decoding................................................................................. 161

15.UART0.................................................................................................................... 163

15.1.Enhanced Baud Rate Generation................................................................... 164

15.2.Operational Modes............................. ..... ................................ ..... .................. 165

15.2.1.8-Bit UART............................................................................................. 165

15.2.2.9-Bit UART............................................................................................. 166

15.3.Multiprocessor Communications.................................................................... 167

16.Enhanced Serial Peripheral Interface (SPI0)...................................................... 173

16.1.Signal Descriptions......................................................................................... 174

16.1.1.Master Out, Slave In (MOSI).................................................................. 174

16.1.2.Master In, Slave Out (MISO).................................................................. 174

16.1.3.Serial Clock (SCK)................................................................................. 174

16.1.4.Slave Select (NSS)................................................................................ 174

16.2.SPI0 Master Mode Operation......................................................................... 175

16.3.SPI0 Slave Mode Operation...........................................................................177

16.4.SPI0 Interrupt Sources................................................................................... 177

16.5.Serial Clock Timing........................ ..... ................................. .... ....................... 178

16.6.SPI Special Function Registers...................................................................... 180

17. Timers ................................................................................................................... 187

17.1.Timer 0 and Timer 1.......................................................................................187

17.1.1.Mode 0: 13-bit Counter/Timer................................................................ 187

17.1.2.Mode 1: 16-bit Counter/Timer................................................................ 189

17.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload...................................... 189

17.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)................................. 190

17.2.Timer 2 .......................................................................................................... 195

17.2.1.16-bit Timer with Auto-Reload................................................................ 195

17.2.2.8-bit Timers with Auto-Reload................................................................196

17.3.Timer 3 .......................................................................................................... 199

17.3.1.16-bit Timer with Auto-Reload................................................................ 199

17.3.2.8-bit Timers with Auto-Reload................................................................200

18.Programmable Counter Array .............................. ..... .... ................................. .... 203

18.1.PCA Counter/Timer.......................................... ..... ................................ ..... ....204

18.2.Capture/Compare Modules............................................................................ 205

18.2.1.Edge-triggered Capture Mode................................................................ 206

18.2.2.Software Timer (Compare) Mode........................................................... 207

Rev. 1.7 5

Page 6

C8051F310/1/2/3/4/5/6/7

18.2.3.High-Speed Output Mode ...................................................................... 208

18.2.4.Frequency Output Mode................. .... ................................. ..... ............. 209

18.2.5.8-Bit Pulse Width Modulator Mode.........................................................210

18.2.6.16-Bit Pulse Width Modulator Mode....................................................... 211

18.3.Watchdog Timer Mode................................................................................... 212

18.3.1.Watchdog Timer Operation.................................................................... 212

18.3.2.Watchdog Timer Usage ......................................................................... 213

18.4.Register Descriptions for PCA........................................................................ 215

19.Revision Specific Behavior ................................................................................. 221

19.1.Revision Identification..................................................................................... 221

19.2.Reset Behavior............................................................................................... 221

19.2.1.Weak Pullups on GPIO Pins.................................................................. 221

19.2.2.VDD Monitor and the RST Pin..................................... .... ..... ..... ............. 221

19.3.PCA Counter........................ ..... .... ................................. ..... ........................... 222

20.C2 Interface.......................................... ..... ..... ................................ ..... .................. 223

20.1.C2 Interface Registers.................................................................................... 223

20.2.C2 Pin Sharing............................................................................................... 225

Document Change List............................................................................................. 226

Contact Information.................................................................................................. 228

6 Rev. 1.7

Page 7

C8051F310/1/2/3/4/5/6/7

List of Figures

1. System Overview

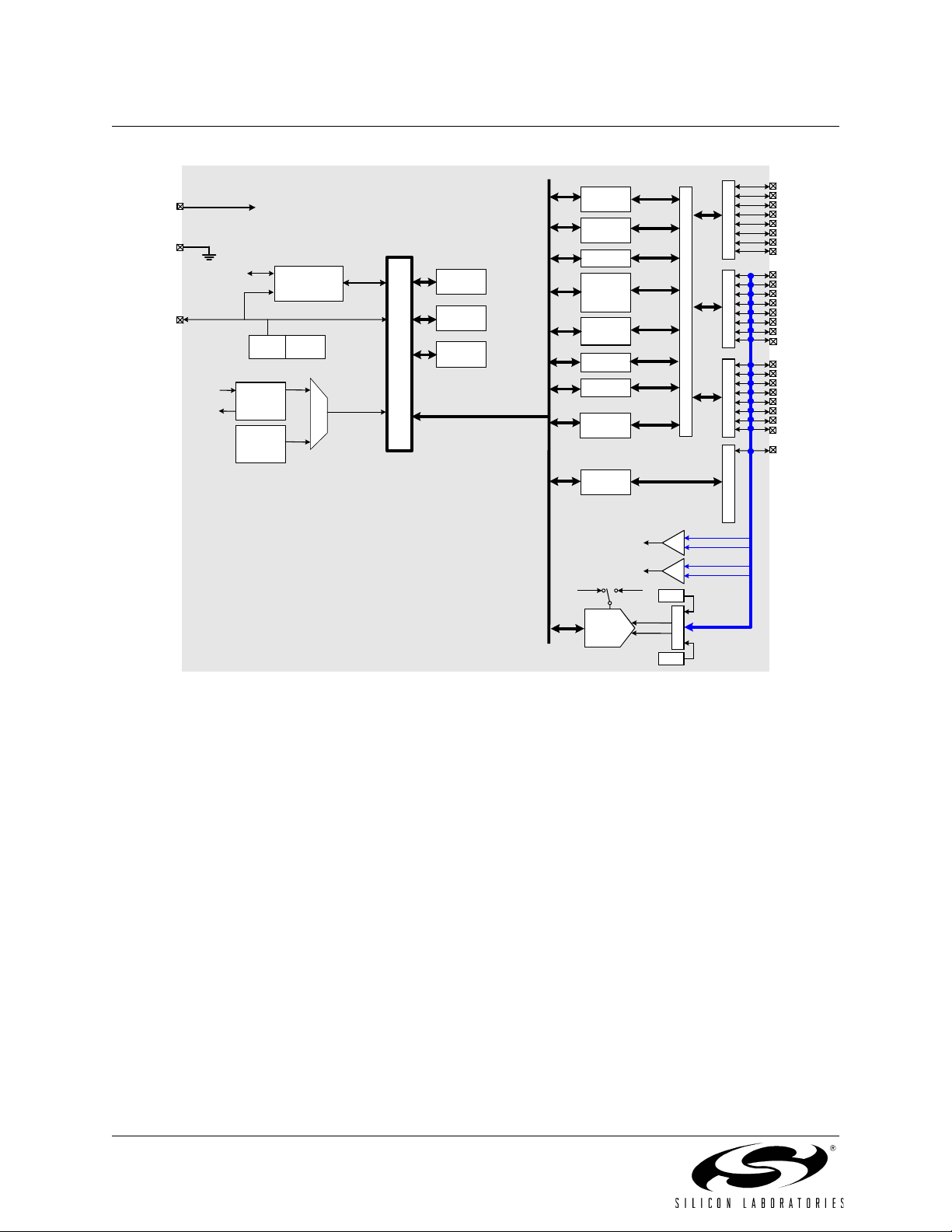

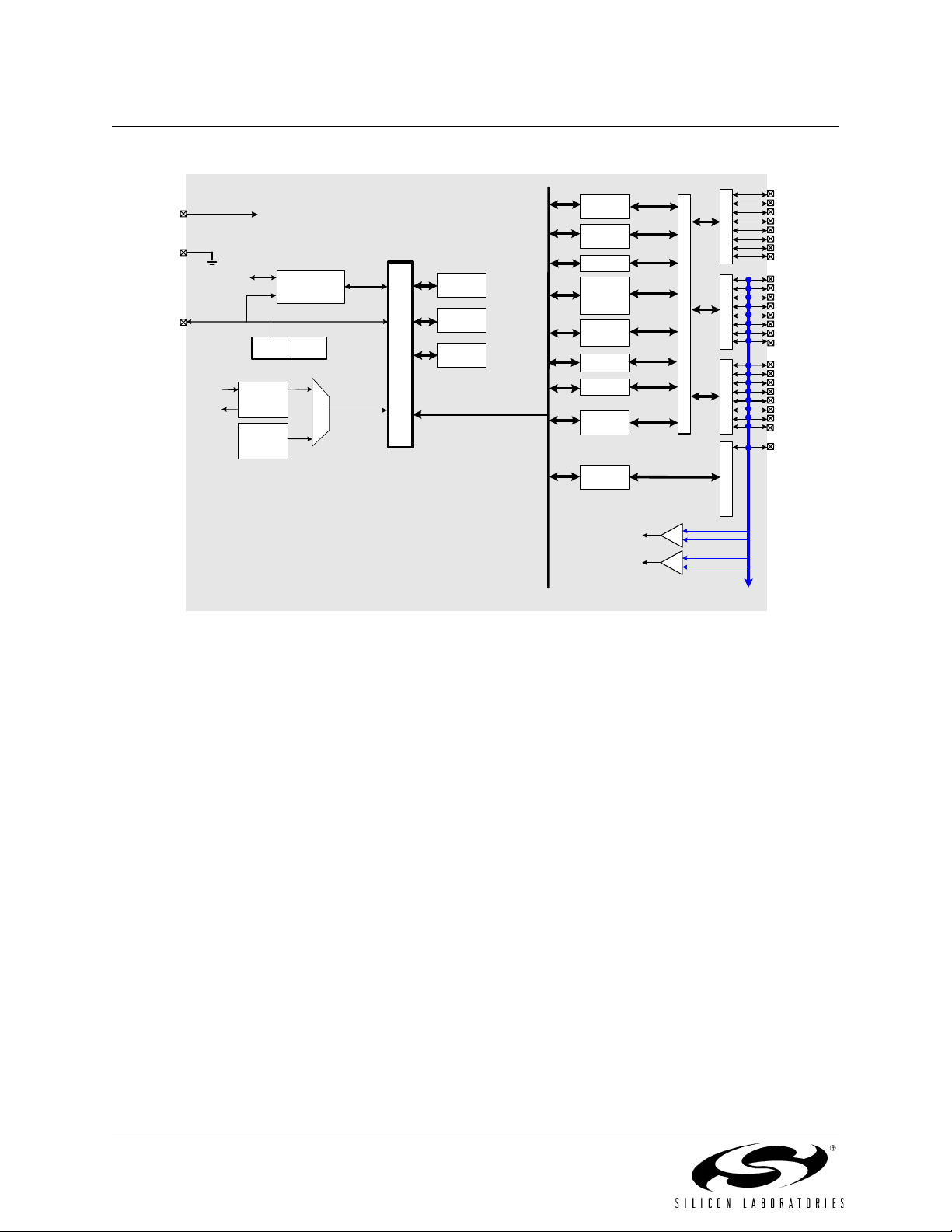

Figure 1.1. C8051F310 Block Diagram.................................................................... 19

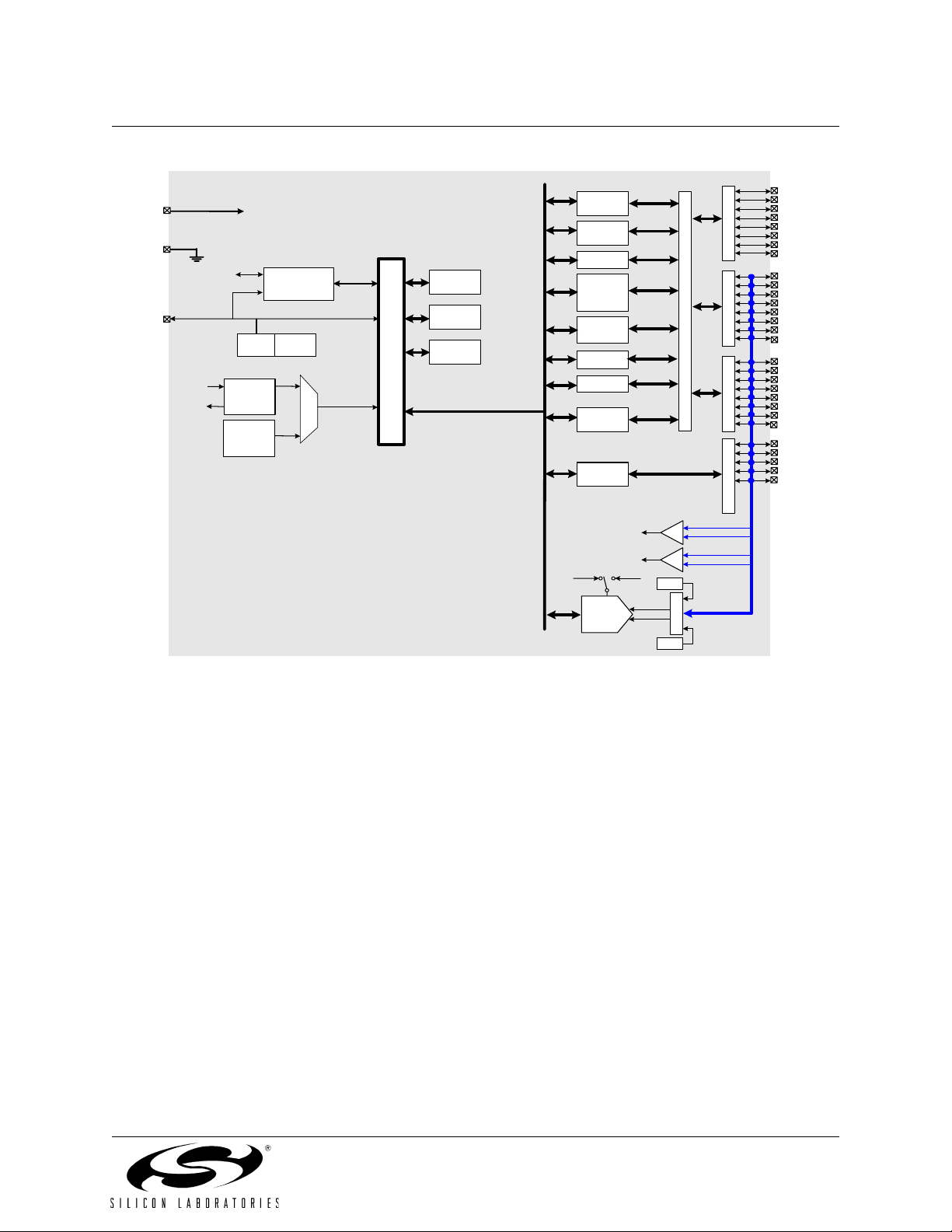

Figure 1.2. C8051F311 Block Diagram.................................................................... 20

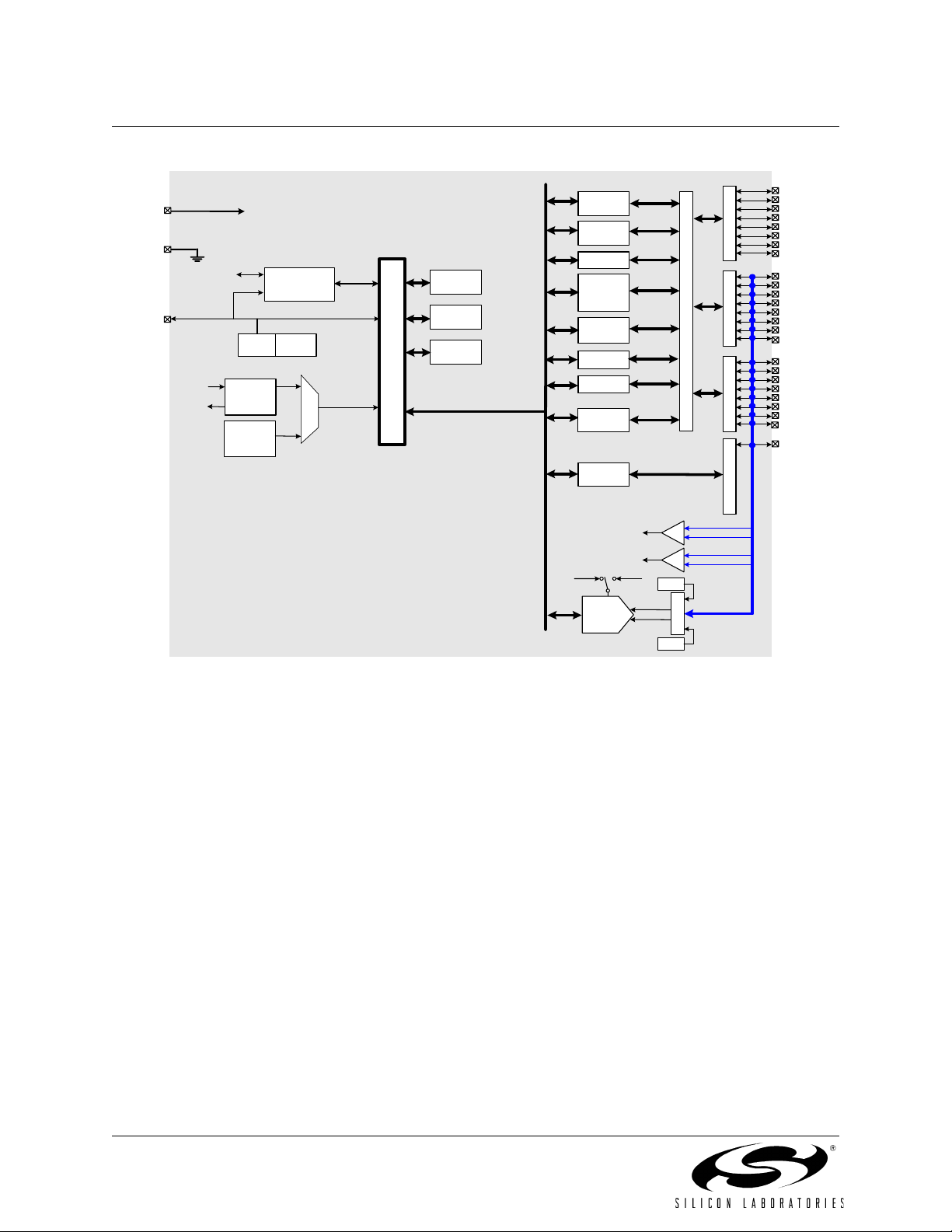

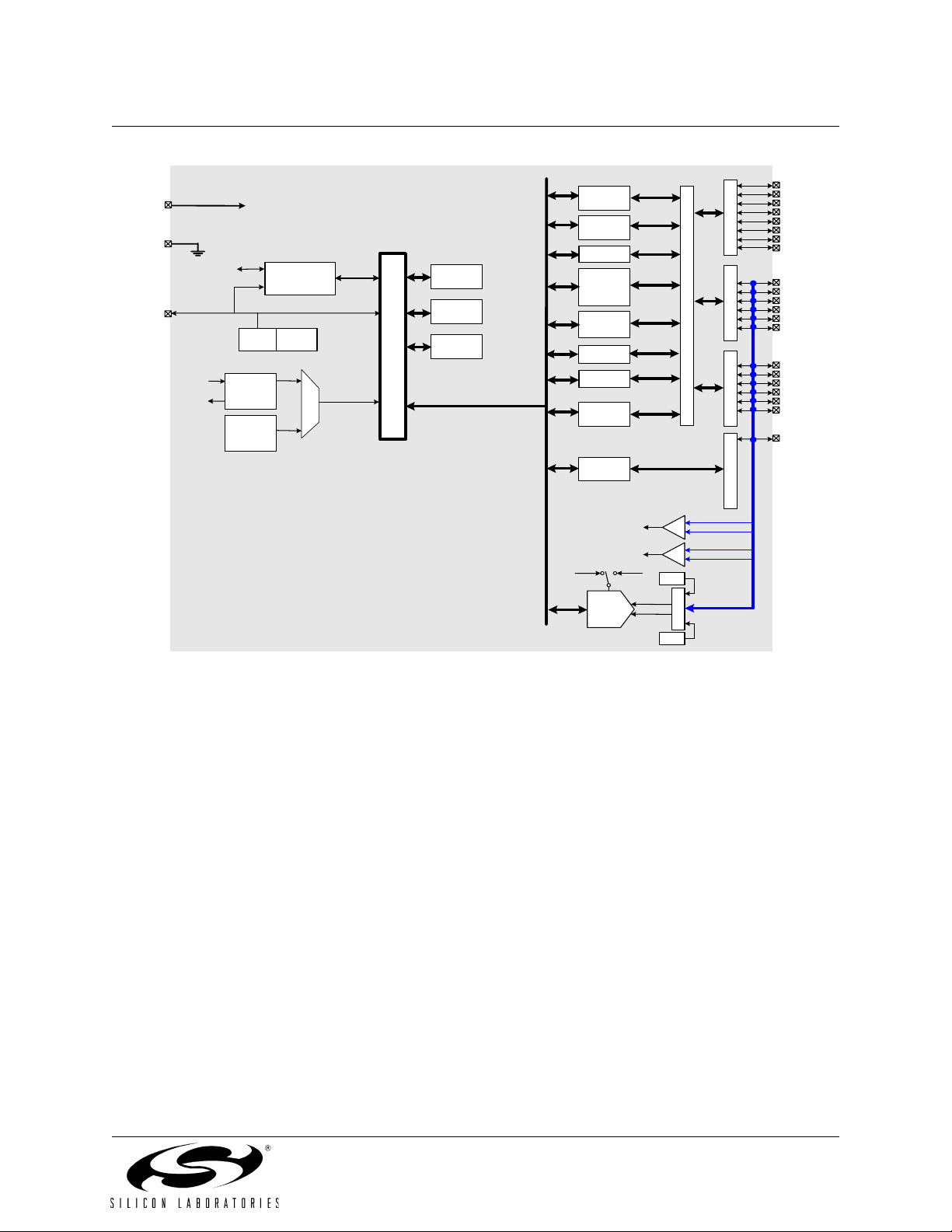

Figure 1.3. C8051F312 Block Diagram.................................................................... 21

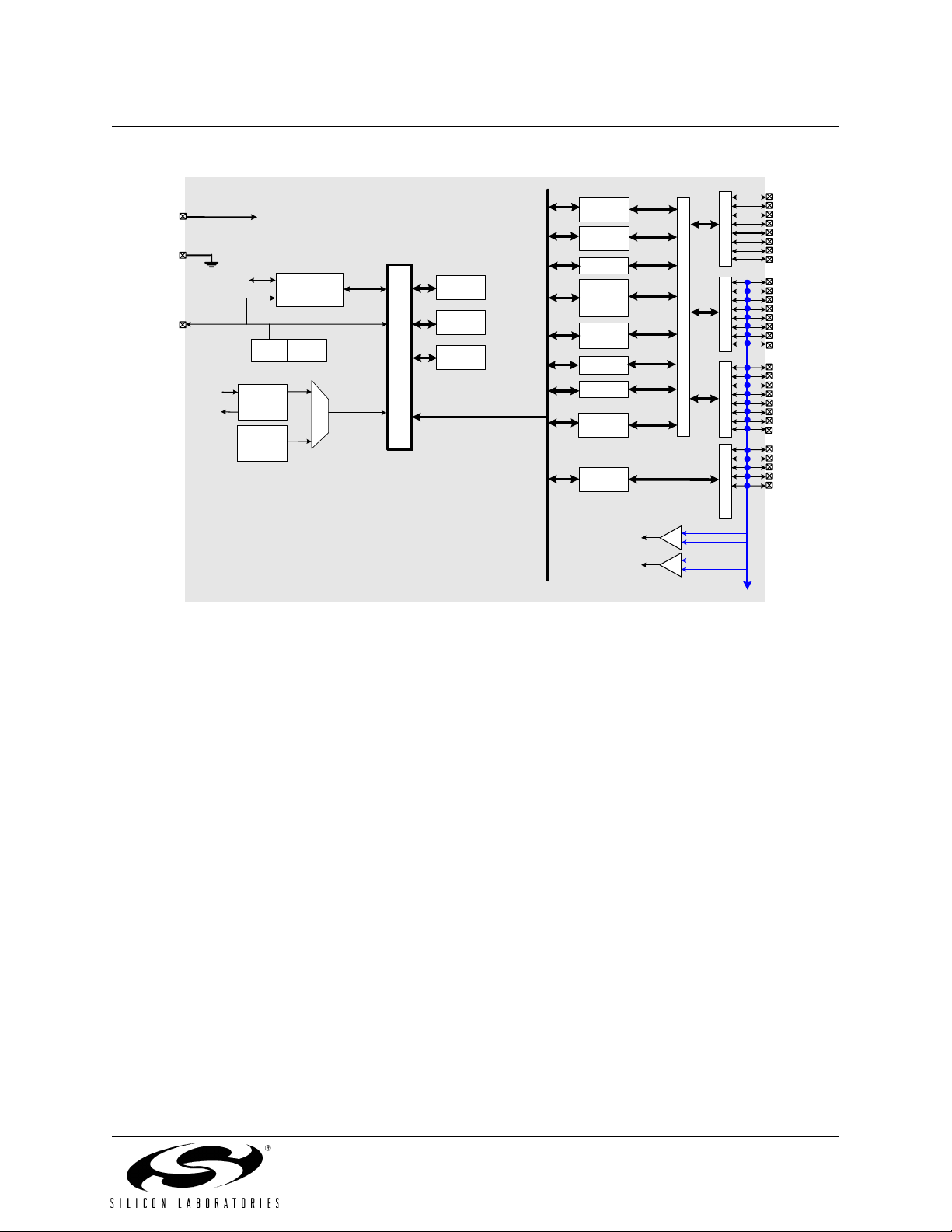

Figure 1.4. C8051F313 Block Diagram.................................................................... 22

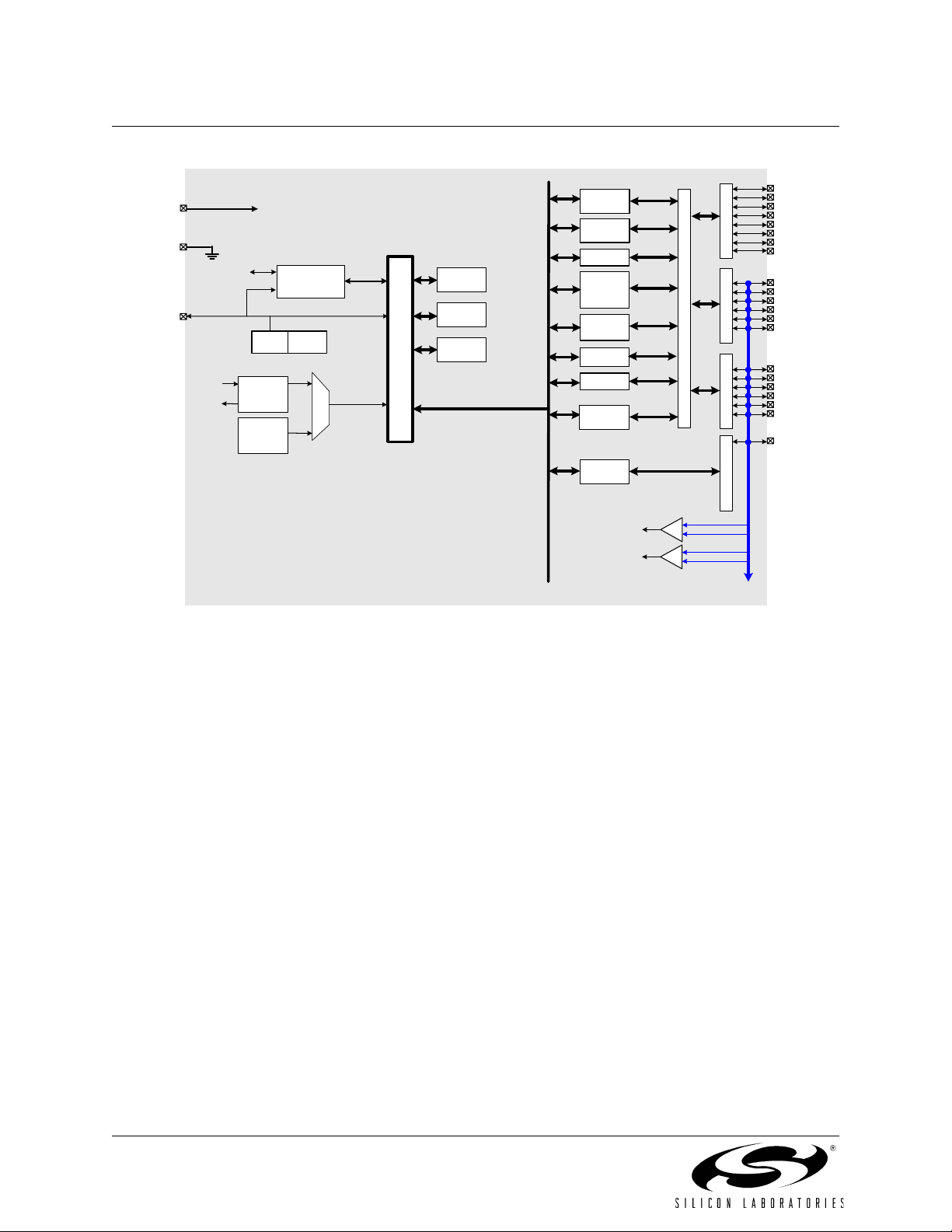

Figure 1.5. C8051F314 Block Diagram.................................................................... 23

Figure 1.6. C8051F315 Block Diagram.................................................................... 24

Figure 1.7. C8051F316 Block Diagram.................................................................... 25

Figure 1.8. C8051F317 Block Diagram.................................................................... 26

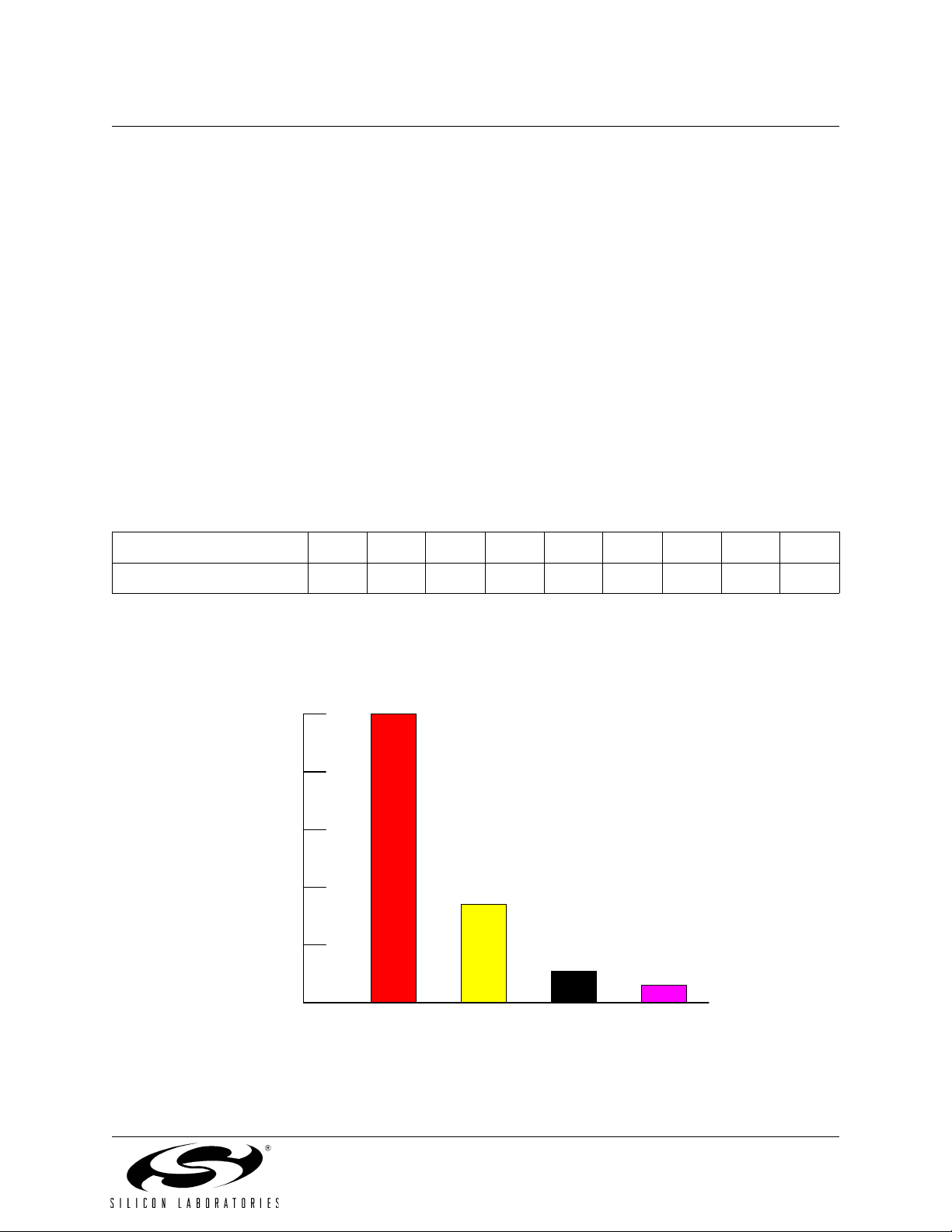

Figure 1.9. Comparison of Peak MCU Execution Speeds ............................ ..... ..... .27

Figure 1.10. On-Chip Clock and Reset..................................................................... 28

Figure 1.11. On-Board Memory Map........................................................................ 29

Figure 1.12. Development/In-System Debug Diagram............................................. 30

Figure 1.13. Digital Crossbar Diagram..................................................................... 31

Figure 1.14. PCA Block Diagram.............................................................................. 32

Figure 1.15. 10-Bit ADC Block Diagram................................................................... 33

Figure 1.16. Comparator0 Block Diagram................................................................ 34

2. Absolute Maximum Ratings

3. Global DC Electrical Characteristics

4. Pinout and Package Definitions

Figure 4.1. LQFP-32 Pinout Diagram (Top View) .................................................... 41

Figure 4.2. LQFP-32 Package Diagram................................................................... 42

Figure 4.3. QFN-28 Pinout Diagram (Top View)...................................................... 43

Figure 4.4. QFN-28 Package Drawing..................................................................... 44

Figure 4.5. Typical QFN-28 Landing Diagram.......................................................... 45

Figure 4.6. QFN-28 Solder Paste Recommendation................................................ 46

Figure 4.7. QFN-24 Pinout Diagram (Top View)...................................................... 47

Figure 4.8. QFN-24 Package Drawing..................................................................... 48

Figure 4.9. Typical QFN-24 Landing Diagram.......................................................... 49

Figure 4.10. QFN-24 Solder Paste Recommendation.............................................. 50

5. 10-Bit ADC (ADC0, C8051F310/1/2/3 /6 only)

Figure 5.1. ADC0 Functional Block Diagram............................................................ 51

Figure 5.2. Typical Temperature Sensor Transfer Function..................................... 52

Figure 5.3. Temperature Sensor Error with 1-Point Calibration............................... 53

Figure 5.4. 10-Bit ADC Track and Conversion Example Timing.............................. 55

Figure 5.5. ADC0 Equivalent Input Circuits .............................................................. 56

Figure 5.6. ADC Window Compare Example: Right-Justified Single-Ended Data... 63

Figure 5.7. ADC Window Compare Example: Left-Justified Single-Ended Data ..... 63

Figure 5.8. ADC Window Compare Example: Right-Justified Differential Data....... 64

Figure 5.9. ADC Window Compare Example: Left-Justified Differential Data.......... 64

6. Voltage Reference (C8051F310/1/2/3/6 only)

Figure 6.1. Voltage Reference Functional Block Diagram....................................... 67

Rev. 1.7 7

Page 8

C8051F310/1/2/3/4/5/6/7

7. Comparators

Figure 7.1. Comparator0 Functional Block Diagram................................................ 69

Figure 7.2. Comparator1 Functional Block Diagram................................................ 70

Figure 7.3. Comparator Hysteresis Plot................................................................... 71

8. CIP-51 Microcontroller

Figure 8.1. CIP-51 Block Diagram............................................................................ 79

Figure 8.2. Memory Map.......................................................................................... 85

9. Reset Sources

Figure 9.1. Reset Sources...................................................................................... 105

Figure 9.2. Power-On and VDD Monitor Reset Timing........................................... 106

10.Flash Memory

Figure 10.1. Flash Program Memory Map.............................................................. 113

11.External RAM

12.Oscillators

Figure 12.1. Oscillator Diagram.............................................................................. 121

Figure 12.2. 32.768 kHz External Crystal Example................................................ 126

13.Port Input/Output

Figure 13.1. Port I/O Functional Block Diagram..................................................... 129

Figure 13.2. Port I/O Cell Block Diagram............................................................... 130

Figure 13.3. Crossbar Priority Decoder with No Pins Skipped............................... 131

Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped ........................ 132

14.SMBus

Figure 14.1. SMBus Block Diagram....................................................................... 145

Figure 14.2. Typical SMBus Configuration............................................................. 146

Figure 14.3. SMBus Transaction............................................................................ 147

Figure 14.4. Typical SMBus SCL Generation......................................................... 151

Figure 14.5. Typical Master Transmitter Sequence................................................ 157

Figure 14.6. Typical Master Receiver Sequence.................................................... 158

Figure 14.7. Typical Slave Receiver Sequence...................................................... 159

Figure 14.8. Typical Slave Transmitter Sequence.................................................. 160

15.UART0

Figure 15.1. UART0 Block Diagram....................................................................... 163

Figure 15.2. UART0 Baud Rate Logic............................................. ..... .................. 164

Figure 15.3. UART Interconnect Diagram.............................................................. 165

Figure 15.4. 8-Bit UART Timing Diagram...............................................................165

Figure 15.5. 9-Bit UART Timing Diagram...............................................................166

Figure 15.6. UART Multi-Processor Mode Interconnect Diagram.......................... 167

16.Enhanced Seria l Peripheral Inte rface (SPI0)

Figure 16.1. SPI Block Diagram............................................................................. 173

Figure 16.2. Multiple-Master Mode Connection Diagram....................................... 176

Figure 16.3. 3-Wire Single Master and Slave Mode Connection Diagram............. 176

Figure 16.4. 4-Wire Single Master and Slave Mode Connection Diagram............. 176

Figure 16.5. Master Mode Data/Clock Timing........................................................ 178

Figure 16.6. Slave Mode Data/Clock Timing (CKPHA = 0).................................... 179

Figure 16.7. Slave Mode Data/Clock Timing (CKPHA = 1).................................... 179

8 Rev. 1.7

Page 9

C8051F310/1/2/3/4/5/6/7

Figure 16.8. SPI Master Timing (CKPHA = 0)........................................................ 183

Figure 16.9. SPI Master Timing (CKPHA = 1)........................................................ 183

Figure 16.10. SPI Slave Timing (CKPHA = 0)........................................................ 184

Figure 16.11. SPI Slave Timing (CKPHA = 1)........................................................ 184

17.Timers

Figure 17.1. T0 Mode 0 Block Diagram.................................................................. 188

Figure 17.2. T0 Mode 2 Block Diagram.................................................................. 189

Figure 17.3. T0 Mode 3 Block Diagram.................................................................. 190

Figure 17.4. Timer 2 16-Bit Mode Block Diagram .................................................. 195

Figure 17.5. Timer 2 8-Bit Mode Block Diagram .................................................... 196

Figure 17.6. Timer 3 16-Bit Mode Block Diagram .................................................. 199

Figure 17.7. Timer 3 8-Bit Mode Block Diagram .................................................... 200

18.Programmable Counter Array

Figure 18.1. PCA Block Diagram............................................................................ 203

Figure 18.2. PCA Counter/Timer Block Diagram.................................................... 204

Figure 18.3. PCA Interrupt Block Diagram............................................................. 205

Figure 18.4. PCA Capture Mode Diagram.............................................................. 206

Figure 18.5. PCA Software Timer Mode Diagram..................................................207

Figure 18.6. PCA High Speed Output Mode Diagram............................................208

Figure 18.7. PCA Frequency Output Mode............................................................ 209

Figure 18.8. PCA 8-Bit PWM Mode Diagram......................................................... 210

Figure 18.9. PCA 16-Bit PWM Mode...................................................................... 211

Figure 18.10. PCA Module 4 with Watchdog Timer Enabled................................. 212

19.Revision Specific Behavior

Figure 19.1. Reading Package Marking................................................................. 221

20.C2 Interface

Figure 20.1. Typical C2 Pin Sharing....................................................................... 225

Rev. 1.7 9

Page 10

C8051F310/1/2/3/4/5/6/7

NOTES:

10 Rev. 1.7

Page 11

C8051F310/1/2/3/4/5/6/7

List of Tables

1. System Overview

Table 1.1. Product Selection Guide ......................................................................... 18

2. Absolute Maximum Ratings

Table 2.1. Absolute Maximum Ratings .................................................................... 35

3. Global DC Electrical Characteristics

Table 3.1. Global DC Electrical Characteristics ....................................................... 36

Table 3.2. Electrical Characteristics Quick Reference ............................................ 38

4. Pinout and Package Definitions

Table 4.1. Pin Definitions for the C8051F31x .......................................................... 39

Table 4.2. LQFP-32 Package Dimensions .............................................................. 42

Table 4.3. QFN-28 Package Dimensions ................................................................ 44

Table 4.4. QFN-24 Package Dimensions ................................................................ 48

5. 10-Bit ADC (ADC0, C8051F310/1/2/3 /6 only)

Table 5.1. ADC0 Electrical Characteristics .............................................................. 65

6. Voltage Reference (C8051F310/1/2/3/6 only)

Table 6.1. External Voltage Reference Circuit Electrical Characteristics ................ 68

7. Comparators

Table 7.1. Comparator Electrical Characteristics .................................................... 78

8. CIP-51 Microcontroller

Table 8.1. CIP-51 Instruction Set Summary ............................................................ 81

Table 8.2. Special Function Register (SFR) Memory Map ...................................... 87

Table 8.3. Special Function Registers ..................................................................... 88

Table 8.4. Interrupt Summary .................................................................................. 96

9. Reset Sources

Table 9.1. Reset Electrical Characteristics ............................................................110

10.Flash Memory

Table 10.1. Flash Electrical Characteristics .......................................................... 112

Table 10.2. Flash Security Summary .................................................................... 114

11.External RAM

12.Oscillators

Table 12.1. Internal Oscillator Electrical Characteristics ....................................... 123

13.Port Input/Output

Table 13.1. Port I/O DC Electrical Characteristics ................................................ 143

14.SMBus

Table 14.1. SMBus Clock Source Selection .......................................................... 150

Table 14.2. Minimum SDA Setup and Hold Times ................................................ 151

Table 14.3. Sources for Hardware Changes to SMB0CN .....................................155

Table 14.4. SMBus Status Decoding ..................................................................... 161

Rev. 1.7 11

Page 12

C8051F310/1/2/3/4/5/6/7

15.UART0

Table 15.1. Timer Settings for Standard Baud Rate s

Using the Internal Oscillator ...............................................................170

Table 15.2. Timer Settings for Standard Baud Rate s

Using an External 25 MHz Oscillator ......................................... ......... 170

Table 15.3. Timer Settings for Standard Baud Rate s

Using an External 22.1184 MHz Oscillator ......................................... 171

Table 15.4. Timer Settings for Standard Baud Rate s

Using an External 18.432 MHz Oscillator ...........................................171

Table 15.5. Timer Settings for Standard Baud Rate s

Using an External 11.0592 MHz Oscillator ......................................... 172

Table 15.6. Timer Settings for Standard Baud Rate s

Using an External 3.6864 MHz Oscillator ........................................... 172

16.Enhanced Seria l Peripheral Inte rface (SPI0)

Table 16.1. SPI Slave Timing Parameters ............................................................ 185

17.Timers

18.Programmable Counter Array

Table 18.1. PCA Timebase Input Options ............................................................. 204

Table 18.2. PCA0CPM Register Settings for PCA Capture/Compare Modules .... 205

Table 18.3. Watchdog Timer Timeout Intervals

19.Revision Specific Behavior

20.C2 Interface

..................................................... 214

12 Rev. 1.7

Page 13

C8051F310/1/2/3/4/5/6/7

List of Registers

SFR Definition 5.1. AMX0P: AMUX0 Positive Channel Select . . . . . . . . . . . . . . . . . . . 57

SFR Definition 5.2. AM X0 N: AMUX0 Negative Channel Select . . . . . . . . . . . . . . . . . . 58

SFR Definition 5.3. ADC0CF: ADC0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

SFR Definition 5.4. ADC0H: ADC0 Data Word MSB . . . . . . . . . . . . . . . . . . . . . . . . . . 59

SFR Definition 5.5. ADC0L: ADC0 Data Word LSB . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

SFR Definition 5.6. ADC0CN: ADC0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

SFR Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte . . . . . . . . . . . . . 61

SFR Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte . . . . . . . . . . . . . . 61

SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte . . . . . . . . . . . . . . . . 62

SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte . . . . . . . . . . . . . . . . 62

SFR Definition 6.1. REF0CN: Reference Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

SFR Definition 7.1. CPT0CN: Comparator0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

SFR Definition 7.2. CPT0MX: Comparator0 MUX Selection . . . . . . . . . . . . . . . . . . . . 73

SFR Definition 7.3. CPT0MD: Comparator0 Mode Selection . . . . . . . . . . . . . . . . . . . . 74

SFR Definition 7.4. CPT1CN: Comparator1 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

SFR Definition 7.5. CPT1MX: Comparator1 MUX Selection . . . . . . . . . . . . . . . . . . . . 76

SFR Definition 7.6. CPT1MD: Comparator1 Mode Selection . . . . . . . . . . . . . . . . . . . . 77

SFR Definition 8.1. DPL: Data Pointer Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

SFR Definition 8.2. DPH: Data Pointer High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

SFR Definition 8.3. SP: Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

SFR Definition 8.4. PSW: Program Status Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

SFR Definition 8.5. ACC: Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

SFR Definition 8.6. B: B Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

SFR Definition 8.7. IE: Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

SFR Definition 8.8. IP: Interrupt Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

SFR Definition 8.9. EIE1: Extended Interrupt Enable 1 . . . . . . . . . . . . . . . . . . . . . . . . 99

SFR Definition 8.10. EIP1: Extended Interrupt Priority 1 . . . . . . . . . . . . . . . . . . . . . . 100

SFR Definition 8.11. IT01CF: INT0/INT1 Configuration . . . . . . . . . . . . . . . . . . . . . . . 101

SFR Definition 8.12. PCON: Power Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

SFR Definition 9.1. VDM0CN: V

SFR Definition 9.2. RSTSRC: Reset Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

SFR Definition 10.1. PSCTL: Program Store R/W Control . . . . . . . . . . . . . . . . . . . . . 116

SFR Definition 10.2. FLKEY: Flash Lock and Key . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

SFR Definition 10.3. FLSCL: Flash Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

SFR Definition 11.1. EMI0CN: External Memory Interface Control . . . . . . . . . . . . . . 119

SFR Definition 12.1. OSCICL: Internal Oscillator Calibration . . . . . . . . . . . . . . . . . . . 122

SFR Definition 12.2. OSCICN: Internal Oscillator Control . . . . . . . . . . . . . . . . . . . . . 122

SFR Definition 12.3. CLKSEL: Clock Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

SFR Definition 12.4. OSCXCN: External Oscillator Control . . . . . . . . . . . . . . . . . . . . 125

SFR Definition 13.1. XBR0: Port I/O Crossbar Register 0 . . . . . . . . . . . . . . . . . . . . . 134

SFR Definition 13.2. XBR1: Port I/O Crossbar Register 1 . . . . . . . . . . . . . . . . . . . . . 135

SFR Definition 13.3. P0: Port0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

SFR Definition 13.4. P0MDIN: Port0 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Monitor Control . . . . . . . . . . . . . . . . . . . . . . . . . . 107

DD

Rev. 1.7 13

Page 14

C8051F310/1/2/3/4/5/6/7

SFR Definition 13.5. P0MDOUT: Port0 Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . 137

SFR Definition 13.6. P0SKIP: Port0 Skip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

SFR Definition 13.7. P1: Port1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

SFR Definition 13.8. P1MDIN: Port1 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

SFR Definition 13.9. P1MDOUT: Port1 Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . 139

SFR Definition 13.10. P1SKIP: Port1 Skip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

SFR Definition 13.11. P2: Port2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

SFR Definition 13.12. P2MDIN: Port2 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

SFR Definition 13.13. P2MDOUT: Port2 Output Mode . . . . . . . . . . . . . . . . . . . . . . . . 141

SFR Definition 13.14. P2SKIP: Port2 Skip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

SFR Definition 13.15. P3: Port3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

SFR Definition 13.16. P3MDIN: Port3 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

SFR Definition 13.17. P3MDOUT: Port3 Output Mode . . . . . . . . . . . . . . . . . . . . . . . . 143

SFR Definition 14.1. SMB0CF: SMBus Clock/Configuration . . . . . . . . . . . . . . . . . . . 152

SFR Definition 14.2. SMB0CN: SMBus Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

SFR Definition 14.3. SMB0DAT: SMBus Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156

SFR Definition 15.1. SCON0: Serial Port 0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . 168

SFR Definition 15.2. SBUF0: Serial (UART0) Port Data Buffer . . . . . . . . . . . . . . . . . 169

SFR Definition 16.1. SPI0CFG: SPI0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 180

SFR Definition 16.2. SPI0CN: SPI0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

SFR Definition 16.3. SPI0CKR: SPI0 Clock Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

SFR Definition 16.4. SPI0DAT: SPI0 Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

SFR Definition 17.1. TCON: Timer Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

SFR Definition 17.2. TMOD: Timer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192

SFR Definition 17.3. CKCON: Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

SFR Definition 17.4. TL0: Timer 0 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

SFR Definition 17.5. TL1: Timer 1 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

SFR Definition 17.6. TH0: Timer 0 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

SFR Definition 17.7. TH1: Timer 1 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

SFR Definition 17.8. TMR2CN: Timer 2 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . .197

SFR Definition 17.9. TMR2RLL: Timer 2 Reload Register Low Byte . . . . . . . . . . . . . 198

SFR Definition 17.10. TMR2RLH: Timer 2 Reload Register High Byte . . . . . . . . . . . 198

SFR Definition 17.11. TMR2L: Timer 2 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

SFR Definition 17.12. TMR2H Timer 2 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

SFR Definition 17.13. TMR3CN: Timer 3 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

SFR Definition 17.14. TMR3RLL: Timer 3 Reload Register Low Byte . . . . . . . . . . . . 202

SFR Definition 17.15. TMR3RLH: Timer 3 Reload Register High Byte . . . . . . . . . . . 202

SFR Definition 17.16. TMR3L: Timer 3 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

SFR Definition 17.17. TMR3H Timer 3 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

SFR Definition 18.1. PCA0CN: PCA Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

SFR Definition 18.2. PCA0MD: PCA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

SFR Definition 18.3. PCA0CPMn: PCA Capture/Compare Mode Registers . . . . . . .217

SFR Definition 18.4. PCA0L: PCA Counter/Timer Low Byte . . . . . . . . . . . . . . . . . . . 218

SFR Definition 18.5. PCA0H: PCA Counter/Timer High Byte . . . . . . . . . . . . . . . . . . .218

SFR Definition 18.6. PCA0CPLn: PCA Capture Module Low Byte . . . . . . . . . . . . . . . 218

14 Rev. 1.7

Page 15

C8051F310/1/2/3/4/5/6/7

SFR Definition 18.7. PCA0CPHn: PCA Capture Module High Byte . . . . . . . . . . . . . . 219

C2 Register Definition 20.1. C2ADD: C2 Address . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

C2 Register Definition 20.2. DEVICEID: C2 Device ID . . . . . . . . . . . . . . . . . . . . . . . . 223

C2 Register Definition 20.3. REVID: C2 Revision ID . . . . . . . . . . . . . . . . . . . . . . . . . 224

C2 Register Definition 20.4. FPCTL: C2 Flash Programming Control . . . . . . . . . . . . 224

C2 Register Definition 20.5. FPDAT: C2 Flash Programming Data . . . . . . . . . . . . . . 224

Rev. 1.7 15

Page 16

C8051F310/1/2/3/4/5/6/7

NOTES:

16 Rev. 1.7

Page 17

C8051F310/1/2/3/4/5/6/7

1. System Overview

C8051F31x device s are fully integrated mixed-signal System-on-a-Chip MCUs. Highli ghted features are

listed below. Refer to

• High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

• In-system, full-speed, non-intrusive debug interface (on-chip)

• True 10-bit 200 ksps 25-channel single-ended/differential ADC with analog multiplexer

(C8051F310/1/2/3/6)

• Precision programmable 25 MHz internal oscillator

• 16 kB (C8051F310/1/6/7) or 8 kB (C8051F312/3/4/5) of on-chip Flash memory

• 1280 bytes of on-chip RAM

• SMBus/I2C, Enhanced UART , and Enhanced SPI serial interfaces implemented in hardware

• Four general-purpose 16-bit timers

• Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer

function

• On-chip Power-On Reset, VDD Monitor, and Temperature Sensor

• On-chip Voltage Comparators (2)

• 29/25/21 Port I/O (5 V tolerant)

With on-chip Power-On Reset, VDD monitor, Watchdog Timer, and clock oscillator, the C8051F31x devices

are truly stand-alone Syste m-on-a-Chip solutions. The F lash memory can be reprogra mmed even in-cir

cuit, providing non-vo latil e data sto rage, and al so al lowin g field u pgrad es of the 805 1 firm ware. Us er software has complete c ontrol of all peripherals, and may individually shut down any or al l peripherals for

power savings.

Table 1.1 for specific product feature selection.

-

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip

resources), full speed, in-circuit debugging using the production MCU installed in the final application. This

debug logic supports inspection and modification of memory and registers, setting breakpoints, single

stepping, run and halt commands. All a nalog and digital peripheral s are fully functional whi le debugging

using C2. The two C2 i nterface pins can be shared with us er functions, all owing in-system p rogramming

and debugging without occupying package pins.

Each device i s specifi ed for 2.7- to-3.6 V ope ration ove r the industr ial temper ature range ( –45 to +85 °C).

The Port I/O and

LQFP, 28-pin QFN, and 24-pin QFN packages. See

ages are also referred to as MLP or MLF packages.

RST pins are tolerant of inpu t signa ls up to 5 V. The C8051F31x are available in 32-pin

Table 1.1 for order i ng part num ber s. Note : QFN pac k-

Rev. 1.7 17

Page 18

C8051F310/1/2/3/4/5/6/7

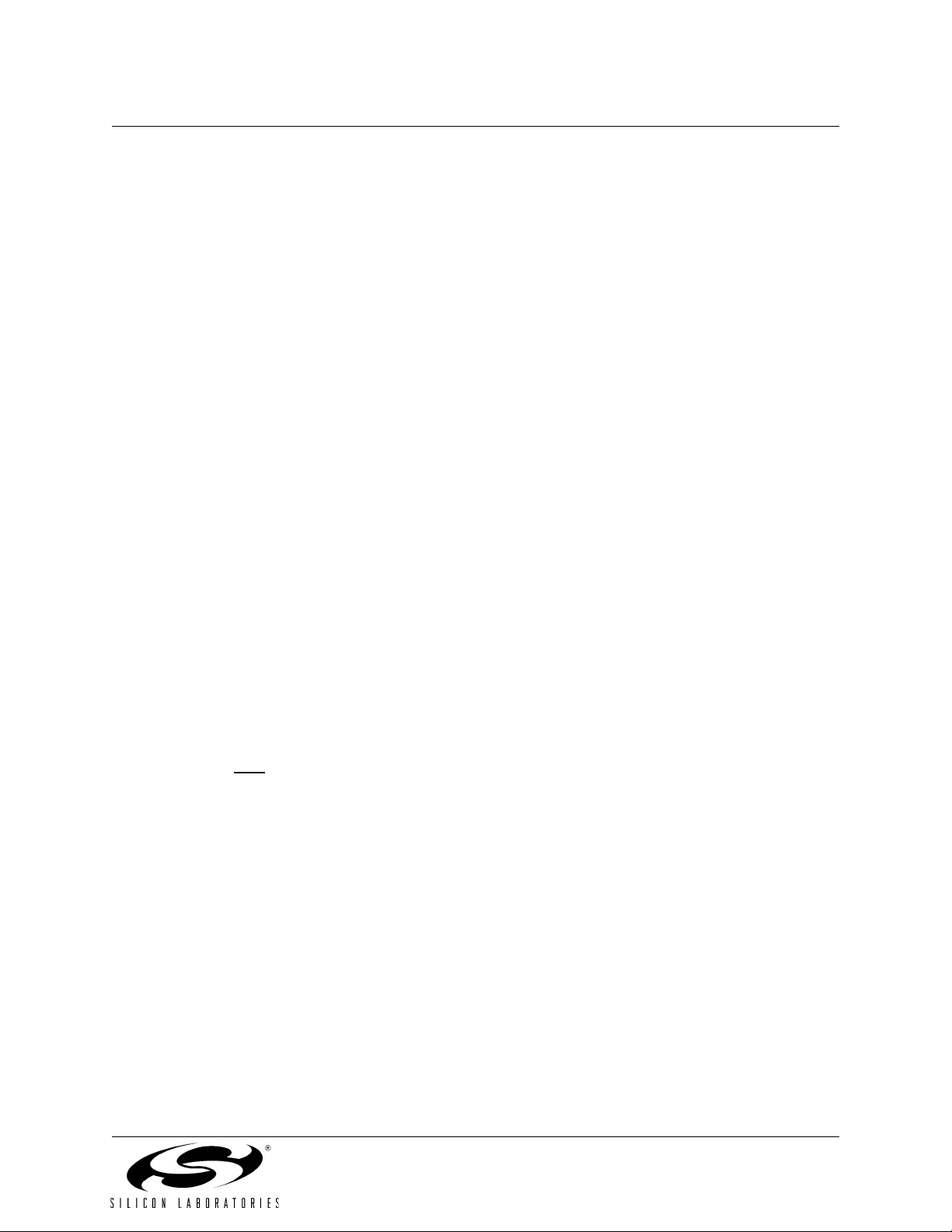

Table 1.1. Product Selection Guide

Ordering Part Number

C8051F310 25 16 1280 3 3 3 3 3 3 29 3 3 2 - LQFP-32

C8051F310-GQ 25 16 1280 3 3 3 3 3 3 29 3 3 2 3 LQFP-32

C8051F311 25 16 1280 3 3 3 3 3 3 25 3 3 2 - QFN-28

C8051F311-GM 25 16 1280 3 3 3 3 3 3 25 3 3 2 3 QFN-28

C8051F312 25 8 1280 3 3 3 3 3 3 29 3 3 2 - LQFP-32

C8051F312-GQ 25 8 1280 3 3 3 3 3 3 29 3 3 2 3 LQFP-32

C8051F313 25 8 1280 3 3 3 3 3 3 25 3 3 2 - QFN-28

C8051F313-GM 25 8 1280 3 3 3 3 3 3 25 3 3 2 3 QFN-28

C8051F314 25 8 1280 3 3 3 3 3 3 29 - - 2 - LQFP-32

C8051F314-GQ 25 8 1280 3 3 3 3 3 3 29 - - 2 3 LQFP-32

C8051F315 25 8 1280 3 3 3 3 3 3 25 - - 2 - QFN-28

C8051F315-GM 25 8 1280 3 3 3 3 3 3 25 - - 2 3 QFN-28

C8051F316-GM 25 16 1280 3 3 3 3 3 3 21 3 3 2 3 QFN-24

C8051F317-GM 25 16 1280 3 3 3 3 3 3 21 - - 2 3 QFN-24

MIPS (Peak)

Flash Memory

RAM

Calibrated Internal 24.5 MHz Oscillator

SMBus/I2C

Enhanced SPI

UART

Timers (16-bit)

Programmable Counter Array

Digital Port I/Os

10-bit 200 ksps ADC

Temperature Sensor

Analog Comparators

Lead-free (RoHS Compliant)

Package

18 Rev. 1.7

Page 19

C8051F310/1/2/3/4/5/6/7

VDD

GND

/RST/C2CK

Analog/Digital

Power

C2D

XTAL1

XTAL2

POR

External

Oscillator

Circuit

2%

Internal

Oscillator

Debug HW

Brown-

Out

Reset

System Clock

8

0

5

1

C

o

SFR Bus

r

e

16kbyte

FLASH

256 byte

SRAM

1K byte

SRAM

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

SMBus

Port 2

Latch

Port 3

Latch

VDD

10-bit

200ksps

ADC

RTC

PCA/

WDT

SPI

VREF

P

0

D

r

v

C

P

R

1

O

S

D

S

r

B

v

A

R

P

2

D

r

v

P

3

D

r

v

CP0

+

-

CP1

+

-

Temp

A

AIN0-AI N20

M

U

X

VDD

P0.0/VREF

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0/C2D

P3.1

P3.2

P3.3

P3.4

Figure 1.1. C8051F31 0 Block Diagr am

Rev. 1.7 19

Page 20

C8051F310/1/2/3/4/5/6/7

VDD

GND

/RST/C2CK

Analog/Digital

Power

C2D

XTAL1

XTAL2

POR

External

Oscillator

Circuit

2%

Internal

Oscillator

Debug HW

Brown-

Out

Reset

System Clock

8

0

5

1

C

o

SFR Bus

r

e

16kbyte

FLASH

256 byte

SRAM

1K byte

SRAM

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

PCA/

WDT

SMBus

Port 2

Latch

Port 3

Latch

VDD

10-bit

200ksps

ADC

RTC

SPI

VREF

P

0

D

r

v

C

P

R

1

O

S

D

S

r

B

v

A

R

P

2

D

r

v

P

3

D

r

v

CP0

+

-

CP1

+

-

Temp

A

AIN0-AIN20

M

U

X

VDD

P0.0/VREF

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0/C2D

Figure 1.2. C8051F311 Block Diagram

20 Rev. 1.7

Page 21

C8051F310/1/2/3/4/5/6/7

VDD

GND

/RST/C2CK

Analog/Digital

Power

C2D

XTAL1

XTAL2

POR

External

Oscillator

Circuit

2%

Internal

Oscillator

Debug HW

Brown-

Out

Reset

System Clock

8

0

5

1

C

o

SFR Bus

r

e

8 kB

FLASH

256 byte

SRAM

1K byte

SRAM

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

RTC

PCA/

WDT

SMBus

SPI

Port 2

Latch

Port 3

Latch

VDD

10-bit

200ksps

ADC

VREF

CP0

CP1

Temp

VDD

C

R

O

S

S

B

A

R

+

-

+

-

A

M

U

X

P

0

D

r

v

P

1

D

r

v

P

2

D

r

v

P

3

D

r

v

AIN0-AIN20

P0.0/VREF

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0/C2D

P3.1

P3.2

P3.3

P3.4

Figure 1.3. C8051F312 Block Diagram

Rev. 1.7 21

Page 22

C8051F310/1/2/3/4/5/6/7

VDD

GND

/RST/C2CK

Analog / Digital

Power

C2D

XTAL1

XTAL2

POR

External

Oscillator

Circuit

2%

Internal

Oscillator

Debug HW

Brown-

Out

Reset

System Clock

8

0

5

1

C

o

SFR Bus

r

e

8 kB

FLASH

256 byte

SRAM

1K byte

SRAM

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

RTC

PCA/

WDT

SMBus

Port 2

Latch

Port 3

Latch

VDD

10-bit

200ksps

ADC

SPI

VREF

CP1

CP0

Temp

VDD

C

R

O

S

S

B

A

R

+

-

+

-

A

M

U

X

P

0

D

r

v

P

1

D

r

v

P

2

D

r

v

P

3

D

r

v

AIN0-AIN20

P0.0/VREF

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0/C2D

Figure 1.4. C8051F313 Block Diagram

22 Rev. 1.7

Page 23

C8051F310/1/2/3/4/5/6/7

VDD

GND

/RST/C2CK

Analog/Digital

Power

C2D

XTAL1

XTAL2

POR

External

Oscillator

Circuit

2%

Internal

Oscillator

Debug HW

Brown-

Out

Reset

8

0

5

1

8 kB

FLASH

256 byte

SRAM

1K byte

SRAM

C

System Clock

o

SFR Bus

r

e

Figure 1.5. C8051F314 Block Diagram

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

RTC

PCA/

WDT

SMBus

SPI

Port 2

Latch

Port 3

Latch

P

0

D

r

v

C

P

R

1

O

S

D

S

r

B

v

A

R

P

2

D

r

v

P

3

D

r

v

CP0

+

-

CP1

+

-

P0.0/VREF

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0/C2D

P3.1

P3.2

P3.3

P3.4

Rev. 1.7 23

Page 24

C8051F310/1/2/3/4/5/6/7

VDD

GND

/RST/C2CK

Analog/Digital

Power

C2D

XTAL1

XTAL2

POR

External

Oscillator

Circuit

2%

Internal

Oscillator

Debug HW

Brown-

Out

Reset

System Clock

8

0

5

1

C

o

SFR Bus

r

e

8 kB

FLASH

256 byte

SRAM

1K byte

SRAM

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

RTC

PCA/

WDT

SMBus

SPI

Port 2

Latch

Port 3

Latch

P

0

D

r

v

C

P

R

1

O

R

CP0

+

-

CP1

+

-

S

D

S

r

B

v

A

P

2

D

r

v

P

3

D

r

v

P0.0/VREF

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0/C2D

Figure 1.6. C8051F315 Block Diagram

24 Rev. 1.7

Page 25

C8051F310/1/2/3/4/5/6/7

/

T

VDD

GND

RST/C2CK

Analog/Digital

Power

C2D

XTAL1

XTAL2

POR

External

Oscillator

Circuit

2%

Internal

Oscillator

Debug HW

Brown-

Out

Reset

System Clock

8

0

5

1

C

o

SFR Bus

r

e

16 kB

FLASH

256 byte

SRAM

1 kB

SRAM

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

PCA/

SMBus

Port 2

Latch

Port 3

Latch

VDD

10-bit

200 ksps

ADC

RTC

WDT

SPI

VREF

CP0

CP1

Temp

VDD

A

M

U

X

+

-

+

-

C

R

O

S

S

B

A

R

P

0

D

r

v

P

1

D

r

v

P

2

D

r

v

P

3

D

r

v

AIN0–AIN20

P0.0/VR EF

P0.1

P0.2/XT A L1

P0.3/XT A L2

P0.4/TX

P0.5/RX

P0.6/CN VS

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P3.0/C2 D

Figure 1.7. C8051F316 Block Diagram

Rev. 1.7 25

Page 26

C8051F310/1/2/3/4/5/6/7

VDD

GND

/RST/C2CK

Analog/Digital

Power

C2D

XTAL1

XTAL2

POR

External

Oscillator

Circuit

2%

Internal

Oscillator

Debug HW

Brown-

Out

Reset

8

0

5

1

16 kB

FLASH

256 byte

SRAM

1 kB

SRAM

C

System Clock

o

SFR Bus

r

e

Figure 1.8. C8051F317 Block Diagram

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

RTC

PCA/

WDT

SMBus

SPI

Port 2

Latch

Port 3

Latch

P

0

D

r

v

C

P

R

1

O

S

D

S

r

B

v

A

R

P

2

D

r

v

P

3

D

r

v

CP0

+

-

CP1

+

-

P0.0/VREF

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P3.0/C2D

26 Rev. 1.7

Page 27

C8051F310/1/2/3/4/5/6/7

k)

1.1. CIP-51™ Microcontroller Core

1.1.1. Fully 8051 Compatible

The C8051F31x family utilizes Silicon Laboratories' proprietary CIP-51 microcontroller core. The CIP-51 is

fully compatible with t he MCS -51™ instruc tion s et; s tandard 80 3x/80 5x as sembl ers and comp ilers ca n be

used to develop software. The CIP-51 core offers all the peripherals included with a standard 8052, includ

ing four 16-bit counter/timers, a full-duplex UART with extended baud rate configuration, an enhanced SPI

port, 1280

I/O pins.

1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all ins truction s except for MU L and DIV take 12 or 24 syste m

clock cycles to execute wi th a maximu m sys tem clock of 12-to- 24

cutes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than

four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that

require each execution time.

bytes of internal RAM , 128 byte Special Function Register (SFR) address space, and 29/25/2 1

MHz. By contrast, the CIP- 51 core exe-

-

Clocks to Execute 1 2 2/3 3 3/4 4 4/5 5 8

Number of Instructions 26 50 5 14 7 3 1 2 1

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. Figure 1.9

shows a comparison of peak throu ghputs for various 8-bit micro controller cores wit h their maximum system clocks.

25

20

15

MIPS

10

5

Silicon Labs

CIP-51

(25 MHz clk)

Microchip

PIC17C75x

(33 MHz clk)

Philips

80C51

(33 MHz clk)

ADuC812

8051

(16 MHz cl

Figure 1.9. Comparison of Peak MCU Execution Speeds

Rev. 1.7 27

Page 28

C8051F310/1/2/3/4/5/6/7

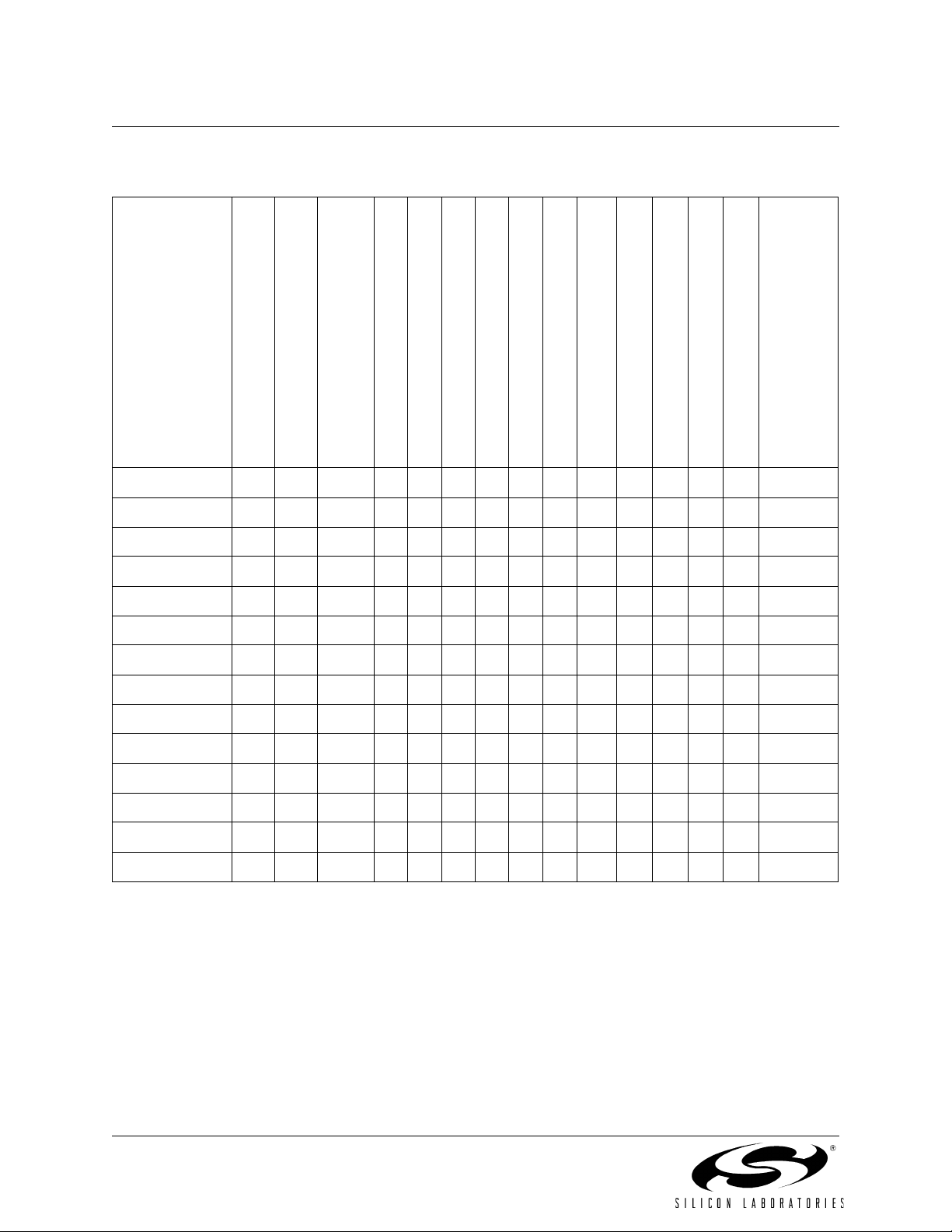

1.1.3. Additional Features

The C8051F31x SoC famil y includes several key enhancements to the CIP-51 co re and peripherals to

improve performance and ease of use in end applications.

The extended interrupt handler provides 14 interrupt sources into the CIP-51 (as opposed to 7 for the standard 8051), allowing numerous analog and digital peripherals to interrupt the controller. An interrupt driven

system requires less intervention by the MCU, giving it more effective throughput. The extra interrupt

sources are very useful when building multi-tasking, real-time systems.

Eight reset source s are available: power-on r eset circuitry (POR), an on-c hip VDD monitor (forces reset

when power supply voltage drops below V

Missing Clock Detec tor, a voltage level detection from Comparator0, a forc ed software reset, an exter nal

reset pin, and an er rant Flash read/wr ite protection c ircuit. Each r eset source excep t for the POR, R eset

Input Pin, or Flash err or may b e dis abled by the use r in soft ware. Th e WDT ma y be pe rman ently ena bled

in software after a power-on reset during MCU initialization.

The internal oscillator is factory calibrated to 24.5 MHz ±2%. An external oscillator drive circuit is also

included, allowing an external crystal, ceramic resonator, capacitor, RC, or CMOS clock source to generate

the system clock. If desi red, the system clock sourc e ma y b e swi tc hed on- the -f ly betw een the internal and

external oscillato r circuits. An ex ternal oscill ator can be extremely us eful in low p ower applica tions, allow

ing the MCU to run from a slow (power savi ng) exter nal crystal s ource, whil e perio dically swi tching to the

fast internal oscillator as needed.

as given in Table 9.1 on page 110), a Watchdog Timer, a

RST

-

XTAL1

XTAL2

Internal

Oscillator

External

Oscillator

Drive

Px.x

Px.x

VDD

Power On

Supply

Monitor

Comparator 0

+

-

System

Clock

Clock Select

C0RSEF

Missing

Clock

Detector

(oneshot)

EN

MCD

Enable

CIP-51

Microcontroller

PCA

WDT

EN

WDT

Enable

+

-

System Reset

Enable

(Software Reset)

SWRSF

'0'

Core

Extended Interrupt

Handler

Figure 1.10. On-Chip Clock and Reset

Reset

Errant

FLASH

Operation

(wired-OR)

Reset

Funnel

/RST

28 Rev. 1.7

Page 29

C8051F310/1/2/3/4/5/6/7

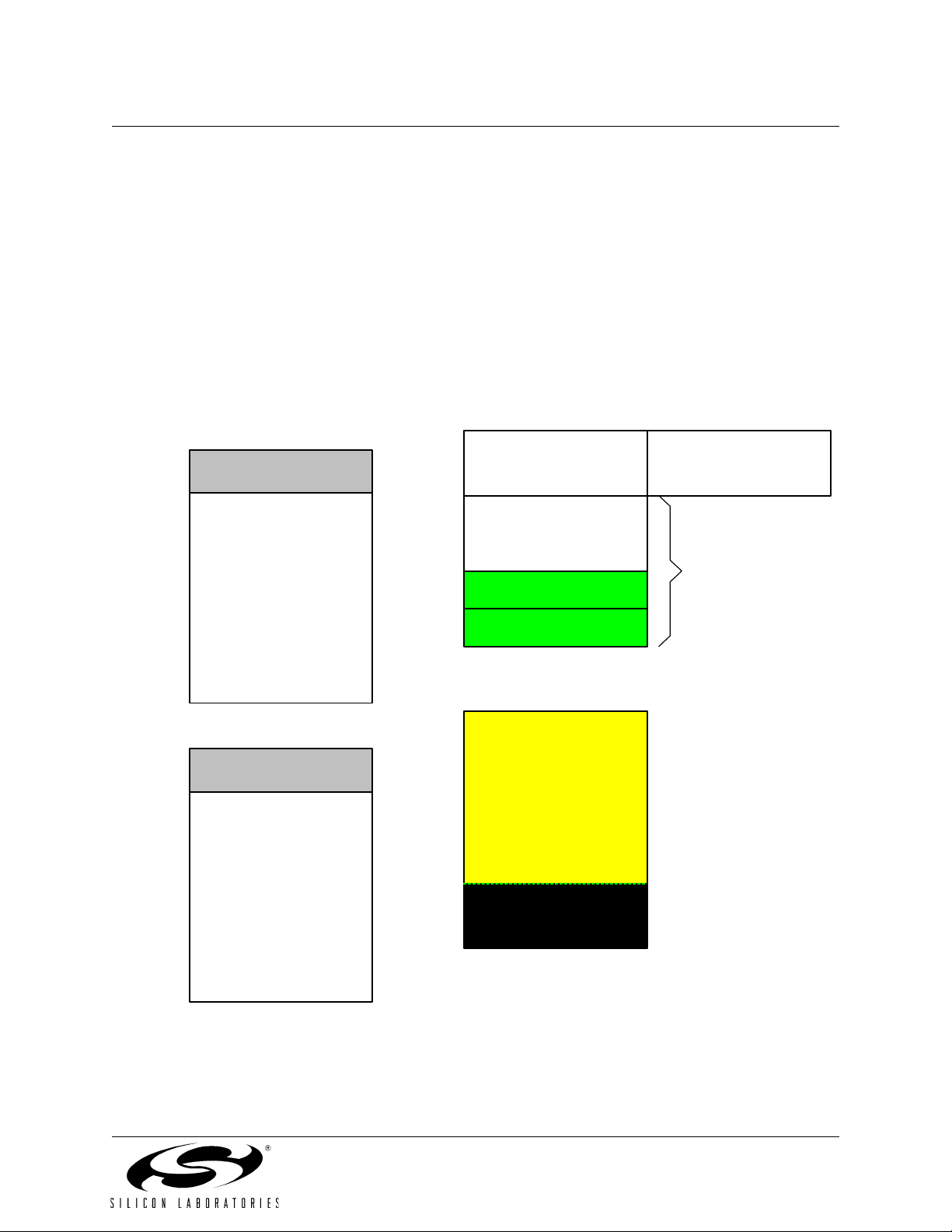

1.2. On-Chip Memory

The CIP-51 has a standa rd 8051 program and data addres s configuration. It inclu des 256 bytes of data

RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general

purpose RAM, and direct add ressing acce sses the 128 byte SFR address space. The lower 128 bytes of

RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of

general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

Program memory con sists of 8 or 16 kB of Fl ash. This memory ma y be reprogramm ed in-system in 51 2

byte sectors, and requi res no specia l off-chip program ming voltage. See

memory map.

Figure 1.11 for the MCU system

PROGRAM/DATA MEMORY

(Flash)

C8051F310/1/6/7

0x3E00

0x3DFF

0x0000

0x2000

0x1FFF

RESERVED

16 kB Flash

(In-System

Programmab le in 5 12

Byte Sectors)

C8051F31 2/3/4/5

RESERVED

0xFF

0x80

0x7F

0x30

0x2F

0x20

0x1F

0x00

0xFFFF

DATA MEMORY (RAM)

INTERNAL DATA ADDRESS SPACE

Upper 128 RAM

(Indirect Addressing

Only)

(Direct and Indirect

Addressing)

Bit Addressable

Gene ra l P u rpo s e

Registers

Special Function

Register's

(Direct Addressing Only)

Lower 128 RA M

(Direct and Indirect

Addressing)

EXTERNAL DATA ADDRESS SPACE

Same 1024 bytes as from

0x0000 to 0x03FF, wrapped

on 1 kB boundaries

0x0000

8 kB Flash

(In-System

Programmab le in 5 12

Byte Sectors)

Figure 1.11. On-Board Memory Map

0x0400

0x03FF

0x0000

XRAM - 1024 Bytes

(accessable using MOVX

instruction)

Rev. 1.7 29

Page 30

C8051F310/1/2/3/4/5/6/7

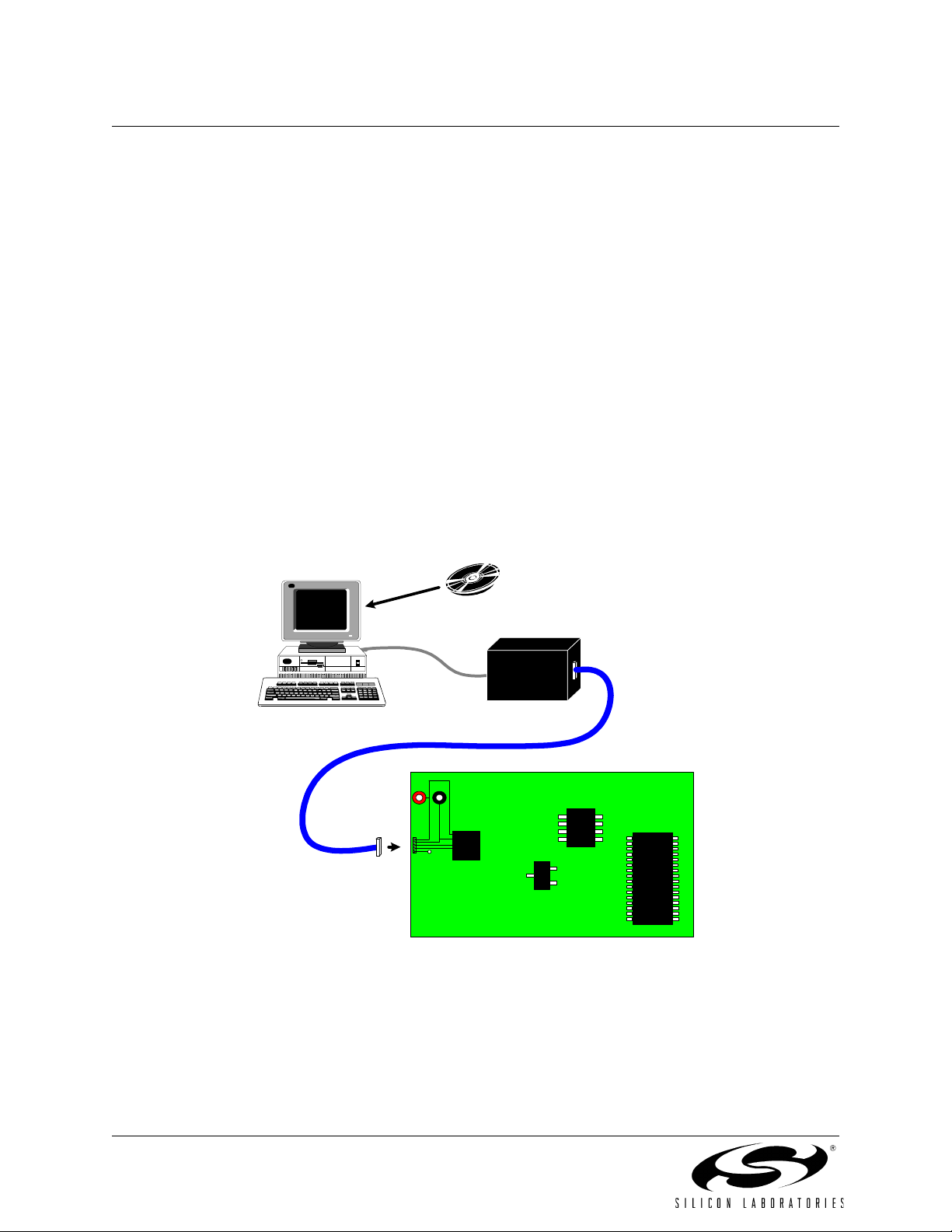

1.3. On-Chip Debug Circuitry

The C8051F31x device s include on- chip Silicon Lab s 2-Wire (C2) debug circuitry that provides non-i ntrusive, full speed, in-circuit debugging of the production part installed in the end application.

Silicon Labs' debugging system supports inspection and modification of memory and registers, breakpoints, and single stepping. No additi onal target RAM , progra m memory, timers, or communication s channels are required. Al l th e d ig ital an d a nal og peri pher a ls ar e functi ona l a nd wor k co rre ctly whi le deb ugg ing .

All the peripherals (except for the ADC and SMB us) are stalled when the MCU is halted, during singl e

stepping, or at a breakpoint in order to keep them synchronized.

The C8051F310DK development kit provides all the hardware and software necessary to develop application code and perfo rm in-circuit debugging wi th the C8051F31x MCUs. Th e kit includes software with a

developer's studio and debugger, an integrated 8051 assembler, a debug adapter, a target application

board with the associated MCU installed, and the required cables and wall-mount power supply.

The Silicon Labs IDE interf ace is a vastl y superio r developing and debuggi ng configurati on, compared t o

standard MCU emulators that use on-b oard "ICE Chips" and require the MCU in the application board to

be socketed. Silico n Labs' debug paradigm incr eases ease of use and p reserves the performa nce of the

precision analog peripherals.

Silicon Labo ratories Integrated

Development Environment

Windows 98SE or later

Debug

Adapter

C2 (x2), VDD, GND

VDD GND

C8051F31x

TARGET PCB

Figure 1.12. Development/In-System Debug Diagram

30 Rev. 1.7

Page 31

C8051F310/1/2/3/4/5/6/7

1.4. Programmable Digital I/O and Crossbar

C8051F310/2/4 devices include 29 I/O pins (three byte-wide Ports and one 5-bit-wide Port);

C8051F311/3/5 devices include 25 I/O pi ns (thr ee by te-wide Ports and one 1-bit-wi de P ort) ; C8 051 F 316/ 7

devices include 21 I/O pins (one byte-wide Port, two 6-bit-wide Ports and one 1-bit-wide Port). The

C8051F31x Ports behav e like typica l 8051 Ports with a few e nhanceme nts. Each Po rt pin may be config

ured as an analog inp ut o r a di gital I/ O pin . Pi ns s ele ct ed a s d ig ital I/O s may a ddi tio nal ly be co nfi gured for

push-pull or open-dr ain output. T he “weak pu llups” that a re fixed on ty pical 80 51 devices may be global ly

disabled, providing power savings capabilities.

The Digital Crossbar allows mapping of internal digital system resources to Port I/O pins (See Figure 1.13).

On-chip counter/timers, serial buses, HW interrupts, comparator output, and other digital signa ls in the

controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This

allows the user to select the exact mix of general purpose Por t I/O and digital resources needed for th e

particular application.

-

Highest

Priority

Lowest

Priority

XBR0, XBR1,

PnSKIP Registers

PnMDOUT,

PnMDIN Registers

Priority

Decoder

(P0.0-P0.7)

(P1.0-P1.7)

(P2.0-P2.3)

(P2.4-P2.7)

(P3.0-P3.4)

2

4

2

2

2

6

2

8

8

4

4

5

Digital

Crossbar

8

8

4

P0

I/O

Cells

P1

I/O

Cells

P2

84

I/O

Cells

P3

5

I/O

Cells

Notes:

1. P3.1–P3.4 only available on the

C8051F310/2/4.

2. P1.6, P1.7, P2.6, P2.7 only

available on the C8051F310/1/2/3/4/5

P0.0

P0.7

P1.0

P1.7

P2.0

P2.7

P3.0

P3.4

UART

SPI

SMBus

CP0

Outputs

CP1

Outputs

SYSCLK

(Internal Digital Signals)

PCA

T0, T1

P0

P1

(Port Latches)

P2

P3

Figure 1.13. Digital Crossbar Diagram

Rev. 1.7 31

Page 32

C8051F310/1/2/3/4/5/6/7

1.5. Serial Ports

The C8051F31x Family includ es an SMBus/I2C interface, a full-duplex UA RT with enhanced baud rate

configuration, an d an Enhanced S PI interface. Eac h of the seri al buses is fully implemented in hardware

and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

1.6. Programmable Counter Array

An on-chip Programmable Counter/Timer Array (PCA) is included in addition to the four 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with five programmable capture/compare modules. The PCA clock is derived from one of six sources: the system clock divided

by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, or

the external oscilla tor c lock s our ce di vi de d by 8 . T he ext er nal cloc k s ourc e s ele ct ion is useful for real - tim e

clock functionality, where the PCA is cloc ked by a n exter nal source while th e inter nal oscilla tor drives the

system clock.

Each capture/compare module can be configured to operate in one of six modes: Edge-Triggered Capture,

Software Timer, High S peed Output, 8- or 16-bit Pulse Width Modulator, or Frequency Output. Additionally,

Capture/Compare Module 4 offers watchdog timer (WDT) capabilities. Following a system reset, Module 4

is configured and enabled in WDT mode. The PCA Capture/Compare Module I/O and External Clock Input

may be routed to Port I/O via the Digital Crossbar.

SYSCLK/12

SYSCLK/4

Timer 0 Overflow

ECI

SYSCLK

External Clock/8

Capture/Compare

Module 0

ECI

CEX0

PCA

CLOCK

MUX

Capture/Compare

Module 1

CEX1

16-Bit Counter/Timer

Capture/Compare

Module 2

CEX2

Capture/Compare

Module 3

CEX3

Capture/Compare

Module 4 / WDT

CEX4

Crossbar

Port I/O

Figure 1.14. PCA Block Diagram

32 Rev. 1.7

Page 33

C8051F310/1/2/3/4/5/6/7

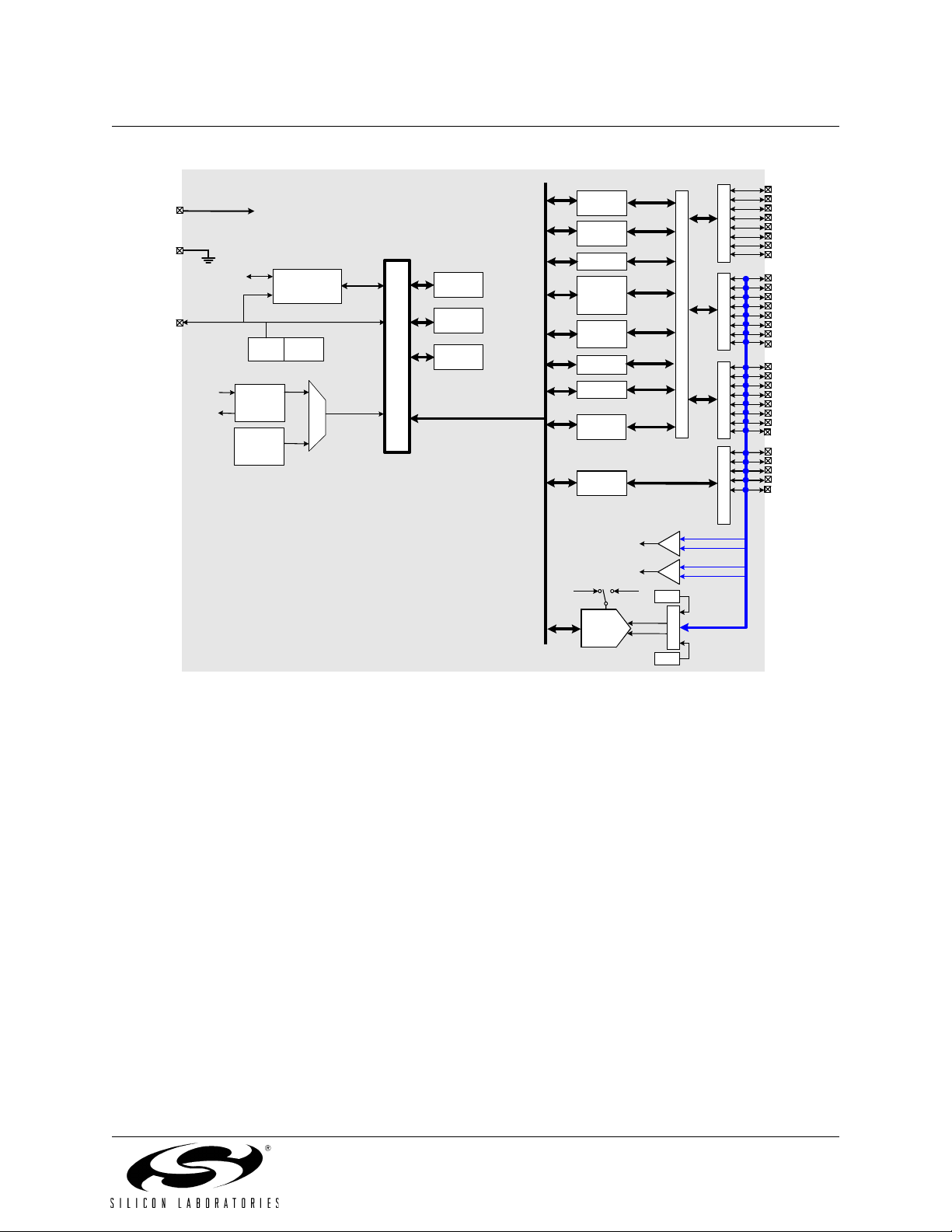

1.7. 10-Bit Analog to Digital Converter

The C8051F310/1/2/3/6 devices include an on-chip 10-bit SAR ADC with a 25-cha nnel differential input

multiplexer. With a maximum throug hput of 200

±1LSB. The ADC system include s a configurab le analog multip lexer that selec ts both positive an d nega

tive ADC inputs. Ports1-3 are availa ble as an ADC inputs; additionally, the on-chip Temperature Sensor

output and the power supply voltage (V

DD

ADC to save power.

Conversions can be started in six ways: a software command, an overflow of Timer 0, 1, 2, or 3, or an

external convert start signal. This flexibility allows the start of conversion to be triggered by software

events, a periodic sig nal (timer ove rflows), or e xternal HW sig nals. Convers ion completi ons are ind icated

by a status bit and an interrupt (if enabled) . The resulting 10-bit data word is latched into the ADC da ta

SFRs upon completion of a conversion.

Window compare registers for the ADC data can be configured to interrupt the controller when ADC data is

either within or o utside of a specified range. The ADC can monitor a key voltage continuously in back

ground mode, but not interrupt the controller unless the converted data is within/outside the specified

range.

ksps, the ADC offers true 10-bit accuracy with an INL of

-

) are available as ADC inputs. User firmware may shut down the

-

Analog Multiplexer

P1.6, P1.7 available on

C8051F310/1/2/3/4/5

P2.6, P2.7 available on

C8051F310/1/2/3/4/5

P3.1-3.4

available on

C8051F310/2

Temp

Sensor

P1.6, P1.7 available on

C8051F310/1/2/3/4/5

P2.6, P2.7 available on

C8051F310/1/2/3/4/5

P3.1-3.4

available on

C8051F310/2

P1.0

P1.7

P2.0

P2.7

P3.0

P3.4

VDD

P1.0

P1.7

P2.0

P2.7

P3.0

P3.4

VREF

GND

23-to-1

AMUX

23-to-1

AMUX

Configuration, Control, and Data Registers

(+)

10-Bit

SAR

(-)

ADC

End of

Conversion

Interrupt

Start

Conversion

16

Window Compare

000 AD0BUSY (W)

001

Timer 0 Overflow

010

Timer 2 Overflow

Timer 1 Overflow

011

CNVSTR Input

100

Timer 3 Overflow

101

ADC Data

Registers

Window

Logic

Compare

Interrupt

Figure 1.15. 10-Bit ADC Block Diagram

Rev. 1.7 33

Page 34

C8051F310/1/2/3/4/5/6/7

1.8. Comparators

C8051F31x devices include two on-chip voltage comparators that are enabled/disabled and configured via