SIGE SE1031W Datasheet

50 Ω R f

LightCharger™ 2.5 Gb/s Transimpedance Amplifier LP

Applications

§ SONET/SDH-based transmission systems, test

equipment and modules

§ OC-48 fibre optic modules and line termination

§ ATM over SONET/SDH

§ Gigabit Ethernet

§ Fibre Channel

Features

§ Single +3.3 V power supply

§ Power dissipation = 110 mW (typ)

§ Input noise current = 360 nA rms when used with

a 0.5 pF detector

§ Transimpedance gain = 2.3 kΩ into a 50 Ω load

(differential)

§ On-chip automatic gain control gives input

current overload of 2.6 mA pk and max output

voltage swing of 300 mV pk-pk

§ Differential 50 Ω out puts

§ Bandwidth (-3 dB) = 2.4 GHz

§ Wide data rate range = 50 Mb/s to 2.5 Gb/s

§ Constant photodiode reverse bias voltage = 1.5 V

(anode to input, cathode to VCC)

§ Minimal external components, supply decoupling

only

§ Operating junction temperature range = -40°C to

+125°C

§ Equivalent to Nortel Networks AB89-A4A

Ordering Information

SE1031W

Final

Product Description

SiGe Semiconductor offers a portfolio of optical

networking ICs for use in high-performance optical

transmitter and rece iver functions, from 155 Mb/s up

to 12.5 Gb/s.

SiGe Semiconductor’s SE1031 is a fully integrated,

silicon bipolar transimpedance amplifier; providing

wideband, low noise preamplification of signal current

from a photodetector. It features differential outputs,

and incorporates an automatic gain control

mechanism to increase dynamic range, allowing input

signals up to 2.6 mA peak. A decoupling capacitor on

the supply is the only external circuitry required. A

system block diagram is shown after the functional

description, on page 3.

Noise performance is optimized for 2.5 Gb/s

operation, with a calculated rms noise based

sensitivity of –26 dBm for 10

using a detector with 0.5 pF capacitance and a

responsivity of 0.9 A/W, with an infinite extinction ratio

source.

-10

bit error rate, achieved

Type Package Remark

SE1031W Bare Die None

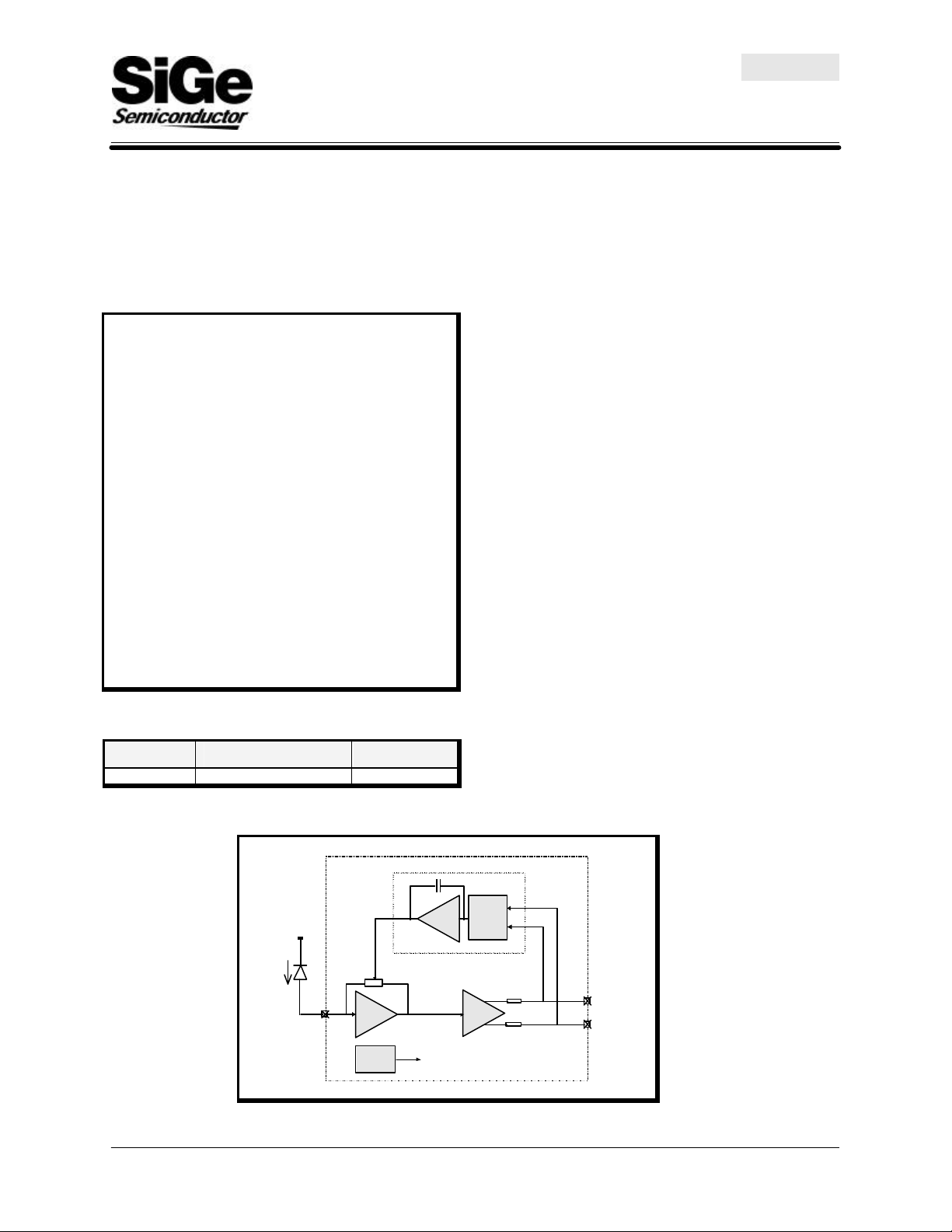

Functional Block Diagram

VCC or +ve supply

Input

Current

TZ_IN

SE1031

TzAmp

2.5 Gb/s

Tz Amp

Bandgap

Reference

54-DST-01 § Rev 1.3 § Apr 11/02 1 of 7

Automatic Gain Control

Integrator

Output

Driver

Rectifier

50 Ω

OUTP

OUTN

Top

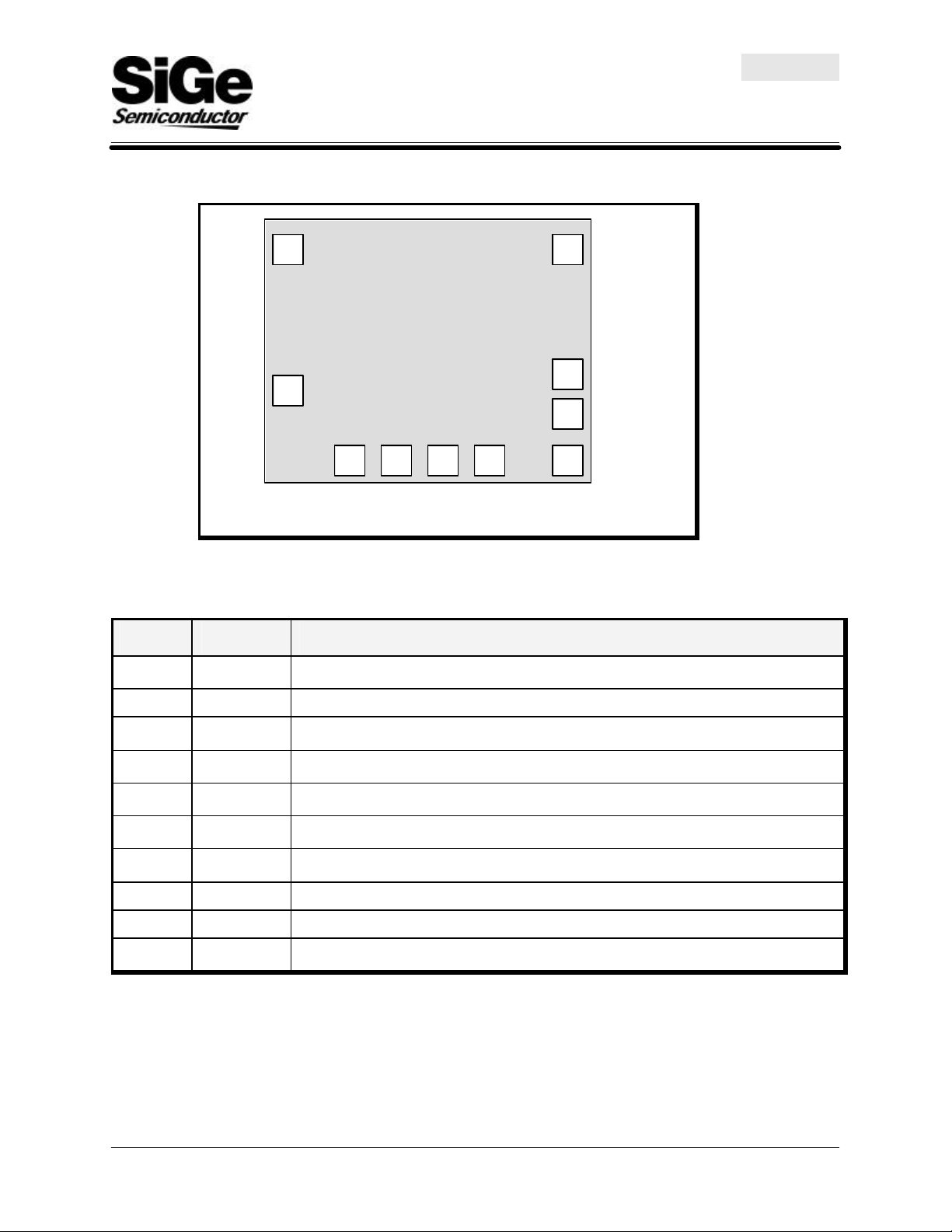

Bondpad Diagram

SE1031W

LightCharger™ 2.5 Gb/s Transimpedance Amplifier LP

Final

VCC

TZ_IN

1

View

2

6 5 4 3

10

9

8

7

VCC VEE2 VEE1 VEE1 VEE1

Bondpad Description

Pad No. Name Description

1 VCC

2 TZ_IN Input pad (connect to photodetector anode).

3 VEE2

4 VEE1

5 VEE1

6 VEE1

7 VCC

8 OUTN Negative differential voltage output.

Positive supply (+3.3 V), pads 1, 7 & 10 are connected on chip. Only one pad needs

to be bonded.

Negative supply (0V) – Note this is separate ground for the input stage, which is AC

coupled on chip. There is no DC current through this pad.

Negative supply (0V), pads 4, 5 & 6 are connected on chip. Only one pad needs to be

bonded.

Negative supply (0V), pads 4, 5 & 6 are connected on chip. Only one pad needs to be

bonded.

Negative supply (0V), pads 4, 5 & 6 are connected on chip. Only one pad needs to be

bonded.

Positive supply (+3.3 V), pads 1, 7 & 10 are connected on chip. Only one pad needs

to be bonded.

VCC

OUTP

OUTN

9 OUTP Positive differential voltage output.

10 VCC

Positive supply (+3.3 V), pads 1, 7 & 10 are connected on chip. Only one pad needs

to be bonded.

54-DST-01 § Rev 1.3 § Apr 11/02 2 of 7

2 2

LightCharger™ 2.5 Gb/s Transimpedance Amplifier LP

Functional Description

Amplifier front-end

The transimpedance front-end amplifies an input

current from a photodetector, at pin TZ_IN, to produce

a differential output voltage with the feedback resistor

Rf determining the level of amplification (see the

functional block diagram on page 1). An automatic

gain control loop varies this resistor, to ensure that

the output from the front-end does not saturate the

output driver stage that follows. This gain control

allows input signals of up to 2.6 mA peak.

The input pin TZ_IN is biased at 1.5 V below the

supply voltage VCC, allowing a photodetector to have

a constant reverse bias by connecting the cathode to

3.3 V. This enables full single rail operation.

The front-end stage has its own supply ground

connection (VEE2) to achieve optimum noise

performance and maintain integrity of the high-speed

signal path. The front-end shares the VCC (+3.3 V)

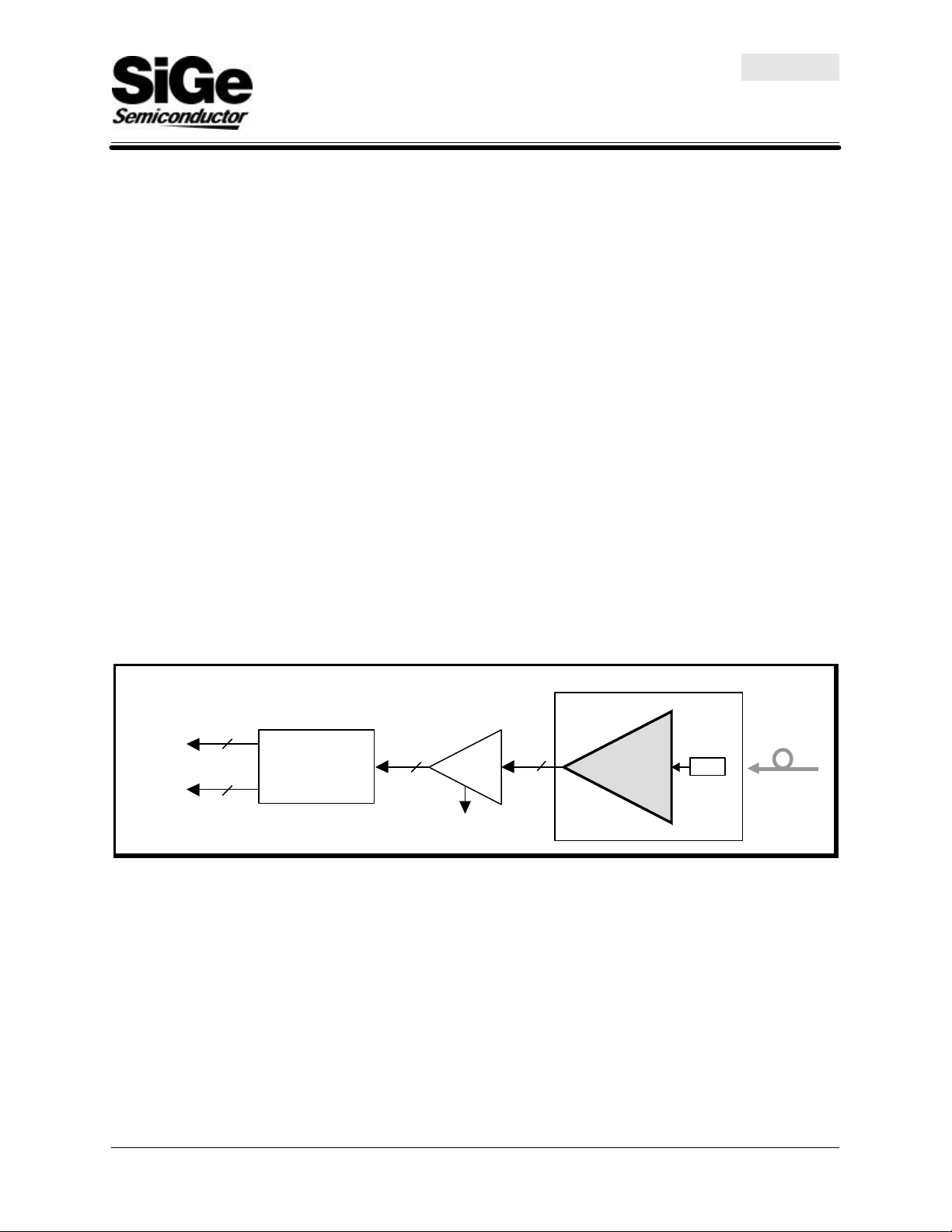

System Block Diagram

SE1031W

Final

connection with the remainder of the circuitry, which has

a separate ground (VEE1).

Output driver stage

The output driver acts as a buffer stage, capable of

swinging up to 300 mVpk-pk differential into a 100 Ω

load. The small output swings allow ease of use with

low voltage post amplifiers (e.g. 3.3 V parts).

Increasing optical input level gives a positive-going

output signal on the OUTP pin.

Automatic Gain Control (AGC)

The AGC circuit monitors the voltages from the output

driver and compares them to an internal reference

level produced via the on-chip bandgap reference

circuit. When this level is exceeded, the gain of the

front-end is reduced by controlling the feedback

resistor Rf.

A long time-constant integrator is used within the

control loop of the AGC with a typical low frequency

cut-off of 10 kHz.

Receiver Module

2.5 GHz

2.5 Gb/s

Clock

Data

Clock & Data

Recovery

AGC

Amplifier

2

SE1230

LOS

2

SE1031

TZ

Amplifier

PIN

54-DST-01 § Rev 1.3 § Apr 11/02 3 of 7

Loading...

Loading...