D602

3V, 6GHz Divide-by-2 Static Prescaler

Final

Applications

5GHz WLAN, IEEE 802.11a and HIPERLAN

VSAT at 3.6 to 4.2 GHz

Satellite Communications at 4.5 to 4.8 GHz

5 Gbps Clock Generator

Features

Low Phase Noise, -141dBc/Hz at 1kHz offset

Single Supply Voltage, 2.7 - 4.0 V

Low Power Consumption, 42mW

Power Down Mode, 0.2µA

Compatible with common PLL synthesizer ICs

8-Pin Plastic SOIC Package

Ordering Information

Type Package Remark

D602 8-Pin SOIC Plastic

Package

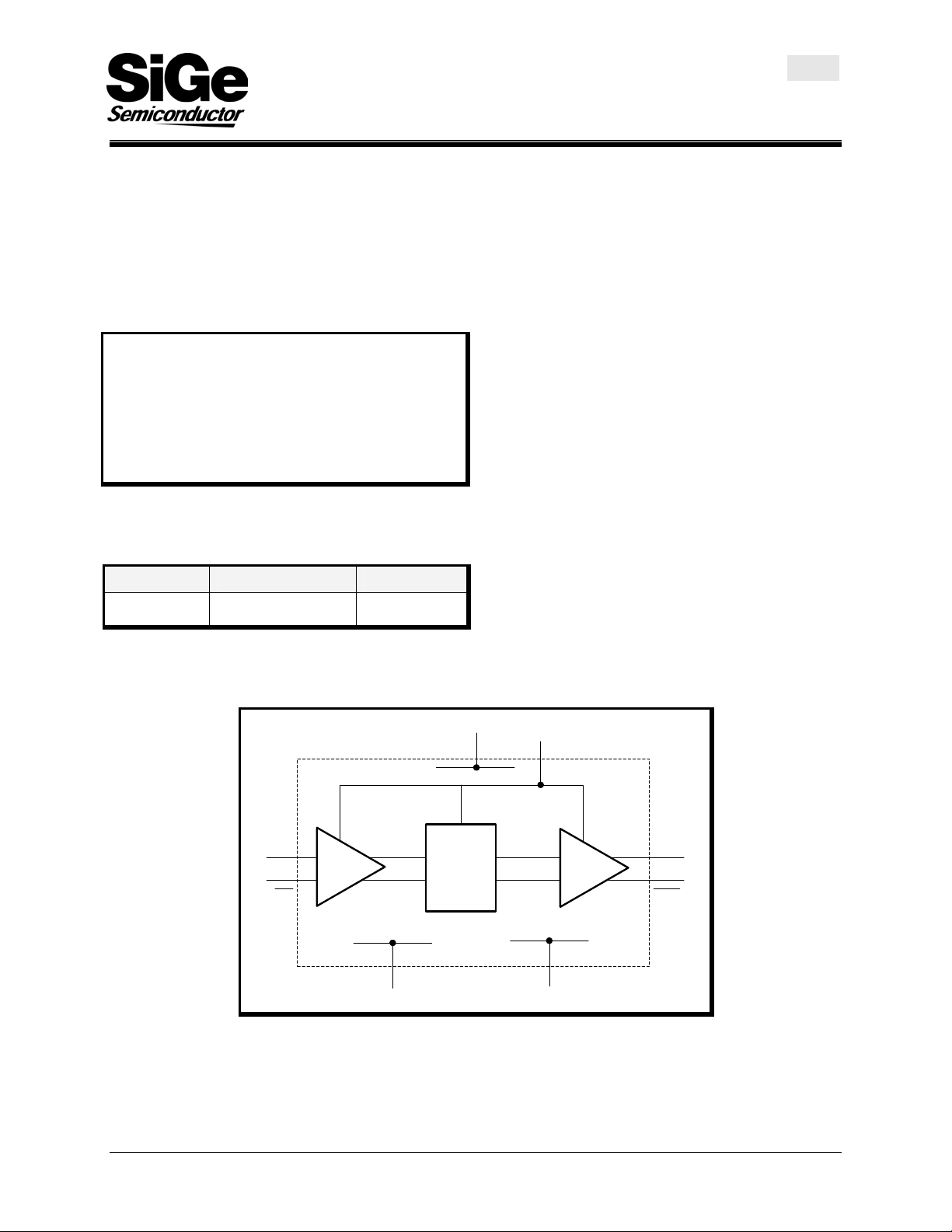

Functional Block Diagram

Product Description

The D602 is a SiGe divide-by-2 low noise static

prescaler capable of operation up to 6.0 GHz. The

D602 operates over a wide range of input frequencies

and levels, and provides differential outputs for low

noise operation with the common PLL style frequency

synthesizer ICs.

The static nature of the prescaler prevents spurious

generation.

The D602 prescaler can operate from either a single

positive or single negative supply with power down

mode for low standby power consumption.

In

In

V

CC

f

In

V

EE

2÷

PWD

Out

f

Out

Out

V

EE

20-DST-01 Rev 5.0 Sept/01 1 of 8

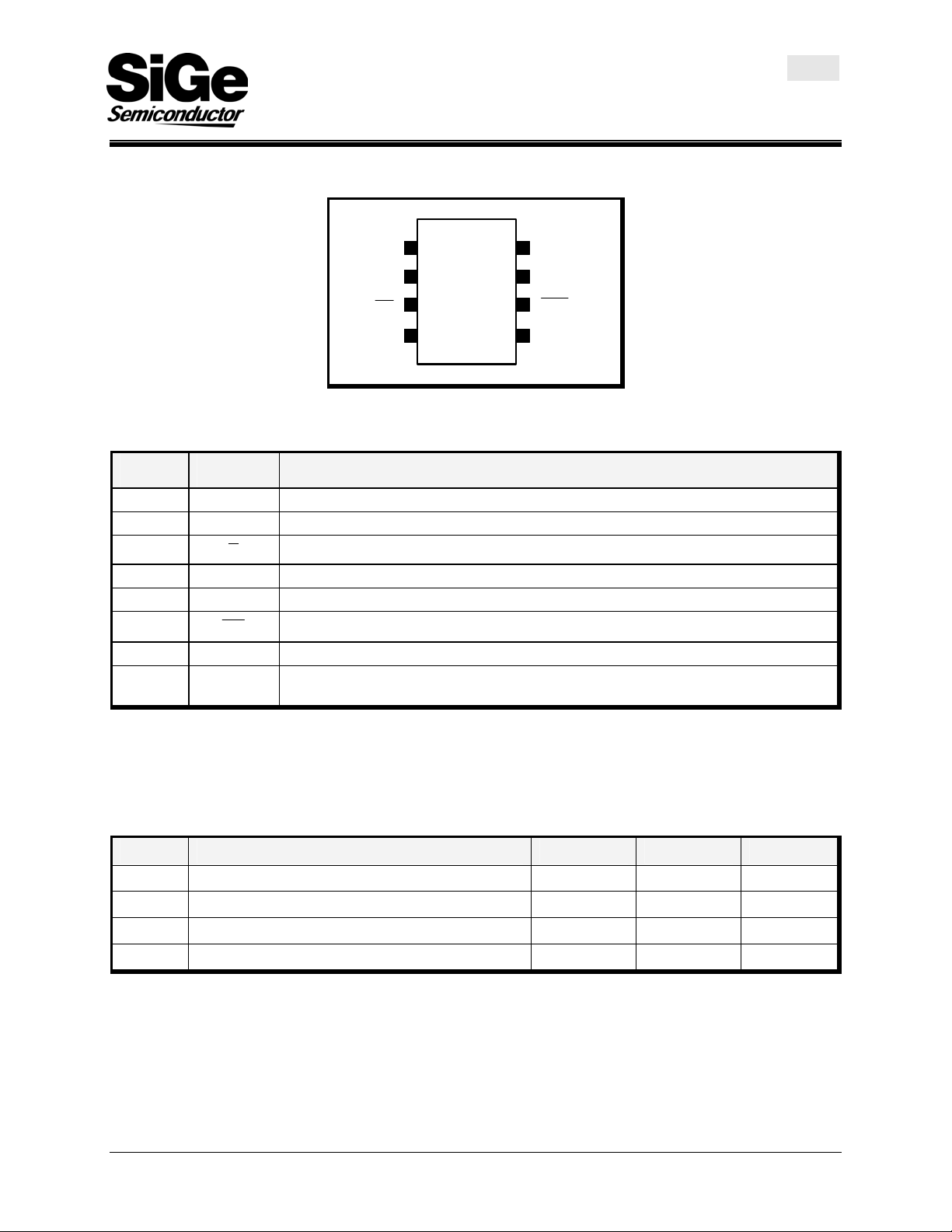

Pin Out Diagram

D602

3V, 6GHz Divide-by-2 Static Prescaler

Final

CC

EE

1

2

D602

3

4

V

In

In

V

PWD

8

7

Out

6

Out

V

5

EE

Pin Out Description

Pin No. Name Description

1 VCC Power Supply Voltage Input

2 In Prescaler Input (internally-biased)

3

4 VEE Ground for Input (pins 4 and 5 must be connected to the same potential)

5 VEE Ground for Output (pins 4 and 5 must be connected to the same potential)

6

7 Out Output (open-collector)

8 PWD

In

Out

Prescaler Complementary Input (internally-biased)

Complementary Output (open-collector)

Power Down high impedance CMOS input. When PWD is high, the part is powered

down.

Absolute Maximum Ratings

Operation in excess of any one of above Absolute Maximum Ratings may result in permanent damage. This device is

a high performance RF integrated and is ESD sensitive. The RF inputs on this device are Class 0 ESD rated;

therefore suitable precaution should be taken during handling, assembly and testing.

Symbol Parameter Min. Max. Unit

Supply Voltage -0.3 +4.3 V

Voltage on any pin with respect to VEE -0.3 VCC + 0.3 V

Differential input voltage -2.0 +2.0 V

Storage Temperature -65 +150 °C

20-DST-01 Rev 5.0 Sept/01 2 of 8

D602

3V, 6GHz Divide-by-2 Static Prescaler

Final

Electrical Characteristics

Conditions: VCC = 3.0V, -40°C < TA < 85°C unless otherwise specified

Symbol Parameter Note Min. Typ. Max. Unit

VCC Supply Voltage 2.7 3.0 4.0 V

TA Operating Temperature 1 -40 25 85 °C

ICC Supply Current 14 18 mA

I

CC – PWDN

f

In(U)

f

In(L)

f

Osc

P

In(U)

P

In(L)

P

Out

Power-Down Supply Current

(V

PWD

= High)

0.2 1.0 µA

Upper Limit of Input Frequency 2 5.8 6.4 GHz

Lower Limit of Input Frequency 2 0.6 1.0 GHz

Self Oscillation Output Frequency 3 1.0 GHz

Upper Limit of Input Power 0 3 dBm

Lower Limit of Input Power -20 -10 dBm

Output Power 4 -15.0 0 dBm

VIH High-Level PWD Input Voltage VCC - 0.2 V

VIL Low-Level PWD Input Voltage 0.2 V

IIH High-Level PWD Input Current -100.0 100.0 nA

IIL Low-Level PWD Input Current -100.0 100.0 nA

PN

Residual Phase Noise at 1kHz offset from

a 2.5GHz (f

) carrier

Out

-141 dBc/Hz

Notes: (1) Sample Tested

(2) For a sine-wave input

(3) Since the input signal is AC coupled, in the absence of an RF input, the prescaler may self oscillate and

provide an output at this frequency. Self oscillation can be eliminated by powering down the prescaler,

or applying a differential DC input voltage (a 47kΩ resistor placed between pin 3 and V

CC

).

(4) This power is delivered to a 50Ω load. It excludes the power dissipated in the external pull-up resistors.

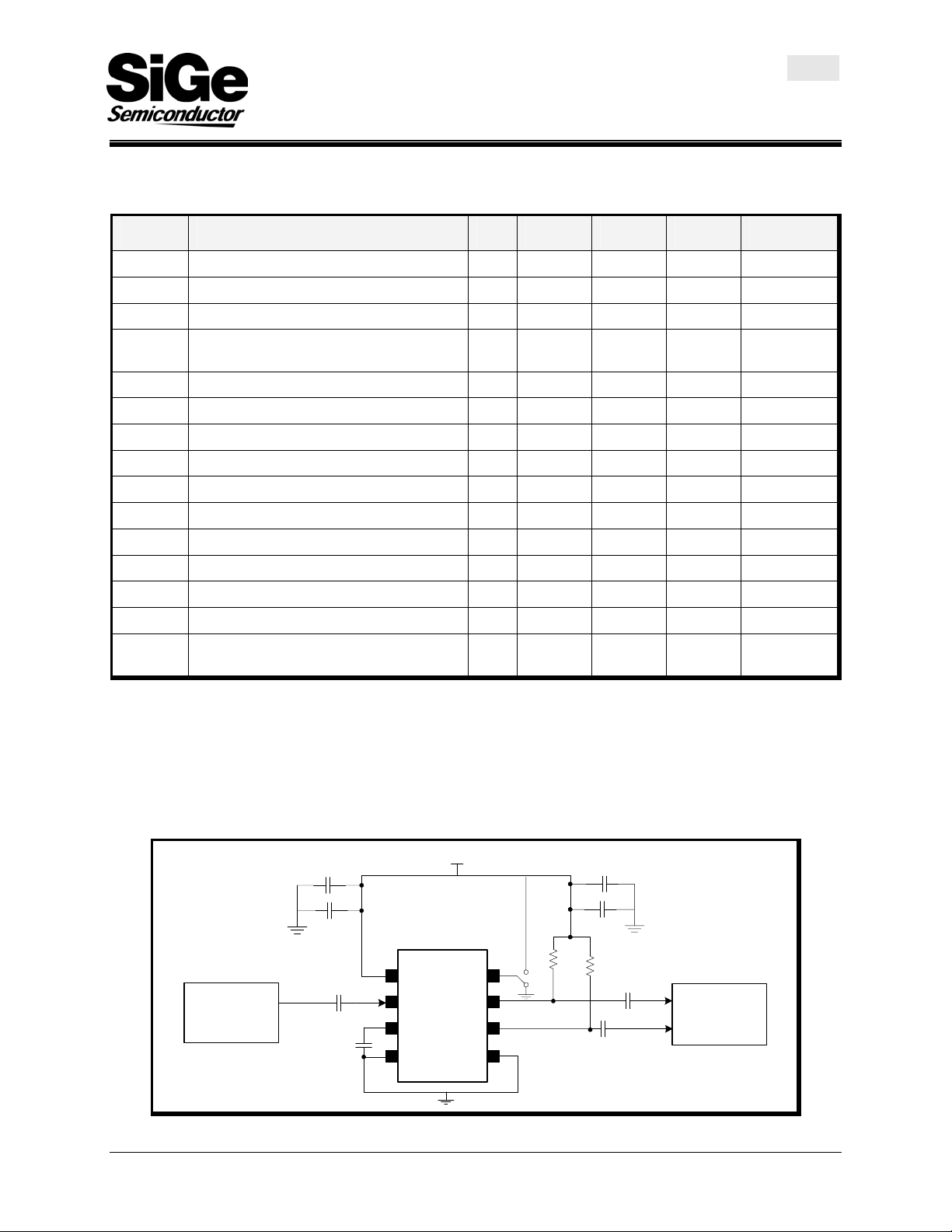

Test Circuit

V

Signal

Generator

100p

100n

1n

1p

1

2

3

4

D602

CC

8

7

6

5

51

100p

100n

51

1n

1n

50 Ohm

Measurement

Equipment

20-DST-01 Rev 5.0 Sept/01 3 of 8

Loading...

Loading...