Page 1

r

Product Technical Specification and

Customer Design Guidelines

®

Wireless Microprocesso

WMP100/

Open AT® Software Suite v1.0

Reference: WM_DEV_WUP_PTS_005

Revision: 002

Date: March 19, 2007

Page 2

®

WMP100/Open AT

Software

Suite v1.0

Product Technical Specification &

Customer Design Guidelines

Reference: WM_DEV_WUP_PTS_005

Revision:

Date:

002

March 19, 2007

®

Powered by the Wavecom Open AT

Software Suite

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

confidential ©

Page : 1 / 152

Page 3

WM_DEV_WUP_PTS_005

March 19, 2007

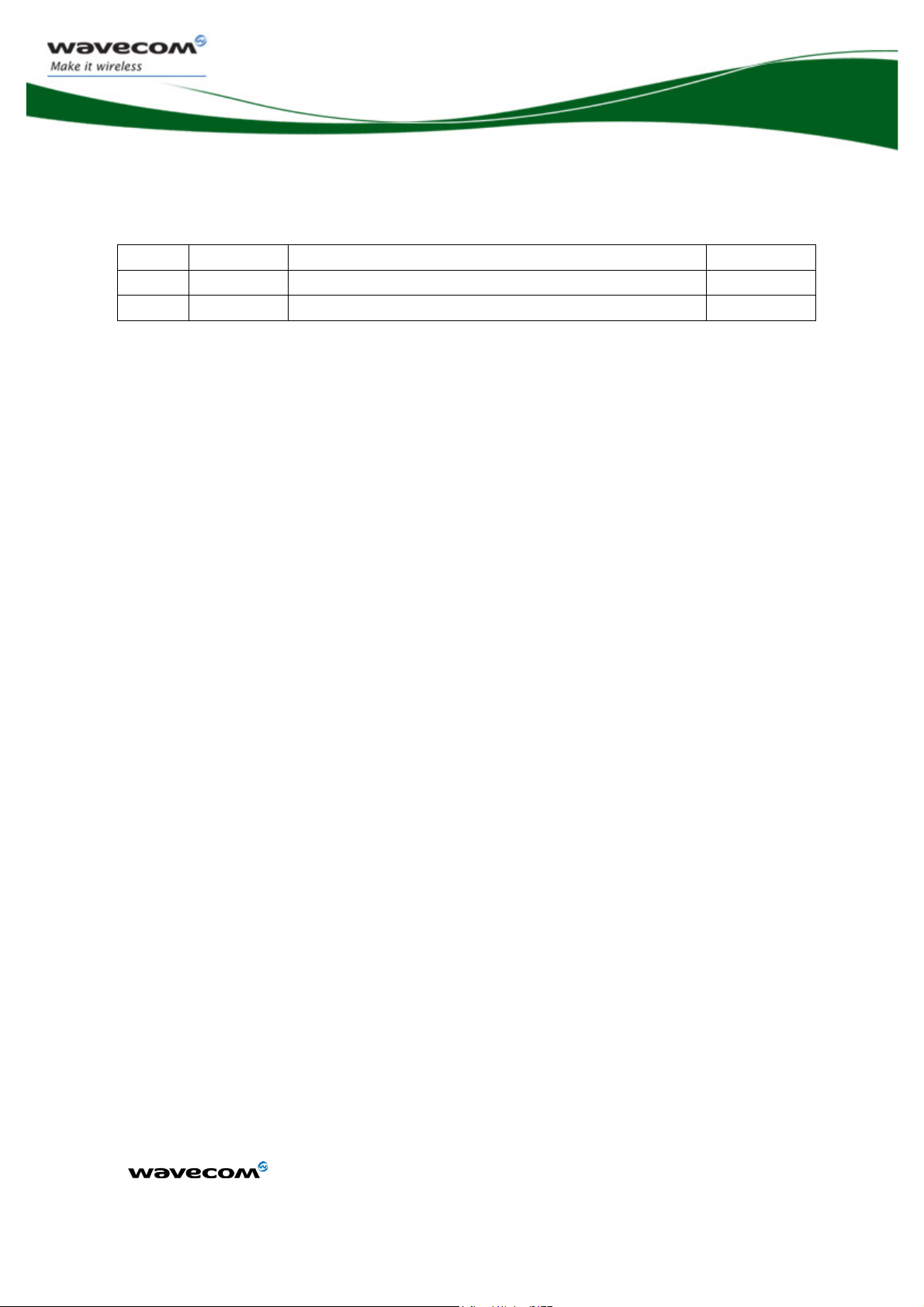

Document Information

Level Date History of the evolution

001 19/10/2006 Creation (Preliminary version)

002 19/03/2007 Updates

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 2 / 152

Page 4

WM_DEV_WUP_PTS_005

March 19, 2007

Overview

This document defines and specifies the WMP100/Open AT® Software Suite

v1.0 available in a GSM/GPRS Class 10 quad-band version.

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 3 / 152

Page 5

WM_DEV_WUP_PTS_005

March 19, 2007

Table of Contents

Document Information......................................................................... 2

Overview ............................................................................................. 3

Table of Contents................................................................................ 4

Table of Figures................................................................................. 10

Cautions ............................................................................................ 12

Trademarks ....................................................................................... 12

Copyright .......................................................................................... 12

1 References................................................................................ 13

1.1 Reference documents............................................................................13

1.1.1 WAVECOM reference documentation ............................................13

1.1.2 General reference documentation ..................................................13

1.2 List of abbreviations ..............................................................................14

2 General description................................................................... 17

2.1 General information...............................................................................17

2.1.1 Overall dimensions ........................................................................17

2.1.2 Environment and mechanics..........................................................17

2.1.3 GSM/GPRS Features ......................................................................17

2.1.4 Interfaces.......................................................................................18

2.1.5 Operating system ..........................................................................18

2.2 Functional description ...........................................................................19

2.2.1 RF functionalities ...........................................................................20

2.2.2 Baseband functionalities................................................................20

2.3 Software description .............................................................................20

3 Interfaces ................................................................................. 21

3.1 General Interfaces .................................................................................21

3.2 Power supply ........................................................................................22

3.2.1 Power supply description ..............................................................22

3.2.2 Power supply constraints on VBATT-RF ........................................22

3.2.3 Power supply constraints on VBATT-BB........................................23

3.2.4 Electrical characteristics ................................................................23

3.2.5 Pin description...............................................................................23

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 4 / 152

Page 6

WM_DEV_WUP_PTS_005

March 19, 2007

Application ....................................................................................24

3.2.6

3.3 Power consumption ..............................................................................25

3.3.1.1 Power consumption without Open AT® processing .................26

3.3.1.2 Power consumption with a Dhrystone Open AT® application...27

3.3.1.3 Consumption waveform samples.............................................28

3.3.1.3.1 Connected mode current waveform .......................................28

3.3.1.3.2 Slow Idle mode current waveform .........................................29

3.3.1.3.3 Fast Idle mode current waveform ..........................................30

3.3.1.3.4 Transfer mode Class 10 current waveform ............................31

3.4 Electrical information for digital I/O........................................................32

3.5 SPI Bus .................................................................................................34

3.5.1 Features ........................................................................................34

3.5.1.1 Characteristics .........................................................................34

3.5.1.2 SPI configuration .....................................................................34

3.5.1.3 SPI waveforms ........................................................................35

3.5.2 Pin description...............................................................................36

3.5.3 Application ....................................................................................36

3.5.3.1 4-wire interface .......................................................................36

3.5.3.2 3-wire interface .......................................................................37

3.6 I2C bus..................................................................................................38

3.6.1 Features ........................................................................................38

3.6.1.1 Characteristics .........................................................................38

3.6.1.2 I²C waveforms .........................................................................38

3.6.2 Pin description...............................................................................39

3.6.3 Application ....................................................................................39

3.7 Keyboard interface.................................................................................40

3.7.1 Features ........................................................................................40

3.7.2 Pin description...............................................................................41

3.7.3 Application ....................................................................................42

3.8 Main serial link (UART1)........................................................................42

3.8.1 Features ........................................................................................42

3.8.2 Pin description...............................................................................43

3.8.3 First download ..............................................................................45

3.8.4 Application ....................................................................................46

3.9 Auxiliary serial link (UART2) ..................................................................50

3.9.1 Features ........................................................................................50

3.9.2 Pin description...............................................................................51

3.9.3 Application ....................................................................................51

3.10 SIM Interface.........................................................................................52

3.10.1 Features ........................................................................................52

3.10.2 Pin description...............................................................................54

3.10.3 Application ....................................................................................54

3.11 General Purpose Input/Output ...............................................................56

3.11.1 Features ........................................................................................56

3.11.2 Pin description...............................................................................56

3.12 Analog to Digital Converter....................................................................58

3.12.1 Features ........................................................................................58

3.12.2 Pin description...............................................................................58

3.12.3 Application ....................................................................................59

3.13 Digital to Analog Converter....................................................................60

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 5 / 152

Page 7

WM_DEV_WUP_PTS_005

March 19, 2007

3.13.1

Features ........................................................................................60

3.13.2 Pin description...............................................................................60

3.14 Analogue audio interface.......................................................................61

3.14.1 Microphone Features .....................................................................61

3.14.1.1 Electrical characteristics...........................................................61

3.14.1.1.1 MIC1 Microphone Inputs ...................................................61

3.14.1.1.2 MIC2 Microphone Inputs ...................................................62

3.14.2 Speaker Features ...........................................................................64

3.14.2.1 Speakers Outputs Power .........................................................64

3.14.2.1.1 SPK1 Speaker Outputs.......................................................64

3.14.2.1.2 SPK2 Speaker Outputs......................................................66

3.14.3 Pin description...............................................................................67

3.14.4 Application ....................................................................................67

3.14.4.1 Microphone .............................................................................67

3.14.4.1.1 MIC2 Differential connection example................................67

3.14.4.1.2 MIC2 single-ended connection example ............................69

3.14.4.1.3 MIC1 Differential connection example................................70

3.14.4.1.4 MIC1 Single-ended connection example ............................72

3.14.4.2 Speaker ...................................................................................73

3.14.4.2.1 SPK2 Differential connection..............................................73

3.14.4.2.2 SPKx Single-ended connection ..........................................74

3.14.5 Design recommendation ................................................................74

3.14.5.1 General ....................................................................................74

3.14.5.2 Recommended microphone characteristics..............................74

3.14.5.3 Recommended speaker characteristics ....................................75

3.14.5.4 Recommended filtering components........................................75

3.14.5.5 Audio track and PCB layout recommendation ..........................77

3.15 PWM / Buzzer Output ...........................................................................78

3.15.1 Features ........................................................................................78

3.15.2 Pin description...............................................................................78

3.15.3 Application ....................................................................................79

3.16 Battery charging interface .....................................................................80

3.16.1 Feature ..........................................................................................80

3.16.1.1 Pre-Charging ...........................................................................81

3.16.1.2 Temperature monitoring ..........................................................81

3.16.2 Pin description...............................................................................82

3.16.3 Application ....................................................................................82

3.17 ON / ~OFF signal...................................................................................84

3.17.1 Features ........................................................................................84

3.17.2 Pin description...............................................................................84

3.17.3 Application ....................................................................................84

3.17.3.1 Power ON ................................................................................85

3.17.3.2 Power OFF...............................................................................87

3.18 BOOT signal ..........................................................................................88

3.18.1 Features ........................................................................................88

3.18.2 Pin description...............................................................................88

3.18.3 Application ....................................................................................88

3.19 Reset signals .........................................................................................89

3.19.1 Features ........................................................................................89

3.19.2 Pin description...............................................................................92

3.19.3 Application ....................................................................................93

3.20 External Interrupt ..................................................................................94

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 6 / 152

Page 8

WM_DEV_WUP_PTS_005

March 19, 2007

3.20.1

Features ........................................................................................94

3.20.2 Pin description...............................................................................94

3.20.3 Application ....................................................................................95

3.21 VCC_2V8 and VCC_1V8 output ..............................................................96

3.21.1 Features ........................................................................................96

3.21.2 Pin description...............................................................................96

3.21.3 Application ....................................................................................96

3.22 Real Time Clock.....................................................................................97

3.22.1 Features ........................................................................................97

3.22.2 Pin description...............................................................................97

3.22.3 Application ....................................................................................98

3.22.4 Design recommendation ................................................................98

3.23 BAT-RTC (Backup Battery) ....................................................................99

3.23.1 Features ........................................................................................99

3.23.2 Pin description.............................................................................100

3.23.3 Application ..................................................................................100

3.23.3.1 Super Capacitor .....................................................................100

3.23.3.2 Non Rechargeable battery......................................................101

3.23.3.3 Rechargeable battery cell .......................................................101

3.24 FLASH-LED signal ...............................................................................102

3.24.1 Features ......................................................................................102

3.24.2 Pin description.............................................................................103

3.24.3 Application ..................................................................................104

3.25 Digital audio interface (PCM) ...............................................................104

3.25.1 Features ......................................................................................104

3.25.2 Pin description.............................................................................107

3.25.3 Application TBD...........................................................................107

3.26 USB 2.0 interface ................................................................................107

3.26.1 Features ......................................................................................107

3.26.2 Pin description.............................................................................108

3.26.3 Application ..................................................................................109

3.27 Memory interface ................................................................................110

3.27.1 Features ......................................................................................111

3.27.1.1 Generic Description................................................................111

3.27.1.2 Case of ST 32/8 (M36W0R5030T0ZAQF) ..............................112

3.27.1.3 Access bus Waveform ...........................................................113

3.27.1.4 Flash space............................................................................116

3.27.1.5 RAM space ............................................................................116

3.27.1.6 16-bit wide data bus User Space ...........................................117

3.27.2 Electrical characteristics of the signals.........................................117

3.27.3 Pin description.............................................................................117

3.27.4 Application ..................................................................................120

3.27.5 Constraints ..................................................................................121

3.28 RF interface .........................................................................................124

3.28.1 RF connection..............................................................................124

3.28.2 RF performances .........................................................................124

3.28.3 Antenna specifications ................................................................125

3.28.4 Antenna.......................................................................................125

4 Consumption measurement procedure ................................... 127

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 7 / 152

Page 9

WM_DEV_WUP_PTS_005

March 19, 2007

Hardware configuration.......................................................................127

4.1

4.1.1 Equipment ...................................................................................127

4.1.2 Wireless Microprocessor motherboard ........................................129

4.1.3 SIM cards used ...........................................................................130

4.2 Software configurations ......................................................................130

4.2.1 Wireless Microprocessor configuration ........................................130

4.2.2 Equipment configuration .............................................................131

4.3 Template .............................................................................................132

5 Technical specifications ......................................................... 133

5.1 Ball Grid Array pin out .........................................................................133

5.2 Environmental Specifications...............................................................139

5.3 MSL level ............................................................................................140

5.4 Mechanical specifications....................................................................140

5.4.1 Physical characteristics................................................................140

5.4.2 Mechanical drawings ..................................................................140

5.4.3 Mechanical constraints................................................................143

5.5 PCB specifications...............................................................................143

6 Peripheral devices references ................................................. 143

6.1 SIM Card Reader .................................................................................143

6.2 Microphone.........................................................................................143

6.3 Speaker ...............................................................................................143

6.4 Antenna Cable.....................................................................................144

6.5 GSM antenna ......................................................................................144

7 Noises and design................................................................... 145

7.1 EMC recommendations .......................................................................145

7.2 Power Supply......................................................................................145

8 Appendix................................................................................. 146

8.1 Standards and Recommendations.......................................................146

8.2 Safety recommendations (for information only) ...................................150

8.2.1 RF safety .....................................................................................150

8.2.1.1 General ..................................................................................150

8.2.1.2 Exposure to RF energy...........................................................150

8.2.1.3 Efficient terminal operation ....................................................150

8.2.1.4 Antenna care and replacement ..............................................151

8.2.2 General safety..............................................................................151

8.2.2.1 Driving...................................................................................151

8.2.2.2 Electronic devices ..................................................................151

8.2.2.3 Vehicle electronic equipment .................................................151

8.2.2.4 Medical electronic equipment ................................................151

8.2.2.5 Aircraft ..................................................................................152

8.2.2.6 Children .................................................................................152

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 8 / 152

Page 10

WM_DEV_WUP_PTS_005

March 19, 2007

8.2.2.7

Blasting areas ........................................................................152

8.2.2.8 Potentially explosive atmospheres .........................................152

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 9 / 152

Page 11

WM_DEV_WUP_PTS_005

March 19, 2007

Table of Figures

Figure 1 : Functional architecture ................................................................... 19

Figure 2 : Power supply during burst emission ..............................................22

Figure 3 : Reject filter diagram........................................................................ 24

Figure 4: SPI Timing diagrams, Mode 0, Master, 4 wires ............................... 35

Figure 5: Example of 4-wire SPI bus application............................................. 36

Figure 6: Example of 3-wire SPI bus application............................................. 37

Figure 7: I²C Timing diagrams, Master ........................................................... 38

Figure 8: First example of I²C bus application................................................. 39

Figure 9: Second example of I²C bus application ............................................ 40

Figure 10: Example of keyboard implementation ............................................ 42

Figure 11: Example of UART1 connection for download with another device on

the link...................................................................................................... 45

Figure 12: Example of RS-232 level shifter implementation for UART1........... 46

Figure 13: Example of V24/CMOS serial link implementation for UART1 ........ 48

Figure 14: Example of full modem V24/CMOS serial link implementation for

UART1 ...................................................................................................... 49

Figure 15: Example of RS-232 level shifter implementation for UART2........... 51

Figure 16: Example of SIM Socket implementation......................................... 54

Figure 17: Example of MIC2 input differential connection with LC filter.......... 67

Figure 18: Example of MIC2 input differential connection without LC filter..... 68

Figure 19: Example of MIC2 input single-ended connection with LC filter ...... 69

Figure 20: Example of MIC2 input single-ended connection without LC filter . 69

Figure 21: Example of MIC1 input differential connection with LC filter.......... 70

Figure 22: Example of MIC1 input differential connection without LC filter..... 71

Figure 23: Example of MIC1 input single-ended connection with LC filter ...... 72

Figure 24: Example of MIC1 input single-ended connection without LC filter . 72

Figure 25: Example of Speaker differential connection.................................... 73

Figure 26: Example of Speaker single-ended connection ................................ 74

Figure 27: Microphone ................................................................................... 75

Figure 28: Audio track design......................................................................... 77

Figure 29: Example of buzzer implementation ................................................ 79

Figure 30: Example of LED driven by the BUZZ-OUT output........................... 79

Figure 31: Charging block diagram................................................................. 80

Figure 32: Charging schematic for Li-Ion ........................................................ 82

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 10 / 152

Page 12

WM_DEV_WUP_PTS_005

March 19, 2007

Figure 33: Example of ON/~OFF pin connection ............................................. 84

Figure 34 : Power-ON sequence (no PIN code activated) ................................ 85

Figure 35 : Power-OFF sequence ................................................................... 87

Figure 36: Example of BOOT pin implementation ........................................... 88

Figure 37 : Reset functional block................................................................... 89

Figure 38 : Reset waveform events ................................................................ 90

Figure 39 : Reset sequence waveform............................................................ 91

Figure 40 : BOOT sequence waveform .......................................................... 92

Figure 41: Example of ~RESET pin connection with push button configuration

................................................................................................................. 93

Figure 42: Example of ~RESET pin connection with transistor configuration.. 93

Figure 43: Example of INTx driving example with open collector.................... 95

Figure 44: Example of INTx driving example with open collector.................... 95

Figure 45 : PCB lay out for the crystal MS2V-T1S .......................................... 98

Figure 46 : Real Time Clock power supply...................................................... 99

Figure 47: RTC supplied by a gold capacitor................................................. 100

Figure 48: RTC supplied by a non rechargeable battery................................ 101

Figure 49: RTC supplied by a rechargeable battery cell ................................ 101

Figure 50 : FLASH-LED state during RESET and Initialization time ............... 103

Figure 51: Example of GSM activity status implementation.......................... 104

Figure 52 : PCM Frame waveform................................................................ 106

Figure 53 : PCM Sampling waveform........................................................... 106

Figure 54: Example of USB implementation.................................................. 109

Figure 55: Memory bus ................................................................................ 110

Figure 56: Read synchronous timing ............................................................ 113

Figure 57: Write synchronous timing ...........................................................114

Figure 58: Read / Write Asynchronous timing .............................................. 115

Figure 59: Memory connection schematic .................................................... 120

Figure 60: Memory PCB ............................................................................... 123

Figure 61: Antenna and ground balls placement .......................................... 126

Figure 62: RF 50 ohms embedded line ......................................................... 126

Figure 63: Antenna connection point keep away area ..................................126

Figure 64: RF connector and ESD protection example .................................. 127

Figure 65: Typical hardware configuration ................................................... 128

Figure 66 : Environmental classes ................................................................ 139

Figure 67 : Mechanical drawing ................................................................... 141

Figure 68 : Mechanical drawing ................................................................... 142

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 11 / 152

Page 13

WM_DEV_WUP_PTS_005

March 19, 2007

Cautions

This platform contains a modular transmitter. This device is used for wireless

applications. Note that all electronics parts and elements are ESD sensitive.

Information provided herein by WAVECOM is accurate and reliable. However

no responsibility is assumed for its use and any of such WAVECOM

information is herein provided “as is” without any warranty of any kind,

whether express or implied.

General information about WAVECOM and its range of products is available at

the following internet address:

http://www.wavecom.com

Trademarks

®, WAVECOM®, WISMO®, Open AT®, Wireless Microprocessor®, Wireless

®

, and certain other trademarks and logos appearing on this document, are

CPU

filed or registered trademarks of Wavecom S.A. in France or in other countries.

All other company and/or product names mentioned may be filed or registered

trademarks of their respective owners.

Copyright

This manual is copyrighted by WAVECOM with all rights reserved. No part of

this manual may be reproduced in any form without the prior written

permission of WAVECOM. No patent liability is assumed with respect to the

use of their respective owners.

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 12 / 152

Page 14

WM_DEV_WUP_PTS_005

March 19, 2007

1 References

1.1 Reference documents

For more details, several documents are referenced in this specification. The

WAVECOM documents references herein are provided in the WAVECOM

documentation package; the general reference documents which are not

WAVECOM owned are not provided in the documentation package.

1.1.1 WAVECOM reference documentation

®

[1] Wireless Microprocessor

Reference: WM_DEV_WUP_PTS_004

[2] WMP100 Development Kit User Guide

Reference: WM_DEV_WUP_UGD_001

WMP100 Technical Specification

®

[3] AT Command Interface Guide for Open AT

Firmware v6.5

Reference: WM_DEV_OAT_UGD_035

1.1.2 General reference documentation

[4] “I²C Bus Specification”, Version 2.0, Philips Semiconductor 1998

[5] ISO 7816-3 Standard

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 13 / 152

Page 15

WM_DEV_WUP_PTS_005

March 19, 2007

1.2 List of abbreviations

Abbreviation Definition

AC Alternative Current

ADC Analog to Digital Converter

A/D Analog to Digital conversion

AF Audio-Frequency

AT ATtention (prefix for modem commands)

AUX AUXiliary

CAN Controller Area Network

CB Cell Broadcast

CEP Circular Error Probable

CLK CLocK

CMOS Complementary Metal Oxide Semiconductor

CS Coding Scheme

CTS Clear To Send

DAC Digital to Analogue Converter

dB Decibel

DC Direct Current

DCD Data Carrier Detect

DCE Data Communication Equipment

DCS Digital Cellular System

DR Dynamic Range

DSR Data Set Ready

DTE Data Terminal Equipment

DTR Data Terminal Ready

EFR Enhanced Full Rate

E-GSM Extended GSM

EMC ElectroMagnetic Compatibility

EMI ElectroMagnetic Interference

EMS Enhanced Message Service

EN ENable

ESD ElectroStatic Discharges

FIFO First In First Out

FR Full Rate

FTA Full Type Approval

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 14 / 152

Page 16

WM_DEV_WUP_PTS_005

March 19, 2007

Abbreviation

Definition

GND GrouND

GPI General Purpose Input

GPC General Purpose Connector

GPIO General Purpose Input Output

GPO General Purpose Output

GPRS General Packet Radio Service

GPS Global Positioning System

GSM Global System for Mobile communications

HR Half Rate

I/O Input / Output

LED Light Emitting Diode

LNA Low Noise Amplifier

MAX MAXimum

MIC MICrophone

MIN MINimum

MMS Multimedia Message Service

MO Mobile Originated

MT Mobile Terminated

na Not Applicable

NF Noise Factor

NMEA National Marine Electronics Association

NOM NOMinal

NTC Négative Temperature Coefficient

PA Power Amplifier

Pa Pascal (for speaker sound pressure measurements)

PBCCH Packet Broadcast Control CHannel

PC Personal Computer

PCB Printed Circuit Board

PDA Personal Digital Assistant

PFM Power Frequency Modulation

PSM Phase Shift Modulation

PWM Pulse Width Modulation

RAM Random Access Memory

RF Radio Frequency

RFI Radio Frequency Interference

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 15 / 152

Page 17

WM_DEV_WUP_PTS_005

March 19, 2007

Abbreviation

Definition

RHCP Right Hand Circular Polarization

RI Ring Indicator

RST ReSeT

RTC Real Time Clock

RTCM Radio Technical Commission for Maritime services

RTS Request To Send

RX Receive

SCL Serial CLock

SDA Serial DAta

SIM Subscriber Identification Module

SMS Short Message Service

SPI Serial Peripheral Interface

SPL Sound Pressure Level

SPK SPeaKer

SRAM Static RAM

TBC To Be Confirmed

TDMA Time Division Multiple Access

TP Test Point

TVS Transient Voltage Suppressor

TX Transmit

TYP TYPical

UART Universal Asynchronous Receiver-Transmitter

USB Universal Serial Bus

USSD Unstructured Supplementary Services Data

VSWR Voltage Standing Wave Ratio

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 16 / 152

Page 18

WM_DEV_WUP_PTS_005

March 19, 2007

2 General description

2.1 General information

The WMP100 Wireless Microprocessor® is a self-contained E-GSM/GPRS

900/1800 and 850/1900 quad-band processor, including the characteristics

listed in the subsection below.

2.1.1 Overall dimensions

• Length: 25 mm

• Width: 25 mm

• Thickness: 3.65 mm

• Weight: 4.25 g

• Package: WMBGA576 / ball Ø 0,6 mm @ pitch 1mm

2.1.2 Environment and mechanics

• Green policy: Restriction of Hazardous Substances in Electrical and

Electronic Equipment (RoHS) compliant

• Complete shielding

The WMP100 is compliant with RoHS Directive 2002/95/EC which sets limits

for the use of certain restricted hazardous substances. This directive states

that “from 1st July 2006, new electrical and electronic equipment put on the

market does not contain lead, mercury, cadmium, hexavalent chromium,

polybrominated biphenyls (PBB) or polybrominated diphenyl ethers (PBDE)”.

2.1.3 GSM/GPRS Features

• 2 Watts EGSM 900/GSM 850 radio section running under 3.6 Volts

• 1 Watt GSM1800/1900 radio section running under 3.6 Volts

• Hardware GPRS class 10 capable

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 17 / 152

Page 19

WM_DEV_WUP_PTS_005

March 19, 2007

2.1.4 Interfaces

• Digital section running under 2.8 Volts and 1.8Volts.

• 3V/1V8 SIM interface

• 1.8V Parallel interface for devices (memories, LCD…)

• Power supply

• Watchdog

• Serial links (UART)

• Analogue audio

• ADC / DAC

• PCM digital audio

• Keyboard

• USB 2.0 slave

• Serial buses (I2C,SPI)

• PWM

• GPIOs

2.1.5 Operating system

• Real Time Clock with calendar

• Echo Cancellation + noise reduction (quadri codec)

• Full GSM or GSM/GPRS Operating System stack

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 18 / 152

Page 20

WM_DEV_WUP_PTS_005

March 19, 2007

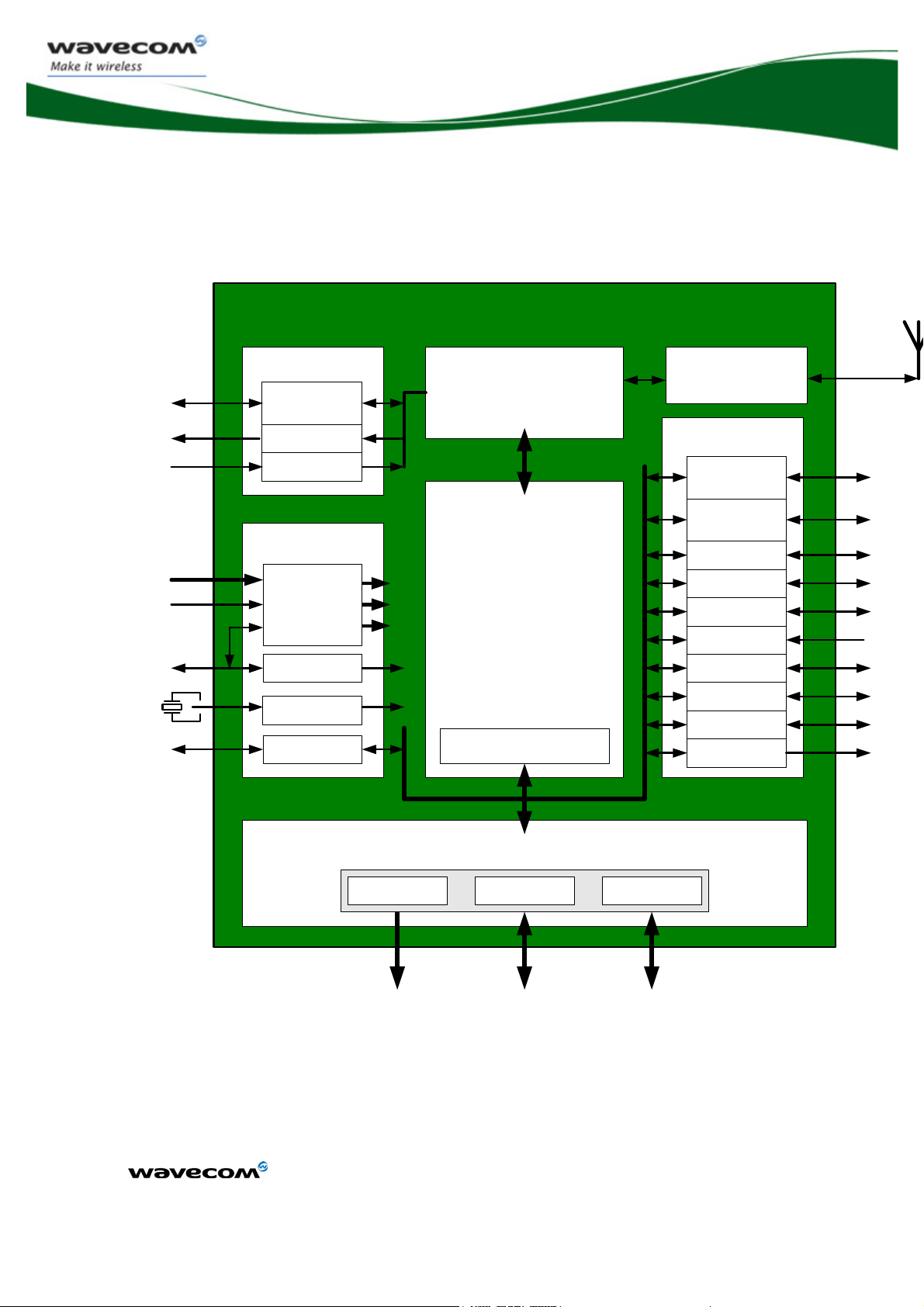

2.2 Functional description

The global architecture of WMP100 is described below:

WMP100

32768

kHz

Analog Interfaces

AUDIO

CH1 & CH2

DAC

ADCs

Control &

Power

power

supplys

reset

RTC

Charging

DSP

core

ARM 946

32bit

core

AHB bus

Radio

GSM / GPRS

Digital Interfaces

UART

1,2

SPI

1,2

PCM

SIM

I²C

ITs

USB 2.0

KEYPAD

GPIOs

PWM

Extended Memory Bridge

ControlDataAddress

Figure 1 : Functional architecture

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 19 / 152

Page 21

WM_DEV_WUP_PTS_005

March 19, 2007

2.2.1 RF functionalities

The Radio Frequency (RF) range complies with the Phase II EGSM 900/DCS

1800 and GSM 850/PCS 1900 recommendation. The frequencies are listed in

the table below.

Transmit band (Tx) Receive band (Rx)

GSM 850 824 to 849 MHz 869 to 894 MHz

E-GSM 900 880 to 915 MHz 925 to 960 MHz

DCS 1800 1710 to 1785 MHz 1805 to 1880 MHz

PCS 1900 1850 to 1910 MHz 1930 to 1990 MHz

The RF part is based on a specific quad band chip including:

• a Digital low-IF receiver

• a Quad-band LNAs (Low Noise Amplifier)

• an Offset PLL (Phase Locked Loop) transmitter

• a Frequency synthesizer

• a Digitally controlled crystal oscillator (DCXO)

• a Tx/Rx FEM (Front-End Wireless Microprocessor

®

) for quad-band

GSM/GPRS

2.2.2 Baseband functionalities

The Baseband is composed of an ARM9, a DSP and an analog element (with

audio signals, I/Q signals, ADC, DAC).

The core power supply is to 1.8 volts. The analog power supply is to 2.8v

2.3 Software description

The Open AT® Software Suite v1.0 is the software package that supports

WMP100. It consists of:

®

• An Open AT

command interface over a serial port or USB.

• An Open AT

applications (telemetry, multimedia, automotive…)

• An Open AT

and debugs applications over the Open AT

• Several Open AT

that are able to run over the Open AT

Firmware v6.5 which drives the WMP100 thanks to an AT

®

Operating System (OS) v5.0 which runs various types of

®

Integrated Development Environment (IDE) which builds

®

plug-ins which are software provided by Wavecom

®

Operating System

®

Operating System

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 20 / 152

Page 22

WM_DEV_WUP_PTS_005

March 19, 2007

3 Interfaces

3.1 General Interfaces

The WMP100 is provided with a “Development Kit Wireless Microprocessor®”

containing an access to the all interfaces.

The available interfaces are described in the table below.

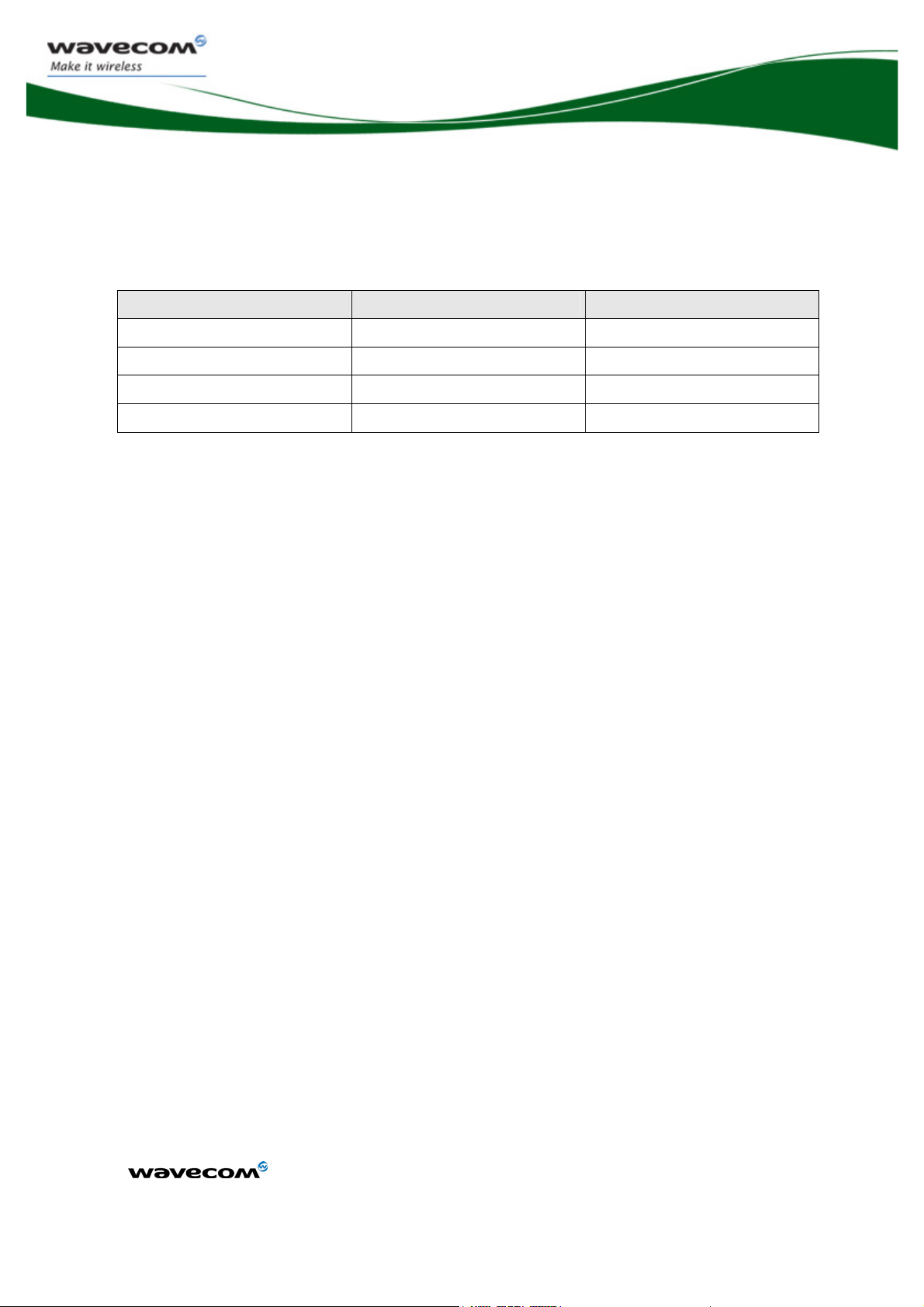

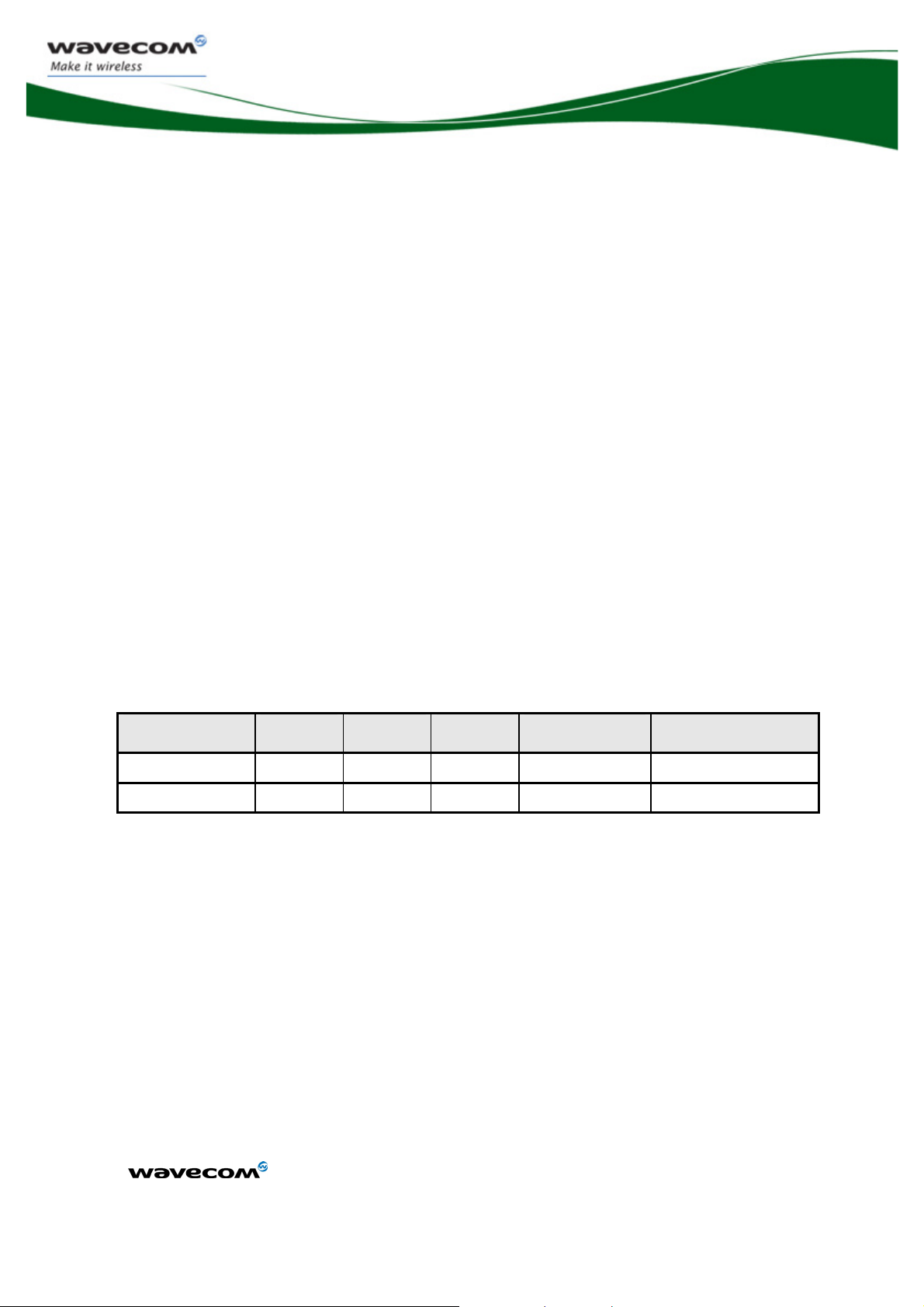

chapter Name Driven by

18.5.1 SPI Bus X X

18.5.2 I2C Bus X X

11 Keyboard Interface X X

12.2 Main Serial Link X X

13.2 Auxiliary Serial Link X X

14 SIM Interface X X

3 General Purpose IO X X

18.3 Analog to Digital

Converter

18.4 Digital to Analog

Converter

16 Analog audio Interface

9 PWM / Buzzer Output X X

18.3.1 Battery charging

interface

18.7 External Interruption X X

18.1 VCC_2V8 and

VCC_1V8

17 Real Time Clock X X

18.2 BAT-RTC (Backup

Battery)

8 FLASH-LED signal X X

18.6 Digital Audio Interface

(PCM)

15 USB 2.0 Interface X X

4 Memory interface

(on parallel interface)

Open AT®

Firmware

v6.5

X X

X X

X X

X X

X X

X X

X X

X X

Not

driven by

Open AT®

Firmware

v6.5

Driven by

Open AT®

OS v5.0

Not

driven by

Open AT®

OS v5.0

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 21 / 152

Page 23

WM_DEV_WUP_PTS_005

March 19, 2007

3.2 Power supply

3.2.1 Power supply description

The power supply is one of the key elements in the design of a GSM terminal.

The WMP100 is powered by a single power supply VBATT. This power supply

feeds two inputs to the supply, VBATT-BB and VBATT-RF.

VBATT-RF powers all the radio components of the WMP100. It has to be

carefully designed because most of the current is transmitted through this

input. The VBATT-RF current is bursted due to the GSM / GPRS transmission

protocol.

VBATT-BB supplies the digital part of the WMP100. VBATT-BB is directly

connected to the internal power management unit of the WMP100. This unit

controls the VBATT-BB voltage and provides the power supplies like VCC_1V8

and VCC_2V8.

Note: The VBATT-BB input generates noise, so the VBATT must be filtered by a

band reject filter.

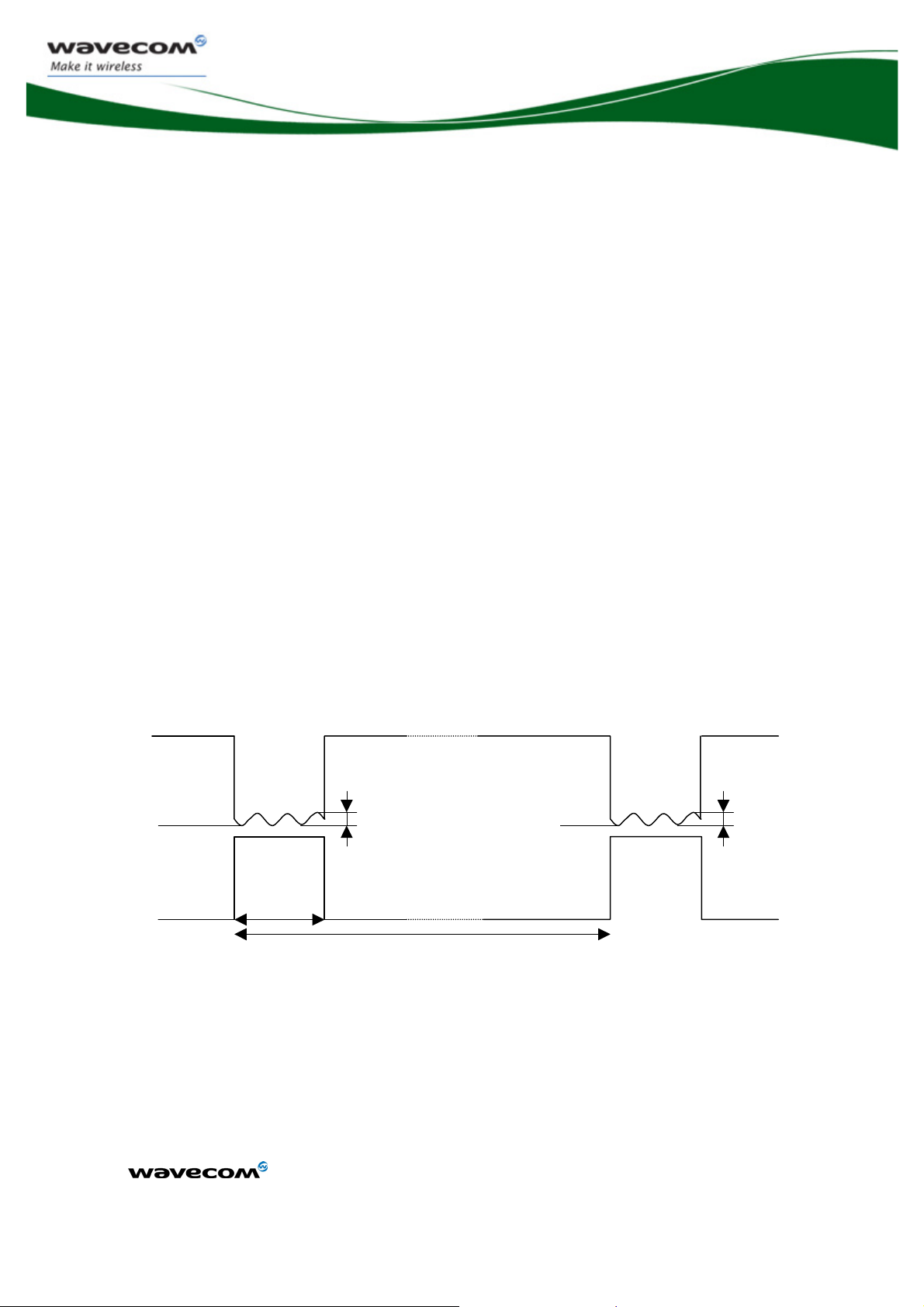

3.2.2 Power supply constraints on VBATT-RF

Due to the bursted emission in GSM / GPRS, the power supply must be able to

deliver high current peaks in a short time. During the peaks the ripple (U

the supply voltage must not exceed a certain limit (see

voltage

for details).

Table 1 Power supply

ripp

) on

• In communication mode, a GSM/GPRS class 2 terminal emits 577μs

radio bursts every 4.615ms. (See

VBATT-RFT

t = 577 μs

Uripp

T = 4,615 ms

Figure 2 below.)

Uripp

Figure 2 : Power supply during burst emission

• In communication mode, a GPRS class 10 terminal emits 1154μs radio

bursts every 4.615ms.

VBATT-RF:

• supplies the RF components with 3.6 V directly. It is essential to keep a

minimum voltage ripple at this connection in order to avoid any phase

error.

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 22 / 152

Page 24

WM_DEV_WUP_PTS_005

March 19, 2007

The RF Power Amplifier current (1.5 A peak in GSM /GPRS mode) flows

with a ratio of:

o 1/8 of the time (around 577μs every 4.615ms for GSM /GPRS cl. 2)

and

o 2/8 of the time (around 1154μs every 4.615ms for GSM /GPRS cl.

10).

The rising time is around 10μs.

3.2.3 Power supply constraints on VBATT-BB

The VBATT-BB input is used as well to supply the WMP100 core as well to

monitor the level voltage of VBATT.

VBATT-BB is internally connected to several regulators and to a switching

regulator which provides the VCC_1V8 voltage internally. Because the

switching regulator generates perturbation on the VBATT signal, it is

mandatory to add an external reject filter between VBATT and VBATT-BB.

3.2.4 Electrical characteristics

Input power Supply Voltage

V

V

MIN

NOM

V

I

MAX

Ripple max (U

MAX

ripp

)

VBATT-BB 3.2 3.6 4.8 0.3 A (TBC) (TBD)

VBATT-RF

1,2

3.2 3.6 4.8 1.5 A (TBC) 10mV(TBC)

Table 1 Power supply voltage

(1): This value has to be guaranteed during the burst (with 1.5A Peak in GSM

or GPRS mode)

(2): Maximum operating Voltage Stationary Wave Ratio (VSWR) 2:1

When powering the WMP100 with a battery, the total impedance

(battery+protections+PCB) should be <150 mOhms.

3.2.5 Pin description

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 23 / 152

Page 25

WM_DEV_WUP_PTS_005

March 19, 2007

Signal Pin number

VBATT-BB

VBATT-RF

AC1,AC2,AD1,AD2

A12,A13,A14,B12,B13,B14

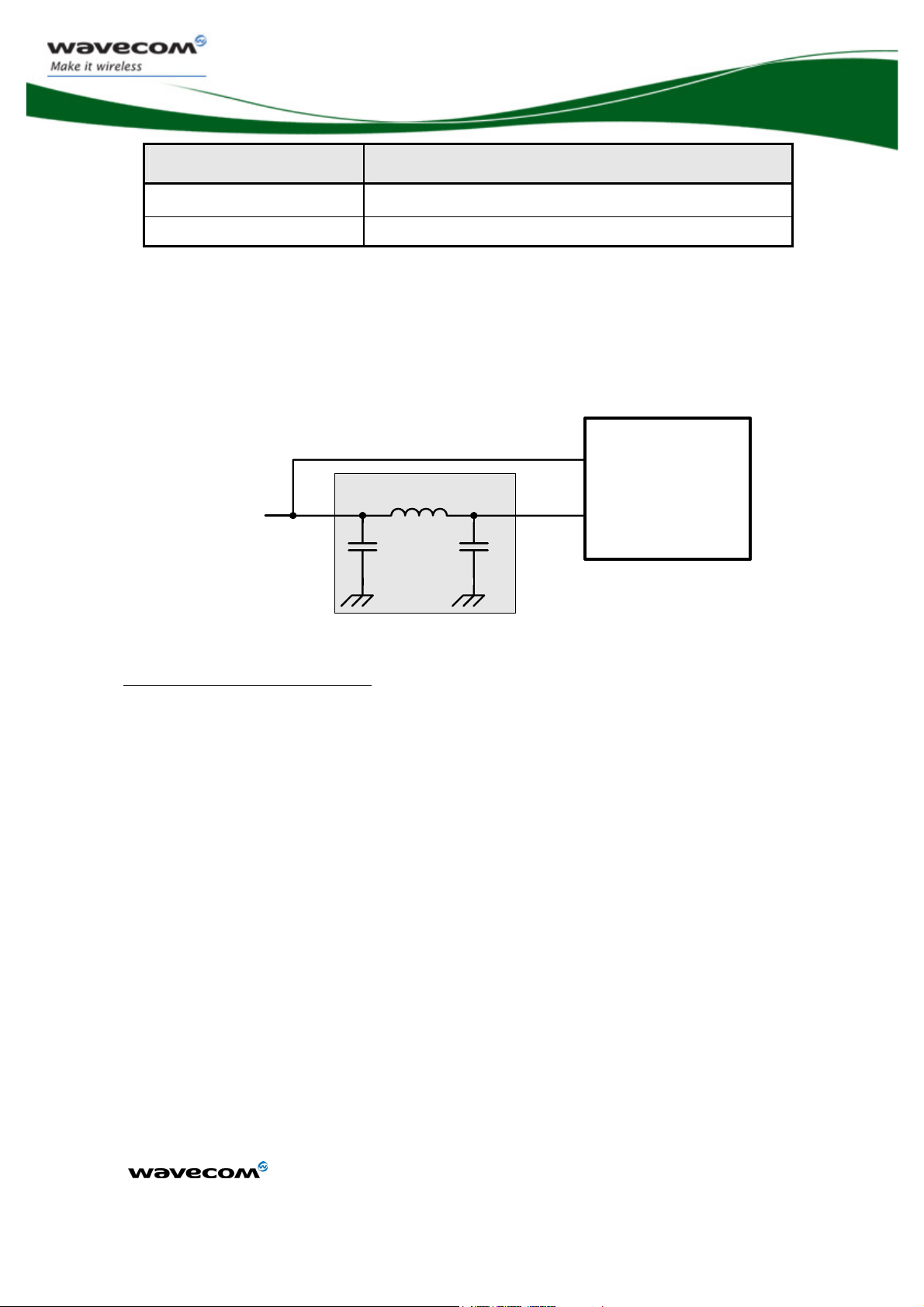

3.2.6 Application

The reject filter must be connected between VBATT and VBATT-BB.

VBATT-RF

VBATT

Filter

C1 C2

L1

VBATT-BB

WMP100

Figure 3 : Reject filter diagram

Recommended components:

C1, C2: 10μF +/-20%

o GRM21BR60J106KE19L from MURATA

o CM21X5R106M06AT from KYOCERA

o JMK212BJ106MG-T from TAYO YUDEN

o C2012X5R0J106MT from TDK

L1: 220nH +/-5%

o 0805CS-221XJLC from COILCRAFT

o 0805G221J E from STETCO

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 24 / 152

Page 26

WM_DEV_WUP_PTS_005

March 19, 2007

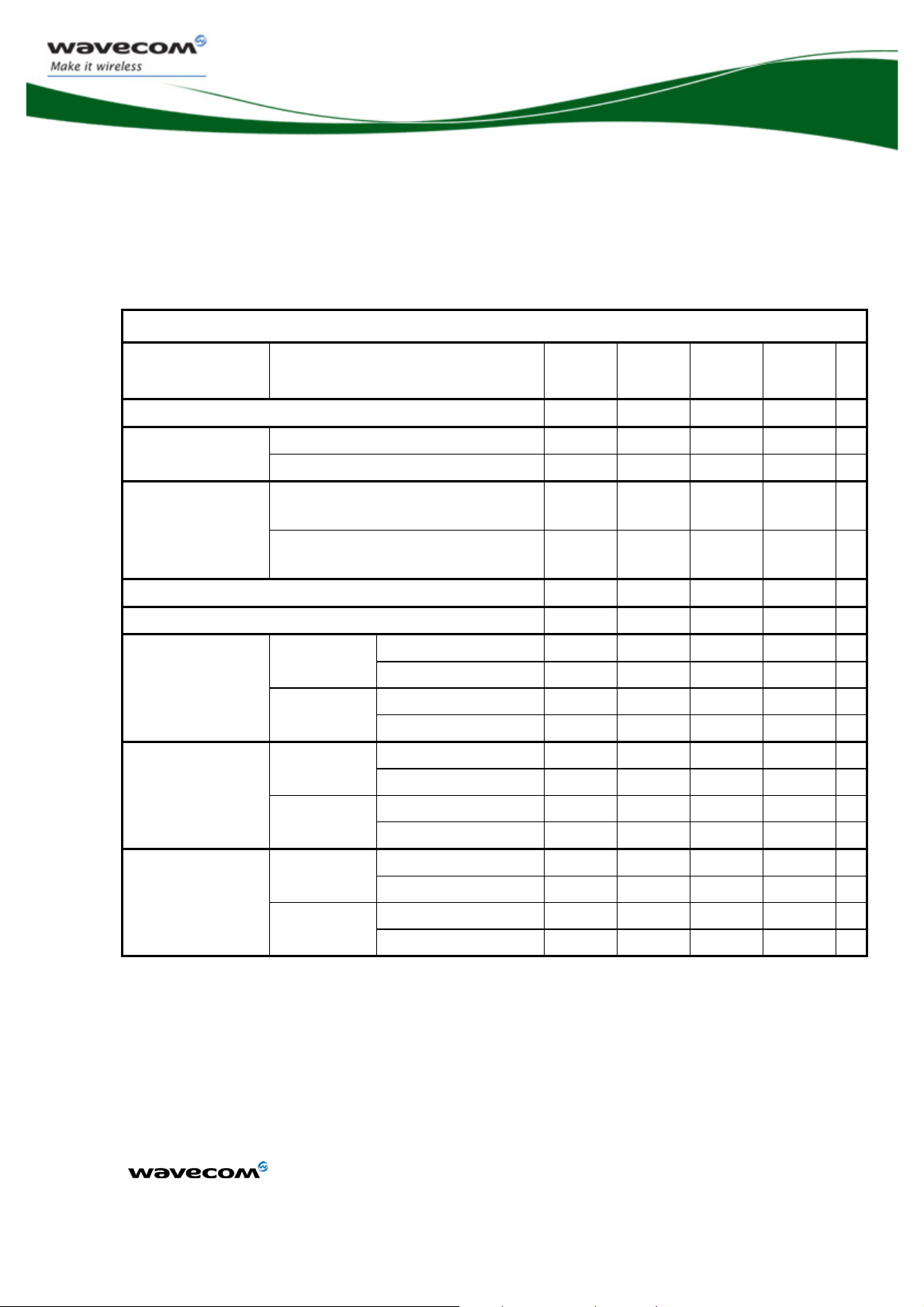

3.3 Power consumption

Power consumption depends on the configuration used. It is for this reason

that the following consumption values are given for each mode, RF band and

type of software used (with or without an Open AT

Note: All of the following information is given assuming a 50 Ω RF output.

The following consumption values were obtained by performing measurements

on WMP100 samples at a temperature of 25° C.

®

application).

Three VBATT values are used to measure the consumption, VBATT

VBATT

(4.8V) and VBATT

MAX

(3.6V).

TYP

(3.2V),

MIN

The average current is given for the three VBATT values and the peak current

given is the maximum current peak measured with the three VBATT voltages.

For a more detailed description of the operating modes, (refer to the document

[3] AT Command Interface Guide for Open AT® Firmware v6.5).

For more information about the consumption measurement procedure, refer to

§ 4.

All following consumption measurement values have to be confirmed.

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 25 / 152

Page 27

WM_DEV_WUP_PTS_005

March 19, 2007

®

3.3.1.1 Power consumption without Open AT

processing

The following measurement results are relevant when:

®

¾ There is no Open AT

®

¾ The Open AT

application is disabled

¾ No processing is required by the Open AT

application

®

application

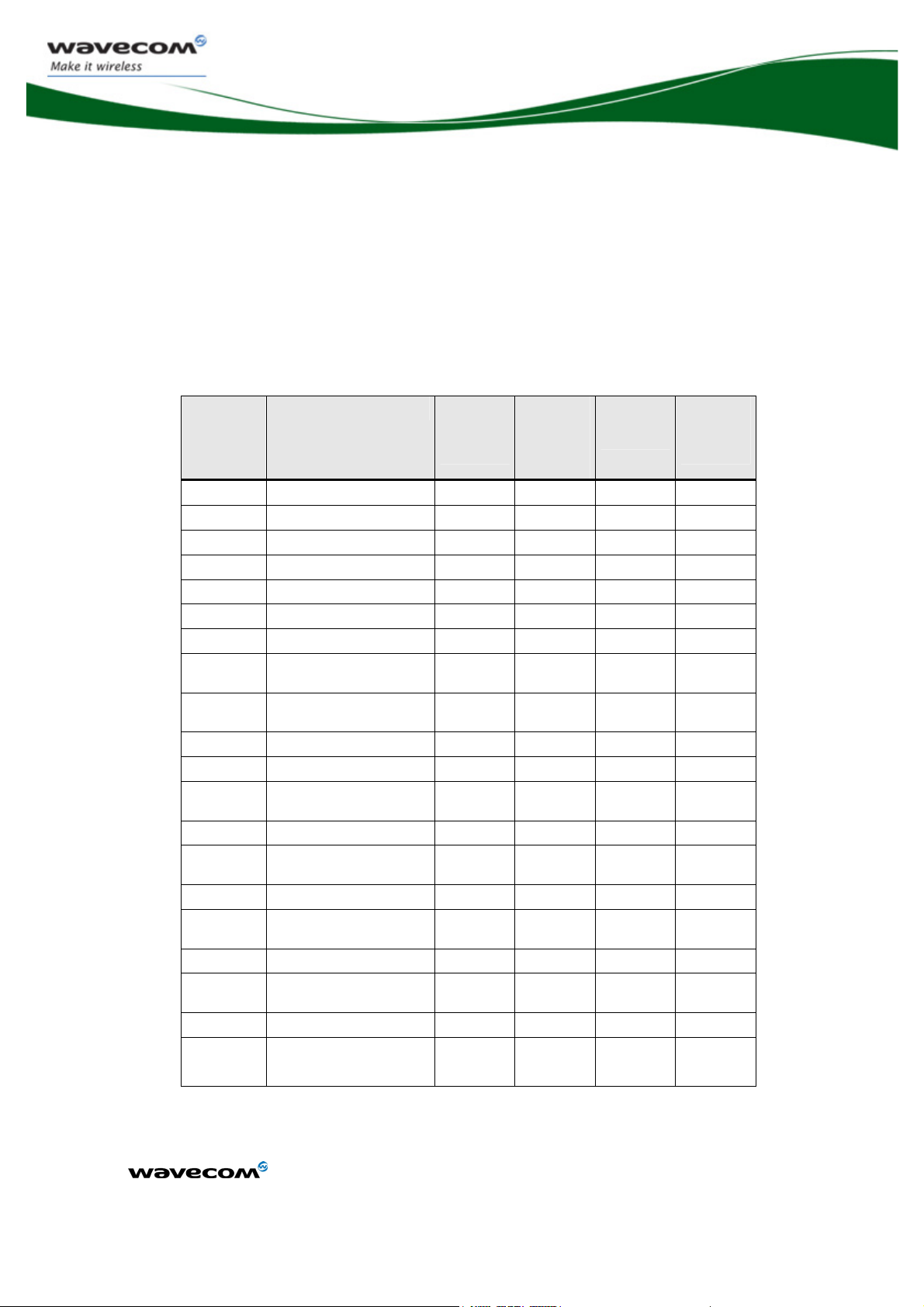

Power consumption without Open AT® processing

I

Operating mode Parameters

MIN

average

VBATT=4,8V

I

NOM

average

VBATT=3,6V

I

MAX

average

VBATT=3,2V

I

MAX

peak

unit

Alarm Mode

Fast Idle Mode

Slow Idle Mode 1

Fast Standby Mode

Slow Standby Mode

Connected Mode

Transfer Mode

class 8 (4Rx/1Tx)

Transfer Mode

class 10 (3Rx/2Tx)

21

Paging 9 (Rx burst occurrence ~2s) 15

Paging 2 (Rx burst occurrence ~0,5s) 17

Paging 9 (Rx burst occurrence ~2s)

Paging 2 (Rx burst occurrence ~0,5s)

1.5

(1.5 to 1.75)

4

(4 to 4.3)

30

1.4

850/900 MHz

PCL5 (TX power 33dBm) 210

PCL19 (TX power 5dBm) 81

PCL0 (TX power 30dBm) 145

1800/1900 MHz

PCL15 (TX power 0dBm) 77

850/900 MHz

gam. 3(TX power 33dBm) 201

gam.17(TX power 5dBm) 78

gam.3(TX power 30dBm) 138

1800/1900 MHz

gam.18(TX power 0dBm) 74

850/900 MHz

gam.3 (TX power 33dBm) 364

gam.17 (TX power 5dBm) 112

gam.3 (TX power 30dBm) 237

1800/1900 MHz

gam.18 (TX power 0dBm) 104

16

17

18

1.6

(1.6 to 1.9)

4.4

(4.4 to 4.75)

36

1.4

218

89

153

85

209

85

146

81

372

120

245

111

15 µA

18 160 RX mA

19 160 RX mA

1.7

(1.7 to 2.05)

4.6

(4.6 to 4.95)

160

160

RX

RX

39 mA

1.5 mA

222 1450 TX mA

92 270 TX mA

157 850 TX mA

88 250

TX

213 1450 TX mA

88 270

TX

149 850 TX mA

84 250

TX

378 1450 TX mA

123 270 TX mA

248 850 TX mA

115 250

TX

mA

mA

mA

mA

mA

mA

means that the current peak is the RF transmission burst (Tx burst)

TX

means that the current peak is the RF reception burst (Rx burst)

RX

1

Slow Idle Mode consumption depends on the SIM card used. Some SIM cards

respond faster than others, in which case the longer the response time is, the

higher the consumption is. These measurements were performed with a large

number of 3V SIM cards, the results in brackets are the minimum and

maximum currents measured from among all the SIMs used.

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 26 / 152

Page 28

WM_DEV_WUP_PTS_005

March 19, 2007

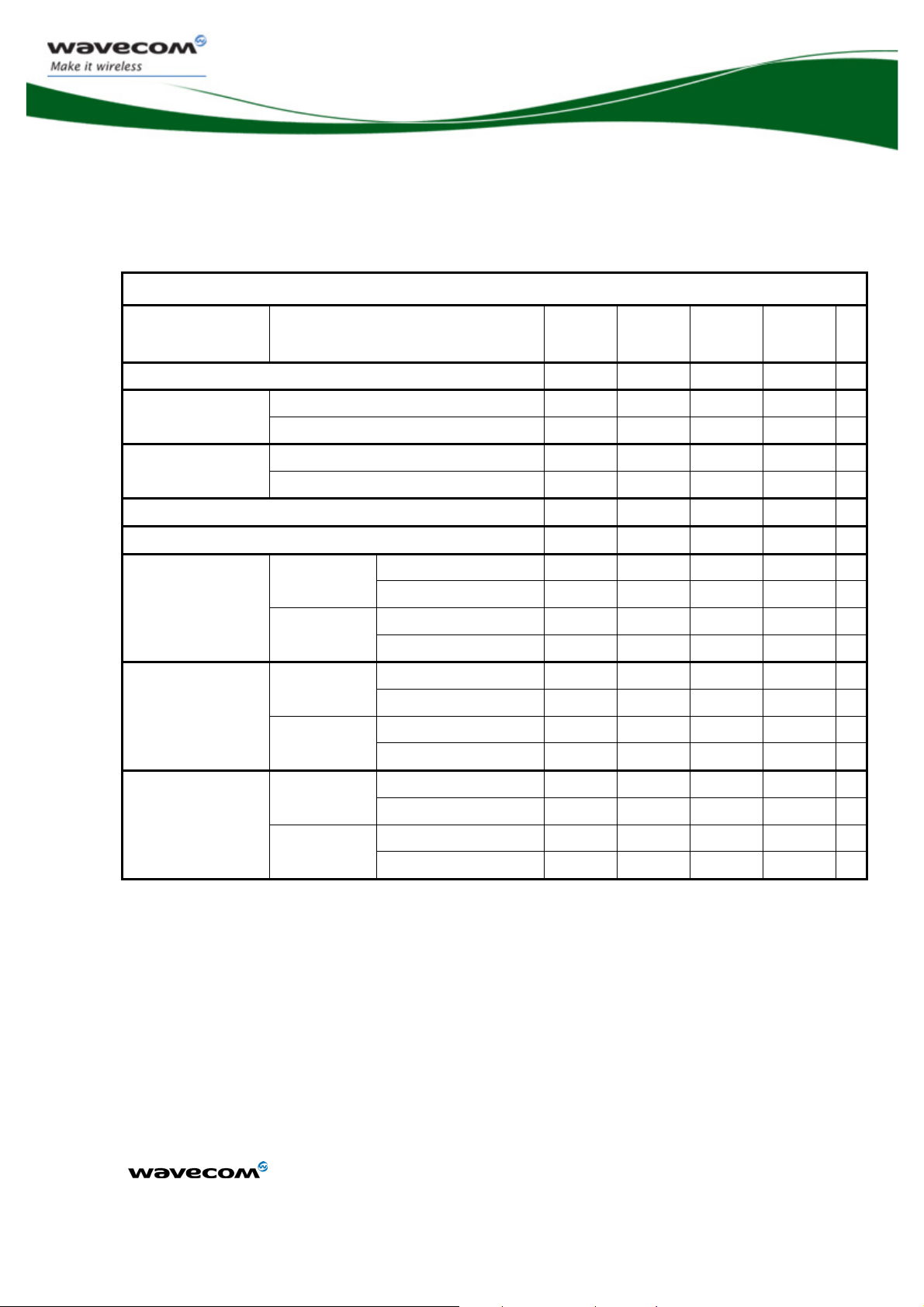

®

3.3.1.2 Power consumption with a Dhrystone Open AT

®

The Open AT

application used is the Dhrystone application. The following

application

consumption results are measured during the run of the Dhrystone application.

Power consumption with Dhrystone Open AT® application

I

Operating mode Parameters

MIN

average

VBATT=4,8V

I

NOM

average

VBATT=3,6V

I

MAX

average

VBATT=3,2V

I

MAX

peak

unit

Alarm Mode

Fast Idle Mode

Slow Idle Mode

Fast Standby Mode

Slow Standby Mode

Connected Mode

Transfer Mode

class 8 (4Rx/1Tx)

Transfer Mode

class 10 (3Rx/2Tx)

N/A

Paging 9 (Rx burst occurrence ~2s) 31

Paging 2 (Rx burst occurrence ~0,5s) 32

Paging 9 (Rx burst occurrence ~2s) N/A

Paging 2 (Rx burst occurrence ~0,5s) N/A

31

N/A

850/900 MHz

PCL5 (TX power 33dBm) 211

PCL19 (TX power 5dBm) 82

PCL0 (TX power 30dBm) 146

1800/1900 MHz

PCL15 (TX power 0dBm) 78

850/900 MHz

gam. 3(TX power 33dBm) 202

gam.17(TX power 5dBm) 78

gam.3(TX power 30dBm) 140

1800/1900 MHz

gam.18(TX power 0dBm) 75

850/900 MHz

gam.3 (TX power 33dBm) 365

gam.17 (TX power 5dBm) 113

gam.3 (TX power 30dBm) 239

1800/1900 MHz

gam.18 (TX power 0dBm) 105

N/A

38

39

N/A

N/A

38

N/A

219

90

154

85

210

86

148

82

373

121

247

113

N/A µA

41 160 RX mA

42 160

mA

RX

N/A 160 RX mA

N/A 160 RX mA

41 mA

N/A mA

223 1450 TX mA

93 270

mA

TX

159 850 TX mA

89 250

mA

TX

214 1450 TX mA

89 270

mA

TX

151 850 TX mA

85 250 TX mA

379 1450 TX mA

125 270

mA

TX

250 850 TX mA

117 250

mA

TX

means that the current peak is the RF transmission burst (Tx burst)

TX

means that the current peak is the RF reception burst (Rx burst)

RX

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 27 / 152

Page 29

WM_DEV_WUP_PTS_005

March 19, 2007

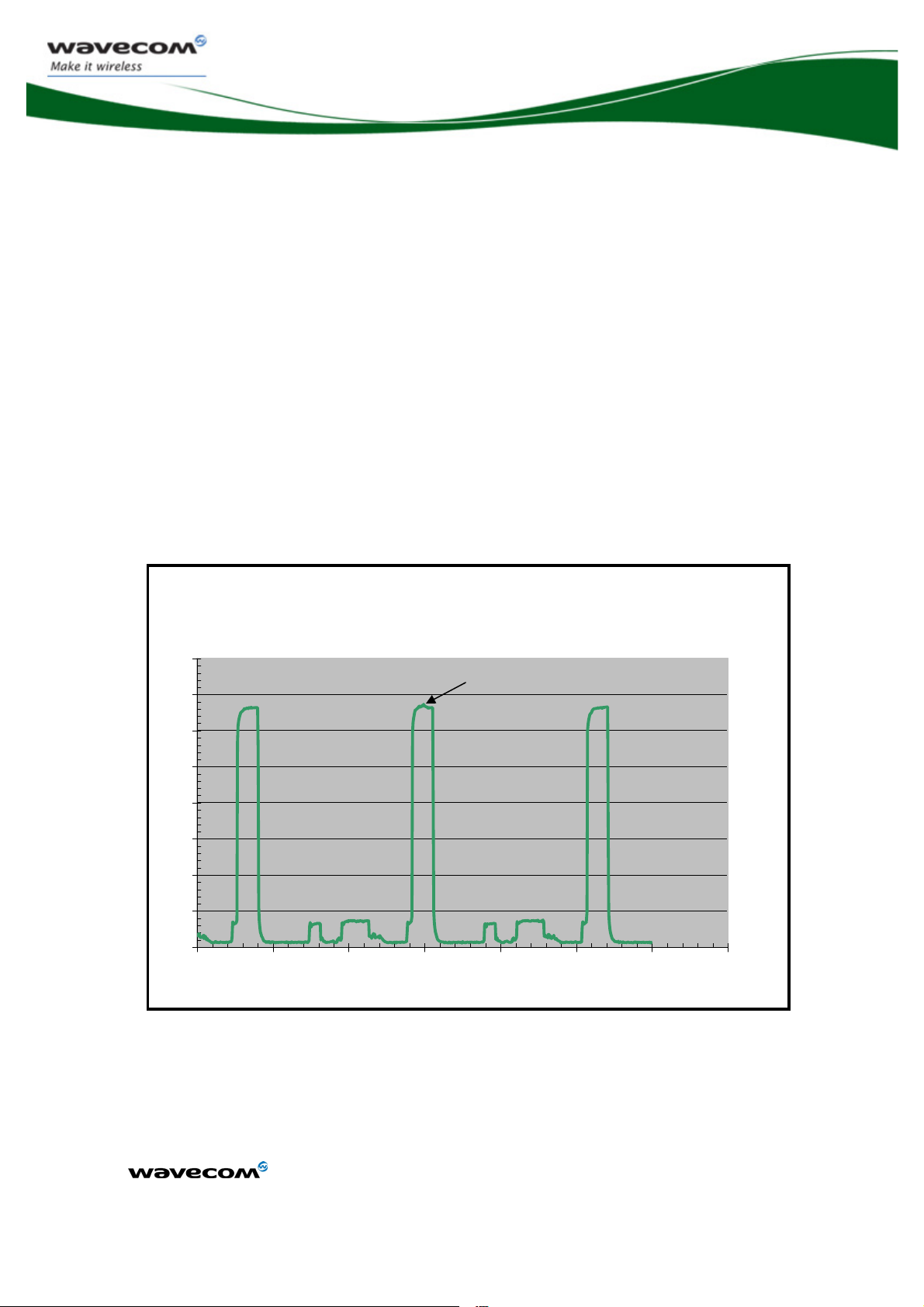

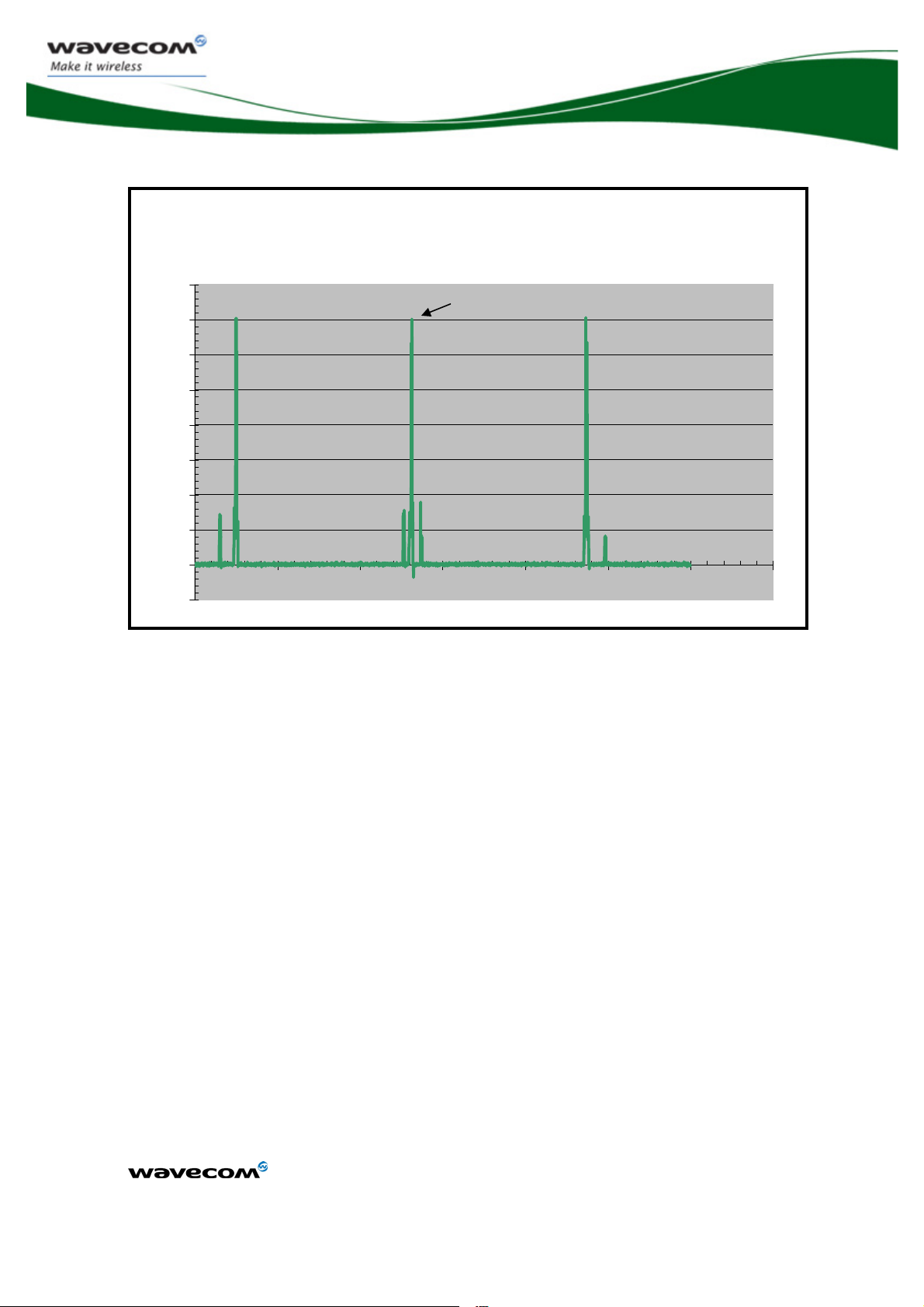

3.3.1.3 Consumption waveform samples

The consumption waveforms presented below are for an EGSM900 network

configuration without the Open AT

®

Software Suite running on the WMP100.

The typical VBATT voltage is 3.6V.

Four significant operating mode consumption waveforms are described:

¾ Connected Mode (PCL5: Tx power 33dBm)

¾ Slow Idle mode (Paging 9)

¾ Fast idle mode (Paging 9)

¾ Transfer mode (GPRS class 10, gam.3: Tx power 33dBm )

The following waveform shows only the form of the current.

3.3.1.3.1 Connected mode current waveform

Connected mode 33dBm

Current(A) / Time (s)

1.6

TX PEAK

1.4

1.2

1

0.8

0.6

0.4

0.2

0

0

0

.

0

0

2

0

.

0

0

4

0

.

0

0

6

0

.0

0

8

0

.0

1

0

.

0

1

2

0

.

0

1

4

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 28 / 152

Page 30

WM_DEV_WUP_PTS_005

March 19, 2007

3.3.1.3.2 Slow Idle mode current waveform

Slow Idle mode Paging ~2s

Current(A) / Time (s)

0.16

0.14

0.12

0.1

0.08

0.06

0.04

0.02

-0.02

RX PEAK

0

0

1

2

3

4

5

6

7

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 29 / 152

Page 31

WM_DEV_WUP_PTS_005

March 19, 2007

3.3.1.3.3 Fast Idle mode current waveform

Fast Idle mode Paging ~2s

Current(A) / Time (s)

0.16

0.14

0.12

0.1

0.08

0.06

0.04

0.02

RX PEAK

0

0

1

2

3

4

5

6

7

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 30 / 152

Page 32

WM_DEV_WUP_PTS_005

March 19, 2007

3.3.1.3.4 Transfer mode Class 10 current waveform

Transfer mode Class 10 33dBm

Current(A) / Time (s)

1.6

TX PEAK

1.4

1.2

1

0.8

0.6

0.4

0.2

0

0

0

.

0

0

2

0

.

0

0

4

0

.

0

0

6

0

.

0

0

8

0

.

0

1

0

.

0

1

2

0

.

0

1

4

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 31 / 152

Page 33

WM_DEV_WUP_PTS_005

March 19, 2007

3.4 Electrical information for digital I/O

There are three types of digital I/O on the WMP100: 2.8Volt CMOS, 1.8Volt

CMOS and Open drain.

The I/O concerned are all interfaces like GPIOs, SPIs, Keypad, etc.

The three types are described below.

Electrical characteristics of digital I/O

2.8 Volts type (2V8 )

Parameter I/O type Minim. Typ Maxim. Condition

Internal 2.8V power supply

Input / Output pin

VIL

VIH

VOL

VOH

IOH

IOL

*Absolute maximum ratings

VCC_2V8

CMOS

CMOS

CMOS

CMOS

1.8 Volts type (1V8)

Parameter I/O type Minim. Typ Maxim. Condition

Internal 1V8 power supply VCC_1V8

Input / Output pin

VIL CMOS -0.5V* 0.54V

VIH CMOS 1.33V 2.2V*

2.74V 2.8V 2.86V

-0.5V* 0.84V

1.96V 3.2V*

0.4V IOL = - 4 mA

2.4V IOH = 4 mA

4mA

- 4mA

1.76V 1.8V 1.94V

VOL CMOS 0.4V IOL = - 4 mA

VOH CMOS 1.4V IOH = 4 mA

IOH

IOL

*Absolute maximum ratings

confidential ©

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

4mA

- 4mA

Page : 32 / 152

Page 34

WM_DEV_WUP_PTS_005

March 19, 2007

Open drain outputs type

Signal name Parameter I/O type Minimum Typ Maximum Condition

FLASH-LED

SDA /

GPIO27

and

SCL /

VOL Open Drain

IOL Open Drain

VOL Open Drain

I

Open Drain

OL

V

Open Drain

TOL

VIH Open Drain

VIL Open Drain

0.4V

8mA

0.4V BUZZ-OUT

100mA

3.3V Tolerated

2V

0.8V

voltage

GPIO26

VOL Open Drain

Open Drain

I

OL

0.4V

3mA

The reset states of each I/O are given in their corresponding interface’s chapter

descriptions. The states definitions are defined below:

Reset state definition

Parameter Definition

0

1

Pull down

Set to GND

Set to supply 1V8 or 2V8 depending of I/O type

Internal pull down with ~60K resistor.

Pull up Internal pull up with ~60K resistor to supply 1V8 or 2V8

depending of I/O type.

Z High impedance

Undefined Be careful, undefined mustn’t be used in your application if

a special state at reset is needed. Those pins can be a

toggling signal during reset.

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 33 / 152

Page 35

WM_DEV_WUP_PTS_005

March 19, 2007

3.5 SPI Bus

The WMP100 provides two SPI bus (i.e. for LCD, memories…).

3.5.1 Features

• a CLK signal

• an I/O signal

• an I signal

• a CS signal complying with standard SPI bus.

3.5.1.1 Characteristics

• Master mode operation

• The Hardware CS is usable only for word handling mode. In normal

mode the CS can be any GPIO.

• The SPI speed is from 102 Kbit/s up to 13 Mbit/s in master mode

operation

• 3 or 4-wire interface

• SPI-mode configuration: 0 to 3 (for more details, refer to document

AT Command Interface Guide for Open AT® Firmware v6.5).

• 1 to 16 bits data length

3.5.1.2 SPI configuration

Operation Maximum

Speed

Master 13 Mb/s 0,1,2,3

For the 4-wire configuration, SPIx-I/O is used as output only, SPIx-I is used as input only.

For the 3-wire configuration, SPIx-I/O is used as input and output.

SPI-

Mode

Duplex

3-wire type 4-wire type

Half SPIx-CLK; SPIx-

IO; ~SPIx-CS

SPIx-CLK; SPIx-IO;

SPIx-I; ~SPIx-CS

[3]

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 34 / 152

Page 36

WM_DEV_WUP_PTS_005

March 19, 2007

3.5.1.3 SPI waveforms

Waveform for SPI transfer with 4-wire configuration in master mode 0 (chip

select is not represented).

CLK-cycle

SPIx-CLK

Data-OUTdelay

SPIx-IO

Data valid

Data-IN-setup

SPIx-I

Data-IN-hold

Data valid

Figure 4: SPI Timing diagrams, Mode 0, Master, 4 wires

AC characteristics

Signal Description Minimum Typ Maximum Unit

CLK-cycle SPI clock frequency 0.1015 13 MHz

Data-OUT delay Data out ready delay time 10 ns

Data-IN-setup Data in setup time 2 ns

Data-OUT-hold Data out hold time 2 ns

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 35 / 152

Page 37

WM_DEV_WUP_PTS_005

March 19, 2007

3.5.2 Pin description

Signal Pin

number

I/O I/O

type

Reset

state

Description Multiplexed

with

SPI1-CLK U15 O 2V8 Z SPI Serial Clock GPIO28

SPI1-IO

SPI1-I

~SPI1-CS

V12

R13

M14

I/O 2V8 Z SPI Serial input/output GPIO29

I 2V8 Z SPI Serial input GPIO30

O 2V8 Z SPI Enable GPIO31 /

INT5

Signal Pin

number

SPI2-CLK

SPI2-IO

SP2-I

~SPI2-CS

R15

M13

U16

T18

I/O I/O

type

Reset

state

Description Multiplexed

with

O 2V8 Z SPI Serial Clock GPIO32

I/O 2V8 Z SPI Serial input/output GPIO33

I 2V8 Z SPI Serial input GPIO34

O 2V8 Z SPI Enable GPIO35 /

INT4

See chapter

characteristics and for Reset state definition.

3.4, “Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage

3.5.3 Application

3.5.3.1 4-wire interface

The particularity of the 4-wire serial interface (SPI bus) is that the input and the

output data lines are dissociated. The SPIx-IO signal is used only for data

output and the SPIx-I signal is used only for data input.

SPIx-CLK

SPIx-IO

WMP100

SPIx-I

VCC_2 V8

R1

~SPIx -CS

Customer

application

Figure 5: Example of 4-wire SPI bus application

One pull up resistor R is needed to set the SPIx-CS level during the reset state.

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 36 / 152

Page 38

WM_DEV_WUP_PTS_005

March 19, 2007

Except for R, no external component is needed if the electrical specification of

the customer application complies with the WMP100 SPIx interface electrical

specification.

3.5.3.2 3-wire interface

When used in 3-wire interface (SPI bus), only the line SPIx-IO is used for

output and input data.

SPIx-CLK

SPIx-IO

WMP100

SPIx-I

~SPIx -CS

VCC_2 V8

R1

Customer

application

Figure 6: Example of 3-wire SPI bus application

The SPIx-I line is not used in 3-wire configuration. This line can be left opened

or used as GPIO for a different application functionality.

One pull up resistor R is needed to set the SPIx-CS level during the reset state.

Except for R, no external component is needed if the electrical specification of

the customer application complies with the WMP100 SPIx interface electrical

specification.

The SPIx interface voltage range is 2.8V. It can be powered by the VCC_2V8

(ball R1) of the WMP100 or by another power supply.

R value depends on the peripheral plugged on the SPIx interface.

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 37 / 152

Page 39

WM_DEV_WUP_PTS_005

March 19, 2007

3.6 I2C bus

3.6.1 Features

The I2C interface includes a clock signal (SCL) and a data signal (SDA)

complying with a 100Kbit/s-standard interface (standard mode: s-mode).

3.6.1.1 Characteristics

The I²C bus is always master.

The maximum speed transfer range is 400Kbit/s (Fast mode: f-mode).

For more information on the bus, see document

Version 2.0, Philips Semiconductor 1998

.

3.6.1.2 I²C waveforms

I²C bus waveform in master mode configuration:

SCL-freq

T-high

SCL

T-data-

setup

Data valid

SDA

T-free

T-start

Data valid

T-data-

hold

[4] “I²C Bus Specification”,

T-stop

Figure 7: I²C Timing diagrams, Master

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 38 / 152

Page 40

WM_DEV_WUP_PTS_005

March 19, 2007

AC characteristics

Signal Description Minimum Typ Maximum Unit

SCL-freq I²C clock frequency 100 400 KHz

T-start Hold time START condition 0.6 μs

T-stop Setup time STOP condition 0.6 μs

T-free Bus free time, STOP to START

1.3 μs

T-high High period for clock 0.6 μs

T-data-hold Data hold time 0 0.9 μs

T-data-setup Data setup time 100 ns

3.6.2 Pin description

Signal Pin

number

SCL

SDA

See chapter 3.4, “Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage

characteristics and for Reset state definition.

AA15

AA16

I/O I/O type Reset

state

Description Multiplexed

with

O Open drain Z Serial Clock GPIO26

I/O Open drain Z Serial Data GPIO27

3.6.3 Application

The two lines need to be pull up to the V

I²C voltage. The VI²C voltage is

dependent on the customer application component connected on the I²C bus.

Nevertheless, the VI²C must complying with the WMP100 electrical

specification (3.3V Max).

The VCC_2V8 (ball R1) of the WMP100 can be used to connect the pull up

resistors, if the I²C bus voltage is 2.8 V.

VI²C

1K 1K

WMP100

SCL

SDA

Customer

application

Figure 8: First example of I²C bus application

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged

confidential ©

without prior written agreement.

Ce document est la propriété exclusive de WAVECOM. Il ne peut être communiqué ou divulgué à

des tiers sans son autorisation préalable.

Page : 39 / 152

Page 41

WM_DEV_WUP_PTS_005

March 19, 2007

The I²C bus is complying with the Standard mode (baud rate 100Kbit/s) and

the Fast mode (baud rate 400Kbit/s). The pull up resistor value choice depends

on the mode used. For the Fast mode, it is recommended to use 1K ohm

resistor to ensure the compliance with the I²C specification. For the Standard

mode, higher values of resistors can be used to save power consumption.

R1

WMP100

VCC_2V8

SCL

SDA

Figure 9: Second example of I²C bus application

3.7 Keyboard interface

3.7.1 Features