Page 1

WM_DEV_Q26EX_PTS_002

006

December 3, 2009

Q26 Extreme Wireless CPU®

Product Technical Specification

and Customer Design Guidelines

Page 2

Product Technical Specification and

Customer Design Guidelines

Due to the nature of wireless communications, transmission and reception of data can never be

guaranteed. Data may be delayed, corrupted (i.e., have errors) or be totally lost. Although significant

delays or losses of data are rare when wireless devices such as the Sierra Wireless modem are used in

a normal manner with a well-constructed network, the Sierra Wireless modem should not be used in

situations where failure to transmit or receive data could result in damage of any kind to the user or

any other party, including but not limited to personal injury, death, or loss of property. Sierra

Wireless accepts no responsibility for damages of any kind resulting from delays or errors in data

transmitted or received using the Sierra Wireless modem, or for failure of the Sierra Wireless modem

to transmit or receive such data.

Do not operate the Sierra Wireless modem in areas where blasting is in progress, where explosive

atmospheres may be present, near medical equipment, near life support equipment, or any

equipment which may be susceptible to any form of radio interference. In such areas, the Sierra

Wireless modem MUST BE POWERED OFF. The Sierra Wireless modem can transmit signals that

could interfere with this equipment. Do not operate the Sierra Wireless modem in any aircraft,

whether the aircraft is on the ground or in flight. In aircraft, the Sierra Wireless modem MUST BE

POWERED OFF. When operating, the Sierra Wireless modem can transmit signals that could

interfere with various onboard systems.

Note: Some airlines may permit the use of cellular phones while the aircraft is on the ground and the door is

open. Sierra Wireless modems may be used at this time.

The driver or operator of any vehicle should not operate the Sierra Wireless modem while in control

of a vehicle. Doing so will detract from the driver or operator’s control and operation of that vehicle.

In some states and provinces, operating such communications devices while in control of a vehicle is

an offence.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 2 of 112

Page 3

Product Technical Specification and

Customer Design Guidelines

This manual is provided “as is”. Sierra Wireless makes no warranties of any kind, either expressed or

implied, including any implied warranties of merchantability, fitness for a particular purpose, or

noninfringement. The recipient of the manual shall endorse all risks arising from its use.

The information in this manual is subject to change without notice and does not represent a

commitment on the part of Sierra Wireless. SIERRA WIRELESS AND ITS AFFILIATES

SPECIFICALLY DISCLAIM LIABILITY FOR ANY AND ALL DIRECT, INDIRECT, SPECIAL,

GENERAL, INCIDENTAL, CONSEQUENTIAL, PUNITIVE OR EXEMPLARY DAMAGES

INCLUDING, BUT NOT LIMITED TO, LOSS OF PROFITS OR REVENUE OR ANTICIPATED

PROFITS OR REVENUE ARISING OUT OF THE USE OR INABILITY TO USE ANY SIERRA

WIRELESS PRODUCT, EVEN IF SIERRA WIRELESS AND/OR ITS AFFILIATES HAS BEEN

ADVISED OF THE POSSIBILITY OF SUCH DAMAGES OR THEY ARE FORESEEABLE OR FOR

CLAIMS BY ANY THIRD PARTY.

Notwithstanding the foregoing, in no event shall Sierra Wireless and/or its affiliates aggregate

liability arising under or in connection with the Sierra Wireless product, regardless of the number of

events, occurrences, or claims giving rise to liability, be in excess of the price paid by the purchaser

for the Sierra Wireless product.

© 2009 Sierra Wireless. All rights reserved.

AirCard® and “Heart of the Wireless Machine®” are filed or registered trademarks of Sierra Wireless.

Watcher® is a trademark of Sierra Wireless, registered in the European Community. Sierra Wireless,

the Sierra Wireless logo, the red wave design, and the red-tipped antenna are trademarks of Sierra

Wireless.

, , ®, inSIM®, “YOU MAKE IT, WE MAKE IT WIRELESS®”,

WAVECOM®, WISMO®, Wireless Microprocessor®, Wireless CPU®, Open AT® are filed or registered

trademarks of Sierra Wireless S.A. in France and/or in other countries.

Windows® is a registered trademark of Microsoft Corporation.

QUALCOMM® is a registered trademark of QUALCOMM Incorporated. Used under license.

Other trademarks are the property of the respective owners.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 3 of 112

Page 4

Product Technical Specification and

Customer Design Guidelines

Sales Desk:

Phone:

1-604-232-1488

Hours:

8:00 AM to 5:00 PM Pacific Time

E-mail:

Post:

Sierra Wireless

13811 Wireless Way

Richmond, BC

Canada V6V 3A4

Fax:

1-604-231-1109

Web:

Consult our website for up-to-date product descriptions, documentation, application notes, firmware

Level

Date

List of revisions

001

December 22, 2008

Creation

002

March 18, 2009

Update power consumption figures add thermal design rules

003

June 05, 2009

Update for Vbatt range, thermal foam and temperature behavior

004

August 4, 2009

Reformatted in Sierra Wireless style.

Updated UART1 tolerance information as follows: The UART1 interface is

a 2.8 volts type. Moreover, it is 3.3 volts tolerant.

Updated Standards and Recommendations section.

005

September 16, 2009

Updated Antenna gain of 4.6dBi and additional information in this

paragraph of the Standards Recommendations section.

Updated CT104-RXD1* to be MUXed with GPIO37

006

December 3, 2009

Standards and Recommendations section:

Updated FCC notice by adding to the last sentence of one paragraph

regarding FCC multi-transmitter information, deleted the following

one sentence regarding compliance, and fixed the values in the

following sentence to 4.6dBi (850MHz) and 3.4dBi (1900MHz) .

Interfaces section:

Updated 3V/1V8 UICC/SIM interface bullet

Updated USIM/SIM card bullet

USIM/SIM Interface section

Added Using the USIM is recommended over the SIM card sentence

upgrades, troubleshooting tips, and press releases:

WM_DEV_Q26EX_PTS_002 Rev 006 Page 4 of 112

Page 5

Product Technical Specification and

Customer Design Guidelines

WM_DEV_Q26EX_PTS_002 Rev 006 Page 5 of 112

Page 6

Product Technical Specification and

Customer Design Guidelines

WM_DEV_Q26EX_PTS_002 Rev 006 Page 6 of 112

Page 7

Product Technical Specification and

Customer Design Guidelines

WM_DEV_Q26EX_PTS_002 Rev 006 Page 7 of 112

Page 8

Product Technical Specification and

Customer Design Guidelines

WM_DEV_Q26EX_PTS_002 Rev 006 Page 8 of 112

Page 9

Product Technical Specification and

Customer Design Guidelines

WM_DEV_Q26EX_PTS_002 Rev 006 Page 9 of 112

Page 10

Product Technical Specification and

Customer Design Guidelines

WM_DEV_Q26EX_PTS_002 Rev 006 Page 10 of 112

Page 11

Product Technical Specification and

Customer Design Guidelines

WM_DEV_Q26EX_PTS_002 Rev 006 Page 11 of 112

Page 12

Product Technical Specification and

Customer Design Guidelines

WM_DEV_Q26EX_PTS_002 Rev 006 Page 12 of 112

Page 13

Product Technical Specification and

Customer Design Guidelines

This document presents and defines the Q26 Extreme Wireless CPU®.

The Q26 Extreme Wireless CPU® is a multi-mode EDGE 2G / WCDMA 3G / HSxPA (High Speed

Downlink & High Speed Uplink Packet Access) solution with dual antenna receive diversity,

footprint compatible with other Wireless CPU® Q26 devices.

The Q26 Extreme Wireless CPU® supports a powerful open software platform (Open AT®). Open AT®

is the world’s most comprehensive cellular development environment, which allows embedded

standard ANSI C applications to be natively executed directly on the Wireless CPU®.

This Product Specification document covers the Wireless CPU® alone and does not include the

programmable capabilities provided via the use of Open AT® Software Suites.

For more details, several reference documents may be consulted. The Wavecom reference documents

are provided in the Wavecom document package, contrary to the general reference documents which

are not authored by Wavecom.

Please check the web site for the latest documentation available.

First Software version available for Q26 Extreme Wireless CPU® is Open AT® Software Suite v2.30.

[1] Getting Started with Open AT

[2] Basic Development Guide for Open AT

[3] ADL User Guide for Open AT

[4] Open AT

[5] Open AT

[6] Open AT

®

Release Note

®

Firmware v7.4 AT Commands Manual (Ref: WM_DEV_OAT_UGD_079-010)

®

Firmware Release Note

®

®

®

WM_DEV_Q26EX_PTS_002 Rev 006 Page 13 of 112

Page 14

Product Technical Specification and

Customer Design Guidelines

[7] “I²C Bus Specification and user guide”, Version 3.0, NXP 2007

Abbreviation

Definition

AC

Alternating Current

ADC

Analog to Digital Converter

A/D

Analog to Digital conversion

AF

Audio-Frequency

AT

ATtention (prefix for modem commands)

AUX

AUXiliary

CAN

Controller Area Network

CB

Cell Broadcast

CEP

Circular Error Probable

CLK

CLocK

CMOS

Complementary Metal Oxide Semiconductor

CS

Coding Scheme

CTS

Clear To Send

DAC

Digital to Analog Converter

dB

Decibel

DC

Direct Current

DCD

Data Carrier Detect

DCE

Data Communication Equipment

DCS

Digital Cellular System

DR

Dynamic Range

DSR

Data Set Ready

DTE

Data Terminal Equipment

DTR

Data Terminal Ready

EDGE

Enhanced Data rates for GSM Evolution

EFR

Enhanced Full Rate

EGPRS

Enhanced General Packet Radio Service

E-GSM

Extended GSM

EMC

ElectroMagnetic Compatibility

EMI

ElectroMagnetic Interference

EMS

Enhanced Message Service

EN

ENable

ESD

ElectroStatic Discharges

FIFO

First In First Out

[8] ISO 7816-3 Standard

Table 1. Abbreviations

WM_DEV_Q26EX_PTS_002 Rev 006 Page 14 of 112

Page 15

Product Technical Specification and

Customer Design Guidelines

Abbreviation

Definition

FR

Full Rate

FTA

Full Type Approval

GND

GrouND

GPI

General Purpose Input

GPC

General Purpose Connector

GPIO

General Purpose Input Output

GPO

General Purpose Output

GPRS

General Packet Radio Service

GPS

Global Positioning System

GSM

Global System for Mobile communications

HR

Half Rate

HSDPA

High Speed Downlink Packet Access

HSUPA

High Speed Uplink Packet Access

HSxPA

High Speed x(downlink/uplink) Packet Access

I/O

Input / Output

LED

Light Emitting Diode

LNA

Low Noise Amplifier

MAX

MAXimum

MIC

MICrophone

MIN

MINimum

MMS

Multimedia Message Service

MO

Mobile Originated

MT

Mobile Terminated

na

Not Applicable

NF

Noise Factor

NMEA

National Marine Electronics Association

NOM

NOMinal

NTC

Negative Temperature Coefficient

PA

Power Amplifier

Pa

Pascal (for speaker sound pressure measurements)

PBCCH

Packet Broadcast Control CHannel

PC

Personal Computer

PCB

Printed Circuit Board

PCM

Pulse Code Modulation (audio) or Protection Circuit Module (battery)

PDA

Personal Digital Assistant

PFM

Power Frequency Modulation

PSM

Phase Shift Modulation

PWM

Pulse Width Modulation

RAM

Random Access Memory

RF

Radio Frequency

RFI

Radio Frequency Interference

WM_DEV_Q26EX_PTS_002 Rev 006 Page 15 of 112

Page 16

Product Technical Specification and

Customer Design Guidelines

Abbreviation

Definition

RHCP

Right Hand Circular Polarization

RI

Ring Indicator

RST

ReSeT

RTC

Real Time Clock

RTCM

Radio Technical Commission for Maritime services

RTS

Request To Send

RX

Receive

SCL

Serial CLock

SDA

Serial DAta

SMS

Short Message Service

SPI

Serial Peripheral Interface

SPL

Sound Pressure Level

SPK

SPeaKer

SRAM

Static Random Access Memory

TBC

To Be Confirmed

TDMA

Time Division Multiple Access

TP

Test Point

TVS

Transient Voltage Suppressor

TX

Transmit

TYP

TYPical

UART

Universal Asynchronous Receiver-Transmitter

UMTS

Universal Mobile Telecommunications System

USB

Universal Serial Bus

USIM

Universal Subscriber Identification Module

USSD

Unstructured Supplementary Services Data

VSWR

Voltage Standing Wave Ratio

WCDMA

Wideband Code Division Multiple Access

Subject matter

Web site

General information about Wavecom and its range of products:

Specific support about the Q26 Extreme Wireless CPU®:

Carrier/Operator approvals:

Open AT® Introduction:

Developer support for software and hardware:

Table 2. Web Site Support Links

WM_DEV_Q26EX_PTS_002 Rev 006 Page 16 of 112

Page 17

Product Technical Specification and

Customer Design Guidelines

The Q26 Extreme Wireless CPU® series is a self-contained GSM/GPRS/EGDE quad-band and HSxPA

tri band Wireless CPU® with the following characteristics:

Dimension:

Length: 40 mm

Width: 32.2 mm

Thickness: 6.3 mm

X/Y form-factor compatible with Q2686/87 Wireless CPU

®

range

EU Directive 2002/95/EC on RoHS

The Q26 Extreme Wireless CPU

®

is compliant with RoHS (Restriction of Hazardous

Substances in Electrical and Electronic Equipment) Directive 2002/95/EC which sets limits

for the use of certain restricted hazardous substances.

This directive states that “from 1st July 2006, new electrical and electronic equipment put

on the market does not contain lead, mercury, cadmium, hexavalent chromium,

polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE)”.

Regulatory: R&TTE directive (CE marking), GCF-CC, PTCRB, FCC/IC.

Manufacturing: ISO/TS 16949

3GPP FDD Release 6 HSUPA Compliant.

Tri-Band UMTS/HxDPA (WCDMA/FDD) 2100/1900/850 MHz (band I, II, V)

Downlink data rates up to HSDPA Category 8 (7.2 Mbps).

Uplink data rates up to HSUPA Category 5 (2 Mbps)

Advanced Type III receiver technology supporting simultaneous Receive Diversity and

Equalization.

Quad-Band GSM GPRS EDGE 850/900/1800/1900 MHz

GPRS class 12

EDGE (E-GPRS) multi-slot class 12

Dual mode with fully automated handover between 2G and 3G networks

Voice: HR, FR and EFR; Adaptive multi-rate AMR in GSM & UMTS.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 17 of 112

Page 18

Product Technical Specification and

Customer Design Guidelines

Digital section running under 2.8 volts and 1.8 volts.

3V/1V8 UICC/SIM interface

Complete interfacing:

Power supply

Serial link

Analog audio

Parallel bus 16bits

PCM digital audio

USIM/SIM card

Keyboard

USB 2.0 slave FS

Serial LCD (not available with AT commands)

Application processor embeds Open AT® Software Suite with extensive set of Plug-Ins, supported by

M2M Studio, enabling the creation of natively executed code in C and/or Lua script.

Up to 88 MIPS for application execution

Includes a low latency, multitasking pre-emptive Operating System

The Q26 Extreme Wireless CPU® has following external connections:

Two solutions for main RF antenna connection

UFL connector

Soldered connection

Diversity RF antenna connection:

Soldered connection

Analogue and digital interfaces:

100 pin I/O connector.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 18 of 112

Page 19

Product Technical Specification and

Customer Design Guidelines

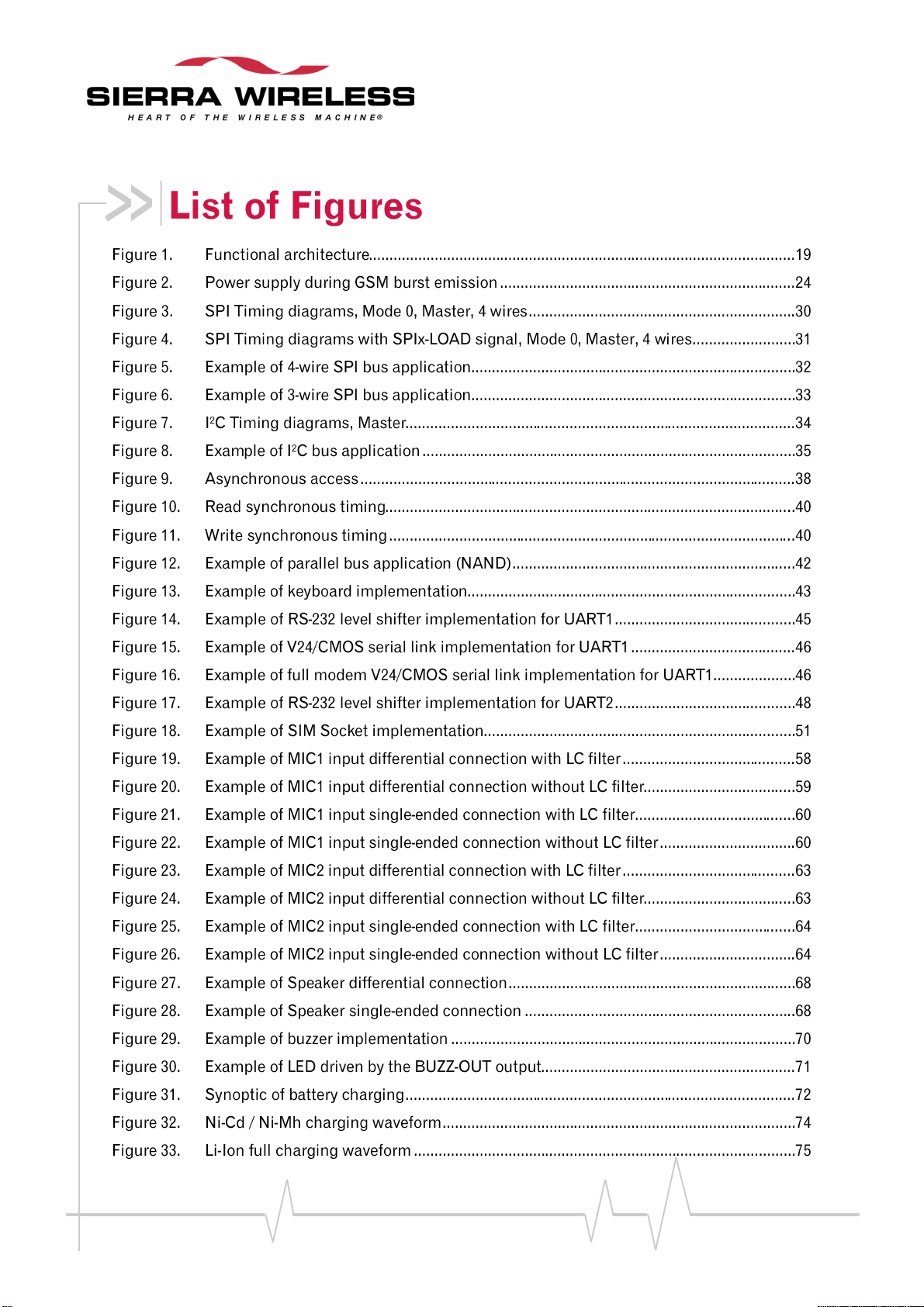

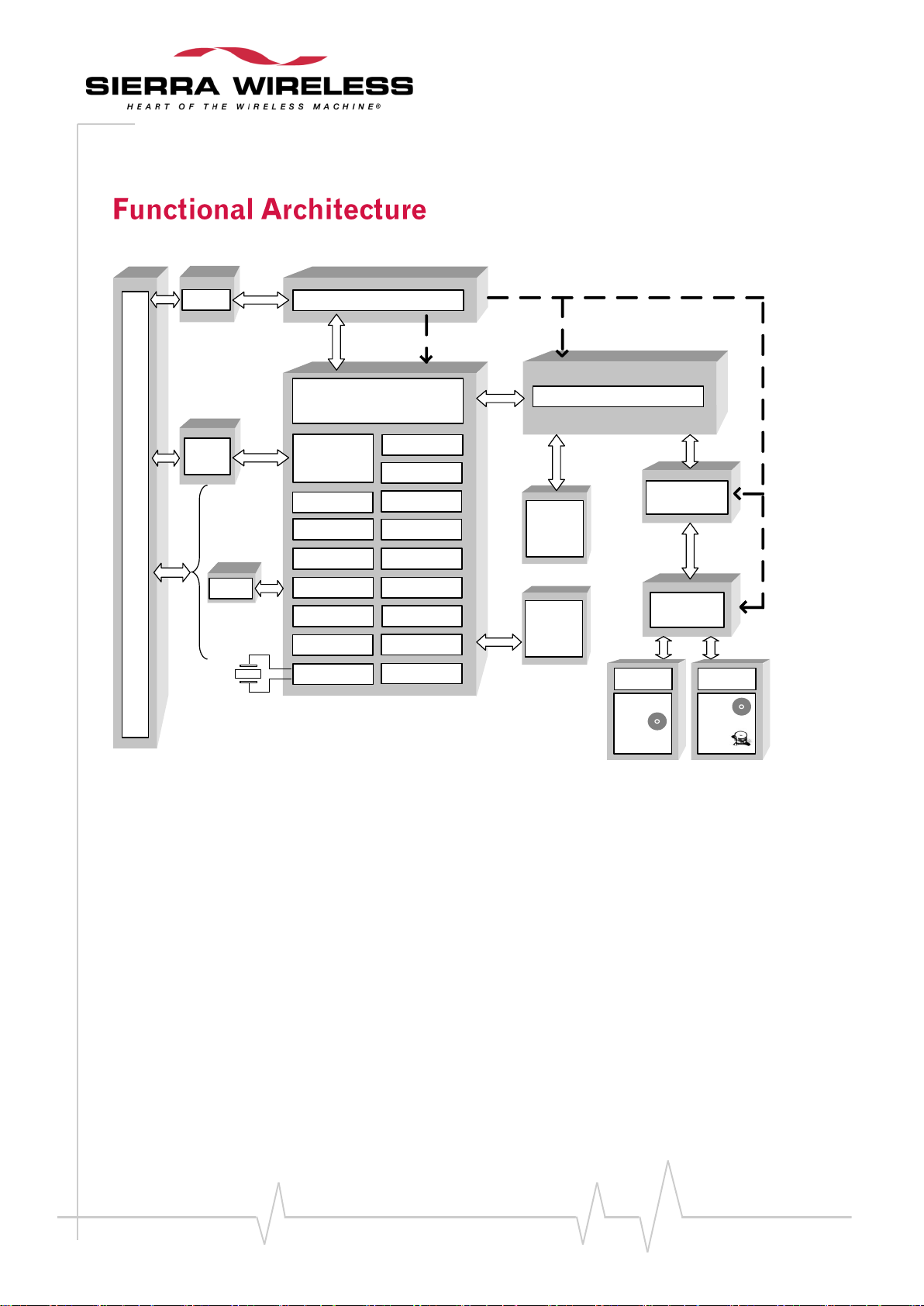

The global architecture of the Q26 Extreme Wireless CPU® is described below:

AUDIO

POWER

UART2

PCM

UART1

USB

SIM 1.8V/3V

EBI

DAC

ADC

GPIO

SPI1

I2C

SPI2

EXT_IT

POWER MANAGEMENT

AUDIO

FILTER

MEMORY

FLASH /

SRAM

RF

FRONT END

2G / 3G RF

TRANSCEIVER

COAX

UFL

MAIN

ANTENNA

Q

2

6

E

X

B

O

A

R

D

T

O

B

O

A

R

D

I

N

T

E

R

F

A

C

E

C

O

N

N

E

C

T

O

R

CHARGER

RTC

USB

detection

KEYPAD

DUAL 2G&3G base band processor

COAX

DIVERSITY

ANTENNA

MEMORY

FLASH /

SDRAM

APPLICATION Processor Core

WM_DEV_Q26EX_PTS_002 Rev 006 Page 19 of 112

Figure 1. Functional architecture

Page 20

Product Technical Specification and

Customer Design Guidelines

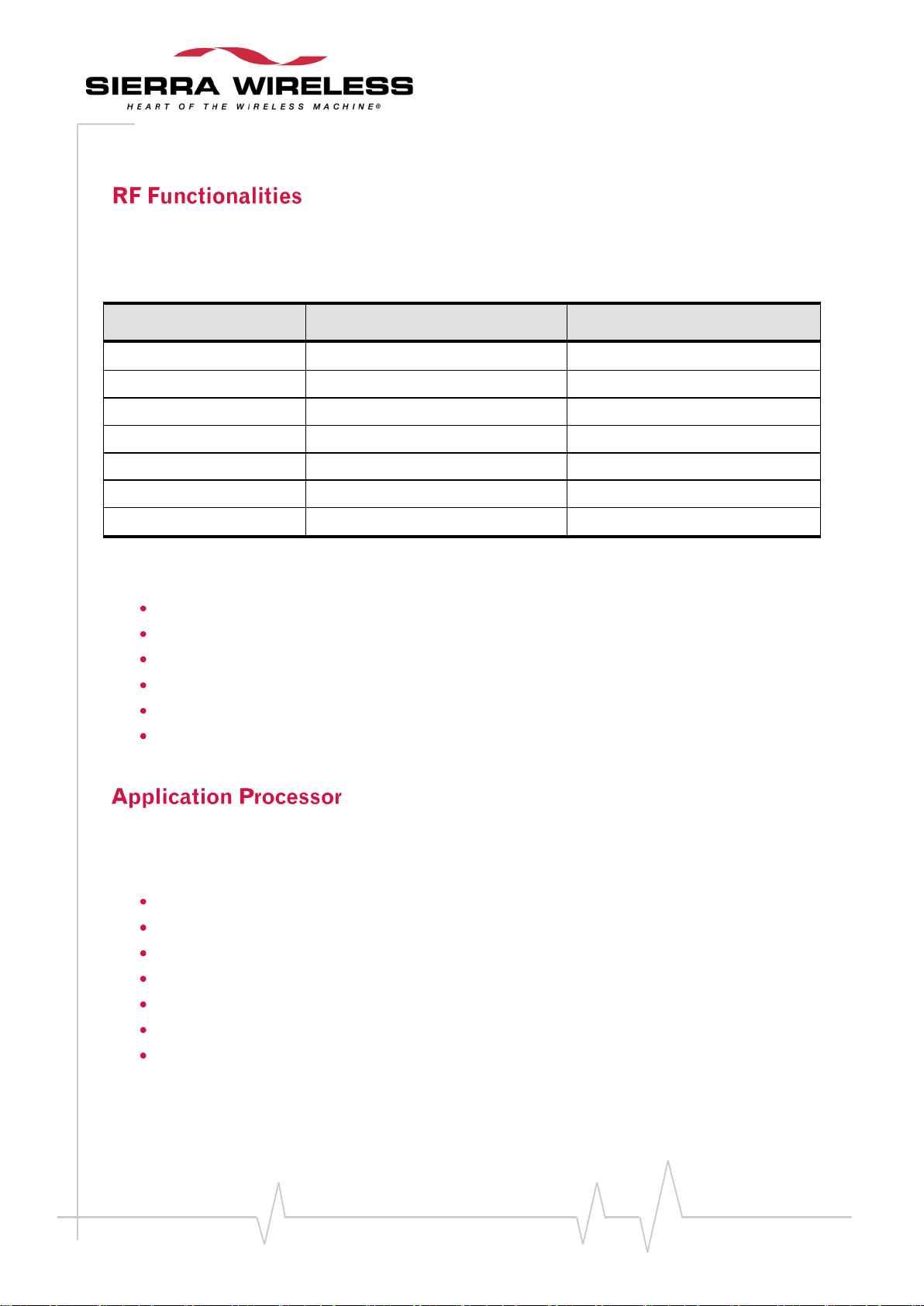

The Radio Frequency (RF) range complies with the Phase II EGSM 900/DCS 1800 and GSM 850/PCS

RF Bandwidth

Transmit band (Tx)

Receive band (Rx)

GSM 850

824 to 849 MHz

869 to 894 MHz

E-GSM 900

880 to 915 MHz

925 to 960 MHz

DCS 1800

1710 to 1785 MHz

1805 to 1880 MHz

PSC 1900

1850 to 1910 MHz

1930 to 1990 MHz

WCDMA Band I

1920 to 1980 MHz

2110 to 2170 MHz

WCDMA Band II

1850 to 1910 MHz

1930 to 1990 MHz

WCDMA Band V

824 to 849 MHz

869 to 894 MHz

1900 recommendations. The frequencies are:

Table 3. RF Frequency Ranges

The Radio Frequency (RF) part is based on a specific quad-band chip with a:

Direct down conversion Rx architecture

Linear direct up-conversion Tx architecture

On chip Tx power control

Analog I/Q base band interface for all modes

Integrated Σ-Δ fractional N synthesiser for dual-mode operation

On chip multi-band true Rx diversity

The Q26 Extreme supports the complete family of software Plug-Ins provided within the Open AT®

Software Suite (TCP-IP, Internet, GPS, Lua, Security, Bluetooth, aqLink™). It also supports

VariPower & VariSpeed (26-104MHz) features allowing highly configurable power optimization:

ARM946 32 bit processor

Programmable to 104MHz operation

Internal Memory (8kbyte Cache I$, 8kbyte D$)

Latency time: < 1ms

Memory access speed up to 52MHz

2 user Timers at 13MHz fine tuning (1 for customer)

3 External IT with debouncing

WM_DEV_Q26EX_PTS_002 Rev 006 Page 20 of 112

Page 21

Product Technical Specification and

Customer Design Guidelines

The Q26 Extreme Wireless CPU® is designed to integrate various types of specific process applications

such as vertical applications (telemetry, multimedia, automotive).

The Operating System offers a set of AT commands to control the Wireless CPU®. With this standard

Operating System, some interfaces of the Wireless CPU® are not available, since they are dependent

on the peripheral devices connected to the Wireless CPU®.

The Operating System is Open AT® compliant.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 21 of 112

Page 22

Product Technical Specification and

Customer Design Guidelines

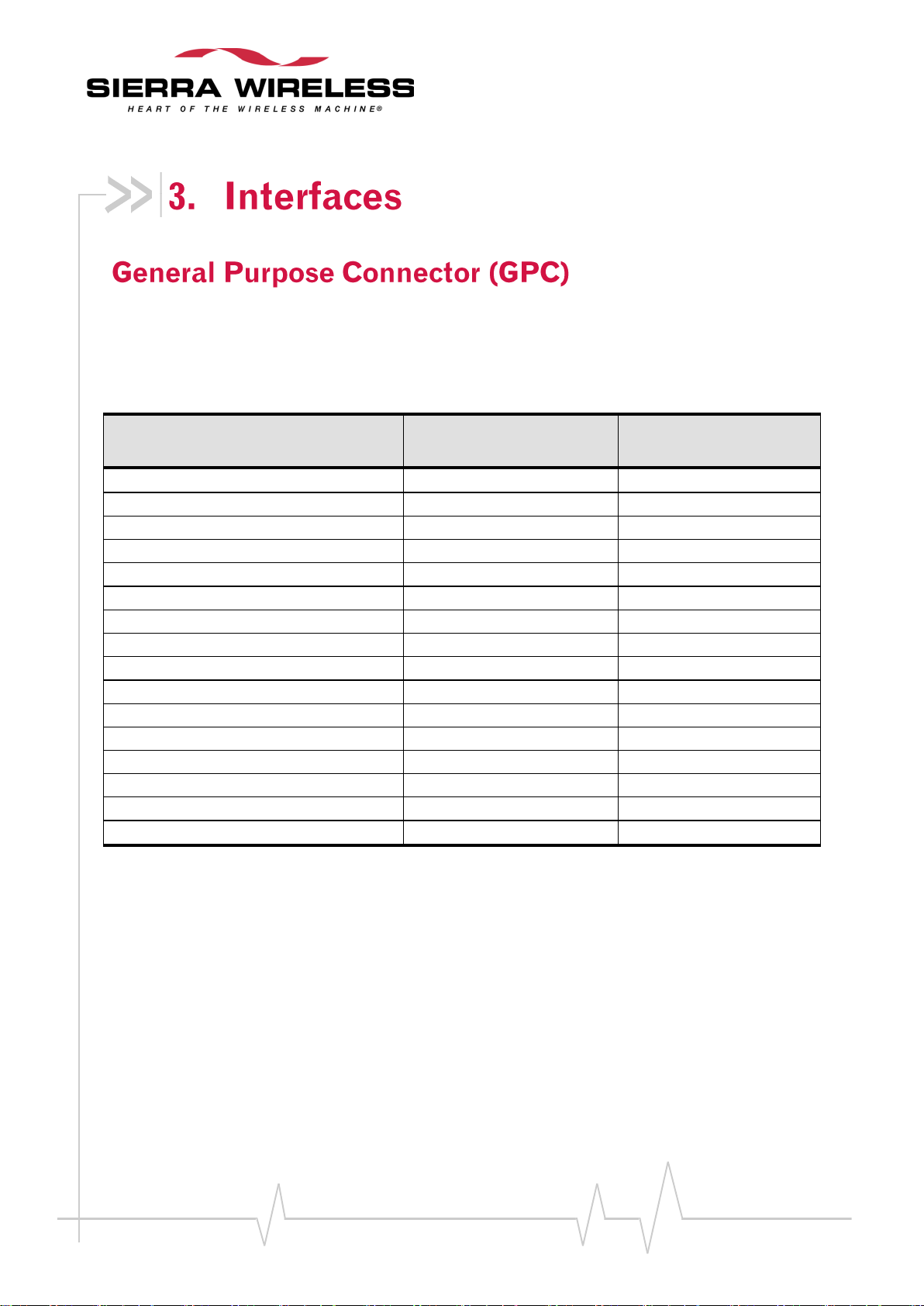

Name

Driven by

AT commands

Driven by

Open AT®

Serial Interface X

Keyboard Interface

X

X

Main Serial Link X X

Auxiliary Serial Link

X

X

USIM Interface X X

General Purpose IO

X

X

Analog to Digital Converter

X

X

Analog Audio Interface

X

X

Buzzer Output X X

Battery Charging Interface

X

X

External Interruption

X

X

VCC_2V8 and VCC_1V8

BAT-RTC (Backup Battery)

LED0 signal X X

Digital Audio Interface (PCM)

X

USB 2.0 Interface X X

A 100-pin connector is provided to interface the Q26 Extreme Wireless CPU® with a board containing

a serial LCD Wireless CPU®, a keyboard, a USIM connector, or a battery connection.

The available interfaces on the GPC are described below.

Table 4. Available GPC Interfaces

WM_DEV_Q26EX_PTS_002 Rev 006 Page 22 of 112

Page 23

Product Technical Specification and

Customer Design Guidelines

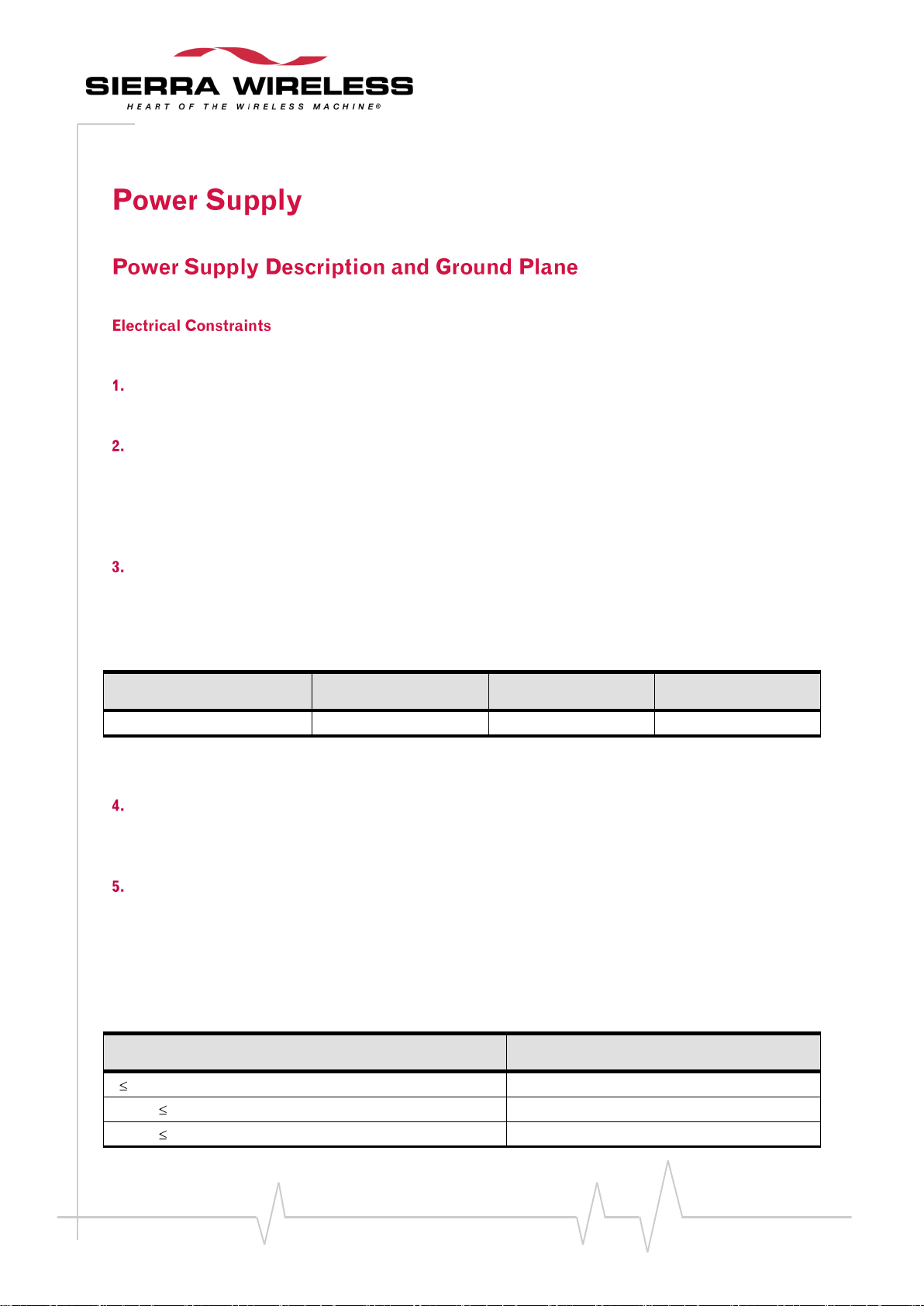

Only the VBATT input is necessary to supply the Q26 Extreme Wireless CPU®.

Vmin

Vnom

Vmax

VBATT1,2

3.4V

3.8V

4.2V

Freq. (Hz)

Uripp Max (mVpp)

f 300

80

300 < f 800

10

800 < f 1100

30

Operational average current

Recommended values for Operational average max current: 1.1A

Peak max current

Recommended values for Peak max current: 2.1A.

The rising time is around 10µs

See subsection g) for worst case description.

Ground

The Q26 Extreme Wireless CPU® shielding case is the grounding. The ground must be connected to

the motherboard through a complete layer on the PCB.

Table 5. Input power supply voltage

(1): This value must be guarantied during the burst (with 2.1A Peak in GSM or GPRS mode)

(2): Max operating Voltage Stationary Wave Ratio (VSWR) 2:1

Impedance

When the Wireless CPU® is supplied with a battery, the total impedance (battery + protections + PCB)

should be < 150 mΩ.

Recommendations when using DC/DC converter

As the radio power amplifier is directly connected to VBATT, the Wireless CPU® is sensitive to any

Alternative Current on lines. When a DC/DC converter is used, Wavecom recommends setting the

converter frequency in such a way that the resulting voltage does not exceed the values in following

table.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 23 of 112

Table 6. Maximum voltage ripple (Uripp) vs. Frequency

Page 24

Product Technical Specification and

Customer Design Guidelines

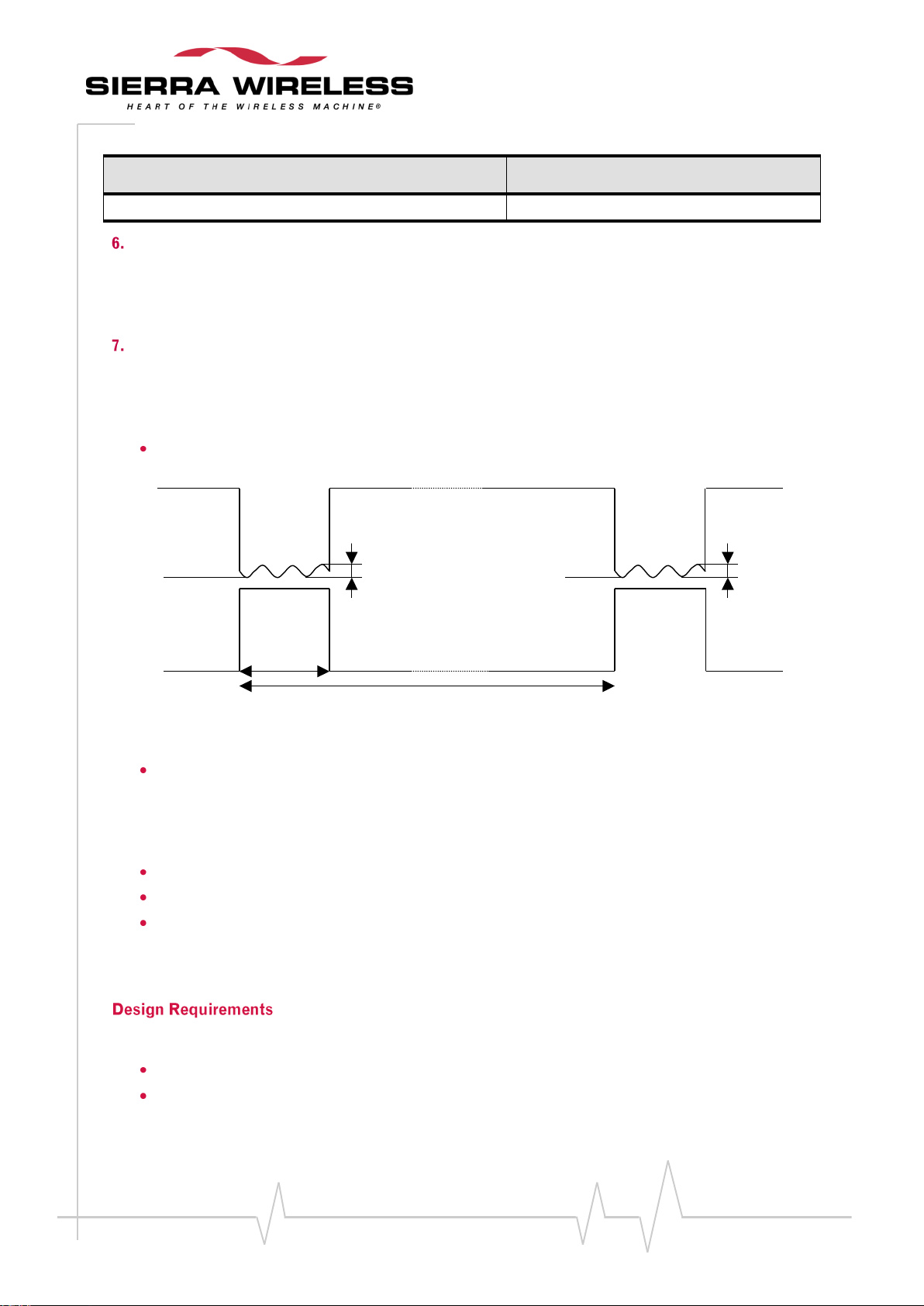

Freq. (Hz)

Uripp Max (mVpp)

f > 1100

60

Constraints in Alarm/Off mode

Uripp

VBATTT

Uripp

T = 4,615 ms

t = 577 µs

When the Wireless CPU® is in Alarm/Off mode, no voltage has to be applied on any pin of the 100-pin

connector, except on Vbatt (pins 1 to 4), BAT-RTC (pin 7) for RTC operation or ON/~OFF (pin 19) to

power-ON the Wireless CPU®.

Details

Due to the burst emission mode used in GSM/GPRS/EGPRS, the power supply must be able to deliver

high current peaks in a short time. During the peaks, the ripple (Uripp) on the supply voltage must not

exceed a certain limit).

In communication mode, a GSM/GPRS class 2 terminal emits 577µs radio bursts every

4.615ms.

Figure 2. Power supply during GSM burst emission

Directly supplies the RF components with 3.8 V. It is essential to keep a minimum voltage

ripple at this connection in order to avoid any phase error.

The RF Power Amplifier current (2.1A max peak in GSM /GPRS mode) flows with a ratio of:

1/8 of the time (577µs every 4.615ms for GSM /GPRS cl. 2) and

2/8 of the time (1154µs every 4.615ms for GSM /GPRS cl. 10).

4/8 of the time (2302µs every 4.615ms for GSM /GPRS cl. 12).

The rising time is around 10µs.

Attention should be paid:

to the quality of the power supply:

linear regulation (recommended) or PWM (Pulse Width Modulation) converter (usable) are

preferred for low noise.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 24 of 112

Page 25

Product Technical Specification and

Customer Design Guidelines

PFM (Power Frequency Modulation) or PSM (Phase Shift Modulation) system must be

avoided.

to the capacity to deliver high current peaks in a short time (burst radio emission).

that the VBATT line supports peak currents with an acceptable voltage drop which

guarantees a VBATT minimal value of 3.4V.

For PCB design constraints related to power supply tracks, ground planes and shielding, refer to the

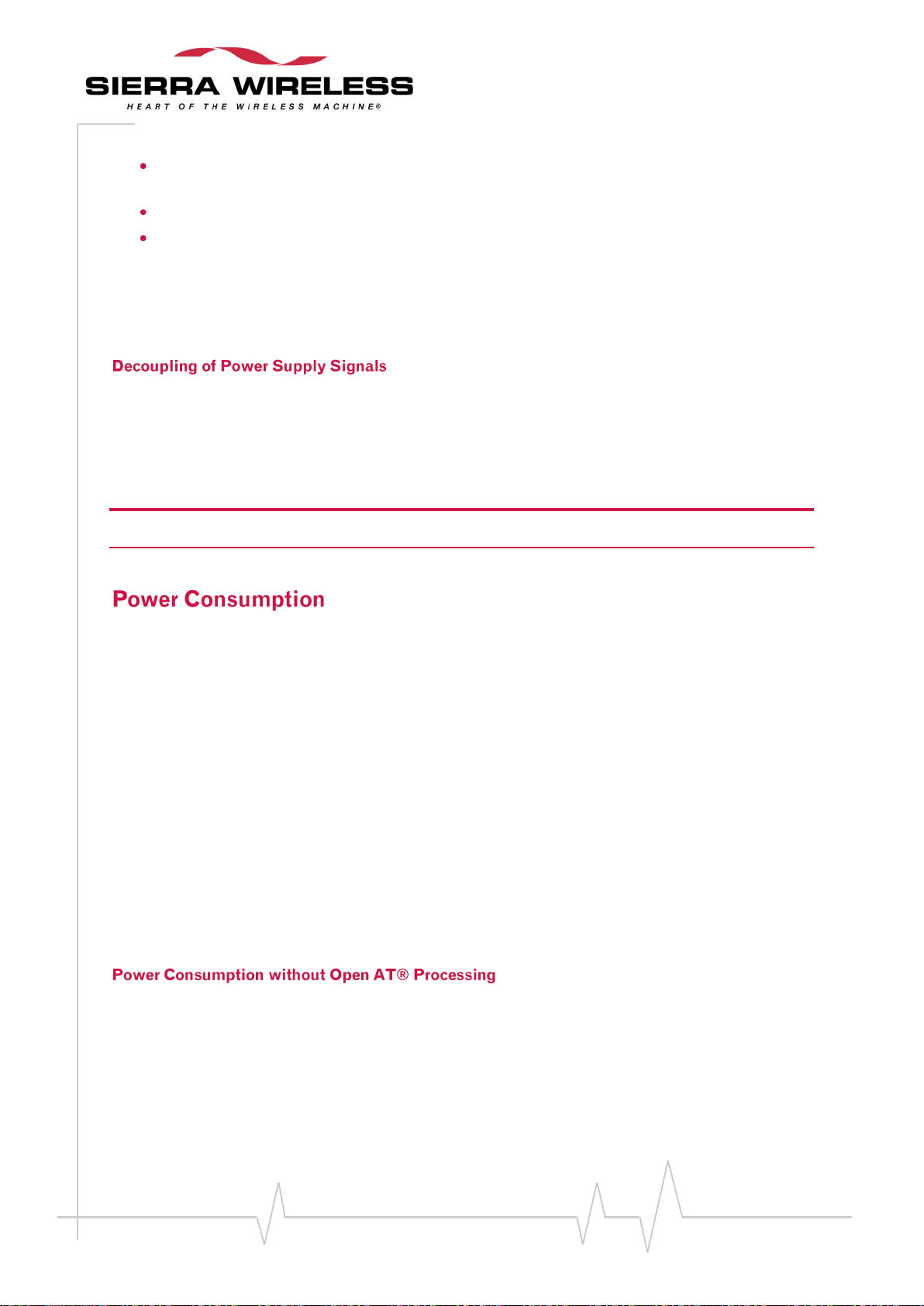

Design Guidelines section.

Decoupling capacitors on VBATT lines are embedded in the Wireless CPU. Hence, it should not be

necessary to add decoupling capacitors close to the Wireless CPU.

However, in case of EMI/RFI problem, VBATT signal may require some EMI/RFI decoupling: parallel

33 pF capacitor close to the Wireless CPU or a serial ferrite bead (or both to get better results). Low

frequency decoupling capacitors (22µF to 100µF) may be used to reduce the TDMA noise (217Hz).

Caution: When ferrite beads are used, the recommendation given for the power supply connection must

be followed with care (as high current capacity and low impedance).

Power consumption is dependent on the configuration used. It is for this reason that the following

consumption values are given for each mode, RF band and type of software used (AT or Open AT®).

All the following information is given assuming a 50 ohms RF output.

The following consumption values were obtained by performing measurements on the Wireless

CPU® samples at a temperature of 25° C.

Three VBATT values are used to measure the consumption, VBATTmin (3.4V), VBATTmax (4.2V) and

VBATTtyp (3.8V).

The average current is given for the three VBATT values and the peak current given is the maximum

current peak measured with the three VBATT voltages.

For a more detailed description of the operating modes, see the appendix of the AT Command User

Guide [5].

First let’s define start-up current in view to avoid start issues.

The following measurement results are relevant when there is no Open AT® application.

For explanation of power consumption mode, please Open AT® feature navigator document available

on Wavecom website.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 25 of 112

Page 26

Product Technical Specification and

Customer Design Guidelines

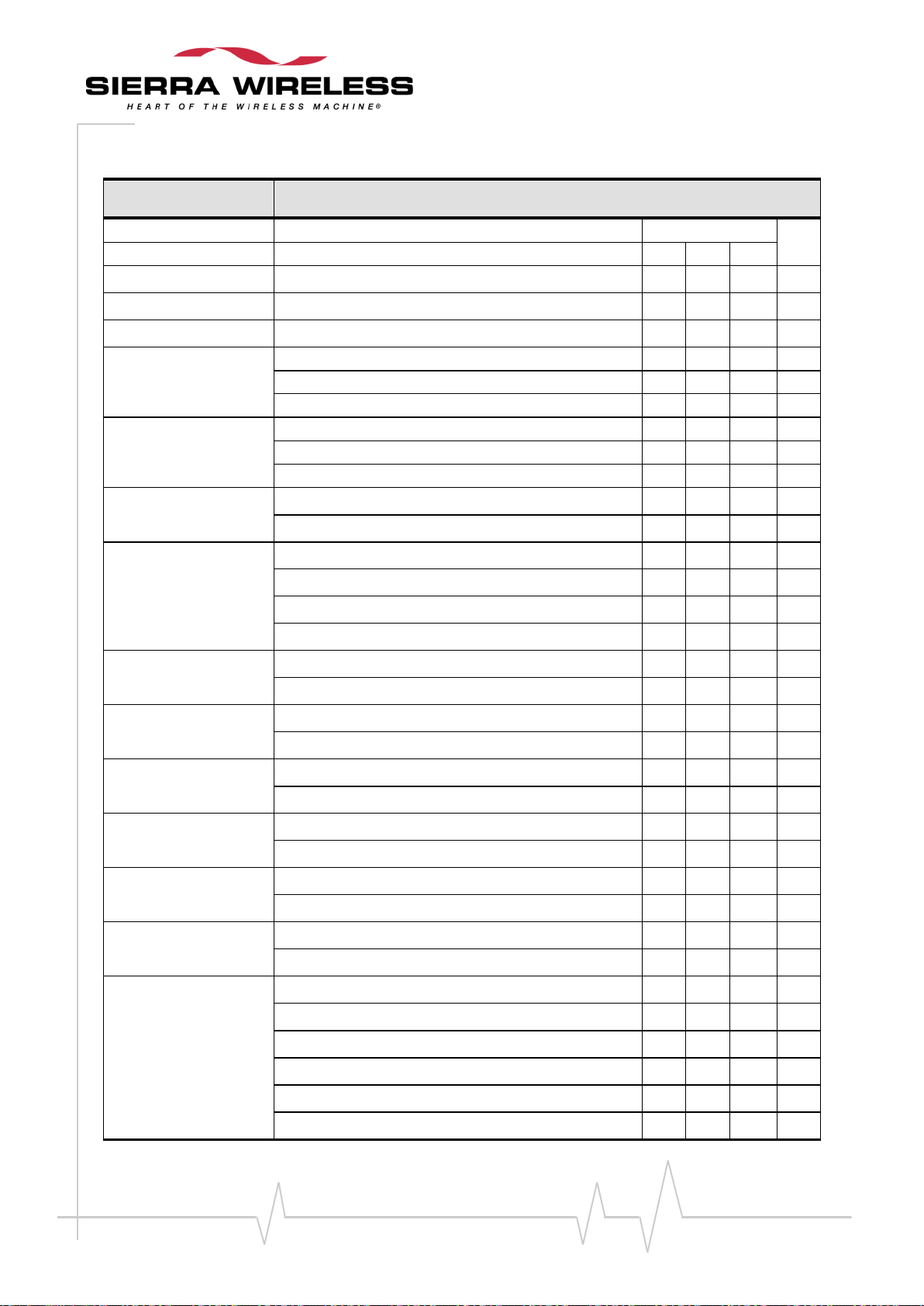

Table 7. Power Consumption without Open AT® Processing

Operating Mode

Power Consumption

Parameters

INOM average

Unit

VBATT=3.8V

Min

Typ

Max

ALARM Mode

16 µA

SLEEP Mode

1.4 mA

ACTIVE Mode

24.5

mA

SLEEP mode with

telecom stack in Idle

Mode 1

Case 2G (Paging 9/Rx burst occurrence ~2s)

3.1 mA

Case 2G (Paging 2/Rx burst occurrence ~0,5s)

6.4 mA

Case WCDMA (Paging 9)

2

mA

ACTIVE mode with

telecom stack in Idle

Mode 1

Case 2G (Paging 9/Rx burst occurrence ~2s)

28.6

mA

Case 2G (Paging 2/Rx burst occurrence ~0,5s)

32.8

mA

Case WCDMA (Paging 9)

27.6

mA

Peak current in

GSM/GPRS Mode

850/900 MHz - PCL5/gam.3 (TX power 33dBm)

2.1 A 1800/1900 MHz - PCL0/gam.3 (TX power 30dBm)

1.7

A

GSM Connected Mode

(Voice)

850/900 MHz - PCL5 (TX power 33dBm)

470 mA

850/900 MHz - PCL19 (TX power 5dBm)

300 mA

1800/1900 MHz - PCL0 (TX power 30dBm)

420 mA

1800/1900 MHz - PCL15 (TX power 0dBm)

290 mA

GPRS Transfer Mode

class 8 (4Rx/1Tx)

850/900 MHz - gam. 3(TX power 33dBm)

455 mA

1800/1900 MHz - gam.3(TX power 30dBm)

415 mA

GPRS Transfer Mode

class 10 (3Rx/2Tx)

850/900 MHz - gam.3 (TX power 30dBm)

570 mA

1800/1900 MHz - gam.3 (TX power 27dBm)

500 mA

GPRS Transfer Mode

class 12 (1Rx/4Tx)

850/900 MHz - gam.3 (TX power 27dBm)

720 mA

1800/1900 MHz - gam.3 (TX power 24dBm)

620 mA

EGPRS Transfer Mode

class 8 (4Rx/1Tx)

850/900 MHz - gam.6 (TX power 27dBm)

385 mA

1800/1900 MHz - gam.5 (TX power 26dBm)

380 mA

EGPRS Transfer Mode

class 10 (3Rx/2Tx)

850/900 MHz - gam.6 (TX power 24dBm)

480 mA

1800/1900 MHz - gam.5 (TX power 23dBm)

460 mA

EGPRS Transfer Mode

class 12 (1Rx/4Tx)

850/900 MHz - gam.6 (TX power 21dBm)

640 mA

1800/1900 MHz - gam.5 (TX power 20dBm)

600 mA

UMTS Connected Mode

(Voice)

BAND I @ +22 dBm

780

810

mA

BAND I @ +10 dBm

570 mA

BAND II @ +22 dBm

821

920

mA

BAND II @ +10 dBm

570 mA

BAND V @ +22 dBm

780

825

mA

BAND V @ +10 dBm

535 mA

WM_DEV_Q26EX_PTS_002 Rev 006 Page 26 of 112

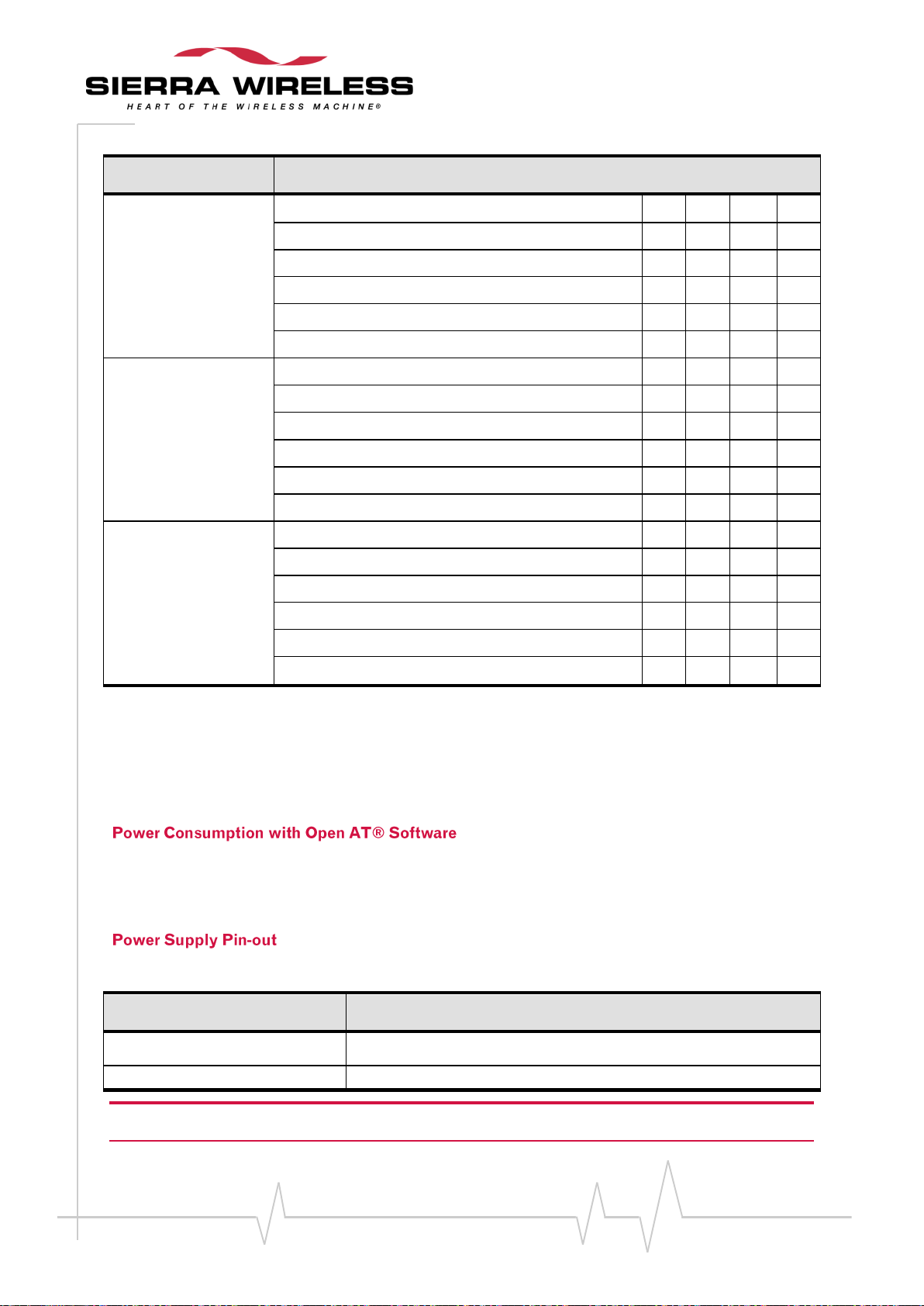

Page 27

Product Technical Specification and

Customer Design Guidelines

Operating Mode

Power Consumption

UMTS Data Transfer2

384kbits/s

BAND I @ +22 dBm

855

885

mA

BAND I @ +10 dBm

645 mA

BAND II @ +22 dBm

860

930

mA

BAND II @ +10 dBm

635 mA

BAND V @ +22 dBm

825

870

mA

BAND V @ +10 dBm

550 mA

HSDPA Data Transfer2

Cat. 8

7.2Mbits/s

BAND I @ +22 dBm

915

945

mA

BAND I @ +10 dBm

720 mA

BAND II @ +22 dBm

935

1050

mA

BAND II @ +10 dBm

720 mA

BAND V @ +22 dBm

875

920

mA

BAND V @ +10 dBm

625 mA

HSUPA Data Transfer2

Cat. 5

2Mbist/s

BAND I @ +22 dBm

890

920

mA

BAND I @ +10 dBm

705 mA

BAND II @ +22 dBm

920

990

mA

BAND II @ +10 dBm

710 mA

BAND V @ +22 dBm

875

920

mA

BAND V @ +10 dBm

625 mA

Signal

Pin number

VBATT

1,2,3,4

GND

Shielding

means that the current peak is the RF transmission burst (Tx burst)

TX

means that the current peak is the RF reception burst (Rx burst)

RX

1

This Mode consumption is dependent on the USIM card used. Some USIM cards respond faster than others, the longer

the response time, the higher the consumption. The measurements were performed with a large number of 3V USIM

cards, the results in brackets are the minimum and maximum currents measured from among all the USIMs used.

The activation of the Open AT® software could increase the power consumption up to 60mA in

ACTIVE mode and CONNECTED when the full CPU load is used by the Open AT® application.

Table 8. Power supply pin-out

Caution: The grounding connection is made through the shielding the four leads must be soldered to

the ground plane.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 27 of 112

Page 28

Product Technical Specification and

Customer Design Guidelines

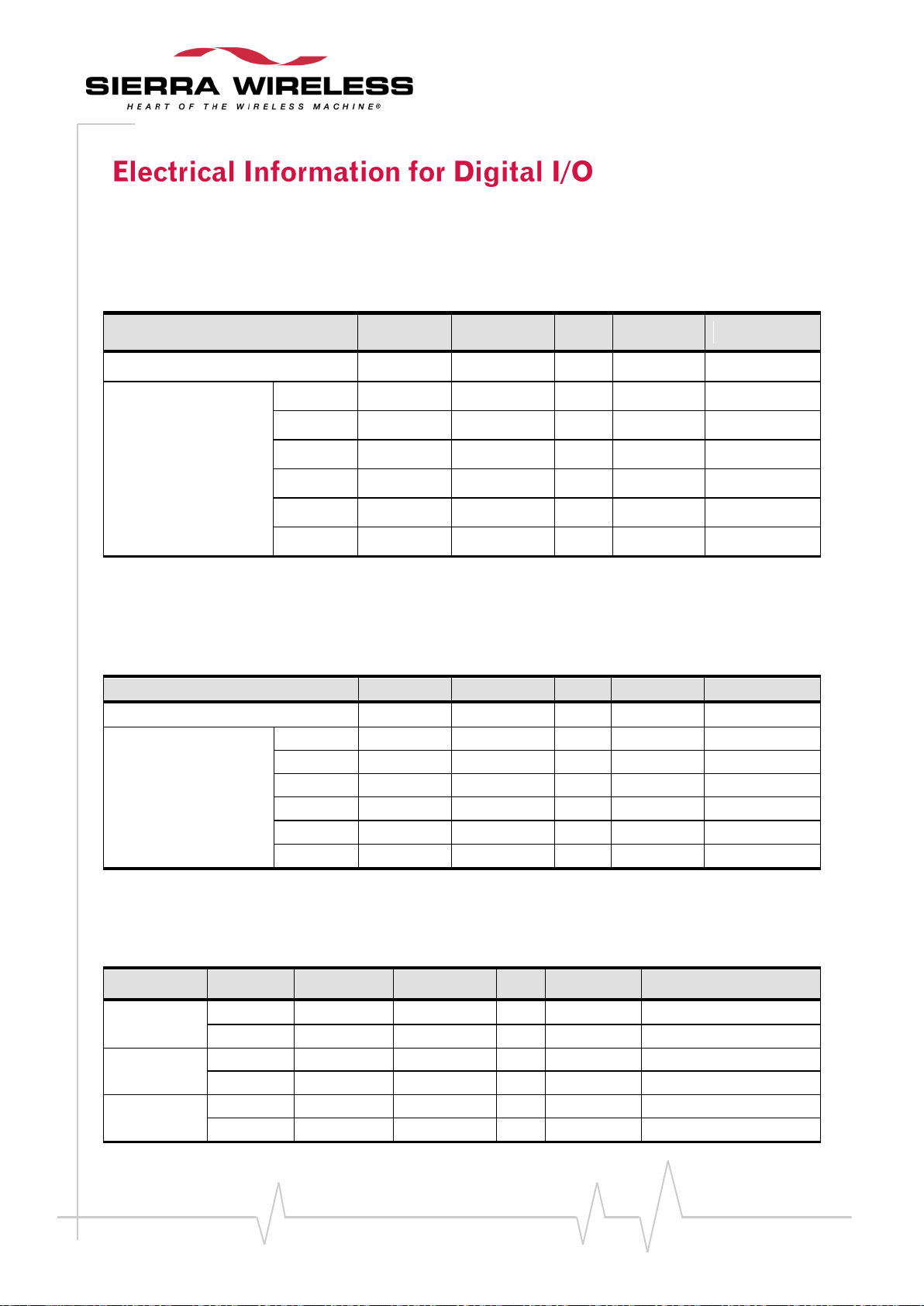

The three types of digital I/O on the Q26 Extreme Wireless CPU® are: 2.8Volt CMOS, 1.8Volt CMOS

Parameter

I/O type

Minim.

Typ

Maxim.

Condition

Internal 2.8V power supply

VCC_2V8

2.74V

2.8V

2.86V

Input / Output pin

VIL

CMOS

-0.5V*

0.84V

VIH

CMOS

1.96V

3.2V*

VOL

CMOS

0.4V

IOL = - 4 mA

VOH

CMOS

2.4V

IOH = 4 mA

IOH 4mA

IOL - 4mA

Parameter

I/O type

Minim.

Typ

Maxim.

Condition

Internal 1V8 power supply

VCC_1V8

1.76V

1.8V

1.94V

Input / Output pin

VIL

CMOS

-0.5V*

0.54V

VIH

CMOS

1.33V

2.2V*

VOL

CMOS

0.4V

IOL = - 4 mA

VOH

CMOS

1.4V

IOH = 4 mA

IOH 4mA

IOL - 4mA

Signal name

Parameter

I/O type

Minimum

Typ

Maximum

Condition

LED0

VOL

Open Drain

0.4V

IOL

Open Drain

8mA

BUZZER0

VOL

Open Drain

0.4V

IOL

Open Drain

100mA

SDA1/

GPIO27

VTOL

Open Drain

3.3V

Tolerated voltage

VIH

Open Drain

2V

and Open drain.

The three types are described below:

Table 9. 2.8 Volt type (2V8 )

*Absolute maximum ratings

All 2.8V I/O pins do not accept input signal voltage above the maximum voltage specified above,

except for the UART1 interface, which is 3.3V tolerant.

Table 10. 1.8 Volt type (1V8)

*Absolute maximum ratings

Table 11. Open drain output type

WM_DEV_Q26EX_PTS_002 Rev 006 Page 28 of 112

Page 29

Product Technical Specification and

Customer Design Guidelines

Signal name

Parameter

I/O type

Minimum

Typ

Maximum

Condition

and

SCL1/

GPIO26

VIL

Open Drain

0.8V

VOL

Open Drain

0.4V

IOL

Open Drain

3mA

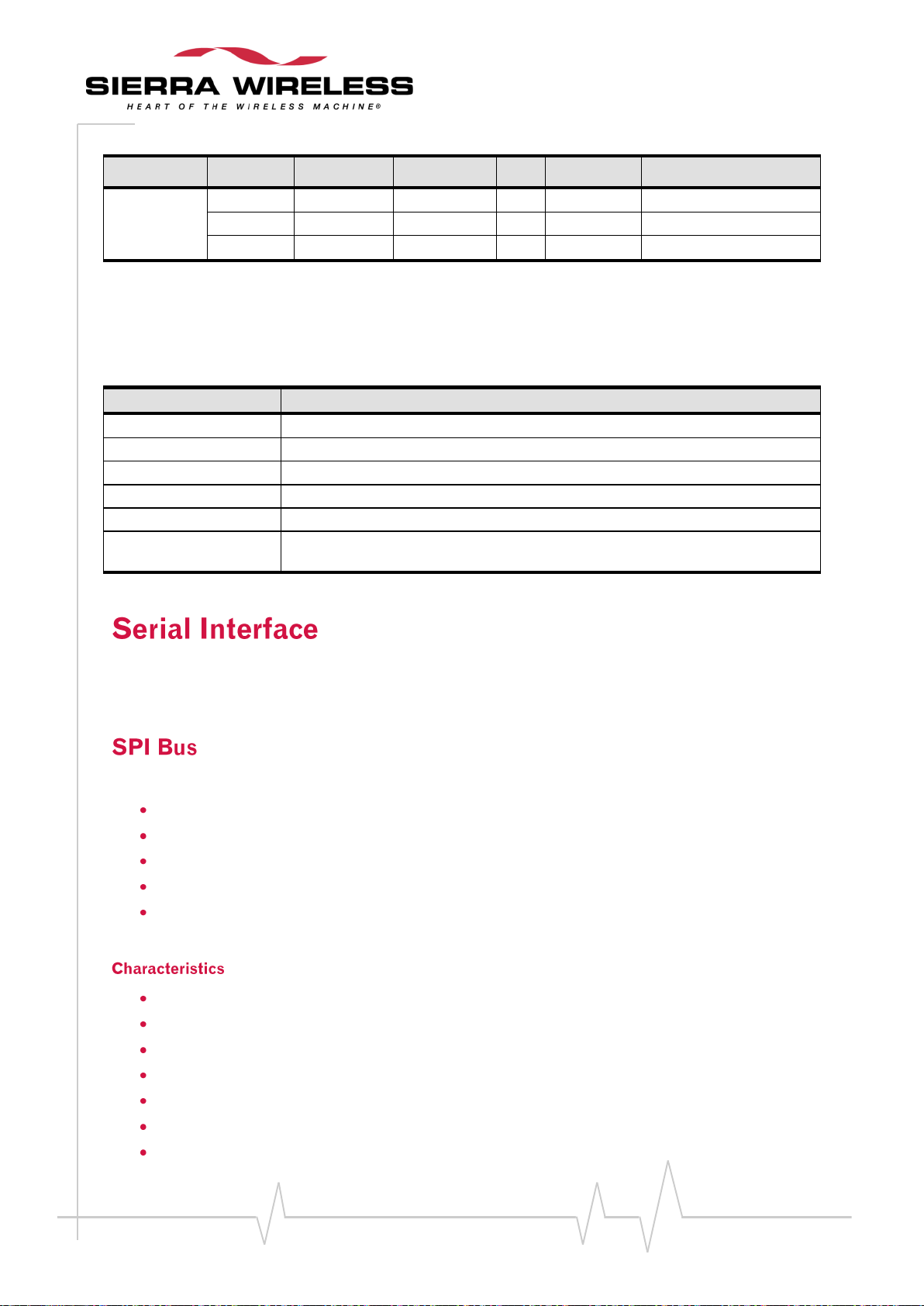

Parameter

Definition

0

Set to GND

1

Set to supply 1V8 or 2V8 depending on I/O type

Pull-down

Internal pull-down with ~60kohms resistor.

Pull-up

Internal pull-up with ~60kohms resistor to supply 1V8 or 2V8 depending on I/O type.

Z

High impedance

Undefined

Caution: undefined must not be used in your application if a special state is required

at reset. These pins may be a toggling signal during reset.

The reset states of the I/Os are given in each interface description chapter. Definitions of these states

are given below:

Table 12. Reset state definition

The Q26 Extreme Wireless CPU® provides two SPI bus (i.e. for LCD, memories…). or an I²C 2-wire

interface.

Both SPI bus interfaces include:

A CLK signal

An I/O signal

An I signal

A CS (Chip Select) signal complying with the standard SPI bus (any GPIO).

An optional Load signal (only the SPIx-LOAD signal)

Master mode operation

The CS signal must be any GPIO

The LOAD signal (optional) is used for the word handling mode (only the SPIx-LOAD signal)

SPI speed is from 102 kbit/s to 13 Mbit/s in master mode operation

3 or 4-wire interface(5-wire possible with the optional SPIx-LOAD signal)

SPI-mode configuration: 0 to 3

1 to 16 bits data length

WM_DEV_Q26EX_PTS_002 Rev 006 Page 29 of 112

Page 30

Product Technical Specification and

Customer Design Guidelines

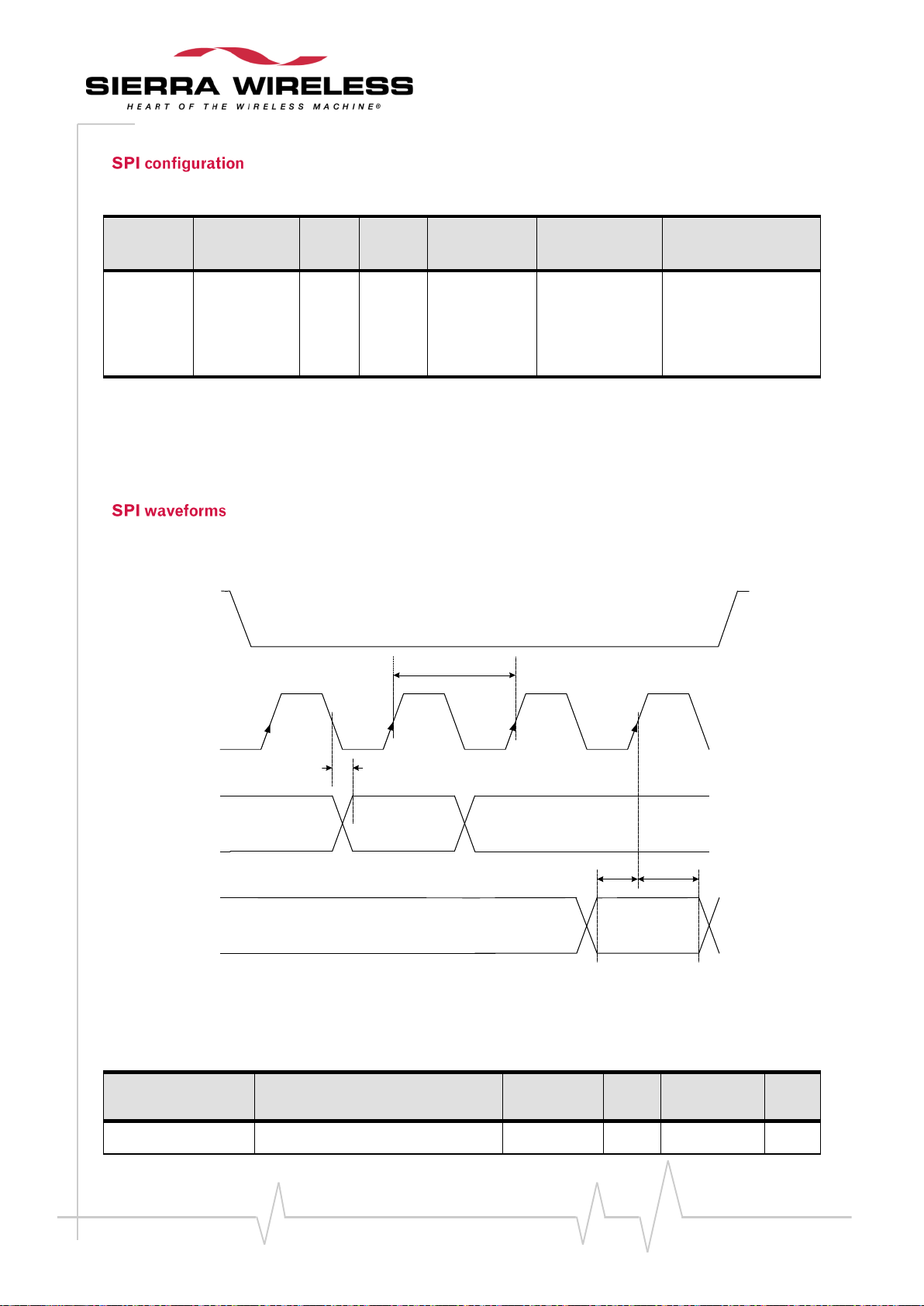

Table 13. SPI Configuration

Operation

Maximum

Speed

SPI-

Mode

Duplex

3-wire type

4-wire type

5-wire type

Master

13 Mb/s

0,1,2,3

Half

SPIx-CLK;

SPIx-IO;

GPIOx as CS

SPIx-CLK;

SPIx-IO;

SPIx-I;

GPIOx as CS

SPIx-CLK;

SPIx-IO;

SPIx-I;

GPIOx as CS;

SPIx-LOAD

(not muxed in GPIO);

Data-OUTdelay

CLK-cycle

Data-IN-hold

Data-IN-setup

SPIx-IO

Data valid

Data valid

SPIx-CLK

SPIx-I

GPIOx as CS

Signal

Description

Minimum

Typ

Maximum

Unit

CLK-cycle

SPI clock frequency

0.102

13

MHz

For the 3-wire configuration, SPIx-I/O is used as input and output.

For the 4-wire configuration, SPIx-I/O is used as output only, SPIx-I is used as input only.

For the 5-wire configuration, SPIx-I/O is used as output only, SPIx-I is used as input only. And the dedicated SPIx-LOAD

signal is used. It is an additional signal in more than a Chip Select (any other GPIOx)

Waveforms for SPI transfer with 4-wire configuration in master mode 0.

Figure 3. SPI Timing diagrams, Mode 0, Master, 4 wires

Table 14. AC characteristics

WM_DEV_Q26EX_PTS_002 Rev 006 Page 30 of 112

Page 31

Product Technical Specification and

Customer Design Guidelines

Signal

Description

Minimum

Typ

Maximum

Unit

Data-OUT delay

Data out ready delay time

10

ns

Data-IN-setup

Data in setup time

2

ns

Data-OUT-hold

Data out hold time

2

ns

Waveforms for SPI transfer with the SPIx-LOAD signal configuration in master mode 0 (chip select is

CLK-cycle

Tload_lead

SPIx-IO

D1

SPIx-CLK

SPIx-LOAD

D0

Tload_high Tload_lag

Dx

Signal

Pin

number

I/O

I/O

type

Reset

state

Description

Multiplexed

with

SPI1-CLK

23 O 2V8 Z SPI Serial Clock

GPIO28

SPI1-IO

25

I/O

2V8 Z SPI Serial input/output

GPIO29

SPI1-I

24 I 2V8 Z SPI Serial input

GPIO30

SPI1-LOAD

22 O 2V8 Z SPI load

GPIO31

not represented).

Figure 4. SPI Timing diagrams with SPIx-LOAD signal, Mode 0, Master, 4 wires

For Open drain, 2V8 and 1V8 voltage characteristics and Reset state definition refer to Chapter 3.3, "Electrical information for

digital I/O".

WM_DEV_Q26EX_PTS_002 Rev 006 Page 31 of 112

Table 15. Pins description

Page 32

Product Technical Specification and

Customer Design Guidelines

Table 16. Pins description

Signal

Pin

number

I/O

I/O

type

Reset

state

Description

Multiplexed

with

SPI2-CLK

26 O 2V8 Z SPI Serial Clock

GPIO32

SPI2-IO

27

I/O

2V8 Z SPI Serial input/output

GPIO33

SP2-I

29 I 2V8 Z SPI Serial input

GPIO34

SPI2-LOAD

28 O 2V8 Z SPI Load

GPIO35

Customer

application

Q26 Extreme

Wireless CPU

®

SPIx-IO

SPIx-CLK

~SPIx-LOAD

VCC_2V8

R1

SPIx-I

See Chapter 3.3 “Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage characteristics and Reset state

definition.

The specific feature of 4-wire serial interface (SPI bus) in which the input and output data lines are

disassociated. The SPIx-IO signal is used only for ouput data whereas the SPIx-I signal is used only

for input data.

Figure 5. Example of 4-wire SPI bus application

One pull-up resistor R1 is needed to set the SPIx-CS level for the reset state. R1 recommended value:

100kohm.

Except for R1, no external components are needed if the electrical specification of the customer

application complies with the Q26 Extreme Wireless CPU® SPIx interface electrical specification.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 32 of 112

Page 33

Product Technical Specification and

Customer Design Guidelines

The specific feature of 3-wire serial interface (SPI bus) in which the input and output data lines are

Customer

application

Q26 Extreme

Wireless CPU

®

SPIx-IO

SPIx-CLK

~SPIx-LOAD

VCC_2V8

R1

nc-SPIx-I

disassociated. The SPIx-IO signal is used for both output and input data.

Figure 6. Example of 3-wire SPI bus application

One pull-up resistor R1 is needed to set the SPIx-CS level for the reset state. R1 value depends on the

peripheral plugged on the SPIx interface. R1 recommended value: 100kohm.

Except for R1, no external components are needed if the electrical specification of the customer

application complies with the Q26 Extreme Wireless CPU® SPIx interface electrical specification.

The SPIx-I line is not used in 4-wire configuration. This line can be left open or used as GPIO for other

application’s functionality.

The SPIx interface voltage range is 2.8V. It can be powered either by VCC_2V8 (pin 10) of the Q26

Extreme Wireless CPU or by any other power supply.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 33 of 112

Page 34

Product Technical Specification and

Customer Design Guidelines

The I2C interface includes a clock signal (SCL1) and data signal (SDA1) complying with a 100kbit/s-

SCL-freq

T-free

SDA1

SCL1

Data valid Data valid

T-start

T-data hold T-data setup

T-high

T-stop

Signal

Description

Minimum

Typ

Maximum

Unit

SCL1-freq

I²C clock frequency

100 400

kHz

T-start

Hold time START condition

0.6

µs

T-stop

Setup time STOP condition

0.6

µs

T-free

Bus free time, STOP to START

1.3

µs

T-high

High period for clock

0.6

µs

T-data-hold

Data hold time

0 0.9

µs

T-data-setup

Data setup time

100

ns

standard interface (standard mode: s-mode).

The I²C bus is always master.

The maximum speed transfer range is 400kbit/s (fast mode: f-mode).

I²C bus waveform in master mode configuration:

Figure 7. I²C Timing diagrams, Master

Table 17. AC characteristics

WM_DEV_Q26EX_PTS_002 Rev 006 Page 34 of 112

Page 35

Product Technical Specification and

Customer Design Guidelines

Table 18. Pin description

Signal

Pin

number

I/O

I/O type

Reset

state

Description

Multiplexed

with

SCL1

44 O Open drain

Z

Serial Clock

GPIO26

SDA1

46

I/O

Open drain

Z

Serial Data

GPIO27

Customer

application

Q26 Extreme

Wireless CPU

®

SDA1

SCL1

1k 1k

VCC_2V8

See Chapter Caution:, "Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage characteristics and Reset

state definition.

The two lines need to be pulled-up to the V_I²C voltage. The V_I²C voltage is dependent on the

customer application component connected on the I²C bus. Nevertheless, the VI²C must comply with

the Q26 Extreme Wireless CPU® electrical specification.

The VCC_2V8 (pin 10) of the Q26 Extreme Wireless CPU® may be used to connect the pull-up

resistors, if the I²C bus voltage is 2.8 V.

Figure 8. Example of I²C bus application

The pull-up resistor values are selected depending on the mode used. For the Fast mode, it is

recommended to use 1kohm resistor in order to ensure the compliance with the I²C specification. For

the Standard mode, higher values of resistors may be used to save power consumption.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 35 of 112

Page 36

Product Technical Specification and

Customer Design Guidelines

The Q26 Extreme Wireless CPU® offers a 16 bits parallel and 1V8 bus interface. Its characteristics are

described below:

Up to 128 Mega Byte address range per chip select (CS2 and CS3),

Support for 8, 16, and 32 bit (multiplexed synchronous mode) devices,

Byte enable signals for 16 bit and 32 bits operation,

Fully programmable timings based on AHB (a division of the ARM clock at 26 MHz ) cycles

(except for synchronous mode which is based on CLKBURST cycles at 26 MHz only),

individually selectable timings for read and write,

0 to 7 clock cycles for setup,

1 to 32 clock cycles for access cycle,

1 to 8 clock cycles for page access cycle,

0 to 7 clock cycles for hold,

1 to 15 clock cycles for turnaround.

Page mode Flash memory support,

page size of 4, 8, 16 or 32,

Burst mode Flash memory support up to AHB (26 MHz) clock frequency (for devices

sensitive to rising edge of the clock only)

AHB, AHB/2, AHB/4 or AHB/8 burst clock output

burst size of 4, 8, 16, 32,

automatic CLKBURST power-down between accesses,

Intel mode (WE and OE) and Motorola mode (E and R/W) control signals,

Synchronous write mode,

Synchronous multiplexed data/address mode (x32 mode),

Adaptation to word, halfword, and byte accesses to the external devices.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 36 of 112

Page 37

Product Technical Specification and

Customer Design Guidelines

Table 19. Pinout Definitions

Signal

Pin

number

Reset

state

I/O

I/O

type

Description

Multiplexed

with

D0

85

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D1

87

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D2

89

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D3

91

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D4

93

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D5

95

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D6

97

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D7

99

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D8

100

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D9

98

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D10

96

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D11

94

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D12

92

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D13

90

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D14

88

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

D15

86

Pull down

I/O

1V8

Bidirectional data and address line

Not mux

~OER/W

81 1 O

1V8

Output enable signal (Intel mode);

read not write signal (Motorola mode)

Not mux

~WE-E

84 1 O

1V8

Write enable Signal (Intel mode)

Enable signal (Motorola mode)

Not mux

~CS3

83

Pull up

I/O

1V8

User Chip select 3

GPIO44

~CS2

51

Pull up

I/O

1V8

User Chip Select 2

GPIO1/INT2

A1

42 1 O

1V8

This signal has 2 functions:

external Address or byte enable 2 for

16 or 32 bits devices.

An other name is used : A1_BE2

Not mux

A24

53 Z I/O

1V8

Address line for external device /

Command selection

GPIO2

For all timing diagrams in the following section the notations here after are used:

ADR is used for address bus A [24,1] or D [15:0].when used as address lines.

DATA is used for D[15:0] when used as DATA lines

~CS is used for ~CS2 or~CS3.

~BE is used for A1_~BE2 (Double function on A1 pin).

~OE and R/W are used for ~OE_R/W

WM_DEV_Q26EX_PTS_002 Rev 006 Page 37 of 112

Page 38

Product Technical Specification and

Customer Design Guidelines

~WE and E are used for ~WE_E

Signal

Description

Minimum

Typ

Maximum

Unit

TADR_DELAY

ADR delay time from ~CS active

3

ns

TDATA_SETUP

DATA to ~OE setup time

18

ns

TDATA_HOLD

DATA hold time after ~OE inactive

3 4

ns

TDATA_DELAY

DATA delay time from ~CS active

5

ns

TDATA_SECURE

DATA hold time after ~WE inactive or

~CS inactive

-5[1]

ns

TADV_DELAY

ADV delay time from ~CS active and

inactive

3

ns

TWE_DELAY

~WE delay time from ~CS active

3[2]

ns

TOE_DELAY

~OE delay time from ~CS active

3[2]

ns

TBE_DELAY

~BE delay time from ~CS active

3

ns

~ADV signal (Not available on 100 pins connector) is the address valid signal.

Figure 9. Asynchronous access

The ~ADV signal is mentioned here because synchronous mode devices may require the signal to be

asserted when an asynchronous access is performed.

Table 20. AC Characteristic of Asynchronous Accesses

[1]

This timing forces to program at least one cycle for asynchronous.

[2]

These maximum delays depend also on setting of registers

WM_DEV_Q26EX_PTS_002 Rev 006 Page 38 of 112

Page 39

Product Technical Specification and

Customer Design Guidelines

For all timing diagrams in the following section the notations here after are used:

ADR is used for address bus as A24, A1 or D [15:0].when used as address lines.

DATA is used for D [15:0]. when used as data lines.

~CS is used for ~CS2 or ~CS3.

~BE is used for A1_~BE2 (Double function on A1 pin).

~OE and R/W are used for ~OE_R/W.

~WE and E are used for ~WE_E

CLKBURST: is the internal clock at 26 MHz (Not available on connector pinout).

~ADV signal (Not available on 100 pins connector) is the address valid signal.

~BAA: signal (Not available on 100 pins connector): is the burst address advance for

synchronous operations.

~WAIT signal (Not available on 100 pins connector): is the wait signal for synchronous

operation.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 39 of 112

Page 40

Product Technical Specification and

Customer Design Guidelines

Figure 10. Read synchronous timing

WM_DEV_Q26EX_PTS_002 Rev 006 Page 40 of 112

Figure 11. Write synchronous timing

Page 41

Product Technical Specification and

Customer Design Guidelines

Table 21. AC Characteristic of Asynchronous Accesses

Signal

Description

Minimum

Typ

Maximum

Unit

TDATA_DELAY

CLKBURTS falling edge to DATA valid

delay

4

ns

TWE_SETUP

WE to CLKBURST setup time

7

ns

TBE_DELAY

CLKBURST falling edge to BE delay

4

ns

TCLKBURST

CLKBURST clock : period time

38.4

ns

TADR_SETUP

Address bus setup time

7

ns

TADR_HOLD

Address bus hold time

19

ns

TADR_TRISTATE

Address bus tristate time

10

ns

TDATA_SETUP

Data bus setup time

5

ns

TDATA_HOLD

Data bus hold time

3

ns

TCS_SETUP

Chip select setup time

7

ns

TADV_SETUP

ADV setup time

7

ns

TADV_HOLD

ADV hold time

7

ns

TOE_DELAY

Output Enable delay time

13

ns

TBAA_DELAY

BAA delay time

13

ns

TWAIT_SETUP

Wait setup time

5

ns

TWAIT_HOLD

Wait hold time

5

ns

WM_DEV_Q26EX_PTS_002 Rev 006 Page 41 of 112

Page 42

Product Technical Specification and

Customer Design Guidelines

For example, it is possible to interface an NAND memory.

Address bus size

Address lines

Chip select available

1

A1

/CS2, /CS3

2

A1, A24

/CS2, /CS3

Figure 12. Example of parallel bus application (NAND)

The following table lists the possible configurations depending on address bus size requested on

parallel interface.

Table 22. Address bus size details

Few signals are multiplexed. It is thus possible to have these configurations.

~CS3*, A1, GPIO2

~CS3*, A1, A24,

~CS3*, ~CS2*, A1, GPIO2

~CS3*, ~CS2*, A1, A24

WM_DEV_Q26EX_PTS_002 Rev 006 Page 42 of 112

Page 43

Product Technical Specification and

Customer Design Guidelines

This interface provides 10 connections:

Signal

Pin

number

I/O

I/O

type

Reset

state

Description

Multiplexed with

ROW0

68

I/O

1V8 0 Row scan

GPIO9

ROW1

67

I/O

1V8 0 Row scan

GPIO10

ROW2

66

I/O

1V8 0 Row scan

GPIO11

ROW3

65

I/O

1V8 0 Row scan

GPIO12

ROW4

64

I/O

1V8 0 Row scan

GPIO13

COL0

59

I/O

1V8

Pull-up

Column scan

GPIO4

COL1

60

I/O

1V8

Pull-up

Column scan

GPIO5

COL2

61

I/O

1V8

Pull-up

Column scan

GPIO6

COL3

62

I/O

1V8

Pull-up

Column scan

GPIO7

COL4

63

I/O

1V8

Pull-up

Column scan

GPIO8

5 rows (ROW0 to ROW4) and

5 columns (COL0 to COL4).

The scanning is a digital one and debouncing is performed in the Q26 Extreme Wireless CPU®.

No discrete components such as Rs, Cs (Resistors, Capacitors) are needed.

Table 23. Keyboard interface pin description

See Chapter Caution:, “Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage characteristics and for

Reset state definition.

With the Open AT® Software, when the keyboard service is used, the whole multiplexed signals

become unavailable for other purposes. In the same way if one or more GPIOs (of this table) are

allocated the keyboard service is unavailable.

Figure 13. Example of keyboard implementation

WM_DEV_Q26EX_PTS_002 Rev 006 Page 43 of 112

Page 44

Product Technical Specification and

Customer Design Guidelines

A flexible 8-wire serial interface is available, complying with V24 protocol signaling, but not with V28

Signal

Pin

number

I/O

I/O

type

Reset state

Description

Multiplexed

with

CT103-TXD1*

71 I 2V8 Z Transmit serial data

GPIO36

CT104-RXD1*

73 O 2V8 Z Transmit serial data

GPIO37

~CT105-RTS1*

72 I 2V8 Z Request To Send

GPIO38

~CT106-CTS1*

75 O 2V8 Z Clear To Send

GPIO39

~CT107-DSR1*

74 O 2V8 Z Data Set Ready

GPIO40

~CT108-2-DTR1*

76 I 2V8 Z Data Terminal Ready

GPIO41

~CT109-DCD1 *

70 O 2V8

Undefined

Data Carrier Detect

GPIO43

~CT125-RI1 *

69 O 2V8

Undefined

Ring Indicator

GPIO42

CT102-GND*

Shielding

leads

GND

Ground

(electrical interface) due to a 2.8 volts interface.

The signals are:

TX data (CT103-TX)

RX data (CT104-RX)

Request To Send (~CT105-RTS)

Clear To Send (~CT106-CTS)

Data Terminal Ready (~CT108-2-DTR)

Data Set Ready (~CT107-DSR).

Data Carrier Detect (~CT109-DCD)

Ring Indicator (CT125-RI).

Table 24. UART1 interface pin description

* See Chapter 3.3 Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage characteristics and for the

reset state definition.

*According to PC view

With the Open AT® Software Suite, when the UART1 service is used, the whole multiplexed signals

become unavailable for other purposes. In the same way if one or more GPIOs (of this table) are

allocated the UART1 service is unavailable.

The rise and fall time of the reception signals (mainly CT103) must be less than 300 ns.

The maximum baud rate of UART1 is 921 kbit/s for the Open AT® Software Suite firmware.

Caution: The Q26 Extreme Wireless CPU® is designed to operate using all the serial interface signals. In

particular, it is mandatory to use RTS and CTS for hardware flow control in order to avoid data

loss/corruption during transmission.

The level shifter must be a 2.8V with V28 electrical signal compliant.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 44 of 112

Page 45

Product Technical Specification and

Customer Design Guidelines

Figure 14. Example of RS-232 level shifter implementation for UART1

U1 chip also protects the Wireless CPU against ESD at 15kV. (Air Discharge)

Recommended Components:

R1, R2: 15kohm

C1, C2, C3, C4, C5: 1uF

C6: 100nF

C7: 6.8uF TANTAL 10V CP32136 AVX

U1: ADM3307AECP Analog devices

J1: SUB-D9 female

R1 and R2 are necessary only during Reset state, to force the ~CT1125-RI1 and ~CT109-DCD1 signal to

high levels.

The ADM3307AECP chip has a maximum speed of 921kbits/s. If other level shifters are used, ensure

that their speeds are compliant with the UART1 useful speed.

The ADM3307AECP can be powered either by VCC_2V8 (pin 10) of the Q26 Extreme Wireless CPU®

or by an external regulator at 2.8 volts.

If the UART1 interface is connected directly to a host processor, it is not necessary to use level shifters.

The interface can be connected as shown in the figure 15.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 45 of 112

Page 46

Product Technical Specification and

Customer Design Guidelines

V24/CMOS possible design:

Customer application

( DTE )

Q26 Extreme

Wireless CPU

( DCE )

GND

~RESET

ON / ~OFF

CT103-TXD1 / GPIO36

CT104-RXD1 / GPIO37

~CT105-RTS1 / GPIO38

~CT106-CTS1 / GOPI39

19

75

72

73

18

71

Shielding

Rx

RTS

CTS

GND

Tx

Customer application

( DTE )

Q26 Extreme

Wireless CPU

( DCE )

GND

~RESET

ON / ~OFF

~CT107-DSR1 / GPIO40

~CT109-DCD1 / GPIO43

~CT108-2-DTR1 / GPIO41

~CT125-RI1 / GPIO42

19

69

76

70

18

74

Shielding

DCD

DTR

RI

GND

DSR

CT103-TXD1 / GPIO36

CT104-RXD1 / GPIO37

~CT105-RTS1 / GPIO38

~CT106-CTS1 / GOPI39

75

72

73

71

Rx

RTS

CTS

Tx

2x 15k

2.8Volt

Figure 15. Example of V24/CMOS serial link implementation for UART1

The design shown in the above figure is a basic design type.

However, a more flexible design to access this serial link with all the modem signals is shown below:

Figure 16. Example of full modem V24/CMOS serial link implementation for UART1

It is recommended to add 15kohm pull-up resistor on ~CT125-RI1 and ~CT109-DCD1 to set high level

for reset state.

The UART1 interface is a 2.8 volts type. Moreover, it is 3.3 volts tolerant.

For use with 5-wire serial interface

WM_DEV_Q26EX_PTS_002 Rev 006 Page 46 of 112

Signal: CT103-TXD1*, CT104-RXD1*, ~CT105-RTS1*, ~CT106-CTS1*

Page 47

Product Technical Specification and

Customer Design Guidelines

The signal ~CT108-2-DTR1* must be managed by following the V24 protocol signaling, if you

Signal

Pin

number

I/O

I/O type

Reset

state

Description

Multiplexed

with

CT103-TXD2*

31 I 1V8 Z Transmit serial data

GPIO14

CT104-RXD2*

30 O 1V8 Z Receive serial data

GPIO15

~CT106-CTS2*

32 O 1V8 Z Clear To Send

GPIO16

~CT105-RTS2*

33 I 1V8 Z Request To Send

GPIO17

want to use the slow idle mode.

Other signals and their multiplexes are not available.

Please refer to technical appendixes of AT Commands Manual [5] for more information.

For use with 4-wire serial interface

CT103-TXD1*, CT104-RXD1*, ~CT105-RTS1*, ~CT106-CTS1*

The signal ~CT108-2-DTR1* must be configured at low level.

Other signals and their multiplexes are not available.

Please refer to technical appendixes in the AT Commands Manual [5] for more information.

For use with 2-wire serial interface

This case is possible for connected external chip, but not recommended (and forbidden for AT

command or modem use)

The flow control mechanism has to be managed at the customer side.

CT103-TXD1*, CT104-RXD1*

The signal ~CT108-2-DTR1* must be configured at low level.

The signals ~CT105-RTS1*, ~CT106-CTS1* are not used, please configure the AT command

(AT+IFC=0,0 see AT command User Guide [5]).

The signal ~CT105-RTS1* must be configured at low level.

Other signals and their multiplexes are not available.

Please refer to technical appendixes in the AT Commands Manual [5] for more information.

An auxiliary serial interface (UART2) is available on Q26 Extreme Wireless CPU®. This interface may

be used to connect a Bluetooth or a GPS chip controlled by an Open AT® Plug-in.

Table 25. UART2 interface pin description

See Chapter Caution:, “Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage characteristics and Reset

state definition.

* According to PC view

WM_DEV_Q26EX_PTS_002 Rev 006 Page 47 of 112

Page 48

Product Technical Specification and

Customer Design Guidelines

Caution: The Q26 Extreme Wireless CPU® UART2 is designed to operate using all the serial interface

Q26 Extreme

signals. In particular, it is recommended to use RTS and CTS for hardware flow control in order

to avoid data corruption during transmission.

The maximum baud rate of UART2 is 921 kbit/s for the Open AT® Software Suite firmware.

The voltage level shifter must be a 1.8 volts with V28 electrical signal compliant.

Figure 17. Example of RS-232 level shifter implementation for UART2

Recommended components:

Capacitors

C1: 220nF

C2, C3, C4: 1μF

Inductor

L1: 10μH

RS-232 Transceivers

U1: LINEAR TECHNOLOGY LTC

®

2804IGN

J1: SUB-D9 female

The LTC2804 may be powered either by VCC_1V8 (pin 5) of the Q26 Extreme Wireless CPU® or by an

external regulator at 1.8 volts.

The UART2 interface may be connected directly to other components, if the voltage interface is 1.8V.

For use with 4-wire serial interface

CT103-TXD2*, CT104-RXD2*, ~CT105-RTS2*, ~CT106-CTS2*

The signal ~CT108-2-DTR2* must be configured at low level.

Other signals and their multiplexes are not available.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 48 of 112

Page 49

Product Technical Specification and

Customer Design Guidelines

Please refer to technical appendixes in the AT Commands Manual [5] for more information.

Signal

Pin

number

I/O

I/O type

Reset

state

Description

Multiplexed

with

SIM-CLK

14 O 2V9 / 1V8

0

USIM Clock

Not mux

~SIM-RST

13 O 2V9 / 1V8

0

USIM Reset

Not mux

SIM-IO

11

I/O

2V9 / 1V8

*Pull-up

USIM Data

Not mux

SIM-VCC

9 O 2V9 / 1V8

USIM Power

Supply

Not mux

SIMPRES

12 I 1V8

Z

USIM Card

Detect

GPIO18

For use with 2-wire serial interface

This case is possible for connected external chip, but not recommended (and forbidden for AT

command or modem use)

The flow control mechanism has to be managed at the customer side.

CT103-TXD2*, CT104-RXD2*

The signals ~CT105-RTS2*, ~CT106-CTS2* are not used, you must configure the AT command

(AT+IFC=0,0 see AT Commands Manual [5]).

The signal ~CT105-RTS2* must be configured at low level.

Other signals and their multiplexes are not available.

Please refer to technical appendixes in the AT Commands Manual [5] for more information.

The Universal Subscriber Identification Module (USIM) may be directly connected to the Q26

Extreme Wireless CPU® via this dedicated interface. Using the USIM is recommended over the SIM

card.

The five signals are:

SIM-VCC: USIM power supply

~SIM-RST: reset

SIM-CLK: clock

SIM-IO: I/O port

SIMPRES: USIM card detect

The USIM interface controls a 1V8/3V USIM.

Table 26. USIM interface pin description

*USIM-IO pull-up is about 10kohm

WM_DEV_Q26EX_PTS_002 Rev 006 Page 49 of 112

Page 50

Product Technical Specification and

Customer Design Guidelines

* See Chapter 3.3 “Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage characteristics and Reset

state definition.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 50 of 112

Page 51

Product Technical Specification and

Customer Design Guidelines

Table 27. USIM interface electrical characteristics

Parameter

Conditions

Minim.

Typ

Maxim.

Unit

SIM-IO VIH

IIH = ± 20µA

0.7xSIMVCC

V

SIM-IO VIL

IIL = 1mA

0.4

V

~SIM-RST, SIM-CLK

VOH

Source current = 20µA

0.9xSIMVCC

V

SIM-IO VOH

Source current = 20µA

0.8xSIMVCC

~SIM-RST, SIM-IO,

SIM-CLK

VOL

Sink current = -200µA

0.4

V

SIM-VCC Output Voltage

SIMVCC = 2.9V

IVCC= 1mA

2.84

2.9

2.96

V

SIMVCC = 1.8V

IVCC= 1mA

1.74

1.8

1.86

V

SIM-VCC current

VBATT = 3.8V

10

mA

SIM-CLK Rise/Fall Time

Loaded with 30pF

20 ns

~SIM-RST, Rise/Fall Time

Loaded with 30pF

20 ns

SIM-IO Rise/Fall Time

Loaded with 30pF

0.7 1 µs

SIM-CLK Frequency

Loaded with 30pF

3.25

MHz

Q26 Extreme

Note: When SIMPRES is used, a low to high transition means that the USIM card is inserted and a high to

low transition means that the USIM card is removed.

Figure 18. Example of SIM Socket implementation

WM_DEV_Q26EX_PTS_002 Rev 006 Page 51 of 112

Page 52

Product Technical Specification and

Customer Design Guidelines

Recommended components:

Signal

Pin number

Description

VCC

1

SIM-VCC

RST

2

~SIM-RST

CLK

3

SIM-CLK

CC4

4

SIMPRES with 100 k pull-down resistor

GND

5

GROUND

VPP

6

Not connected

I/O 7 SIM-IO

CC8

8

VCC_1V8 of Wireless CPU (pin 5)

R1: 100 kohm

C1: 470 pF

C2: 100 nF

D1: ESDA6V1SC6 from ST

D2: DALC208SC6 from SGS-THOMSON

J1: ITT CANNON CCM03 series

The capacitor (C2) placed on the SIM-VCC line must not exceed 330 nF.

Table 28. Pin description of the SIM socket

WM_DEV_Q26EX_PTS_002 Rev 006 Page 52 of 112

Page 53

Product Technical Specification and

Customer Design Guidelines

The Q26 Extreme Wireless CPU® provides up to 45 General Purpose I/Os, used to control any external

Signal

Pin

number

I/O

I/O type*

Reset state

Multiplexed with

GPIO0

43

I/O

2V8

Undefined

32kHz**

GPIO1

51

I/O

1V8

Pull-up

~CS2 / INT2

GPIO2

53

I/O

1V8 Z A24

GPIO3

50

I/O

1V8 Z INT0

GPIO4

59

I/O

1V8

Pull-up

COL0

GPIO5

60

I/O

1V8

Pull-up

COL1

GPIO6

61

I/O

1V8

Pull-up

COL2

GPIO7

62

I/O

1V8

Pull-up

COL3

GPIO8

63

I/O

1V8

Pull-up

COL4

GPIO9

68

I/O

1V8 0 ROW0

GPIO10

67

I/O

1V8 0 ROW1

GPIO11

66

I/O

1V8 0 ROW2

GPIO12

65

I/O

1V8 0 ROW3

GPIO13

64

I/O

1V8 0 ROW4

GPIO14

31

I/O

1V8 Z CT103-TXD2

GPIO15

30

I/O

1V8 Z CT104-RXD2

GPIO16

32

I/O

1V8 Z ~CT106-CTS2

GPIO17

33

I/O

1V8 Z ~CT105-RTS2

GPIO18

12

I/O

1V8 Z SIMPRES

GPIO19

45

I/O

2V8 Z Not mux

GPIO20

48

I/O

2V8

Undefined

Not mux

GPIO21

47

I/O

2V8

Undefined

Not mux

GPIO22

57

I/O

2V8 Z Not mux*

GPIO23

55

I/O

2V8 Z Not mux

GPIO24

58

I/O

2V8 Z Not mux

GPIO25

49

I/O

2V8 Z INT1

GPIO26

44

I/O

Open drain

Z

SCL1

device such as an LCD or a Keyboard backlight.

Table 29. GPIO pin description

WM_DEV_Q26EX_PTS_002 Rev 006 Page 53 of 112

Page 54

Product Technical Specification and

Customer Design Guidelines

Signal

Pin

number

I/O

I/O type*

Reset state

Multiplexed with

GPIO27

46

I/O

Open drain

Z

SDA1

GPIO28

23

I/O

2V8 Z SPI1-CLK

GPIO29

25

I/O

2V8 Z SPI1-IO

GPIO30

24

I/O

2V8 Z SP1-I

GPIO31

22

I/O

2V8 Z SPI1_LOAD

GPIO32

26

I/O

2V8 Z SPI2-CLK

GPIO33

27

I/O

2V8 Z SPI2-IO

GPIO34

29

I/O

2V8 Z SPI2-I

GPIO35

28

I/O

2V8 Z SPI2_LOAD

GPIO36

71

I/O

2V8 Z CT103-TXD1

GPIO37

73

I/O

2V8 1 CT104-RXD1

GPIO38

72

I/O

2V8 Z ~CT105-RTS1

GPIO39

75

I/O

2V8 Z ~CT106-CTS1

GPIO40

74

I/O

2V8 Z ~CT107-DSR1

GPIO41

76

I/O

2V8 Z ~CT108-2-DTR1

GPIO42

69

I/O

2V8

Undefined

~CT125-RI1

GPIO43

70

I/O

2V8

Undefined

~CT109-DCD1

GPIO44

83

I/O

2V8

Pull-up

PWM1 / ~CS3

See Chapter 3.3, “Electrical information for digital I/O” for Open drain, 2V8 and 1V8 voltage characteristics and Reset

state definition.

* If a Bluetooth module is used with the Q26 Extreme Wireless CPU®, these GPIOs must be reserved.

** With the Open AT® Software Suite see “AT Commands Manual ” [5].

Reset State:

0: Set to GND

1: Set to supply 1V8 or 2V8 depending on I/O type.

Pull-down: Internal pull-down with ~60k resistor.

Pull-up: Internal pull-up with ~60k resistor to supply 1V8 or 2V8 depending on I/O type.

Z: High impedance.

Undefined: caution, undefined must not be used in your application if a special state at

reset is needed. These pins may be of toggling signals.

Two Analog to Digital Converter inputs are provided by the Q26 Extreme Wireless CPU®. The

converters are more than 10-bit resolution, ranging from 0 volt to 2 volts.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 54 of 112

Page 55

Product Technical Specification and

Customer Design Guidelines

ADC1 / BAT-TEMP input can be used, typically, to monitor external temperature, useful for safety

Signal

Pin number

I/O

I/O type

Description

ADC1/BAT-TEMP*

20 I Analog

A/D converter

ADC2

21 I Analog

A/D converter

Parameter

Min

Typ

Max

Unit

Maximum output code

1635

LSB

Sampling period

0,5 3* s Input signal range

0 2

V

Input impedance

ADC1/BAT-TEMP

1M

ADC2

1M

Signal

Pin number

I/O

I/O type

Description

DAC0

82 O Analog

D/A converter

Parameter

Min

Typ

Max

Unit

Resolution

- 8 -

bits

Maximum Output voltage

2.1

2.2

2.3

V

power off in case of application over heating (for Li-Ion battery).

ADC2 input can be used for customer application.

Table 30. ADC pin description

* This input can be used for a battery charging temperature sensor,

see Chapter 0, “Battery Charging interface“.

Table 31. ADC electrical characteristics

*Sampling rate only for ADC2 and Open AT® application.

One Digital to Analog Converter (DAC) input is provided by the Wireless Microprocessor®.

The converter is 8-bit resolution, guaranteed monotonic with a range from 0V to 2.3V. This output

assumes a typical external load of 2k and 50pF in parallel to GND.

Table 32. Pin description of the DAC

Table 33. Electrical Characteristics of the DAC

WM_DEV_Q26EX_PTS_002 Rev 006 Page 55 of 112

Page 56

Product Technical Specification and

Customer Design Guidelines

Parameter

Min

Typ

Max

Unit

Minimum Output voltage

0 - 40

mV

Output voltage after reset

-

1.147

-

V

Integral Accuracy

-5 - +5

LSB

Differential Accuracy

-1 - +1

LSB

Full scale settling time

(load: 50pF // 2k to GND)

-

40 - µs

One LSB settling time

(load: 50pF // 2k to GND )

- 8 -

µs

Two different microphone inputs and two different speaker outputs are supported. The Q26 Extreme

Wireless CPU® also includes an echo cancellation feature and noise reduction, which allows handsfree function.

In some cases, ESD protection must be added on the audio interface lines.

The connection can be either differential or single-ended but using a differential connection in order

to reject common mode noise and TDMA noise is strongly recommended. When using a single-ended

connection, be sure to have a very good ground plane, a very good filtering as well as shielding in

order to avoid any disturbance on the audio path.

The gain of MIC inputs is internally adjusted and can be tuned using an AT command.

Both can be configured in differential or single ended.

The MIC2 inputs already include the biasing for an electret microphone allowing an easy connection.

By default, the MIC1 inputs are single-ended but it can be configured in differential.

The MIC1 inputs do not include an internal bias. The MIC1 input needs to have an external biasing if

an electret microphone is used.

AC coupling is already embedded in the Q26 Extreme Wireless CPU

®.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 56 of 112

Page 57

Product Technical Specification and

Customer Design Guidelines

DC equivalent circuit

AC equivalent circuit

Parameters

Min

Typ

Max

Unit

DC Characteristics

N/A V

AC Characteristics

200 Hz < F < 4 kHz

Z1

70

120

160

k

Working voltage

(MIC1P-MIC1N)

AT+VGT*=3500(4)

13.8

18.6***

mVrms

AT+VGT*=2000(4)

77.5

104***

AT+VGT*=700(4)

346

465***

Maximum rating voltage

(MIC1P or MIC1N)

Positive

+7.35

V

Negative

-0.9

MIC1P

MIC1N

Z1

Z1

GND

MIC1P

MIC1N

DC

Blocked

Table 34. Equivalent circuits of MIC1

Table 35. Electrical Characteristics of MIC1

*The input voltage depends of the input micro gain set by AT command. Please refer to the document :AT command User

Guide [7]

**Because MIC2P is internally biased, it is necessary to use a coupling capacitor to connect an audio signal provided by

an active generator. Only a passive microphone can be directly connected to the MIC2P and MIC2N inputs.

*** This value is obtained with digital gain = 0 and for frequency = 1kHz :

(4)

This value is given in dB, but it’s possible to toggle to index value. Please refer to the document :AT command User

Guide [7]

Warning: The voltage input value for MIC1 can’t exceed the maximum working

voltage, otherwise clipping will appear.

WM_DEV_Q26EX_PTS_002 Rev 006 Page 57 of 112

Page 58

Product Technical Specification and

Customer Design Guidelines

C5

40

38

Audio

ADC

100k Ohm

typ

100k Ohm

typ

100nF

100nF

MIC1P

MIC1N

VCC_2V8

(pin10)

R3

R2

R1

R4

C2

C3C1

L1

L2

C4