Siemens BUZ110S Datasheet

SIPMOS ® Power Transistor

• N channel

• Enhancement mode

• Avalanche-rated

• dv/dt rated

• 175°C operating temperature

• also in SMD available

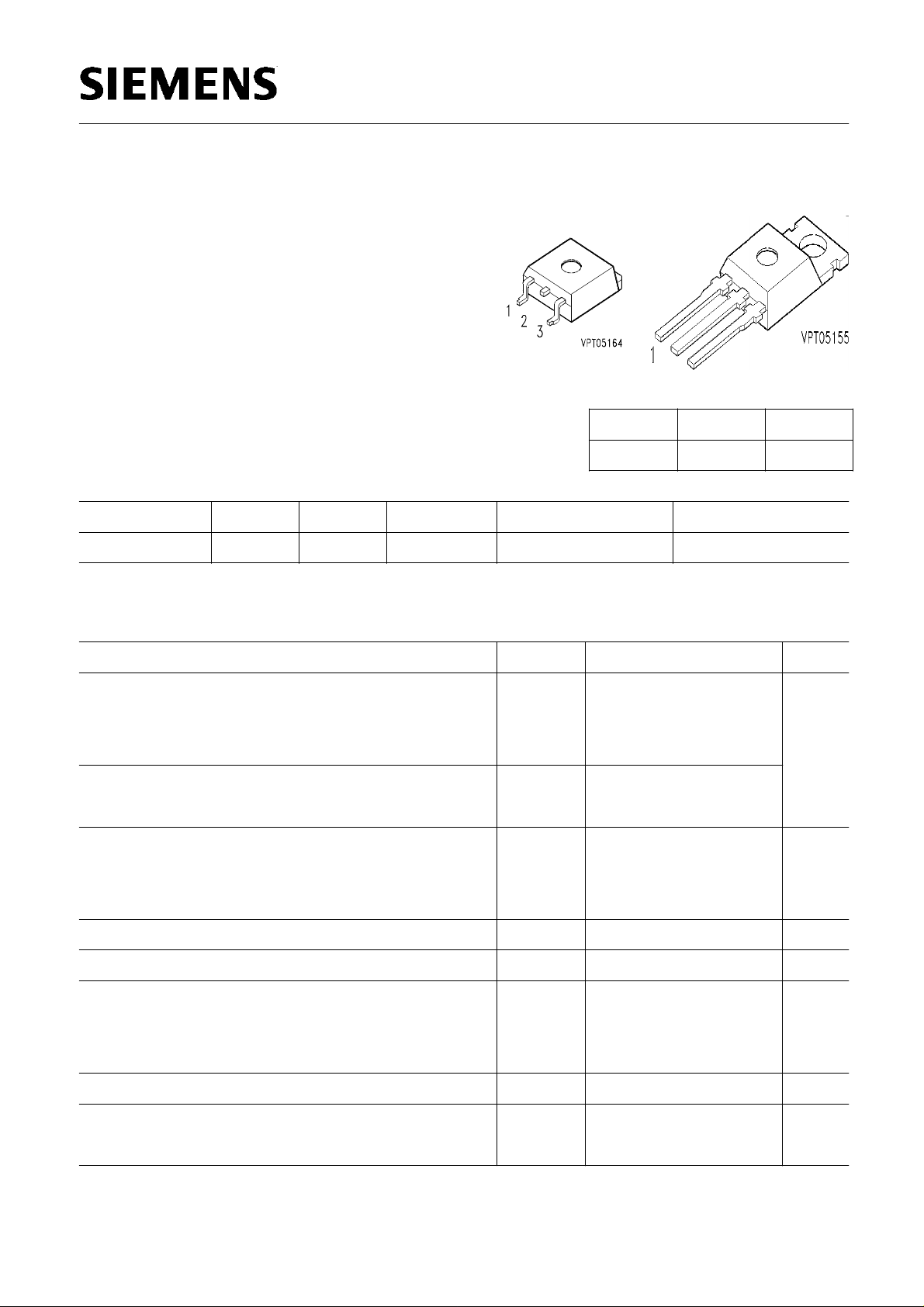

BUZ 110 S

SPP80N05

Pin 1 Pin 2 Pin 3

G D S

Type

V

DS

I

D

R

DS(on

BUZ 110 S 55 V 80 A 0.012

)

Ω

Package Ordering Code

TO-220 AB Q67040-S4005-A2

Maximum Ratings

Parameter Symbol Values Unit

Continuous drain current

T

= 25 °C

C

T

= 100 °C

C

Pulsed drain current

T

= 25 °C

C

Avalanche energy, single pulse

I

= 80 A, VDD = 25 V, RGS = 25

D

L = 144 µH, T

= 25 °C

j

Avalanche current,limited by T

Ω

jmax

Avalanche energy,periodic limited by T

Reverse diode dv/dt

jmax

I

D

I

Dpuls

E

AS

I

AR

E

AR

dv/dt

A

80

66

320

mJ

460

80 A

20 mJ

kV/µs

I

= 80 A, VDS = 40 V, diF/dt = 200 A/µs

S

T

= 175 °C

jmax

Gate source voltage V

Power dissipation

T

= 25 °C

C

Semiconductor Group 1 28/Jan/1998

GS

P

tot

6

±

20 V

200

W

BUZ 110 S

SPP80N05

Maximum Ratings

Parameter Symbol Values Unit

Operating temperature T

Storage temperature T

Thermal resistance, junction - case R

Thermal resistance, junction - ambient R

j

stg

thJC

thJA

-55 ... + 175 °C

-55 ... + 175

≤

0.75 K/W

≤

62

IEC climatic category, DIN IEC 68-1 55 / 175 / 56

Electrical Characteristics,

Parameter Symbol Values Unit

Static Characteristics

Drain- source breakdown voltage

V

= 0 V, ID = 0.25 mA, Tj = 25 °C

GS

Gate threshold voltage

V

GS=VDS, ID

= 200 µA

Zero gate voltage drain current

V

= 50 V, VGS = 0 V, Tj = -40 °C

DS

V

= 50 V, VGS = 0 V, Tj = 25 °C

DS

V

= 50 V, VGS = 0 V, Tj = 150 °C

DS

Gate-source leakage current

V

= 20 V, VDS = 0 V

GS

Drain-Source on-resistance

V

= 10 V, ID = 66 A

GS

at Tj = 25°C, unless otherwise specified

min. typ. max.

V

(BR)DSS

55 - -

V

GS(th)

2.1 3 4

I

DSS

-

-

-

I

GSS

- 10 100

R

DS(on)

- 0.009 0.012

-

0.1

-

V

µA

0.1

1

100

nA

Ω

Semiconductor Group 2 28/Jan/1998

BUZ 110 S

SPP80N05

Electrical Characteristics,

at Tj = 25°C, unless otherwise specified

Parameter Symbol Values Unit

min. typ. max.

Dynamic Characteristics

Transconductance

≥

V

2

DS

* ID * RDS(on)max, ID

= 66 A

Input capacitance

V

= 0 V, VDS = 25 V, f = 1 MHz

GS

Output capacitance

V

= 0 V, VDS = 25 V, f = 1 MHz

GS

Reverse transfer capacitance

V

= 0 V, VDS = 25 V, f = 1 MHz

GS

Turn-on delay time

V

= 30 V, VGS = 10 V, ID = 80 A

DD

= 3.9

Ω

R

G

Rise time

V

= 30 V, VGS = 10 V, ID = 80 A

DD

= 3.9

Ω

R

G

Turn-off delay time

V

= 30 V, VGS = 10 V, ID = 80 A

DD

= 3.9

Ω

R

G

Fall time

V

= 30 V, VGS = 10 V, ID = 80 A

DD

= 3.9

Ω

R

G

Gate charge at threshold

V

= 40 V, ID ≥ 0.1 A, VGS =0 to 1 V

DD

Gate charge at 7.0 V

V

= 40 V, ID = 80 A, VGS =0 to 7 V

DD

Gate charge total

V

= 40 V, ID = 80 A, VGS =0 to 10 V

DD

Gate plateau voltage

V

= 40 V, ID = 80 A

DD

g

fs

C

iss

C

oss

C

rss

t

d(on)

t

r

t

d(off)

t

f

Q

g(th)

Q

g(7)

Q

g(total)

V

(plateau)

S

30 - -

pF

- 2420 3025

- 745 930

- 380 475

ns

- 20 30

- 35 55

- 45 70

- 30 45

nC

- 3 4.5

- 65 100

- 85 130

V

- 5.8 -

Semiconductor Group 3 28/Jan/1998

Loading...

Loading...