Page 1

T E C H N I C A L I N F O R M A T I O N

HIPERFACE DSL

Implementation

®

Page 2

© SICK STEGMANN GmbH

All rights reserved. No component of the description may by copied or processed in any

other way without the written consent of the company.

This documentation applies to the HIPERFACE DSL® release version 1.07, release date

July 29, 2016. Subject to modification without notice.

SICK STEGMANN GmbH accepts no responsibility for the non-infringement of patent

rights, e.g. in the case of recommendations for circuit designs or processes.

The trade names listed are the property of the relevant companies.

HIPERFACE® and HIPERFACE DSL® are registered trademarks of SICK STEGMANN

GmbH.

SICK STEGMANN GmbH

Dürrheimer Strasse 36

78166 Donaueschingen, Germany

Tel.: +(49) 771 / 807 – 0

Fax: +(49) 771 / 807 – 100

Internet: http://www.sick.com

E-mail: info@sick.com

Made in Germany, 2016.

2

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 3

Contents

CONTENTS

1 List of figures..................................................................................... 5

2 Scope of application of the document........................................... 6

2.1 Symbols used............................................................................................ 6

2.2 Associated documents............................................................................. 6

2.3 HIPERFACE DSL® for Motor Feedback Systems...................................... 6

2.4 Features of HIPERFACE DSL®.................................................................. 7

3 Protocol overview.............................................................................. 9

3.1 Process data channel............................................................................... 11

3.2 Safe Channel 1......................................................................................... 12

3.3 Safe Channel 2......................................................................................... 13

3.4 Parameters Channel................................................................................. 13

3.5 SensorHub Channel.................................................................................. 13

4 Hardware installation....................................................................... 15

4.1 Interface circuit......................................................................................... 15

4.2 FPGA IP Core............................................................................................. 18

4.3 Cable specification................................................................................... 21

5 Interfaces............................................................................................ 22

5.1 Drive interface........................................................................................... 22

5.2 SPI PIPE Interface..................................................................................... 23

5.3 Control signals.......................................................................................... 24

5.4 Test signals............................................................................................... 26

6 Register map...................................................................................... 29

6.1 Explanation of the registers..................................................................... 29

6.2 Online Status D......................................................................................... 30

6.3 DSL Master function register................................................................... 32

6.4 Function register for the DSL Slave......................................................... 55

7 Central functions............................................................................... 59

7.1 System start.............................................................................................. 59

7.2 System diagnostics................................................................................... 60

7.3 Fast position.............................................................................................. 61

7.4 Safe position, Channel 1.......................................................................... 66

7.5 Parameters Channel................................................................................. 67

7.6 Status and error messages...................................................................... 74

8 Motor feedback system resources.................................................. 86

8.1 Access to resources.................................................................................. 86

8.2 Resources list............................................................................................ 89

8.3 Node.......................................................................................................... 90

8.4 Identification resources............................................................................ 93

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

3

Page 4

CONTENTS

8.5 Monitoring resources................................................................................ 99

8.6 Code disk position range.......................................................................... 113

8.7 Code disk position.................................................................................... 113

8.8 Administration resources......................................................................... 114

8.9 Counter resources.................................................................................... 124

8.10 Data storage resources............................................................................ 126

8.11 SensorHub resources............................................................................... 133

9 FPGA IP-Core...................................................................................... 136

9.1 Interface blocks........................................................................................ 139

9.2 Serial interface block................................................................................ 140

9.3 Parallel interface block............................................................................. 145

9.4 Basic interface specification.................................................................... 148

9.5 Register assignment................................................................................. 150

9.6 Implementation of the IP Core for Xilinx Spartan-3E/6......................... 151

9.7 Installation of the IP Core for Altera FPGAs............................................ 156

10 DSL component interoperability..................................................... 161

10.1 Servo controller recommendations......................................................... 161

10.2 Motor recommendations.......................................................................... 164

10.3 Recommendations for connection line................................................... 166

10.4 Recommendations on installation site.................................................... 168

11 Index.................................................................................................... 169

12 Glossary.............................................................................................. 170

13 Versions.............................................................................................. 171

4

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 5

1 List of figures

1. Drive system with HIPERFACE DSL®............................................................................ 7

2. Length of protocol packages......................................................................................10

3. Data channels in HIPERFACE DSL®........................................................................... 11

4. HIPERFACE DSL® SensorHub interface.....................................................................14

5. Interface circuit with separate encoder cable.......................................................... 16

6. Interface circuit with two core cable (integrated in cable).......................................16

7. Block diagrams of the "standard" DSL Master IP Core with interfaces.................. 19

8. Reset procedure......................................................................................................... 20

9. DSL system interfaces................................................................................................22

10. SPI-PIPE interface time control..................................................................................24

11. "Read Pipeline" transaction....................................................................................... 24

12. Sample signal............................................................................................................. 26

13. Register block overview..............................................................................................29

14. Interrupt masking....................................................................................................... 39

15. DSL Slave status and summary.................................................................................46

16. Sequence of the bytes to calculate the CRC.............................................................48

17. Status table for DSL system start..............................................................................59

18. Position value format..................................................................................................62

19. Polling of position registers in free running mode....................................................64

20. Polling of rotation speed registers in free running mode.........................................64

21. SYNC mode signals.....................................................................................................66

22. Polling registers for the fast position in SYNC mode................................................66

23. Polling of rotation speed registers in SYNC mode....................................................66

24. Polling the safe position.............................................................................................67

25. Reading from remote register....................................................................................68

26. "Long message" characteristics.................................................................................69

27. Example of a "long message" read command..........................................................72

28. Reset of the Parameters Channel............................................................................. 73

29. Acknowledgment of event bits...................................................................................74

30. Tree structure of the resources database.................................................................87

31. Code disc position....................................................................................................114

32. Workflows for data storage......................................................................................126

33. sHub® categories......................................................................................................133

34. Block circuit diagram of the DSL Master IP Core................................................... 136

35. Combination examples of interface blocks ........................................................... 140

36. Serial interface block signals ................................................................................. 140

37. Time control of the SPI.............................................................................................142

38. Parallel interface block signals............................................................................... 145

39. Allocation of parallel interface block to host..........................................................147

40. Read access basic interface................................................................................... 149

41. Write access basic interface....................................................................................149

42. Connection of the hybrid motor cable to the servo controller ..............................163

43. Pin layout M23..........................................................................................................167

LIST OF FIGURES 1

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

5

Page 6

2 SCOPE OF APPLICATION OF THE DOCUMENT

2 Scope of application of the document

This document is for a standard HIPERFACE DSL® application. For safety applications,

please only refer to the document “HIPERFACE DSL® safety manual (8017596)".

2.1 Symbols used

NOTE

Notes refer to special features of the device. Please pay attention to these notes. They

often contain important information.

Tips provide additional information that facilitates using the documentation.

CAUTION

Safety notes contain information about specific or potential dangers, and misuse of the

application. This information is to prevent injury.

Read and follow the safety notes carefully.

2.2 Associated documents

Along with this manual, the following documents are relevant for the use of the HIPER‐

FACE DSL® interface:

Document number Title Status

8017596 HIPERFACE DSL® safety manual 2018-01-15

Table 1: Associated documents

Individual encoder types with the HIPERFACE DSL® interface are described with the fol‐

lowing documents:

Data sheet

•

Operating instructions

•

Errata document

•

2.3 HIPERFACE DSL® for Motor Feedback Systems

This document describes the use and implementation of the HIPERFACE DSL® data pro‐

tocol installed in motor feedback systems of servo drives.

HIPERFACE DSL® is a purely digital protocol that requires a minimum of connection

cables between frequency inverter and motor feedback system. The robustness of the

protocol enables the connection to the motor feedback system via the motor connec‐

tion cable.

Motor feedback systems with the HIPERFACE DSL® interface can be used across all per‐

formance ranges and substantially simplify the installation of an encoder system in the

drive:

Standardized digital interface (RS485)

•

Analog components for the encoder interface are not required

•

Standardized interface between the frequency inverter application and the proto‐

•

col logic

6

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 7

Drive

OK …

DSL connection

MFB

system

Motor

SCOPE OF APPLICATION OF THE DOCUMENT

2

Figure 1: Drive system with HIPERFACE DSL

Based on the name for the predecessor protocol, the SICK HIPERFACE®, the name

HIPERFACE DSL® stands for HIgh PERformance InterFACE Digital Servo Link.

This interface takes into account all the current requirements of digital motor feedback

systems and also contains future enhancements for the manufacturers of frequency

inverters.

2.4 Features of HIPERFACE DSL

Some of the main advantages of HIPERFACE DSL® are based on the opportunity for

connection of the encoder:

A digital interface on the frequency inverter for all communication with the motor

•

feedback system. The interface complies with the RS485 standard with a transfer

rate of 9.375 MBaud.

Communication with the encoder via a twisted pair

•

Power supply and communication with the encoder can be carried out using the

•

same dual cable. This is possible by the enhancement of the frequency - inverter

with a transformer.

The connection cables to the encoder can be routed as a shielded, twisted- pair

•

cable in the power supply cable to the motor. This means that no encoder plug

connector to the motor and to the frequency inverter is necessary.

The cable length between the frequency inverter and the motor feedback system

•

can be up to 100 m, without degradation of the operating performance.

®

®

The digital HIPERFACE DSL® protocol can be used for a variety of frequency inverter

applications:

For the feedback cycle of the frequency inverter's synchronous cyclic data that

•

enables synchronous processing of position and rotation speed of the encoder.

Shortest possible cycle time: 12.2 µs.

•

Transmission of the safe position of the motor feedback system with a maximum

•

cycle time of 216 µs.

Redundant transmission of the safe position of the motor feedback system with a

•

maximum cycle time of 216 µs, so that suitable motor feedback systems can be

used in SIL2 applications (in accordance with IEC 61508).

Transmission of the safe position of the motor feedback system on a second chan‐

•

nel with a maximum cycle time of 216 µs, so that suitable motor feedback sys‐

tems can be used in SIL3 applications (in accordance with IEC 61508).

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

7

Page 8

2 SCOPE OF APPLICATION OF THE DOCUMENT

Parameter data channel for bi-directional general data transfer with a band width

•

of up to 340 kBaud. This data includes an electronic type label for designation of

the motor feedback system and for storage of frequency inverter data in the motor

feedback system.

SensorHub channel via which motor data from external sensors is transmitted,

•

that are connected by the HIPERFACE DSL® SensorHub protocol to the motor feed‐

back system.

The protocol is integrated into the frequency inverter in the form of hardware logic. This

logic circuit is supplied by several manufacturers as an IP Core for FPGA components

(FPGA = Field Programmable Gate Array).

The available protocol logic enables free routing when installing the HIPERFACE

•

DSL® IP Core. The protocol circuit can be installed along with the frequency

inverter application on the same FPGA.

Choice between full-duplex SPI (SPI = serial peripheral interface) or parallel inter‐

•

face between protocol logic and frequency inverter applications for standardized

access to process data (position, rotation speed) and parameters.

Fast additional full-duplex SPI between protocol logic and frequency inverter appli‐

•

cations for standardized access to secondary position data

Additional configurable SPI for output of the data from external sensors.

•

Configurable interrupt output

•

8

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 9

3 Protocol overview

HIPERFACE DSL® is a fast digital protocol for motor feedback systems for the connec‐

tion between servo drive and motor feedback system. The protocol is installed in the

transport layer in the frequency inverter using a digital logic circuit (DSL Master IP

Core).

The position data are generated in two different ways in HIPERFACE DSL®, either in

free running mode, in which the position values are sampled and transmitted as quickly

as possible, or in SYNC mode, in which the position data are sampled and transmitted

synchronously with a defined clock signal. With a frequency inverter application, this

clock signal is normally the clock feedback of the frequency inverter.

In SYNC mode the protocol matches the time points for the sampling of the data with‐

out time fluctuations with the clock coming from the frequency inverter.

For each frequency inverter cycle at least one position value is sampled and transmit‐

ted with constant latency to the DSL Master. As the protocol matches the internal data

transfer speed to the frequency inverter cycle, the overall transfer rate of the

HIPERFACE DSL® depends on the frequency inverter clock.

The protocol package is matched to the various lengths, see figure 2. Provided the fre‐

quency inverter cycle is long enough, additional sampling points can be positioned in

the frequency inverter cycle, known as "Extra" packages. The number of additional

packages is programmed by the user with a divider value.

PROTOCOL OVERVIEW

3

The number of packages transmitted per frequency inverter cycle cannot be selected at

random, as the lower and upper range length of a protocol package must be adhered

to. This must be taken into account when setting the divider value.

In free running mode, the frequency inverter cycle is not taken into account for sam‐

pling and transmission and the protocol uses the minimum package length.

It must be noted that the minimum package length in free running mode is shorter than

the minimum package length in SYNC mode.

table 1 shows the dependency of the lengths of the protocol packages using examples

for the length of the frequency inverter cycle.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

9

Page 10

PROTOCOL OVERVIEW

3

Figure 2: Length of protocol packages

Table 1: Frequency inverter cycle and length of protocol packages

Inverter cycle frequency

(kHz)

Length of the fre‐

quency inverter cycle

(µs)

Length of the protocol

package

(µs)

Protocol packages

per frequency

inverter cycle

2 500 12.50 40

4 250 12.50 20

6.25 160 13.33 12

8 125 12.50 10

16 62.5 12.50 5

40 25 12.50 2

37 to 84 27 to 12.2 27 to 12.2 1

Free running -- 11.52 --

In HIPERFACE DSL®, the data are transmitted over several channels. Each individual

channel is adapted to different requirements according to its content. The cycle time of

each individual channel varies with the length of the basic protocol package.

10

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 11

Inverter

OK …

MFB

system

DDPos

DDPos DDPos DDPos DDPos DDPos DDPos DDPos

Process data channel

Safe channel 1

Safe position 1

Status CRC

Position request

Parameter answer

SensorHub channel

SensorHub data

SensorHub data

Parameter channel Slave-Master

Parameter channel Master-Slave

Parameter request

Safe channel 2

Safe position 2

Status 2 CRC

PROTOCOL OVERVIEW 3

Figure 3: Data channels in HIPERFACE DSL

table 2 gives an overview of the characteristics of the various channels.

NOTE

It should be noted that the minimum cycle time and the maximum band width only

apply if the maximum number of sample points per frequency inverter cycle was pro‐

grammed (refer to "Register synchronization control", chapter 6.3.2).

Table 2: Channels for protocol data

Channel in

HIPERFACE DSL

Process data chan‐

nel

Safe Channel 1 Absolute / safe position, status of

Safe Channel 2 Absolute / safe position, status of

Parameter channel General data, parameters Variable 330 to 167

SensorHub channel External data 12.2 to 27.0 660 to 334

3.1 Process data channel

®

Function Cycle time (µs) Band width

®

Fast position, rotation speed 12.2 to 27.0 1321 to 669

96.8 to 216.0 660 to 334

Channel 1

96.8 to 216.0 660 to 334

Channel 2

(kBaud)

The fast position value of the motor feedback system is transferred on the process data

channel synchronously with the position requests that are controlled by the signal at

the SYNC input of the frequency inverter cycle.

The process data channel is the fastest channel of the HIPERFACE DSL® protocol. Every

protocol package transferred contains a complete update of the content of this chan‐

nel.

This content consists of increments to rotation speed that is used as feedback parame‐

ters for the control loop of the motor drive (see chapter 6.3.12 and chapter 6.3.13).

If the fast position from the process data channel cannot be calculated (either due to

transmission or due to sensor errors), estimation is made by the DSL Master based on

the last two available position values of Safe Channel 1. The worst case deviation from

the actual mechanical position is also provided.

NOTE

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

For reliable position estimation, the user needs to provide application specific informa‐

tion about maximum speed and maximum acceleration. Please see chapter 7.3.1 for

details.

®

11

Page 12

3 PROTOCOL OVERVIEW

3.1.1 Sampling Time

The fast position value sampling time is based on the transmission of a SYNC edge in a

protocol package (where the SYNC edge can be user-commanded or belong to an

EXTRA package, see above).

The duration from SYNC edge to sampling time point is based on the following formula:

t

sample

where

t

latency

t

delay

t

jitter

EDGES refers to the number of set bits in the EDGES register, see chapter 6.3.7. Sam‐

pling latency will always be less than 1 μs. Note that position values will only be avail‐

able after a longer duration (around 10 μs after SYNC edge) due to data serialization

and transmission to the drive controller.

3.2 Safe Channel 1

= t

latency

+ t

delay

± t

jitter

< 100 ns

= 5 ns/m * l_cable [m]

= 6.5 ns + 13.33 ns * EDGES

3.2.1 Sampling Time

The safe position value of the motor feedback system is transferred on the Safe Chan‐

nel as an absolute value. In addition, the status of the encoder is reported on this chan‐

nel in the form of errors and warnings.

NOTE

The safe position value transferred on the Safe Channel is not synchronous with the fre‐

quency inverter cycle signal at the SYNC input.

The safe position is used by the DSL Master IP Core to check the fast position value of

the process data channel and can be used by the frequency inverter application for the

same purpose.

Where there are deviations between the safe and the fast position values, an error

message is generated (see chapter 5.4.2). In this case, the protocol replaces the fast

position with the estimated position. Please see chapter 7.3.1 for details.

In each package of the safe channel, a collection of status bits is transferred that

reflects the error and warning condition of the motor feedback system.

NOTE

It should be noted that each bit of the summary byte of the Safe Channel refers to one

status byte the motor feedback system. Each status byte of the encoder can be read

with a "short message" (see chapter 7.5.1).

12

The safe position value (both channel 1 and 2) is not synchronous to the drive con‐

troller cycle signal at the SYNC input. The safe position value is transmitted in eight

protocol packages. The sampling point of the safe position is based upon the SYNC

edge of the first of these eight protocol packages (keeping in mind that the SYNC edge

might be user-commanded or belong to a DSL Master-generated EXTRA package, see

above). Depending on the actual position of the last user-generated SYNC edge the safe

position value will be 1 to 9 protocol packages old. Depending on the timer settings for

SYNC to EXTRA packages the sampling time of the safe position value will change

between measurements.

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 13

3.3 Safe Channel 2

In Safe Channel 2, copies of the absolute position value and the status of the motor

feedback system are transferred. This information can be discarded in non-safe appli‐

cations.

NOTE

The Safe Channel 2 is only accessible in the safety variants of the DSL Master IP Core.

For sampling time of safe channel 2 see chapter 3.2.1.

PROTOCOL OVERVIEW 3

3.4

Parameters Channel

The Parameters Channel is the interface, over which the frequency inverter application

reads and writes parameters of the motor feedback system.

In addition to the main task of position measurement, motor feedback systems with the

HIPERFACE DSL® interface also have various internal resources installed. These

resources are accessible via the Parameters Channel.

Examples of these resources are temperature measurements, monitoring - mecha‐

nisms for correct functioning, product data (the "electronic type label") or freely pro‐

grammable data fields.

NOTE

It should be noted that the resources actually installed for DSL products differ and are

listed in the relevant product data sheet.

There are two types of communication on the Parameters Channel:

"Short message" transaction

•

"Long message" transaction

•

A "short message” transaction allows access to resources that have an influence on

the HIPERFACE DSL® protocol interface and are used for monitoring them. This includes

detailed status and error messages for the motor feedback system and indications of

the signal strength on the DSL connection. As a "short message" transaction is

processed directly by the interface logic of the motor feedback system, this transaction

is completed in a comparatively short time.

A "long message" transaction allows access to all the other resources of the motor

feedback system. Unlike a "short message" transaction, a "long message" normally

requires processing by the motor feedback system processor and therefore has does

not have a response time that can be defined in advance.

NOTE

It should be noted that in HIPERFACE DSL®, a maximum of one "short message" and

one "long message" are processed at any time.

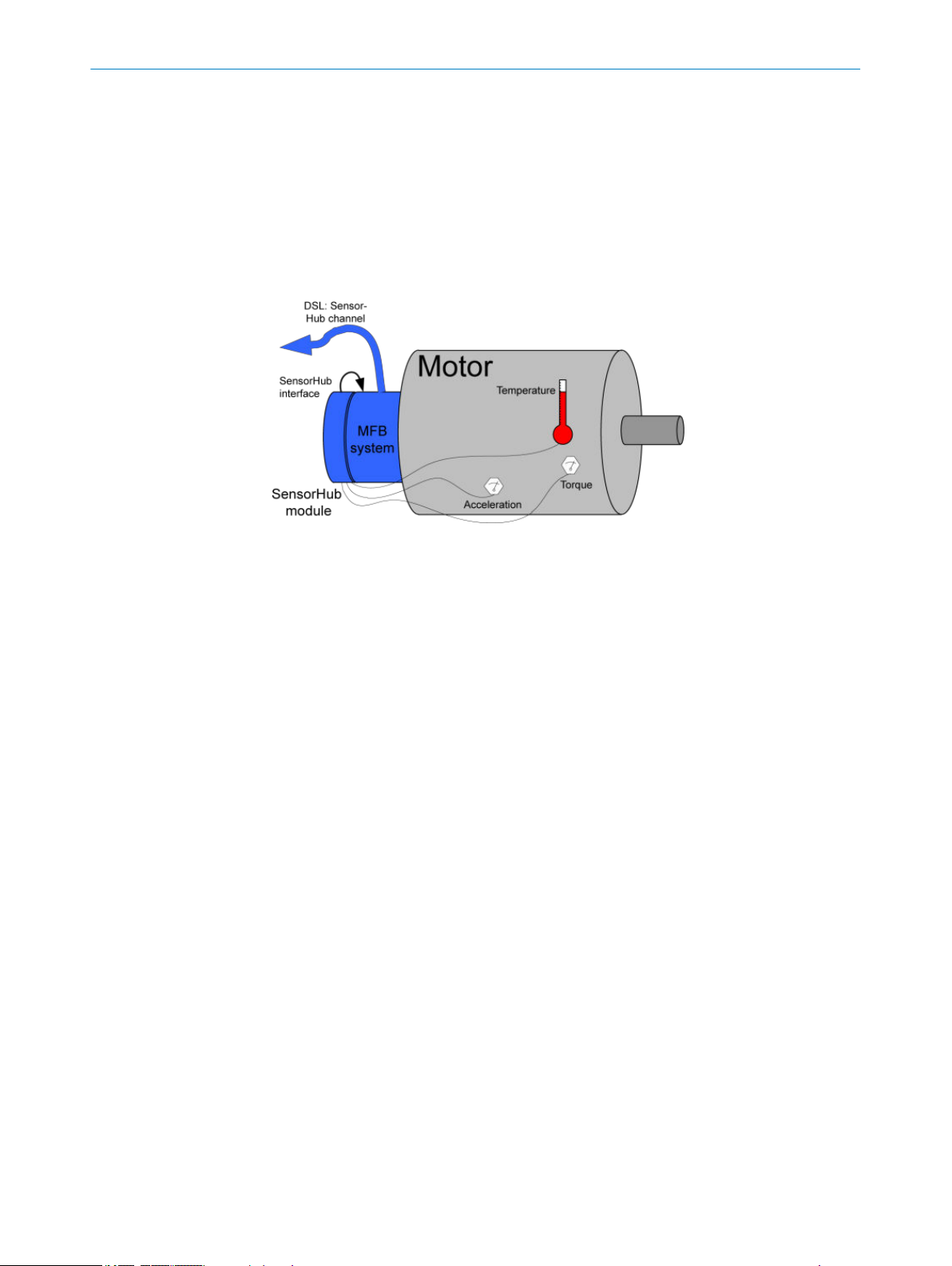

3.5 SensorHub Channel

Data from additional external sensors can be transferred on the SensorHub Channel

that can be used in the frequency inverter system. External sensors must be connected

to the motor feedback system via the HIPERFACE DSL® SensorHub interface. Various

sensors or sensor networks are accessible via this interface and can be selected using

HIPERFACE DSL®.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

13

Page 14

3 PROTOCOL OVERVIEW

The configuration of external sensors is carried out via the Parameters Channel, whilst

the data are transferred via the SensorHub Channel. The transfer of protocol packages

in the SensorHub Channel takes place synchronously with the DSL transfer and as an

extension of the frequency inverter cycle signal that is present at the DSL Master SYNC

input. Depending on the use of the SensorHub interface, external data can therefore be

sampled and transferred synchronously.

The protocol in the SensorHub Channel is not monitored by HIPERFACE DSL®. Apart

from the monitoring of the data transfer quality, there are no protocol mechanisms on

this channel.

Figure 4: HIPERFACE DSL® SensorHub interface

14

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 15

4 Hardware installation

The installation of HIPERFACE DSL® in a drive system requires an interface circuit with

specific components as well as the installation of a digital logic core for an FPGA com‐

ponent.

The interface circuit is described thoroughly in this chapter. The chapter also contains

recommendations for the selection of components.

The digital logic core (IP Core) is supplied by SICK for prescribed FPGA types.

In addition, the type of cable recommended for the connection between the frequency

inverter and the motor feedback system is described thoroughly in this chapter.

NOTE

It may also be possible to use other sorts of cable. These must be tested before use,

however.

As a physical layer, HIPERFACE DSL® uses a transfer in accordance with EIA-485

(RS-485).

4.1 Interface circuit

HARDWARE INSTALLATION 4

In most cases a transceiver for more than 20 MBaud is suitable. Nevertheless the tim‐

ing parameters of the transceiver have to fulfill the requirements of the following

table 3 under worst case conditions of the application.

Table 3: Interface circuit

Characteristic Value Units

Transfer rate >20 MBaud

Permitted common mode voltage -7 to +12 V

Receiver: Differential threshold voltage < 200 mV

Load resistance < 55 Ohm

Receiver running time delay < 60 ns

Sender running time delay < 60 ns

Sender power-up delay < 80 ns

Sender power-down delay < 80 ns

Sender rise time < 10 ns

Sender dropout time < 10 ns

Switch over time of 1 bit < 106.7 ns

Protection against short-circuit

Protection against bus conflict

HIPERFACE DSL® can be used in connection with two different interface circuit configu‐

rations. Each configuration requires a different sort of connection cable (see

chapter 4.3).

4.1.1 Separate encoder cable - four core cable

When using a separate encoder cable, the smallest interface circuit can be used. The

separate encoder cable allows a four core connection.

In connection with the associated table, figure 5 below gives the specification of the

interface circuit.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

15

Page 16

DE

RE\

VCC

R

D

A

B

VSS

C1

C2

R1

R2

7..12 VDC

DATA+

DATA-

PWR+

PWR-

DSL

EN

DSL

IN

DSL

OUT

U2

DE

RE\

VCC

R

D

A

B

VSS

U2

C1

C2

R1

R2

TR1

C3

C4

7..12 VDC

L1

L2

DSL+

DSL-

DSL

EN

DSL

IN

DSL

OUT

4 HARDWARE INSTALLATION

Figure 5: Interface circuit with separate encoder cable

Recommended components for the interface circuit are set out in table 4.

Table 4: Components for the interface circuit with separate encoder cable

Component Part Manufacturer

C1 Ceramic capacitor 100 nF

C2 Ceramic capacitor 2.2 µF, 16 V

R1, R2 Resistors 56R

U2 RS485 transceiver SN65LBC176A

SN75LBC176A

Texas Instruments

Texas Instruments

NOTE

The use of four core cable is no longer recommended for the motor cable.

4.1.2 Integrated cable - two core cable

For a connection via a two core cable integrated in the motor cable, (see chapter 4.3),

the data cables must be provided with a transformer to raise the common mode rejec‐

tion ratio. To feed the supply voltage into the data cables choke coils are also required.

In connection with the associated table, figure 6 below gives the specification of the

interface circuit.

Figure 6: Interface circuit with two core cable (integrated in cable)

16

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 17

Recommended components for the interface circuit are set out in table 5.

Table 5: Components of the interface circuit with two core cable (integrated in cable)

Component Part Manufacturer

C1 Ceramic capacitor 100 nF

C2 Ceramic capacitor 2.2 µF, 16 V

C3, C4 Ceramic capacitor 470 nF, 50 V

L1, L2 Choke coils 744043101, 100 µH

R1, R2 Resistors 56R

U2 RS485 transceiver SN65LBC176A

TR1 Transformer PE-68386NL

4.1.3 Motor feedback voltage supply

Motor feedback systems with HIPERFACE DSL® have been developed for operation with

a supply voltage of 7 to 12 V. The voltage supply is measured at the encoder plug con‐

nector.

HARDWARE INSTALLATION 4

ELL6SH101M, 100 µH

SN75LBC176A

78602/1C

B78304B1030A003

78602/1C

Würth Elektronik

Panasonic

Texas Instruments

Texas Instruments

Pulse Engineering

Murata

Epcos

Epcos

table 6 below describes the specification for the power supply.

Table 6: Voltage supply

Parameter Value

Switch-on voltage ramp Max. 180 ms from 0 to 7 V

Inrush current Max. 3.5 A (0 to100 µs)

Operating current Max. 250 mA at 7 V

4.1.4 Interface circuit design recommendations

figure 5 and figure 6 show the two different interface circuits depending on the chosen

system configuration. The following recommendations help in attaining a system design

optimized for transmission robustness.

During PCB design a good RF isolation for the interface circuit shall be achieved

•

against the motor power circuit.

The two sides of the transformer TR1 have to be well separated from each other to

•

avoid crosstalk.

Inside the servo controller the DSL-signal lines shall be routed as short as possible

•

and with good symmetry in the differential part. To avoid or reduce signal distur‐

bances by EMC-noise it is recommended to place this circuit as close as possible

to the connection point of the DSL-lines.

During PCB layout design also assess and avoid potential EMC-noise coupling

•

from brake lines as well as the brake power supply circuit.

For the encoder power supply via L1/L2 a star connection to a very low impedance

•

point is important. Both inductances shall be well matched to each other to avoid

differential mode noise. Self-resonance frequency should be of at least 10 MHz. A

common mode filter between L1/L2 and the supply voltage can improve robust‐

ness.

The DSL-line impedance is matched balanced by 2 x 56 Ohm. C2 grounds remain‐

•

ing common mode noise after the transformer; RF parts shall be used or different

types paralleled to get low impedance on a broader frequency range. PCB design

Max. 1 A (100 µs to 400 µs)

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

17

Page 18

4 HARDWARE INSTALLATION

at this area needs to consider RF requirements for the actual components selec‐

tion and PCB layout.

DSL signal transmission is done with about 10 MHz frequency but square signal

•

harmonics can reach frequencies beyond (to 60 MHz) which should be considered

for layout design.

The used motor cable shall meet the impedance requirements of (110 +/-10)

•

Ohm to avoid signal reflections.

DSL line connection to the servo controller shall be separated from the motor

•

power connection point.

A good main shielding connection to a low inductance path shall allow draining

•

motor power residual current. For the DSL-line shielding a separate connection

point is recommended. For the connection unshielded DSL lines shall be avoided

or kept as short as possible (<20 mm).

4.2 FPGA IP Core

The frequency inverter system communicates with the DSL motor feedback system via

a special protocol logic circuit that is designated as the DSL Master. The circuit is sup‐

plied by SICK and must be installed in an FPGA component. It is supplied as an Intellec‐

tual Property Core (IP Core). The DSL Master IP Core is supplied in different forms,

depending on the FPGA vendor preferred by the user (compiled netlist or encrypted

VHDL). If there is sufficient space in the FPGA being used, the DSL Master can be

installed in the same component as the frequency inverter application.

CAUTION

There are two different IP Cores available, one for standard and one for safety applica‐

tions. This manual only describes the standard variant. Please choose according to the

desired system.

For interfacing the IP Core, several options are available. For details of those interface

blocks see chapter 9.1.

The following figure show the possible combinations of IP Core and interface block vari‐

ants.

18

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 19

Standard DSL Master

(dslm_n)

Parallel

interface

Parallel Bus Drive interface

SPI Pipeline

Test signals

Control signals

DSL

Standard DSL Master

(dslm_n)

Serial

interface

SPI Drive interface

SPI Pipeline

Test signals

Control signals

DSL

Standard DSL Master

(dslm_n)

User

interface

Miscellaneous Drive interface

SPI Pipeline

Test signals

Control signals

DSL

Serial

interface

SPI

A)

B)

C)

HARDWARE INSTALLATION 4

4.2.1 DSL Master inputs / outputs

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

Figure 7: Block diagrams of the "standard" DSL Master IP Core with interfaces

Table 7: Pin functions of the IP Core interface

Signal name Type Function

rst* Input Master reset (High active)

clk* Input Clock input

sync* Input Position sampling resolution

interrupt Output Configurable interrupt

link Output Connection indication

pos_ready Output Position data availability indication

sync_locked Output Position sampling resolution locked

bigend Input Byte sequence choice

fast_pos_rdy Output Fast position update indication

sample Output DSL bit sampling information

estimator_on Output Postion Estimator activated

safe_channel_err Output Transmission error in safe channel 1

safe_pos_err Output Safe position not valid

acceleration_err Output Fast channel / position error

acc_thr_err Output Fast channel / position threshold error

encoding_err Output DSL message encoding error

dev_thr_err Output Estimator deviation threshold reached

aux_signals Output (12) Auxiliary signals

dsl_in* Input DSL cable, input data

®

19

Page 20

rst

a b

Switch on

4 HARDWARE INSTALLATION

Signal name Type Function

dsl_out* Output DSL cable, output data

dsl_en* Output DSL cable transceiver, activation

spipipe_ss Input SensorHub SPI slave select

spipipe_clk Input Serial clock for SPI SensorHub

spipipe_miso Output SPI SensorHub, master output data/slave input

online_status_d Output (16) IP Core status information

hostd_a Input (7) Host interface address

hostd_di Input (8) Host interface data in

hostd_do Output (8) Host interface data out

hostd_r Input Host interface data read

hostd_w Input Host interface data write

hostd_f Input Host interface register freeze

* these signals must be assigned to physical pins of the FPGA.

4.2.2 SYNC signal

data

4.2.3 Reset signal

The HIPERFACE DSL® communication can be established in “SYNC mode” or “free run‐

ning mode”. In free running mode, the IP-Core will use the fastest possible transmis‐

sion timing and this input should be low (0). Please note that the IP-Core is not bound

to any timing of the frequency inverter in this mode.

In SYNC mode the frequency inverter clock must be supplied to this input/pin. Please

refer to table 8 for the signal specification. This signal triggers position sampling of the

DSL encoder. The polarity of the edge can be programmed using the SPOL bit in the

SYS_CTRL register.

As the frame cycle time must always be within a limited range, a divider for the SYNC

frequency has to be chosen accordingly. The divider value needs to be written to the

SYNC_CTRL register.

NOTE

In case of the SYNC frequency changing, the IP-Core will synchronize automatically. Dur‐

ing this synchronization the former sampling frequency is used. Please note that this

synchronization takes a few SYNC periods.

rst is the reset input (high active) of the DSL Master IP Core.

After start-up (switching on) of the frequency inverter, a reset procedure is mandatory to

return the DSL Master IP Core to its initialization condition.

The reset procedure is established by the parameters listed in table 8 and quoted in

figure 8.

20

Figure 8: Reset procedure

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 21

Table 8: Reset time sequence

Diagram reference Parameters in figure 8 Value (cf.figure 8)

a Reset delay Variable

b Duration of the reset signal >60 ns

Additional pin functions are described in detail in chapter 5.

4.3 Cable specification

HARDWARE INSTALLATION 4

The cable recommended for connecting the frequency inverter to the HIPERFACE DSL

®

motor feedback system is specified by the parameters set out in table 8. These techni‐

cal data apply to all configurations.

In the case of integrated cables (see chapter 4.1.2), the motor cables are not listed.

Table 9: Technical data for the HIPERFACE DSL® cable

Characteristic Minimum Typical Maximum Units

Length 100 m

Impedance at 10 MHz 100 110 120

DC loop resistance 0.1

W

W/m

Velocity ratio 0.66 c

Propagation delay 5 ns/m

Limit frequency 25 MHz

Maximum current per cable 0.25 A

Operating temperature -40 125 °C

More information relating cable construction and installation are available on the

Whitepaper “Cable and Connector for HIPERFACE DSL® Motor and Drive Applications”.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

21

Page 22

Inverter

OK …

MFB

system

DSL

Response

Drive

Application

DSL

Master

DSL

Request

rst rst

clk clk

Drive interface Drive interface

SPI-PIPE SPI-PIPE

Control signals

Control signals

Test signals

Test signals

5 INTERFACES

5 Interfaces

The IP Core of the DSL Master includes interfaces to the motor feedback system (DSL

Slave) and to the frequency inverter application (see figure 9).

The motor feedback system communicates via a DSL connection with the DSL Master.

All data channels between the DSL Master and DSL Slave are routed via this connec‐

tion.

The user application is connected via one interface (choice of SPI or parallel bus) and

several control signals . In addition, the frequency inverter provides a clock signal (CLK)

and a reset signal (RST) to the DSL Master IP Core. By means of these signals, a

defined start-up performance is achieved.

According to the requirements of the particular application, an optional serial interface

(SPI-PIPE) can be employed to use the SensorHub Channel (see chapter 3.5).

The various interfaces correspond to the tasks described in table 10.

Figure 9: DSL system interfaces

Table 10: Interface functions

Interface Function

Drive interface Register-based access to all DSL Master and DSL Slave functions relevant

SPI PIPE Optional register-based access to SensorHub Channel data

Control signals DSL Master indication and control signals

Test signals Test signals for development or fault-finding for a DSL controller

CLK Clock signal for the IP Core circuit

RST Reset signal for the IP Core circuit

DSL Connection to the motor feedback system

5.1 Drive interface

The drive interface forms the central communications interface between the frequency

inverter application and the DSL Master IP Core. Absolute and fast position data can

be read via this interface. The functions of the motor feedback system are also accessi‐

22

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

ble via this interface.

The following signals are used for Drive interface:

Table 11: Drive interface signals

Pin name Type Function

online_status_d(0:15) Output IP Core status (see chapter 6.2)

®

for the core frequency inverter application

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 23

Pin name Type Function

hostd_a(0:6) Input Register address bus

hostd_di(0:7) Input Register input data bus

hostd_do(0:7) Output Register output data bus

hostd_r Input Read signal

hostd_w Input Write signal

hostd_f Input Freeze signal

Example installations of interface blocks for the Drive interface of the DSL Master are

supplied together with the IP Core. These examples include a serial SPI interface and a

parallel Texas Instruments EMIFA interface. For more information please see

chapter 9.1.

5.2 SPI PIPE Interface

The SPI PIPE is a read-only Serial Peripheral Interface (SPI). SPI PIPE is an optional com‐

munication channel between the frequency inverter application and the DSL Master IP

Core. Read processes on the SensorHub Channel can be carried out via this interface.

Alternatively, this data can also be read from the registers by standard transactions via

Drive interface.

INTERFACES

5

The type of access to the SensorHub Channel is selected by setting or deleting the

SPPE bits in the SYS_CTRL register (see chapter 6.3.1). If the SPPE bit is deleted, the

data and the status of the SensorHub channel are accessible via the DSL Master

PIPE_S (2Dh) and PIPE_D (2Eh) registers. If the SPPE bit is set, the SensorHub Channel

is read using the SPI PIPE "Read Pipeline" transaction.

SPI PIPE should be activated if, at a fast frequency inverter cycle, the bandwidth of

Drive interface is insufficient to access position and pipeline data, or if the pipeline

data is being processed by another frequency inverter application resource.

NOTE

It should be noted that in every case, the configuration of external sensor components

at the sHub® is carried out via the DSL Master Parameters Channel. The SPI PIPE pro‐

vides only one read access to the SensorHub Channel (see chapter 3.5).

The SensorHub Channel data is kept in a FIFO (First In First Out) buffer that can hold 8

bytes. In addition, for each data byte, status information is also stored in the FIFO buffer

(see chapter 6.3.22 and chapter 6.3.23).

NOTE

It should be noted that the FIFO buffer can only store 8 bytes of SensorHub Channel

data. If the buffer is not read quickly enough, old data will be overwritten. This is indi‐

cated by a flag in the FIFO buffer status information.

The SPI Master for the SPI PIPE is the frequency inverter application. The SPI functions

"Slave Selection" (Pin: spipipe_ss) and "clock" (Pin: spipipe_clk) are controlled by

the frequency inverter application. The SPI function "Data, Master input Slave output"

(Pin: spipipe_miso) is controlled by the DSL Master.

SPI PIPE has the following SPI characteristics:

PHA = 1 (Sampling for clock trailing edge, data changes for clock leading edge)

•

POL = 0 (Basic clock value)

•

The data with the highest value bit (MSB) is given first.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

23

Page 24

spipipe_clk

spipipe_miso

POL=0

PHA=1

1 2 3 4 5 6 7 8

a

b c

n-1 n

d

e

f

spipipe_ss

spipipe_clk

spipipe_miso

PIPE STATUS PIPE DATA

spipipe_ss

5 INTERFACES

When accessing the SensorHub Channel via the SPI PIPE, the first four bits of the sta‐

tus buffer (0101) show a different value for each transaction, in order to check the cor‐

rect function of the interface.

5.2.1 SPI-PIPE timing

The time sequence for SPI PIPE is shown in the time sequence diagram (figure 10 )

below and in table 12.

Figure 10: SPI-PIPE interface time control

Table 12: SPI-PIPE time control

Diagram

reference

Description Mini‐

mum

Maxi‐

mum

Units

A Assertion of spipipe_ss before spipipe_clk 30 ns

B Time for spipipe_clk high 30 ns

C Time for spipipe_clk low 30 ns

D spipipe_ss pulse width 30 ns

E Delay spipipe_miso after spipipe_ss high 25 70 ns

F Delay spipipe_miso after spipipe_clk high 25 70 ns

5.2.2 Read pipeline

The SPI PIPE transaction "Read Pipeline" is used for access to the FIFO buffer values

that contain the data and status of the SensorHub Channel.

Table 13: "Read Pipeline" transaction

Symbol Meaning

PIPE STATUS SensorHub Channel status (see chapter 6.3.21)

PIPE DATA SensorHub Channel data (see chapter 6.3.22)

Figure 11: "Read Pipeline" transaction

5.3 Control signals

Various control signals are available between the DSL Master and the frequency

inverter application to configure the performance of the IP Core or to carry out fast

monitoring of the IP Core status.

5.3.1 SYNC signal

sync is a DSL Master digital input.

24

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 25

One edge on this pin triggers a position sampling. The polarity of the edge can be pro‐

grammed using the SPOL bit in the SYS_CTRL (00h) register. The protocol requires a

constant frequency of the signal at this pin, with deviations permitted within a set toler‐

ance band. Continuously, the protocol synchronizes the protocol frame with the signal

frequency at sync.

NOTE

If the sync signal frequency is outside the tolerance range, re-synchronization of the

protocol is triggered. During the time that the re-synchronization is taking place, sam‐

pling is carried out with the former sync frequency until the re-synchronization is com‐

plete. For more details on the sync signal also see chapter 7.3.3.

5.3.2 INTERRUPT signal

interrupt is a DSL Master digital output.

interrupt is set to "1" if an interrupt condition has been fulfilled in the DSL-Master.

The interrupt conditions are set using the registers MASK_H, MASK_L and MASK_SUM

(see chapter 6.3.5 and chapter 6.3.6).

NOTE

During each write process in one of the registers EVENT_H or EVENT_L, the interrupt

output is masked until the current SPI transaction has ended.

INTERFACES 5

5.3.3 LINK signal

link is a DSL Master digital output.

link is effected by the content of the LINK bit in the MASTER_QM register (see

chapter 6.3.3) and therefore indicates whether the DSL Master has produced a com‐

munications link to a connected HIPERFACE DSL® motor feedback system.

link is intended to be a control signal for an LED display, but can also be used to con‐

trol the start-up performance (see chapter 7.1) or for global error handling.

link is reset if communication faults are detected.

5.3.4 FAST_POS_RDY signal

fast_pos_rdy is a DSL Master digital output.

fast_pos_rdy signals that a new fast position value is available and permits an

event-based reading of the position for incorporating latency reduction.

fast_pos_rdy is always available, even if the position value is invalid or no connec‐

tion to the encoder has been established.

Dependent upon the configuration in the register system control (see chapter 6.3.1),

fast_pos_rdy displays either only the availability of positions based on user require‐

ments (edge at sync input) or all transmitted positions.

5.3.5 SYNC_LOCKED signal

sync_locked is a DSL Master digital output.

sync_locked indicates whether the sync signal was correctly passed to the encoder,

or whether the IP Core is still in a synchronization phase. sync_locked drops to “0”

when the SYNC edge supplied by the application has been transported with more than

2 clock cycles of distortion.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

25

Page 26

5 INTERFACES

5.3.6 BIGEND signal

5.4 Test signals

5.4.1 SAMPLE signal

bigend is a DSL Master digital input.

The byte sequence of the address allocation for registers can be influenced via bigend

(see chapter 9.5). The byte sequence is based on 32 bit-wide data words. The selection

influences the allocation independently of the interface block used.

Table 16 below lists the selection options for bigend.

Table 14: bigend selection

Value Address allocation byte sequence

0 Little endian

1 Big endian

To support development or fault-finding for controllers that have a DSL interface inte‐

grated, the DSL Master supplies some test signals.

sample is a DSL Master digital output.

The sample signal is set at the sampling time point of each bit that is transmitted from

the DSL motor feedback system. It consists of 50 pulses from Channel 1 followed by a

bit pause and 10 pulses from Channel 2 of the motor feedback system.

Figure 12: Sample signal

The sample signal can be used for eye diagrams to measure time and voltage margins

during signal transmission.

When making the evaluation, signal delays in the DSL Master must be taken into

account. The rising edge of the sample signal is offset by 40 ns from the line driver

signal. The time delay of the line driver must also be taken into account. Typically this is

13 ns.

5.4.2 ESTIMATOR_ON signal

estimator_on is a DSL Master digital output.

26

The estimator_on signal is set if some event leads to the transmitted fast position

(see chapter 6.3.12) being invalid and the position estimator supplying the values.

Such events are:

The DSL motor feedback system reporting a position error

•

A coding error in transmission of the fast position

•

A check-sum error in transmission of the fast position

•

Realignment from safe to fast - fast position is forced to the safe position value

•

The protocol is re-synchronizing following a break in the link

•

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 27

The estimator_on signal can be used to carry out a statistical analysis of the inci‐

dence of errors in the DSL system. For more information, please refer to chapter 7.3.1.

It should be noted that the POS flag and estimator_on signal information is redun‐

dant.

5.4.3 DEV_THR_ERR signal

dev_thr_err is a DSL Master digital output.

If the fast position from the process data channel cannot be calculated (either due to

transmission or due to sensor errors), estimation is made by the DSL Master based on

the last two available position values of the Safe Channel. The worst case deviation

from the actual mechanical position is also provided, referring to a user- defined para‐

meter for the maximum possible acceleration in the application (fast position accelera‐

tion boundary, see chapter 6.3.25).

A threshold can be set up for a worst case deviation to raise the dev_thr_err out-

put. The threshold is a user defined parameter for the maximum tolerable deviation in

the application (fast position estimator deviation, see chapter 6.3.26).

dev_thr_err indicates whether the maximum tolerable deviation is violated (‘1’) or

kept (‘0’).

INTERFACES 5

5.4.4 SAFE_CHANNEL_ERR signal

safe_channel_err is a DSL Master digital output.

The safe_channel_err signal is set if some event leads to the safe position or sta‐

tus (see chapter 6.3.15) being invalid. Such events are:

A coding error in transmission of the safe position

•

A check-sum error in transmission of the safe position

•

The safe_channel_err signal can be used to carry out a statistical analysis of the

incidence of errors in the DSL system.

5.4.5 SAFE_POS_ERR signal

safe_pos_err is a DSL Master digital output.

safe_pos_err is a DSL Master digital output. The safe_pos_err signal is set if the

safe position of Safe Channel 1 is not updated or it has never been written since the

startup. Another possible cause can be the DSL motor feedback system reporting a

position error.

5.4.6 ACCELERATION_ERR signal

acceleration_err is a DSL Master digital output.

The acceleration_err signal is set if an encoding error was detected after transmis‐

sion of a fast position value, or if the encoder has transmitted an invalid acceleration

cause of internal errors.

If the acceleration_err signal is set the error counter acc_err_cnt will be incre‐

mented with each transmission (see chapter 6.3.24). As soon as the accelera-

tion_err signal is reset the error counter acc_err_cnt will be set to “0” again.

5.4.7 ACC_THR_ERR signal

acc_thr_err is a DSL Master digital output.

The acc_thr_err signal is set if the threshold programmed in register

acc_err_cnt is exceeded.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

27

Page 28

5 INTERFACES

The acc_thr_err signal can be used to implement a fault-tolerant evaluation in the

drive. For this the maximum position deviation should be calculated from the number of

transmission errors.

5.4.8 ENCODING_ERR signal

encoding_err is a DSL Master digital output.

The encoding_err signal is set if the underlying 8B/10B encoding of a DSL frame

transmission is disturbed.

The encoding_err signal can be used to make a statistical analysis of the bit error

rate of a DSL system.

28

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 29

6 Register map

DSL Master Primary

functions

Registers

for all

main

functions

00h

01h

|

|

2Dh

2Eh

|

3Eh

3Fh

Drive interfacexx

SPI-PIPEx

DSL

Slave

Remote

Registers

40h

41h

|

|

|

7Eh

7Fh

(optional)

The DSL Master is accessible via register in three different register blocks. Each register

block has its own address area (see table 15).

Table 15: Register blocks address area

Register block Address area Functions

Drive 00h to 3Fh

Safe 1 00h to 7Fh Safe Channel 1, position/status

Safe 2 00h to 3Fh Safe Channel 2, position/status

All IP Core registers and functions can be accessed via drive interface. As an option, the

SensorHub Channel data is accessible via the SPI PIPE interface.

In addition, the DSL Slave interface registers are mirrored as decentralized registers.

The address area 40h to 7Fh is intended for this. The addressing of these registers is

identical to the addressing of the registers in the DSL Master. The answer to the trans‐

action is, however, delayed and must be read individually (see under "Short message",

in chapter 7.5.1).

60h to 6Fh

REGISTER MAP 6

Process data Channel, position/status

Parameters Channel (long messages)

SensorHub Channel

Parameters Channel (short messages)

6.1

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

figure 13 below shows via which interface a connection to which register block is estab‐

lished.

Figure 13: Register block overview

Explanation of the registers

In the following description of the registers, symbols are used to describe the standard

value of a bit following a reset. Additional symbols are used to describe the functions

provided to the frequency inverter application for this bit.

®

29

Page 30

REGISTER MAP

6

The bit is described according to the following example: "Function" "Reset value", e.g.

"R/W-0"

Table 16: Function symbols for bits

Function symbol Meaning

R Bit can be read.

W Bit can be set and deleted.

C Bit can only be deleted.

X Bit is not installed and will always be read as "0".

Table 17: Symbols for bit reset values

Reset value Meaning

0 The bit is deleted after a reset.

1 The bit is set after a reset.

x After a reset, the bit has no defined value.

- In the register diagram:

The bit is not installed and will always be read as "0".

NOTE

It should be noted that read access to a bit that can only be written ("W") always returns

the value "0". If a register address that is not used is read, the result will be “0” as well.

6.2 Online Status D

The Online Status D is a non-storing copy of registers EVENT_H and EVENT_L. The sta‐

tic information in these registers must be deleted by the user after the read process, by

writing the value "0" to the corresponding bit in the register, whilst the Online Status D

only shows the current status without storing previous indications. The signal name of

the Online Status is online_status_d (with d indicating drive).

online_status_d is given in two bytes. If an SPI block is used for interfacing the IP

Core, online_status_d is transmitted in each transaction in the first two bytes via

the spi_miso output. When a parallel bus interface is used for drive interface,

online_status_d has 16 dedicated output signals available.

NOTE

It should be noted that when the parallel bus interface is used the 16 signals of the

Online Status D are not frozen during a read access. If required, the user can insert a

Latch (e.g. using the hostd_fcode.inlinesignal).

Table 18: Online Status D, High Byte

Bit 7

INT: Status of the Interrupt output

R-0 R-0 R-1 R-1 R-1 R-1 R-1 R-1

INT SUM SCE FIX1 POS VPOS DTE PRST

Bit 7 Bit 0

30

This bit represents an exception to the Online Status D, as this bit does not relate to an

event indication. INT provides the value of the physical INT output so that request man‐

agement (polling) can be established. The importance of this flag depends on the Inter‐

rupt sources monitored.

1 = interrupt output on "High" level

0 = interrupt output on "Low" level

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 31

Bit 6 SUM: Summary byte

1 = The last valid value from SUMMARY was not zero. The importance of this flag

depends on the particular error source that leads to a set SUMMARY (see

chapter 6.3.14).

0 = The last valid value from SUMMARY was zero.

REGISTER MAP

6

Bit 5

SCE: CRC error on the Safe Channel

1 = The last Safe Channel CRC received was wrong. It is expected that the last safe

position transmitted (see chapter 6.3.16) is invalid.

0 = The last Safe Channel CRC received was correct.

Bit 4 FIX1: This bit always gives a "1". For SPI interfaces, this is used for checking the

spi_miso pin for stuck-at- '0' faults.

Bit 3 POS: Estimator turned on (functionality based on estimator_on, see chapter 5.4.2)

1 = A source of an error in the fast position was identified or an alignment procedure is

currently being carried out. It is probable that the last fast position is invalid. Be aware

that the fast position read through drive interface is provided by the estimator.

0 = No fast position error.

Bit 2

VPOS: Safe position invalid

1 = An error in the safe position was identified. It is expected that the safe position

transmitted from the encoder is invalid.

0 = The last safe position received was correct.

Bit 1 DTE: Deviation Threshold Error (see chapter 5.4.3)

1 = Current value of deviation greater than the specified maximum.

0 = Current value of deviation smaller than the specified maximum.

Bit 0 PRST: Protocol reset

1 = IP-Core has restarted the protocol.

0 = IP-Core running.

Table 19: Online Status D, Low Byte

X-0 X-0 R-0 R-0 R-0 R-1 R-0 R-0

POSTX MIN ANS FIX0 QMLW FREL FRES

Bit 7 Bit 0

Bit 7-6 POSTX1:POSTX0: Position transmission status

00: Position request is transmitted to the DSL encoder.

01: Safe Channel was correctly transmitted.

10: Fast position present (see chapter 6.3.11).

11: Safe Channel 2 was correctly transmitted.

Recommended to trigger on rising edge of a POSTX bit change (is set). A new state is

indicated by a set bit. It is cleared/maintained until a new frame/event arrives.

Bit 5

MIN: Acknowledgment of message initialization

1 = The DSL encoder sends a figure by which the initialization of the Parameter Chan‐

nel is acknowledged.

0 = Parameter Channel not functioning.

Bit 4

ANS: Incorrect answer detected.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

31

Page 32

6 REGISTER MAP

1 = The last answer to a long message was damaged.

0 = No error detected in the last answer to a long message.

Bit 3 FIX0: This bit always gives a "0". For SPI interfaces, this is used for checking the

spi_miso pin for stuck-at-'1' faults.

Bit 2 QMLW: Quality monitoring at Low level (see chapter 6.3.3)

1 = Current value of quality monitoring less than 14.

0 = Current value of quality monitoring greater than or equal to 14.

Bit 1 FREL: Channel status for “long message”.

1 = The channel for the “long message” is free.

0 = The channel for the “long message” is in use.

Bit 0 FRES: Channel status for the "short message". 1 = The channel for the "short message"

is free.

0 = The channel for the "short message" is in use.

6.3 DSL Master function register

The protocol logic controls the performance of the DSL Master via the registers in the

DSL Master IP Core on drive interface. These registers are also used for accessing the

position values.

The table below contains a list of all the function registers available in the IP Core.

NOTE

The addresses given below are referencing a big-endian addressing. For a table stating

the register addresses depending on the endianness, see chapter 9.5.

Table 20: Description of the registers in DSL Master, drive interface

Addr Designation Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value at reset

00h SYS_CTRL PRST MRST FRST LOOP PRDY SPPE SPOL OEN 0000 0000

01h SYNC_CTRL ES 0000 0001

03h MASTER_QM LINK - - -

04h EVENT_H INT SUM SCE - POS VPOS DTE PRST 000- 0000

05h EVENT_L - - MIN ANS - QMLW FREL FRES --00 -000

06h MASK_H - MSUM MSCE - MPOS MVPOS MDTE MPRST -00- 0000

07h MASK_L - - MMIN MANS - MQMLW MFREL MFRES --00 -000

08h MASK_SUM MSUM7:0 0000 0000

09h EDGES Bit sampling pattern 0000 0000

0Ah DELAY RSSI Cable delay 0000 0000

0Bh VERSION Coding

0Ch RELEASE Release date FIFO 0000 0000

0Dh ENC_ID2 - SCI ENC_ID19:16 -000 0000

0Eh ENC_ID1 ENC_ID15:8 0000 0000

0Fh ENC_ID0 ENC_ID7:0 0000 0000

10h POS4 Fast position, byte 4 0000 0000

11h POS3 Fast position, byte 3 0000 0000

12h POS2 Fast position, byte 2 0000 0000

IP Core version number

Quality monitoring

0--- 0000

0101 0111

32

T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Page 33

REGISTER MAP 6

Addr Designation Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value at reset

13h POS1 Fast position, byte 1 0000 0000

14h POS0 Fast position, byte 0 0000 0000

15h VEL2

Speed, byte 2

16h VEL1 Speed, byte 1 0000 0000

17h VEL0 Speed, byte 0 0000 0000

18h SUMMARY SUM7:0 0000 0000

19h VPOS4

Safe position, byte 4

1Ah VPOS3 Safe position, byte 3 0000 0000

1Bh VPOS2 Safe position, byte 2 0000 0000

1Ch VPOS1 Safe position, byte 1 0000 0000

1Dh VPOS0 Safe position, byte 0 0000 0000

1Eh VPOSCRC_H CRC of the safe position, byte1 0000 0000

1Fh VPOSCRC_L CRC of the safe position, byte0 0000 0000

20h PC_BUFFER0

Parameters Channel, byte0

21h PC_BUFFER1 Parameters Channel, byte1 0000 0000

22h PC_BUFFER2 Parameters Channel, byte2 0000 0000

23h PC_BUFFER3 Parameters Channel, byte3 0000 0000

24h PC_BUFFER4 Parameters Channel, byte4 0000 0000

25h PC_BUFFER5 Parameters Channel, byte5 0000 0000

26h PC_BUFFER6 Parameters Channel, byte6 0000 0000

27h PC_BUFFER7 Parameters Channel, byte7 0000 0000

28h PC_ADD_H LID LRW LOFF LIND LLEN LADD9:8 1000 0000

29h PC_ADD_L LADD7:0 0000 0000

2Ah PC_OFF_H LID LOFFADD14:8 1000 0000

2Bh PC_OFF_L LOFFADD7:0 0000 0000

2Ch PC_CTRL - - - - - - - LSTA ---- ---0

2Dh PIPE_S - - - - POVR PEMP PERR PSCI ---- 0000

2Eh PIPE_D SensorHub FIFO, output 0000 0000

2Fh PC_DATA

"Short message" data

38h ACC_EE_CNT - - - Acc. errorthreshold/counter ---0 0000

39h MAXACC Acc. Res. Acc. Mantissa 1111 1111

3Ah MAXDEV_H Max. position deviation, byte1 0000 0000

3Bh MAXDEV_L Max. position deviation, byte0 0000 0000

3Fh DUMMY No data ---- ----

0000 0000

0000 0000

0000 0000

0000 0000

NOTE

It should be noted, that some registers are shared (e.g. 09h EDGES) and others are just

used for accessing the same data (SYS_CTRL and SAFE_CTRL, for instance). In most

cases though, both interfaces use registers that are exclusively available to them.

6.3.1 System control

The system control register SYS_CTRL contains the main control bits of the DSL Master.

8017595/ZTW6/2018-01-15 | SICK T EC H NI C AL IN F OR M AT I ON | HIPERFACE DSL

Subject to change without notice

®

33

Page 34

6 REGISTER MAP

Register 00h: System control

Bit 7 PRST: Protocol reset

Bit 6 MRST: Messages reset

NOTE

It should be noted that apart from a reset of the Master, all system control bits can only

be set and deleted by the user.

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

PRST MRST FRST LOOP PRDY SPPE SPOL OEN

Bit 7 Bit 0

1 = A forced reset of the protocol status will be initiated. If the bit is deleted, a restart of

the connection is triggered.

0 = Normal protocol action

1 = The Parameters Channel is reset. Current short and long messages are discarded.

0 = Normal Parameters Channel action

Bit 5

FRST: Pipeline FIFO, reset

1 = The FIFO is reset. Data is not stored and cannot be read.

0 = Normal FIFO access

Bit 4

LOOP: Test drive interface

Value for the read back test for drive interface. This value has no other purpose.

Bit 3 PRDY: POS_READY mode.