Page 1

5

4

3

2

1

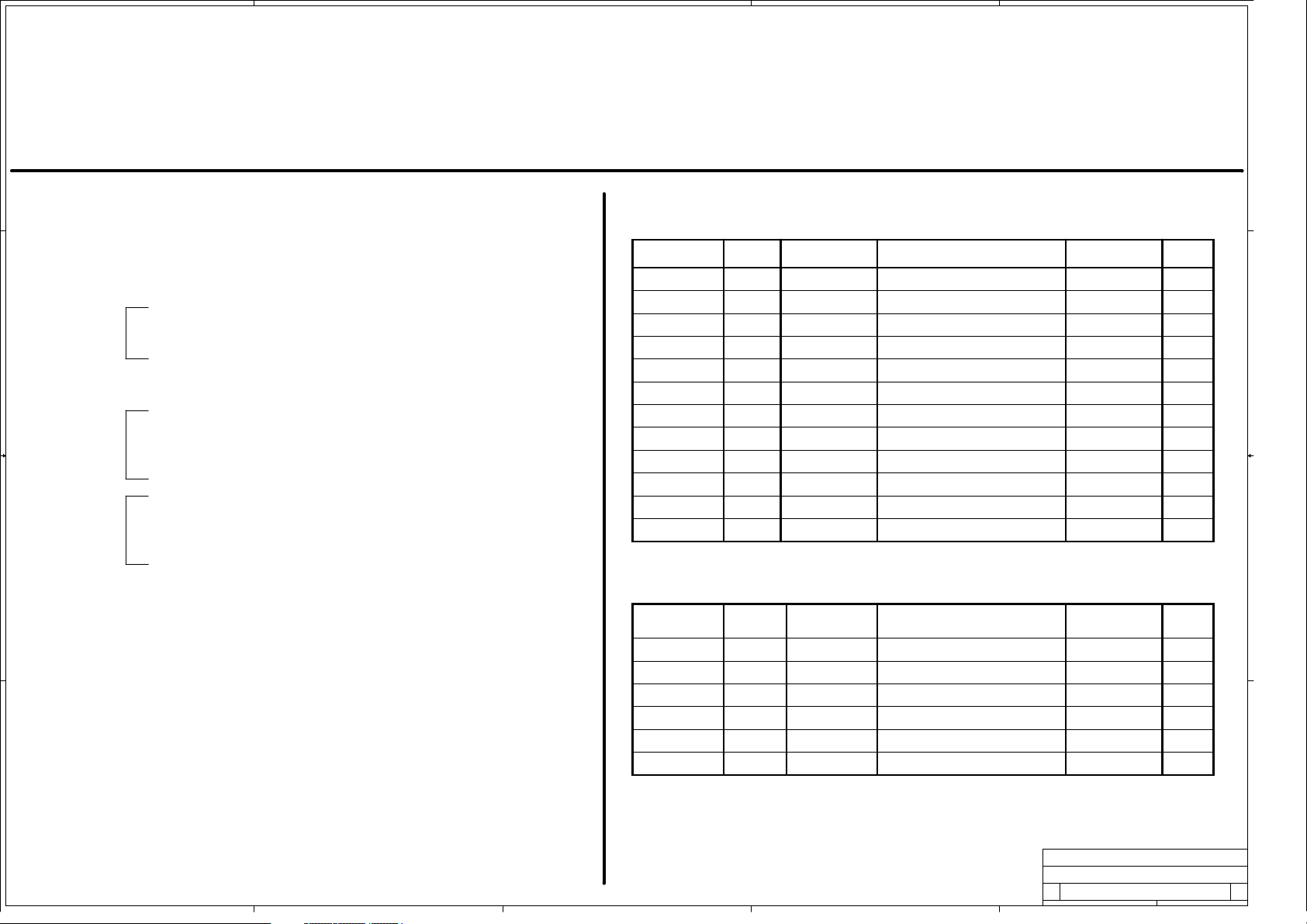

Project Name : A14RMXX REV:1.0

D D

Platform : AMD Danube (Champlain RS880M SB820M)

PAGE

CONTENT

1.

INDEX

2. SYSTEM BLOCK DIAGRAM

SYETEM SEQUENCE

3.

POWER DIAGRAM

4.

CLOCK GEN (ICS9LRS365B) <--DEL

5.

S1G4 HT 1/4

6.

S1G4 DDR 2/4

C C

CPU

NB

SB

B B

A A

7.

S1G4 CTRL DEBUG 3/4

8.

S1G4 PWR 4/4

9.

DDR3 SODIMM

10.

DDR3 SODIMM DECOUPLING

11.

RS880M HT 1/5

12.

RS880M PCIE 2/5

13.

RS880M SYSTEM,DISPLAY 3/5

14.

RS880M SPMEM,SRTAP 4/5

15.

RS880M POWER 5/5

16.

SB8X0 PCIE,CPU,LPC ,CLK 1/5

17.

SB8X0 ACPI,USB,AZ,GPIO 2/5

18.

SB8X0 SATA,SPI,HWM 3/5

19.

SB8X0 POWER 4/5

20.

SB8X0 STRAPS 5/5

21.

CRT,LVDS

22.

HDMI,PWR BTN

23.

CODEC(92HD81),MIC,SPKR,MDC

24.

EXT_MIC/H_P/USB_CHG/G-SEN/3G

25.

HDD/ODD /MINI CARD

26.

LAN/CARD JMC251 / 30PIN CONN

27.

TP/LED/WebCam/FAN

28.

EC IT8500BX/BIOS/KB CONN

29.

VCC SW

30.

31.

DC IN/BT/HOLE/HIGH-SPEED CAP

32.

BATT IN/CHARGER(OZ8602)

33.

CPU CORE/CPU_VDDNB(OZ8380)

34.

+1.1VS(OZ8116)/+0.75VS/+1.8V

35.

+1.5VS/+5VA (OZ815)/+3.3VA

36.

+CPU_VDDR/+2.5V

37.

Reserved

5

4

Release Date PCB P/N

2010.05.20

Daughter Board Schematic Version Change List

3

M/B Schematic Version Change List

PCB Description

A2010.04.09

71R-A14RM0-9HA0 HANDSTAR

71R-A14RM0-T8A0 TTL

71R-A14RM0-4BA1 BTI

A12010.05.19

71R-A14RM0-T8A1 TTL

B

PCB P/N PCB DescriptionRelease Date Version PCBA P/N Note

2

NotePCBA P/NVersion

64R-A14RM1-00A071R-A14RM0-4BA0 BTI

64R-A14RM1-00A1

64R-A14RM1-00B0

64R-A14RM1-10B0

64R-A14RM1-20B0

Shuttle Inc

Shuttle Inc

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Shuttle Inc

A14RM

A14RM

A14RM

INDEX

INDEX

INDEX

1

1 37Monday, October 18, 2010

1 37Monday, October 18, 2010

1 37Monday, October 18, 2010

1.0

1.0

1.0

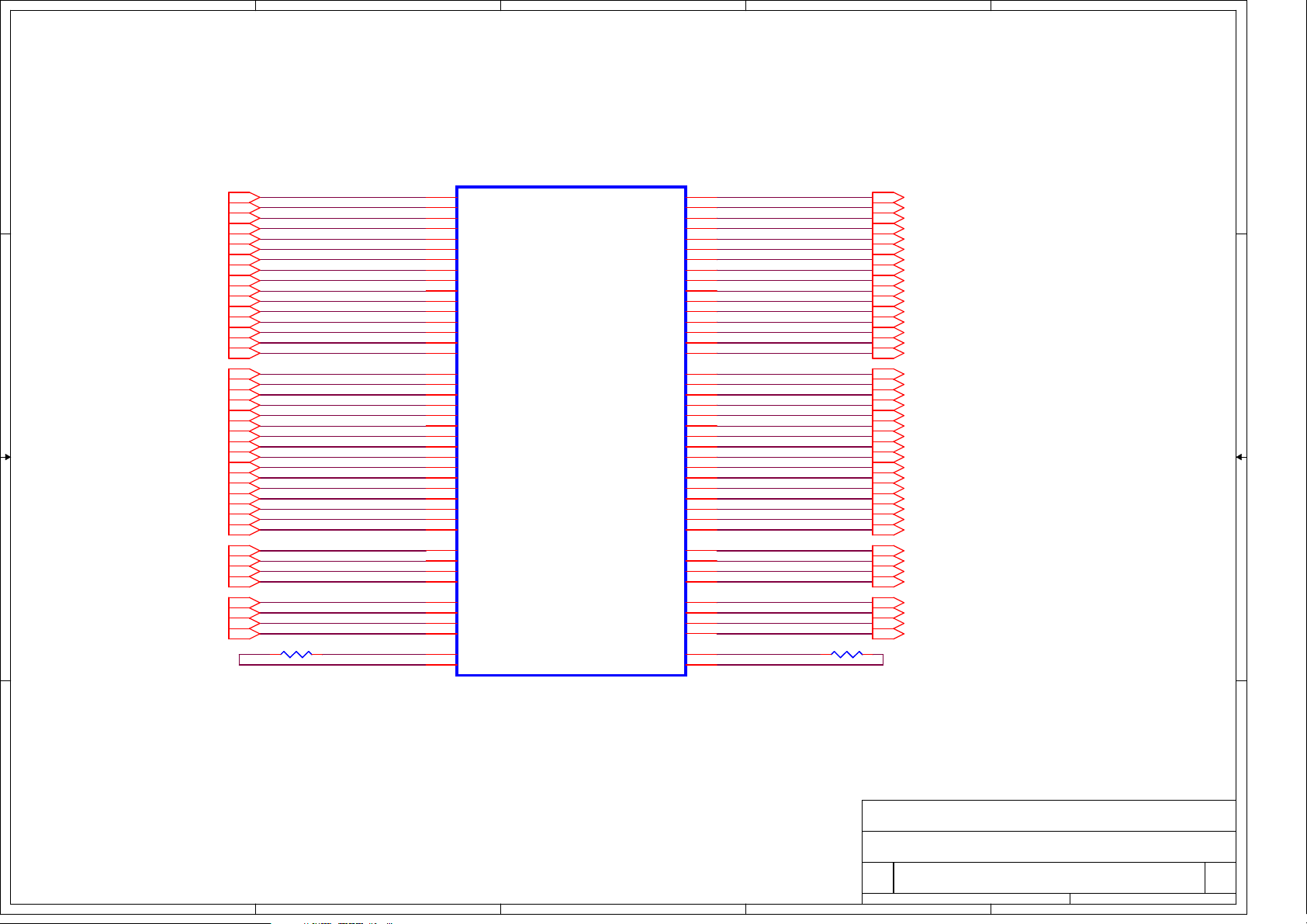

Page 2

5

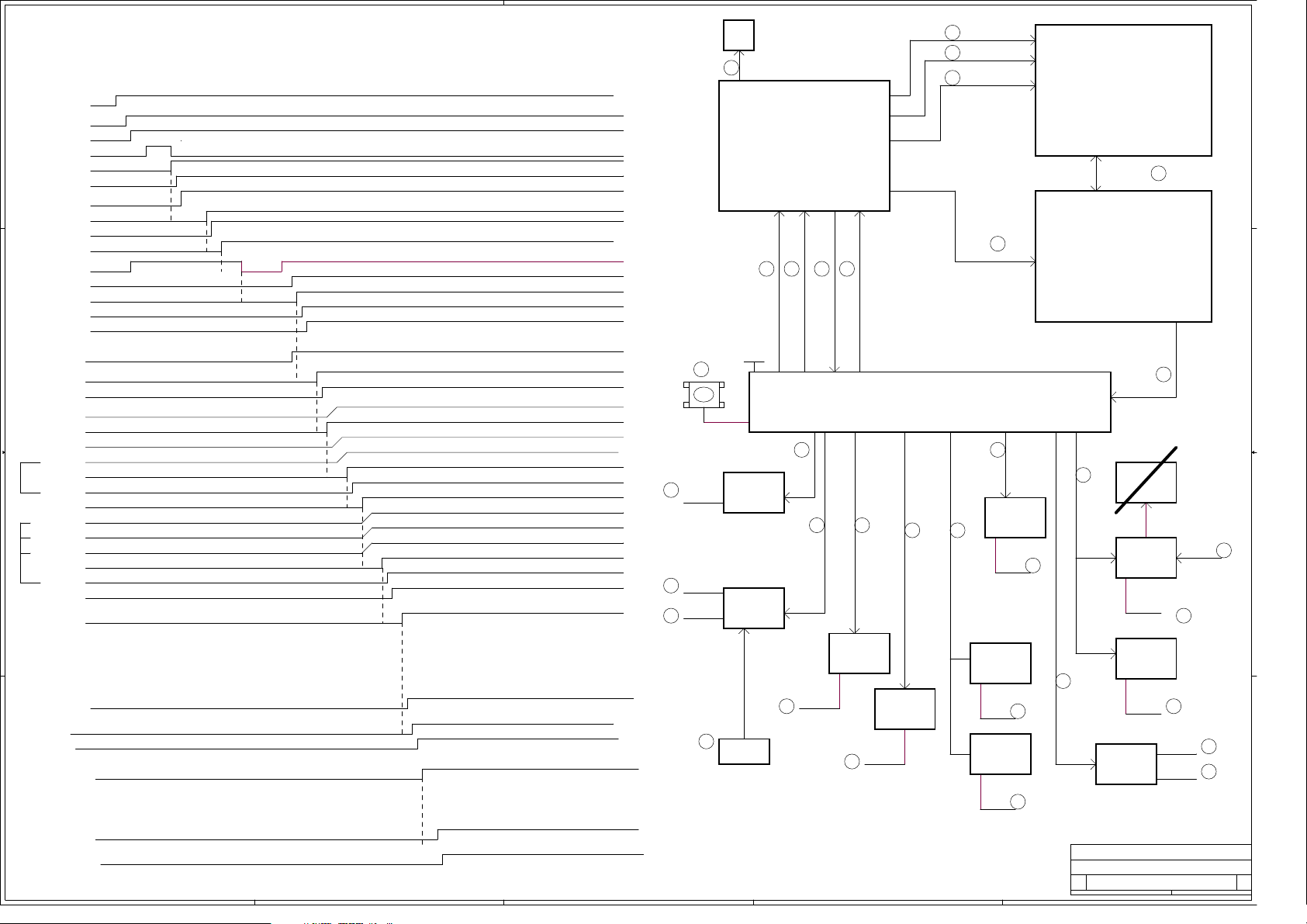

SYSTEM BLOCK DIAGRAM

4

3

2

1

S1G4 SCHEMATIC DESIGN

DDR III, 1333MT/S

Channel A

D D

LVDS CON

VGA CON

C C

B B

HDMI CON

Card Reader

GIGA Lan

22

22

23

27

26 26

MINIPCIE

3G

25

SIM

Mobile 2.5" HDDMobile ODD

AZALIA CODEC

26

Webcam

24

28

GPP INTERFACE

USB*4

25,31

SATA III I/F

HD AUDIO I/F

USB 2.0

AMD S1G4 CPU

25,35,45nm

6,7,8,9

HyperTransport

LINK0

16x16

RS880M

HyperTransport LINK0 CPU I/F

DX10 IGP

LVDS/TVOUT/TMDS

DISPLAY PORT X2

Side Port Memory

1 X16 PCIE I/F

1 X4 PCIE I/F WITH SB

6 X1 PCIE I/F

12,13,14,15,16

PCIE

X4

SB820M

USB2.0 (14)+1.1(2)

SATA III (6 PORTS)

4 X1 PCIE GEN2 I/F

INT. CLK GEN.

GB MAC

HW MONITOR

PCI/PCI BDGE

INT. RTC

26,27,28,29

EC

HD AUDIO

LPC I/F

SPI I/F

ACPI 1.1

Channel B

Mini Card Debug Port

UNBUFFERED DDR3

NEAR SODIMM

18,19

UNBUFFERED DDR3

FAR SODIMM

18,19

CPU Thermal Sensor

ADM1032

SB-TSI

8

SMBUS FORM SB

Clock Gen

ICS9LPR3165B

G-SENSOR

7 Pin

LPC

26

SMBUS FORM SB

5

25

Embedded Controller (EC)

SPI

8

SMBUS 1

ITE8500-BX

PS/2

Battery

7 Pin

SMBUS 0

32

GPIO

29

K/B Matrix

Charger

OZ8602

FAN

3 Pin

GMT_G990

32

28

Flash Rom

8 Pin M-SOP

A A

29

www.schematic-x.blogspot.com

5

4

3

T/P

12 Pin

28

Internal K/B

2

29

Shuttle Inc

Shuttle Inc

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Shuttle Inc

A14RM

A14RM

A14RM

SYSTEM BLOCK

SYSTEM BLOCK

SYSTEM BLOCK

1

1.0

1.0

2 37Monday, October 18, 2010

2 37Monday, October 18, 2010

2 37Monday, October 18, 2010

1.0

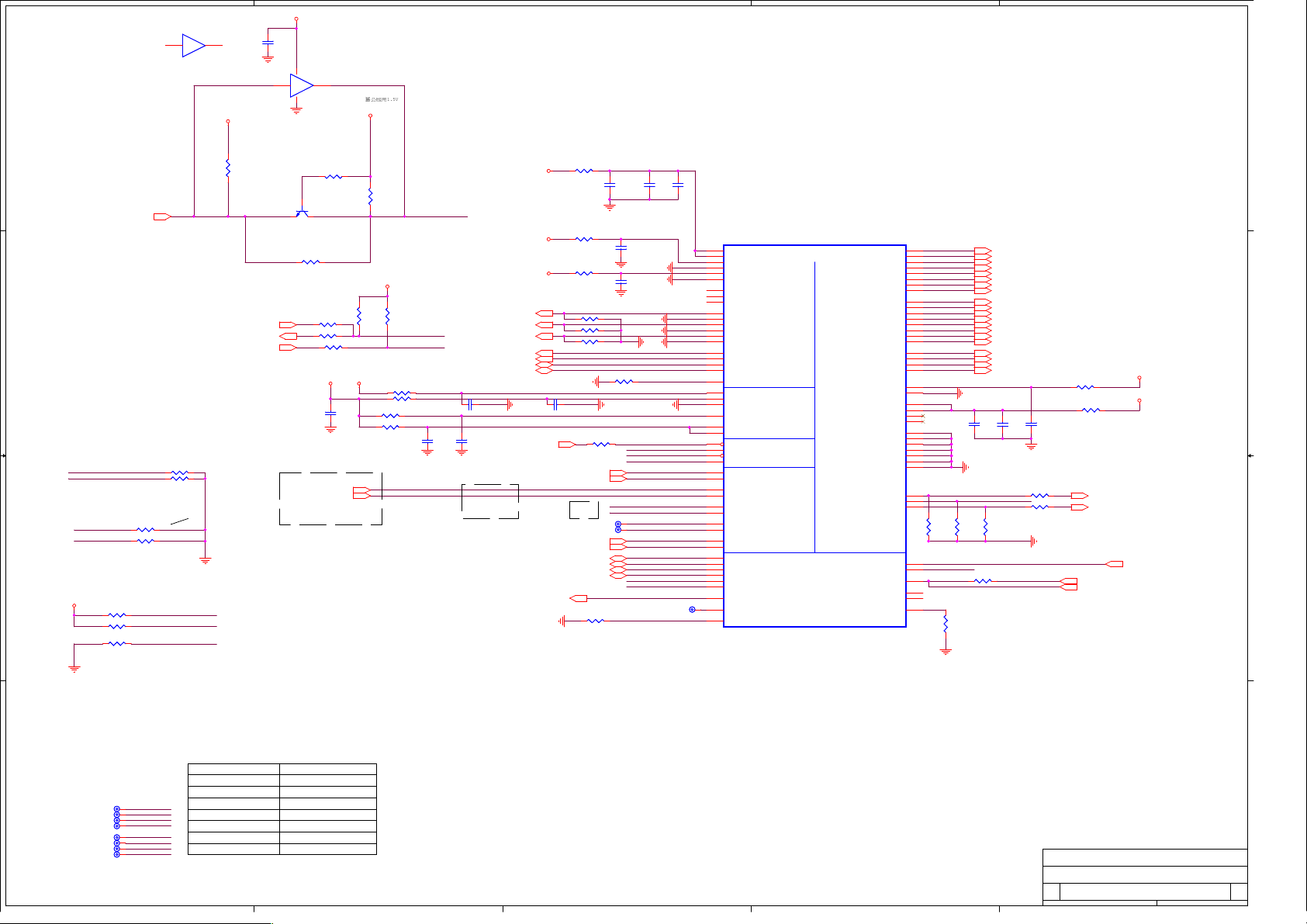

Page 3

5

4

3

2

1

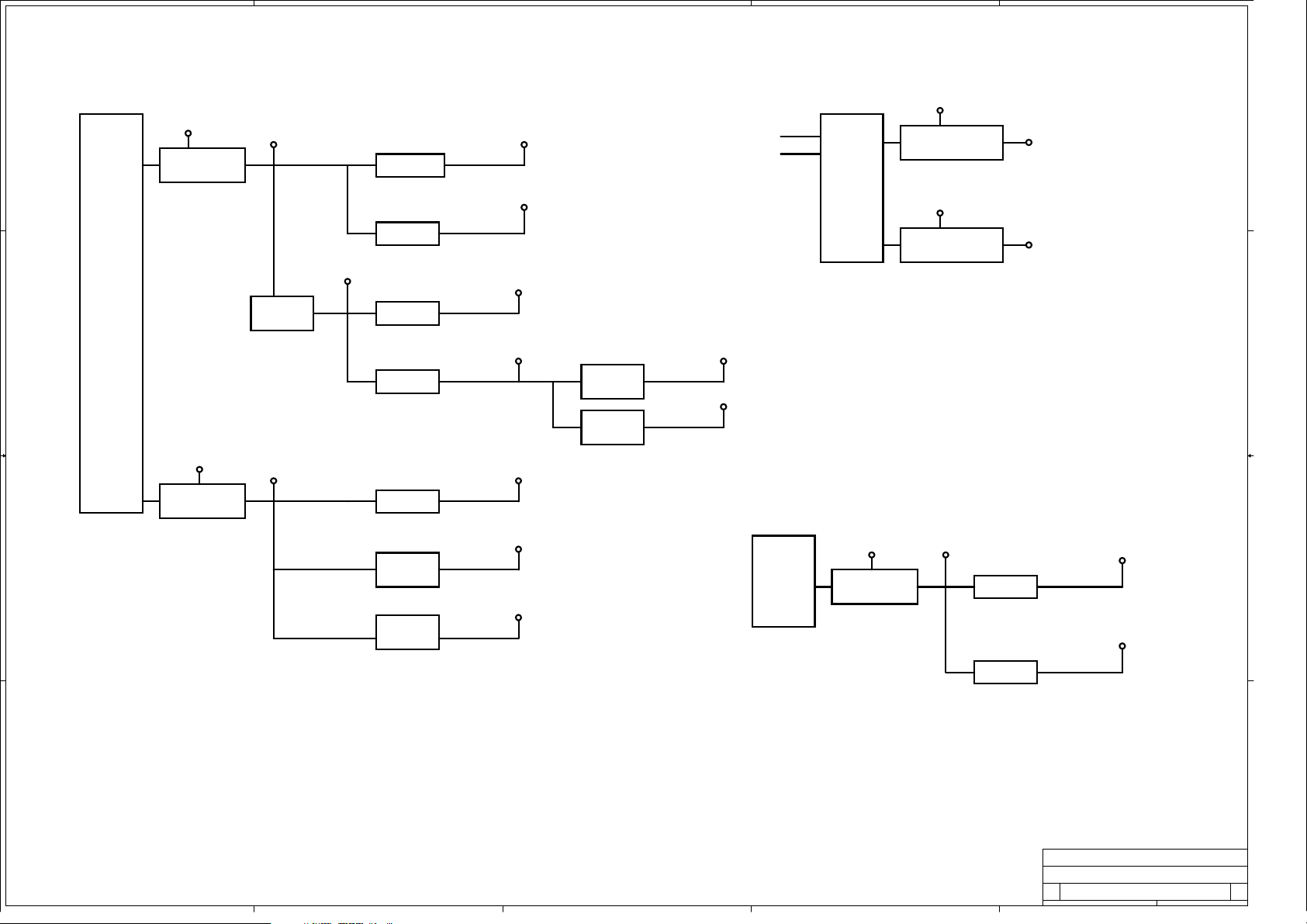

System Power On Sequence

EC Control Pin (O/P)

*

EC Control Pin(I/P)

**

VBAT

D D

Adaptor or Battery

+3VA / +5VA

PWRSW

+3.3VS_ON

*

+5VS

+3.3VS

+1.1VS_ON

*

+1.1VS

PM_RSMRST#

*

PWRBTN#

*

PM_SLP_S5#

*

*

+1.5VS_ON

*

+1.5VS

*

A

*

PM_SLP_S3#

*

+5V_ON

*

+1.8V_ON

*

+1.5V_ON

*

+1.5V

VCORE_ON

*

+CPU_CORE

+CPU_VDDNB

+CPU_VDDR

+1.1V_ON

*

+1.1V

+VCC_NB

SB_PWRGD

NB_PWRGD

*

KBRST#

LDT_STOP#

CPU_PWRGD

+0.75VS

+5V

+3.3V

+1.8V

+2.5V

C C

B

B B

A A

>5S

3.3VS_ON_HV

3.3VS_ON_HV

5V_ON_HV

5V_ON_HV

ALL POWER --> 50 µs < Power Rail Ramp time < 40 ms.

+3.3VALW_R ramp down time > 300 µs. 100 µs < Power Rail Ramp time < 40 ms.

10ms

10ms

+3.3VDUAL ramp before +1.1VDUAL , >10ms

RSMRST# not de-asserted until at least 10 ms after S5_3.3V is valid. ramp up time (10~90%) <50ms

10ms

50ms

20ms

3ms

+3.3V ramp before +1.8v

1ms

0 <(+3.3V) - (+1.8v) < 2.1

3ms

DDR2: VDDIO must never exceed VTT(CPU_VDDR) by greater than 1.1 V

5ms

IV CLK GEN OK about after 3ms

10ms

+1.1V ramp before VCC_NB

10ms

+1.8V ramp before +1.1v

TO SB PWR_GOOD rise time < 50 ms ,fall time < 1 ms

,de-asserted at least 80 ns before VDDCR_11 drops 5% from nominal value.

,de-asserted at least 1 ns before RSMRST# is asserted when entering G3 state.

,PCIE_CLKP/N present no later than 31 ms after SB PWR_GOOD is asserted

(-31 ms < PCIE_CLKP/N to SB PWR_GOOD delay < no maximum)

EC initial after SB_pwrgd 40ms

*EXT CLK 0~30ns

INT CLK40~42ms

(must after LPC clk ready)

SB TO NB NB_PWRGD HIGH to SB_PWRGD HIGH >-22 ms <500ms

14M, HT REFCLKP/N and PCI Express (PCIe) Clocks from CLKGEN to NB before NB_PWRGD > 1 ms.

5ms

KBRST# should be de-asserted before A_RST# (LDT_RST#) is de-asserted.

LDTSTOP_L must be de-asserted a minimum of 1 µs before the de-assertion of RESET_L

SB TO CPU Stable CPUCLK to CPU before LDT_PG/CPU_PWRGD HIGH ? 1 ms

NB_PWRGD to LDT_PG. 77~108ms

RESET_L must be asserted a minimum of 1 ms

prior to the assertion of PWROK(CPU_PWRGD)

CLKIN_H/L must be within specification a

minimum of 1 ms prior to the assertion of PWROK.

5

2

12

RTC

CLK

8A

3

PWRSW

+5VS

+3.3VS

SW

+3.3VA(APL1034)

+5VA

+1.5VS

+0.75V

PWM

1

Adpater

SB8XX

8

+3.3VA

VIN

LDT_PG

LDT_RST#

LDT_STP#

NB_PWRGD

PWR_GOOD

24

10

9

PWRBTN#

PM_RSMRST#

SB_PWRGD

PM_SLP_S5#, PM_SLP_S3#

IT8500BX

4

+3.3VS_ON

6

11

+1.1VS_ON

+1.1VS_ON

PWM

+1.1VS

7

SW

+5V

+3.3V

14

26

CPU_PWRGD

28

LDT_RST#

27

LDT_STOP#

NB_PWRGD

PWROK

RESET_L

LDTSTOP_L

S1G4_CPU

HT_CLK

25

POWERGOOD

RS880

27A

29

LPC_FRAME

17

19

VCORE_ON

CLK GEN

VCORE_PWRGD

PWM

+CPU_CORE

+CPU_VDDNB

VID

26A

+1.5V_ON

SW

15

13

18

+5V_ON

+1.5V

+1.8V_ON

20

LDO

LDO

21

20

SW

+CPU_VDDR

+1.1V

+VCC_NB

22

23

+1.8V

LDO

+2.5V

16

+1.1VON

16

A_RST#

PCIRST#

LDT_RST#

SB PWR_GOOD to PCIRST#. 101~113ms

Shuttle Inc

Shuttle Inc

>1us

PCIRST# to LDT_RST#. 1~2.3ms

RESET_L must remain asserted until the clocks

from the transmitters of all HyperTransport devices

5

4

are stable, and a minimum of 1 ms after PWROK

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Shuttle Inc

A14RM

A14RM

A14RM

POWER DIAGRAM & SEQUENCE

POWER DIAGRAM & SEQUENCE

POWER DIAGRAM & SEQUENCE

1

3 37Monday, October 18, 2010

3 37Monday, October 18, 2010

3 37Monday, October 18, 2010

1.0

1.0

1.0

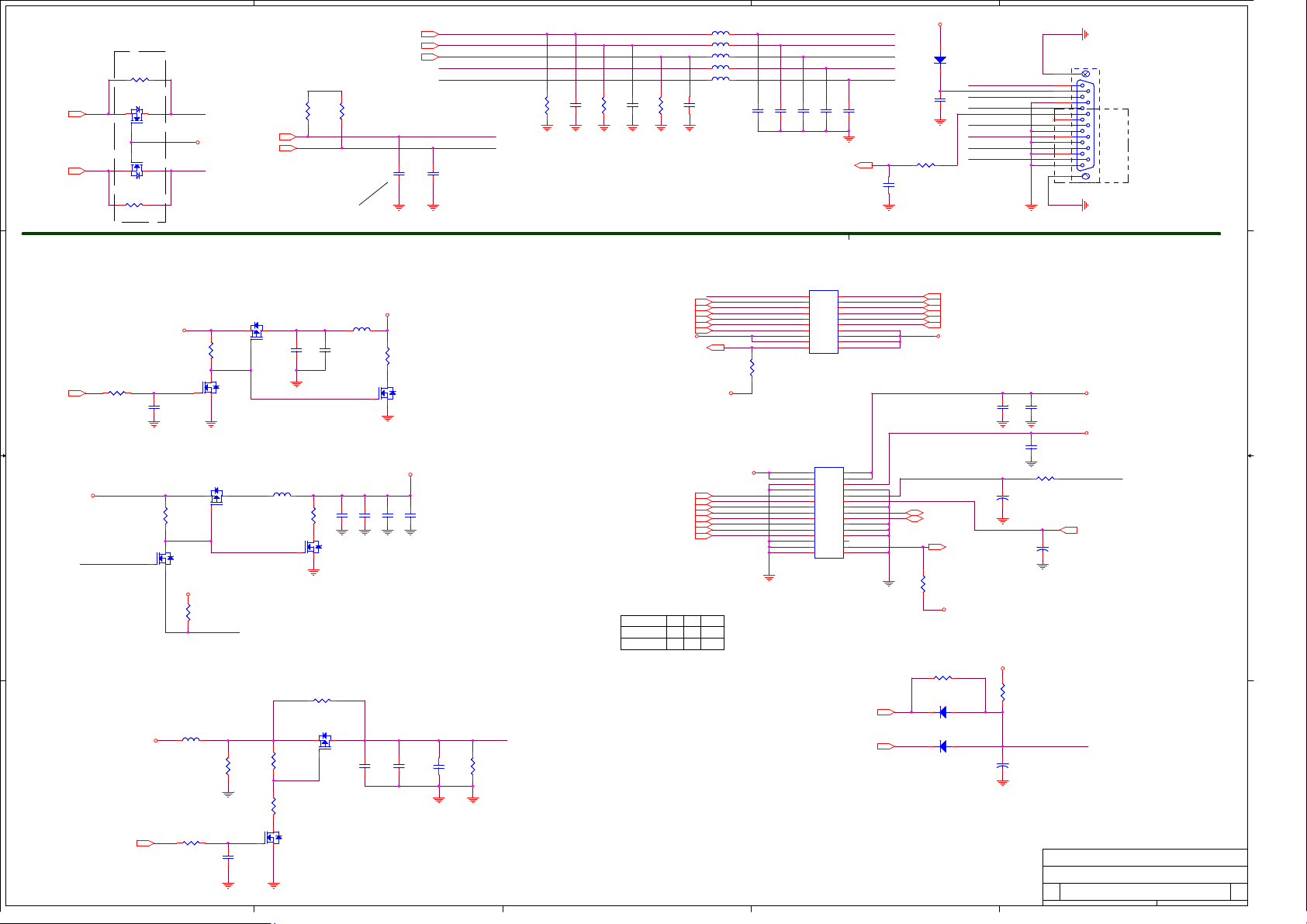

Page 4

5

4

3

2

1

POWER BLOCK DIAGRAM

VIN

D D

OZ815

VIN

AM4826

AM4828

+5VA

3G,AUDIO-D,EN-USB

+3VA

AM4826

AM4826

EC.Gsensor,BAT,SUSBAT

AUDIO-A,CRT,LVDS,HDMI,

+5V

SATA,TP,FAN,WEBCAM,Ctrl(Vcore VDDR)

+5VS

EX-USB, Ctrl (2.5 1.1 0.75 1.8 1.2)

CLOCK.CODEC,NB,SB,......

+3.3V

SVD

SVC

OZ8380

APM3009NU x2

APM3106NU x 3

VIN

AM4826

AM4828

35A

+CPU_CORE

4A

+CPU_VDDNB

LDO

APL1084

C C

AM4826

AM4826

+3.3VS

LAN,MDC,NB,SB,.....

LDO

OZ8033

+2.5V

+1.8V

LDO

OZ8033

VIN

AM4826

AM4828

B B

+1.5VS

SI2301

LDO

FP6137

G9330

+1.5V

+0.75VS

+CPU_VDDR

OZ8116

VIN

AM4826

AM4828

+1.1VS

+1.1V

AM4826

15A

+VCC_NB

AM4826

A A

Shuttle Inc

Shuttle Inc

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Shuttle Inc

A14RM

A14RM

A14RM

GPIO & Power Consumption

GPIO & Power Consumption

GPIO & Power Consumption

1

4 37Monday, October 18, 2010

4 37Monday, October 18, 2010

4 37Monday, October 18, 2010

1.0

1.0

1.0

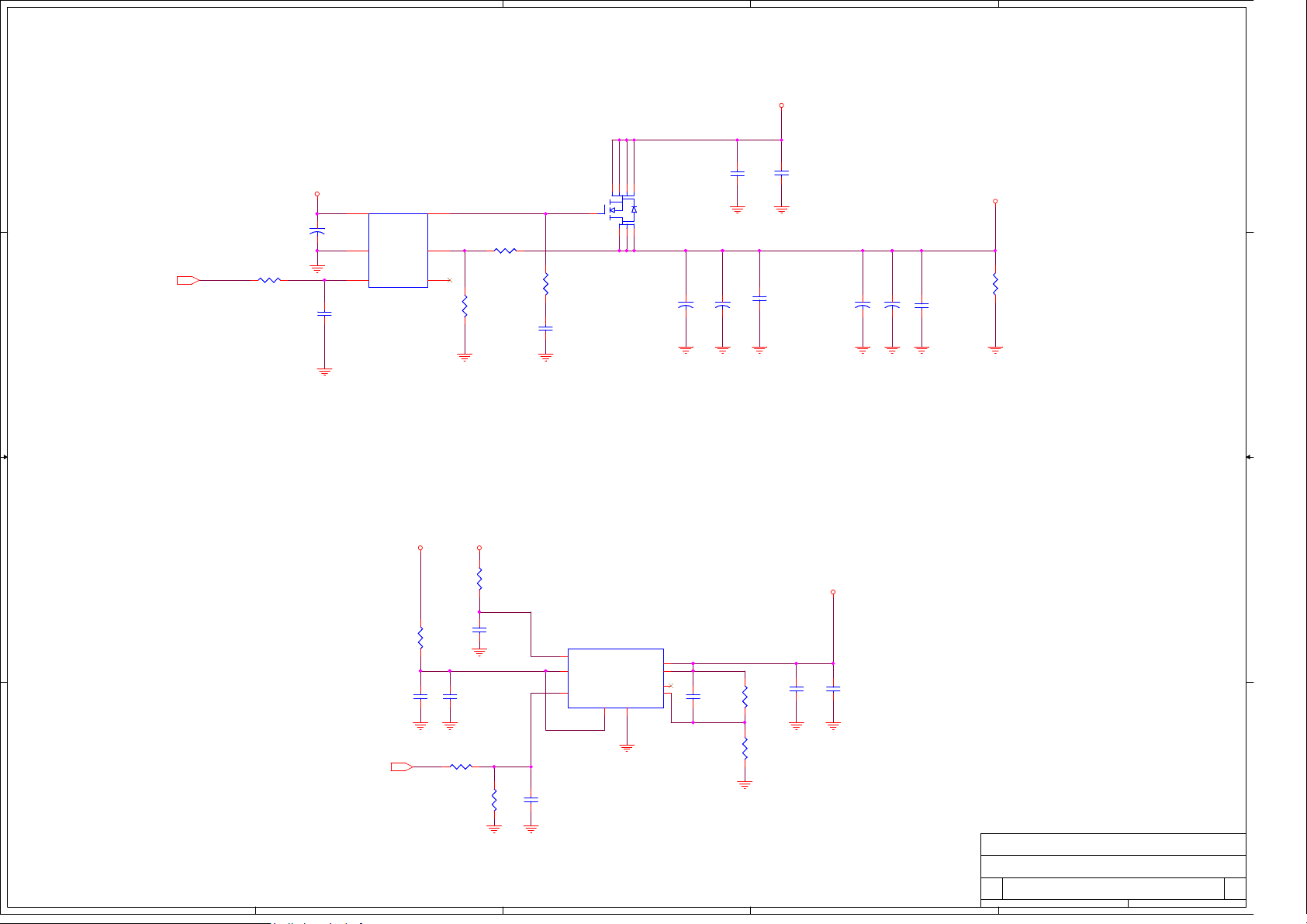

Page 5

5

D D

C C

4

3

2

1

MB_13

use internal clk gen

B B

A A

Shuttle Inc

Shuttle Inc

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Shuttle Inc

A14RM

A14RM

A14RM

CLOCK GEN (ICS9LRS365B)

CLOCK GEN (ICS9LRS365B)

CLOCK GEN (ICS9LRS365B)

1

5 37Monday, October 18, 2010

5 37Monday, October 18, 2010

5 37Monday, October 18, 2010

1.0

1.0

1.0

Page 6

5

4

3

2

1

D D

U6A

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

U6A

HT LINK

HT LINK

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

HT_CPU_NB_C AD_H0 12

HT_CPU_NB_C AD_L0 12

HT_CPU_NB_C AD_H1 12

HT_CPU_NB_C AD_L1 12

HT_CPU_NB_C AD_H2 12

HT_CPU_NB_C AD_L2 12

HT_CPU_NB_C AD_H3 12

HT_CPU_NB_C AD_L3 12

HT_CPU_NB_C AD_H4 12

HT_CPU_NB_C AD_L4 12

HT_CPU_NB_C AD_H5 12

HT_CPU_NB_C AD_L5 12

HT_CPU_NB_C AD_H6 12

HT_CPU_NB_C AD_L6 12

HT_CPU_NB_C AD_H7 12

HT_CPU_NB_C AD_L7 12

HT_CPU_NB_C AD_H8 12

HT_CPU_NB_C AD_L8 12

HT_CPU_NB_C AD_H9 12

HT_CPU_NB_C AD_L9 12

HT_CPU_NB_C AD_H10 12

HT_CPU_NB_C AD_L10 12

HT_CPU_NB_C AD_H11 12

HT_CPU_NB_C AD_L11 12

HT_CPU_NB_C AD_H12 12

HT_CPU_NB_C AD_L12 12

HT_CPU_NB_C AD_H13 12

HT_CPU_NB_C AD_L13 12

HT_CPU_NB_C AD_H14 12

HT_CPU_NB_C AD_L14 12

HT_CPU_NB_C AD_H15 12

HT_CPU_NB_C AD_L15 12

HT_CPU_NB_C LK_H0 12

HT_CPU_NB_C LK_L0 12

HT_CPU_NB_C LK_H1 12

HT_CPU_NB_C LK_L1 12

HT_CPU_NB_C TL_H0 12

HT_CPU_NB_C TL_L0 12

HT_CPU_NB_C TL_H1 12

HT_CPU_NB_C TL_L1 12

+VLDT +VLDT

AF5

AF4

AF6

AF7

AF8

AF17

AF18

AE17

AE18

AD17

AD18

AC18

AC17

AB17

AB18

AA18

AA17

Y18

Y17

W17

W18

V17

V18

U17

U18

T18

T17N6T12

R18

R17

P18

N17

N18

M18

M17

L18

L17

K17

K18

J17

J18

H18

H17

G17

G18

F18

F17

E18

E17

D18

D17

C17

C18

B18

B17

A18

AF9

AF15

AF14

AF16

AF11

AF13

AF10

AF12

AE5

AE9

AE8

AE4P8AE6

AE7

AE3

AC11

AA11

Y11

W11

V11

U11

T11

R11

P11K8P17

N11

M11

L11 AE11

K11

J11

H11

G11 AD11

F11

E11

D11

C11

B11 AB11

A11

C609

C609

AE2

AD6

AD7

AD2

AD5

AD4

AD8

AD9

AD3

AD1

AD10

AC5

AC3

AC6

AC7

AC8

AC2

AC1

AC9

AC4

AC10

AB3

AB4

AB5

AB6

AB9

AB2

AB8

AB1

AB7

AB10

AA3

AA4

AA5

AA1

AA8

AA9

AA6

AA2

AA7

Y1

Y3

Y10

Y2

Y9

Y5

Y6

Y4

W4W5W6

W8

W9

W1

W2

W10

V3D3

V1

V4

V6

V9

V5

V8

V7

V10

U7

U10

U9

U8N8

U5

U6

U4

U3

U1

T5T6T7

T10 AE10

T4

T1

T2

T8

T9

T3

R1

R2 V2

R8

R9

R5

R4

R3

R6

R10

R7

P10 AA10

P1

P5

P2

P3

P6

P4G4

P7

N2

N5

N4

N7

N9 P9

N10

N1

N3

M1

M4

M5

M6

M7

M2

M3

M10

L5

L6

L2

L3

L7

L10

L1

L8

L9

L4

K3

K4

K5

K10

K9

K7

K6

K1

K2

J10

J6

J8

J9

J7

H8

H6

H7

H10

H9

G9

G6

G10

F10

F8

F7

F6

F9

E7

E8E9E10

E6

D6

D8

D10

D9

C9

C10

C6

C7

C8

B9

B7

B6

B8

B10

A8

A7

A10

A9

10U-10-08Y-Z

10U-10-08Y-Z

BGA638_50_26SQ_S1G3_OEM

J3 W3

J5

J1

J2

J4

H2

H4

H1

H5

G1

G2

G5

G3

F5

F2

F4

F1

F3

E4

E1

E3

E2

E5

D1

D2

D5

D4

C2

C5

C4

C3

B3

B5

B4

A4C1A6

A3

A5

A1

C370

C370

C601

C598

C598

.1U-16-04Y-Z

.1U-16-04Y-Z

C601

330P-50-04X-K

330P-50-04X-K

10U-10-08Y-Z

10U-10-08Y-Z

C371

C371

.1U-16-04Y-Z

.1U-16-04Y-Z

C372

C372

.1U-16-04Y-Z

.1U-16-04Y-Z

HT_NB_CPU_C AD_H012

HT_NB_CPU_C AD_L012

HT_NB_CPU_C AD_H112

HT_NB_CPU_C AD_L112

HT_NB_CPU_C AD_H212

HT_NB_CPU_C AD_L212

HT_NB_CPU_C AD_H312

HT_NB_CPU_C AD_L312

HT_NB_CPU_C AD_H412

HT_NB_CPU_C AD_L412

HT_NB_CPU_C AD_H512

HT_NB_CPU_C AD_L512

HT_NB_CPU_C AD_H612

HT_NB_CPU_C AD_L612

HT_NB_CPU_C AD_H712

HT_NB_CPU_C AD_L712

HT_NB_CPU_C AD_H812

HT_NB_CPU_C AD_L812

HT_NB_CPU_C AD_H912

HT_NB_CPU_C AD_L912

HT_NB_CPU_C AD_H1012

HT_NB_CPU_C AD_L101 2

HT_NB_CPU_C AD_H1112

HT_NB_CPU_C AD_L111 2

HT_NB_CPU_C AD_H1212

HT_NB_CPU_C AD_L121 2

HT_NB_CPU_C AD_H1312

HT_NB_CPU_C AD_L131 2

HT_NB_CPU_C AD_H1412

HT_NB_CPU_C AD_L141 2

HT_NB_CPU_C AD_H1512

HT_NB_CPU_C AD_L151 2

HT_NB_CPU_C LK_H012

HT_NB_CPU_C LK_L012

HT_NB_CPU_C LK_H112

HT_NB_CPU_C LK_L112

HT_NB_CPU_C TL_H012

HT_NB_CPU_C TL_L012

HT_NB_CPU_C TL_H112

HT_NB_CPU_C TL_L112

AE16

AE12

AE13

AE14

AE15H15

AD12

AD13

AD14

AD15

AD16

AC14

AC13

AC15

AC16

AC12

AB12

AB13

AB16

AB14

AB15J15

AA12

AA13

AA16

AA15

AA14

Y12

Y14

Y15

Y13

Y16

W12

W13

W14

W15

W16

V12

V13

V15

V16

V14

U13

U14

U12

U15

U16

T13

T16

T14

T15

R16

P16

N16

M16

L16

L15

L13

L14

L12

K12

K16

K14

K15

K13

J14

J13

J16

J12

H14

H16

H12

H13

G14

G12

G13

G16

G15

F15

F12

F16

F13

F14

E12H3E14

E13

E16

E15

D12

D13

D14

D15

D16

C14

C12

C16

C15

C13

B15

B13

B16

B14

B12

A15D7A17

A12

A13

A14

A16

AF19T19

AF21

AF22

AF24

AF20

AF23

AE25

AE20

AE19

AE21

AE22

AE23

AE24

AD23

AD26

AD22M8AD24

AD25

AD19M9AD21

AD20

AC19

AC20

AC21

AC26

AC22

AC23

AC24

AC25

AB19W7AB21

AB22

AB24

AB25

AB26

AB23

AB20

AA19

AA20

AA23

AA22

AA21

AA25

AA26

AA24

Y26

Y19

Y20

Y24

Y25

Y23

Y21

Y22

W25

W26

W21

W22

W23

W24

V21

V22

V23P23

V24

V20

V19J19 P19

V26

V25

U19N19

U21

U22

U23

U24

U25

U26

U20

T20

T23

T22

T21

T24

T25

T26

R20

R23

R24

R25

R26

R19

R21

R22

P26

P24

P22

P21

P25

P20

N20

N22

N21U2N23

N24

N25

N26

M25

M23

M24

M20

M19

M26C26

M21

M22

L22

L24

L23

L26

L21

L25

L19

L20

K26

K20

K24

K19

K21

K22

K25

S1G4

K23

J26

J21

J20

J22

J23

J25

J24

H21

H22

H19

H23

H24

H25

H26

H20

G25

G24

G23

G26

G21

G22

F20

F24

F25

F19

F22

F23

F21

F26

E19

E20

E24

E21

E22

E25

E23

E26

D20

D22

D23

D21

D19

D26

D25

D24

C25

C23

C24

C20

C19

C21

C22

B21

B20

B25

B24

B23

B22

B19

A19

A20

A24

A21

A22

A23

C C

+VLDT+1.1V

MAX 1.5A

R430 0-08R430 0-08

C608

C608

10U-10-08Y-Z

10U-10-08Y-Z

B B

Place close to socket

con_cpu6 38_pz638 2a-284s-41 f_fox

con_cpu6 38_pz638 2a-284s-41 f_fox

A A

Shuttle Inc

Shuttle Inc

Shuttle Inc

Title

Title

Title

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

4

3

2

S1G4 HT

S1G4 HT

S1G4 HT

A14RM

A14RM

A14RM

1.0

1.0

6 37Monday, Octo ber 18, 20 10

6 37Monday, Octo ber 18, 20 10

6 37Monday, Octo ber 18, 20 10

1

1.0

Page 7

5

D D

4

3

2

1

Processor Memory Interface

U6C

+1.5VS

C C

B B

+1.5VS

C121

C121

2.2U-6.3-06R-K

2.2U-6.3-06R-K

R121

R121

0-04

0-04

R384

R384

1K-1-04

1K-1-04

R382

R382

1K-1-04

1K-1-04

PLACE THEM CLOSE TO

CPU WITHIN 1"

R123 39.2-1-04R123 39.2-1-04

R122 39.2-1-04R122 39.2-1-04

MEM_MA_RST#10

MEM_MA0_ODT010

MEM_MA0_ODT110

MEM_MA0_CS#010

MEM_MA0_CS#110

MEM_MA_CKE010

MEM_MA_CKE110

MEM_MA_CLK1_P10

MEM_MA_CLK1_N10

MEM_MA_CLK2_P10

MEM_MA_CLK2_N10

MEM_MA_ADD[0..15]10

MEM_MA_BANK010

MEM_MA_BANK110

MEM_MA_BANK210

MEM_MA_RAS#10

MEM_MA_CAS#10

MEM_MA_WE#10

C419

C419

.1U-16-04Y-Z

.1U-16-04Y-Z

C440

C440

.1U-16-04Y-Z

.1U-16-04Y-Z

CPU_M_VREF_SUS

C431

C431

.01U-25-04X-K

.01U-25-04X-K

+CPU_VDDR

TP54

TP54

TP58

TP58

TP56

TP56

TP55

TP55

TP64

TP64

TP63

TP63

TP66

TP66

TP65

TP65

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

M_ZP

M_ZN

TP

TP

TP

TP

TP

TP

TP

TP

TP

TP

TP

TP

TP

TP

TP

TP

U6B

U6B

D10

VDDR1

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

C10

VDDR2

B10

VDDR3

AD10

VDDR4

AF10

MEMZP

AE10

MEMZN

H16

MA_RESET_L

T19

MA0_ODT0

V22

MA0_ODT1

U21

MA1_ODT0

V19

MA1_ODT1

T20

MA0_CS_L 0

U19

MA0_CS_L 1

U20

MA1_CS_L 0

V20

MA1_CS_L 1

J22

MA_CKE0

J20

MA_CKE1

N19

MA_CLK_H 5

N20

MA_CLK_L 5

E16

MA_CLK_H 1

F16

MA_CLK_L 1

Y16

MA_CLK_H 7

AA16

MA_CLK_L 7

P19

MA_CLK_H 4

P20

MA_CLK_L 4

N21

MA_ADD0

M20

MA_ADD1

N22

MA_ADD2

M19

MA_ADD3

M22

MA_ADD4

L20

MA_ADD5

M24

MA_ADD6

L21

MA_ADD7

L19

MA_ADD8

K22

MA_ADD9

R21

MA_ADD10

L22

MA_ADD11

K20

MA_ADD12

V24

MA_ADD13

K24

MA_ADD14

K19

MA_ADD15

R20

MA_BANK0

R23

MA_BANK1

J21

MA_BANK2

R19

MA_RAS_L

T22

MA_CAS_L

T24

MA_WE_ L

con_cpu638_pz6382a-284s-41f_fox

con_cpu638_pz6382a-284s-41f_fox

VDDR5

VDDR6

VDDR7

VDDR8

VDDR9

VDDR_SENS E

MEMVREF

MB_RESET_L

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L 0

MB0_CS_L 1

MB1_CS_L 0

MB_CKE0

MB_CKE1

MB_CLK_H 5

MB_CLK_L 5

MB_CLK_H 1

MB_CLK_L 1

MB_CLK_H 7

MB_CLK_L 7

MB_CLK_H 4

MB_CLK_L 4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_ L

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

+CPU_VDDR

TP69

TP69

TP

TP

TP28

TP28

TP

TP

TP53

TP53

TP

TP

TP57

TP57

TP60

TP60

TP

TP

TP59

TP59

TP

TP

TP61

TP61

TP

TP

TP

TP

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

FOR +CPU_VDDR

CPU_M_VREF_SUS

MEM_MB_RST# 10

MEM_MB0_ODT0 10

MEM_MB0_ODT1 10

MEM_MB0_CS#0 10

MEM_MB0_CS#1 10

MEM_MB_CKE0 10

MEM_MB_CKE1 10

MEM_MB_CLK1_P 10

MEM_MB_CLK1_N 10

MEM_MB_CLK2_P 10

MEM_MB_CLK2_N 10

MEM_MB_ADD[0..15] 10

MEM_MB_BANK0 10

MEM_MB_BANK1 10

MEM_MB_BANK2 10

MEM_MB_RAS# 10

MEM_MB_CAS# 10

MEM_MB_WE# 10

TP62TP62

PLACE CLOSE TO CPU

+CPU_VDDR

C369

C369

@4.7U-10-08Y-Z

@4.7U-10-08Y-Z

C379

C379

C428

C428

2.2U-6.3-06R-K

2.2U-6.3-06R-K

10U-10-08Y-Z

10U-10-08Y-Z

Place close to socket

C395

C395

C401

C401

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C383

C383

C599

C435

C435

C393

C393

1000P-50-04X-K

1000P-50-04X-K

.1U-16-04Y-Z

.1U-16-04Y-Z

C599

C406

C406

220P-50-04X-K1

.1U-16-04Y-Z

.1U-16-04Y-Z

220P-50-04X-K1

.1U-16-04Y-Z

.1U-16-04Y-Z

C418

C418

C410

C410

220P-50-04X-K1

220P-50-04X-K1

220P-50-04X-K1

220P-50-04X-K1

MEM_MB_DATA[0..63]10

MEM_MB_DM[0..7]10

MEM_MB_DQS0_P10

MEM_MB_DQS0_N10

MEM_MB_DQS1_P10

MEM_MB_DQS1_N10

MEM_MB_DQS2_P10

MEM_MB_DQS2_N10

MEM_MB_DQS3_P10

MEM_MB_DQS3_N10

MEM_MB_DQS4_P10

MEM_MB_DQS4_N10

MEM_MB_DQS5_P10

MEM_MB_DQS5_N10

MEM_MB_DQS6_P10

MEM_MB_DQS6_N10

MEM_MB_DQS7_P10

MEM_MB_DQS7_N10

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

U6C

C11

MB_DATA0

A11

MB_DATA1

A14

MB_DATA2

B14

MB_DATA3

G11

MB_DATA4

E11

MB_DATA5

D12

MB_DATA6

A13

MB_DATA7

A15

MB_DATA8

A16

MB_DATA9

A19

MB_DATA10

A20

MB_DATA11

C14

MB_DATA12

D14

MB_DATA13

C18

MB_DATA14

D18

MB_DATA15

D20

MB_DATA16

A21

MB_DATA17

D24

MB_DATA18

C25

MB_DATA19

B20

MB_DATA20

C20

MB_DATA21

B24

MB_DATA22

C24

MB_DATA23

E23

MB_DATA24

E24

MB_DATA25

G25

MB_DATA26

G26

MB_DATA27

C26

MB_DATA28

D26

MB_DATA29

G23

MB_DATA30

G24

MB_DATA31

AA24

MB_DATA32

AA23

MB_DATA33

AD24

MB_DATA34

AE24

MB_DATA35

AA26

MB_DATA36

AA25

MB_DATA37

AD26

MB_DATA38

AE25

MB_DATA39

AC22

MB_DATA40

AD22

MB_DATA41

AE20

MB_DATA42

AF20

MB_DATA43

AF24

MB_DATA44

AF23

MB_DATA45

AC20

MB_DATA46

AD20

MB_DATA47

AD18

MB_DATA48

AE18

MB_DATA49

AC14

MB_DATA50

AD14

MB_DATA51

AF19

MB_DATA52

AC18

MB_DATA53

AF16

MB_DATA54

AF15

MB_DATA55

AF13

MB_DATA56

AC12

MB_DATA57

AB11

MB_DATA58

Y11

MB_DATA59

AE14

MB_DATA60

AF14

MB_DATA61

AF11

MB_DATA62

AD11

MB_DATA63

A12

MB_DM0

B16

MB_DM1

A22

MB_DM2

E25

MB_DM3

AB26

MB_DM4

AE22

MB_DM5

AC16

MB_DM6

AD12

MB_DM7

C12

MB_DQS_H 0

B12

MB_DQS_L 0

D16

MB_DQS_H 1

C16

MB_DQS_L 1

A24

MB_DQS_H 2

A23

MB_DQS_L 2

F26

MB_DQS_H 3

E26

MB_DQS_L 3

AC25

MB_DQS_H 4

AC26

MB_DQS_L 4

AF21

MB_DQS_H 5

AF22

MB_DQS_L 5

AE16

MB_DQS_H 6

AD16

MB_DQS_L 6

AF12

MB_DQS_H 7

AE12

MB_DQS_L 7

con_cpu638_pz6382a-284s-41f_fox

con_cpu638_pz6382a-284s-41f_fox

MEM:DATA

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H 0

MA_DQS_L 0

MA_DQS_H 1

MA_DQS_L 1

MA_DQS_H 2

MA_DQS_L 2

MA_DQS_H 3

MA_DQS_L 3

MA_DQS_H 4

MA_DQS_L 4

MA_DQS_H 5

MA_DQS_L 5

MA_DQS_H 6

MA_DQS_L 6

MA_DQS_H 7

MA_DQS_L 7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DATA[0..63] 10

MEM_MA_DM[0..7] 10

MEM_MA_DQS0_P 10

MEM_MA_DQS0_N 10

MEM_MA_DQS1_P 10

MEM_MA_DQS1_N 10

MEM_MA_DQS2_P 10

MEM_MA_DQS2_N 10

MEM_MA_DQS3_P 10

MEM_MA_DQS3_N 10

MEM_MA_DQS4_P 10

MEM_MA_DQS4_N 10

MEM_MA_DQS5_P 10

MEM_MA_DQS5_N 10

MEM_MA_DQS6_P 10

MEM_MA_DQS6_N 10

MEM_MA_DQS7_P 10

MEM_MA_DQS7_N 10

A A

C629

C629

10U-10-08Y-Z

10U-10-08Y-Z

5

C615

C615

C610

C610

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C623

C623

C619

C619

220P-50-04X-K1

220P-50-04X-K1

1000P-50-04X-K

1000P-50-04X-K

C600

C600

C633

C633

2.2U-6.3-06R-K

2.2U-6.3-06R-K

2.2U-6.3-06R-K

2.2U-6.3-06R-K

Shuttle Inc

Shuttle Inc

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Shuttle Inc

S1G4 DDR

S1G4 DDR

S1G4 DDR

A14RM

A14RM

A14RM

1

1.0

1.0

7 37Monday, Oct ober 18, 2010

7 37Monday, Oct ober 18, 2010

7 37Monday, Oct ober 18, 2010

1.0

Page 8

5

4

3

2

1

LAYOUT: ROUTE VDDA TRACE APPROX.

BEAD 600MA 0603?

+2.5V

D D

R444 0-06R444 0-06

C634

C634

220P-50-04X-K1

220P-50-04X-K1

Actually install a 2-pin head for this location

Keep net PWRGD, LDT_STOP#, LDT_RST# no stub

+1.5V

R141

R141

300-04

300-04

CPU_PWRGD_IN

CPU_PWRGD17

C C

B B

CPU_LDT_STOP#14,17

H_RCIN#18,29

form SB

CPU_LDT_RST#17

CPU_LDT_REQ#14

R138 0-04R138 0-04

+1.5V

R446

R446

300-04

300-04

R445 0-04R445 0-04

R427

R427

@0-04

@0-04

LDT_STOP#

C576

C576

@100N-04

@100N-04

C639

C639

@100N-04

@100N-04

+1.5V

+1.5V

R466

R466

@2.2K-04

@2.2K-04

B

EC

Q63 @2N3904Q63 @2N3904

R367

R367

@100K-04

@100K-04

SMBCLK_EC_1 H_THRMDA

SMBDAT_EC_1

R426

R426

@0-04

@0-04

7

8

ALERT# THERMDC

6

@ADM1032

@ADM1032

+3.3VS

Q62 2N3904Q62 2N3904

HI voltage level control

(3.3 ->1.5)

R143

R143

@300-04

@300-04

CPU_LDT_REQ#_CPU

VDD_7421

12

@2.2U-6.3-06R-K

@2.2U-6.3-06R-K

1

U18

U18

VDD

ADATA

D+

SCLK

THERM#

ALERT

D-

GND

5

+3.3VS

B

E C

C412

C412

2

4

3

R441

R441

2.2K-04

2.2K-04

THERMDA

R135 @0-04R135 @0-04

MLP_3

2.2K-04

2.2K-04

2.2K-04

R436

R436

R435

R435

4.7K-04

4.7K-04

4.7K-04

A A

SMBCLK_EC25,29

SMBDAT_EC25,29

5

4.7K-04

2.2K-04

R463

R463

B

D20 CD4148WSPD20 CD4148WSP

EC

Q61 2N3904Q61 2N3904

AC

D21 CD4148W SPD21 CD4148WSP

B

Q60 2N3904Q60 2N3904

R460

R460

EC

AC

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

C575

C575

C617

C617

2.2U-6.3-06R-K

2.2U-6.3-06R-K

C403

C403

@3300P-50-04X-K

@3300P-50-04X-K

+1.5VS

C580

C580

.1U-16-04Y-Z

.1U-16-04Y-Z

+1.5V

R132 0-04R132 0-04

R375@68-06 R375@68-06

12

H_THRMDC

1K-04

1K-04

1K-04

1K-04

R464

R464

R129

R129

4

10n-50-04X-K

10n-50-04X-K

CLK_BUF_BCLK_P17

CLK_BUF_BCLK_N17

place them to CPU within 1.5"

R133

R133

300-04

300-04

Keep net CPU_LDT_RST# no stub

LDT_RST#

C130

C130

@180p-04

@180p-04

WARM BOOT

+3.3VS

TSI

1K-04

1K-04

R461

R461

CPU_SIC

CPU_SID

CPU_ALERT

R462 @0-04R462 @0-04

R465 @0-04R465 @0-04

Keep trace from resisor to CPU within 0.6"

keep trace from cap s to CPU within 1.2"

C126 3900P-50-04X-KC126 3900P-50-04X-K

C127 3900P-50-04X-KC127 3900P-50-04X-K

+VLDT

FOR VCORE PWM

+1.5VS

R457

R457

510-04

510-04

R456

R456

510-04

510-04

R142

R142

1K-04

1K-04

CPU_SVC_R

CPU_SVD_R

CPU_PWRGD_IN

SCLK3 18

SDATA3 18

R128

R128

169-1-04

169-1-04

R393 44.2-1-04R393 44.2-1-04

R396 44.2-1-04R396 44.2-1-04

R149

R149

0-04

0-04

+1.5V

R147

R147

1K-04

1K-04

3

CPU_VDDA_RUN

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

LDT_RST#

CPU_PWRGD_IN

LDT_STOP#

CPU_LDT_REQ#_CPU

CPU_SIC

CPU_SID

CPU_ALERT

CPU_VDD0_RUN_FB_H33

CPU_VDD0_RUN_FB_L33

CPU_DBRDY

TP67TP67

CPU_TMS

TP76TP76

CPU_TCK

TP70TP70

CPU_TRST#

TP75TP75

CPU_TDI

TP74TP74

CPU_TEST23_TSTUPD

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST27_SINGLECHAIN

CPU_TEST9_ANALOGIN

CPU_TEST6_DIECRACKMON

TP87TP87

R131 1K-04R131 1K-04

R140 0-04R140 0-04

R148 0-04R148 0-04

R136 0-04R136 0-04

1 2

1 2

1 2

1 2

CPU_HTREF0

CPU_HTREF1

TP91TP91

TP90TP90

U6D

U6D

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

C6

LDTREQ_L

AF4

SIC

AF5

SID

AE6

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_ H

E6

VDD0_FB_ L

Y6

VDD1_FB_ H

AB6

VDD1_FB_ L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

AD7

TEST23

H10

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

AB8

TEST21

AF7

TEST20

AE7

TEST24

AE8

TEST22

AC8

TEST12

AF8

TEST27

C2

TEST9

AA6

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

con_cpu638_pz6382a-284s-41f_fox

con_cpu638_pz6382a-284s-41f_fox

+VLDT is latter then Vcore

+VLDT

12

R361

R361

100K-04

100K-04

Z0515CPU_THERMTRIP#_VDDIO

Q45

Q45

B

2N3904

2N3904

C284

C284

E C

.1U-16-04Y-Z

.1U-16-04Y-Z

M11

VSS

W18

RSVD11

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_ H

VDDIO_FB_ L

VDDNB_FB_ H

VDDNB_FB_ L

DBREQ_L

TEST28_H

TEST28_L

TEST29_H

TEST29_L

RSVD10

C279

C279

1U-10-06Y-Z

1U-10-06Y-Z

SVD

SVC

0 0 1.1 1.1

0 1 1.0 1.2

1 0 0.9 1.0

1 1 0.8 0.8

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

RSVD9

RSVD8

RSVD7

RSVD6

SVC

SVD

TDO

CPU_SVC_R

A6

CPU_SVD_R

A4

CPU_THERMTRIP#_VDDIO

AF6

PROCHOT#_VDDIO

AC7

CPU_MEMHOT#_VDDIO

AA8

CPU_THERMDC

W7

CPU_THERMDA

W8

CPU_VDDIO_SUS_FB_H

W9

Y9

H6

G6

CPU_DBREQ#

E10

CPU_TDO

AE9

CPU_TEST28_H_PLLCHRZ_P

J7

CPU_TEST28_L_PLLCHRZ_N

H8

CPU_TEST17_BP3

D7

CPU_TEST16_BP2

E7

CPU_TEST15_BP1

F7

CPU_TEST14_BP0

C7

CPU_TEST7_ANALOG_T

C3

CPU_TEST10_ANALOGOUT

K8

CPU_TEST8_DIG_T

C4

CPU_TEST29_H_FBCLKOUT_P

C9

C8

Route as 80ohm, diff

H18

H19

AA7

CPU_TEST29_L_FBCLKOUT_N

D5

C5

AUX_OFF 35

CPU_SVC 33

CPU_SVD 33

CPU_PWRGD_SVID_REG 33

BOOT VOLTAGE(VDD)

(CPUVRM_PRO#

(CPUVRM_PRO#

= VCC/GND)

= OPEN)

VID OVERIDE TABLE (VDD)

2

+1.5VS

R360

R360

R364

R364

1K-04

1K-04

300-04

300-04

125* shutdoown

VIL=0.34*1.5=0.51

TP82TP82

R381 @0-04R381 @0-04

R380 @0-04R380 @0-04

TP71TP71

TP89TP89

TP88TP88

TP86TP86

TP80TP80

TP81TP81

TP85TP85

TP93TP93

TP83TP83

TP92TP92

Asserted as an input to force the processor into the HTC-active state

S1G4 does not support MEMHOT_L

TP77TP77

TP78TP78

H_THRMDC

H_THRMDA

CPU_VDDNB_RUN_FB_H 33

CPU_VDDNB_RUN_FB_L 33

TP79TP79

route as differential

TP84TP84

as short as possible

testpoint under package

TEST 15/14 300-04 TO GND FOR TEST

TP73TP73

R425

R425

80.6-1-04

80.6-1-04

TP72TP72

CPU_DBREQ#

CPU_TEST27_SINGLECHAIN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST23_TSTUPD

C, D internal ONLY

A, B is installed ONLY when SCAN is enabled

E is TBD

R458 300-04R458 300-04

R125 1K-04R125 1K-04

R124 @300-04R124 @300-04

R374 1K-04R374 1K-04

R126 1K-04R126 1K-04

R127 1K-04R127 1K-04

R351 1K-04R351 1K-04

R363 1K-04R363 1K-04

R408 1K-04R408 1K-04

R412 1K-04R412 1K-04

R362 1K-04R362 1K-04

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet

R134

R134

10K-04

10K-04

B

low level control (1.5->3.3v)

E C

Q55 2N3904Q55 2N3904

R453 0-04R453 0-04

A C

D22

D22

@CD4148WSP

DS

MB_25

Q72

Q72

G

2N7002K

2N7002K

+1.5VS

A

D

B

E

CN28

CN28

HDT

for debug

KEY

KEY

@ASP-68200-07

@ASP-68200-07

Shuttle Inc

Shuttle Inc

Shuttle Inc

A14RM

A14RM

A14RM

1

@CD4148WSP

C396

C396

.1U-16-04Y-Z

.1U-16-04Y-Z

AMD:1K

1

3

5

7

9

11

13

15

17

19

21

23

S1G4 CTRL DEBUG

S1G4 CTRL DEBUG

S1G4 CTRL DEBUG

CPU_THERMTRIP# 18

CPU_PROCHOT#_VDDIO 17

HI voltage level control

(1.5<-3.3)

2

4

6

8

10

12

14

16

18

20

22

24

26

8 37Monday, October 18, 2010

8 37Monday, October 18, 2010

8 37Monday, October 18, 2010

EC_PROCHOT# 29

of

1.0

1.0

1.0

Page 9

5

4

3

2

1

BOTTOM SIDE DECOUPLING

+CPU_CORE

C451

C451

C398

C398

C563

@10U-10-08Y-Z

D D

U6F

U6F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

+CPU_CORE

C C

+CPU_VDDNB

+1.5VS

B B

U6E

U6E

G4

VDD_1

H2

VDD_2

J9

VDD_3

J11

VDD_4

J13

VDD_5

J15

VDD_6

K6

VDD_7

K10

VDD_8

K12

VDD_9

K14

VDD_10

L4

VDD_11

L7

VDD_12

L9

VDD_13

L11

VDD_14

L13

VDD_15

L15

VDD_16

M2

VDD_17

M6

VDD_18

M8

VDD_19

M10

VDD_20

N7

VDD_21

N9

VDD_22

N11

VDD_23

K16

VDDNB_1

M16

VDDNB_2

P16

VDDNB_3

T16

VDDNB_4

V16

VDDNB_5

H25

VDDIO1

J17

VDDIO2

K18

VDDIO3

K21

VDDIO4

K23

VDDIO5

K25

VDDIO6

L17

VDDIO7

M18

VDDIO8

M21

VDDIO9

M23

VDDIO10

M25

VDDIO11

N17

VDDIO12

con_cpu638_pz6382a-284s-41f_fox

con_cpu638_pz6382a-284s-41f_fox

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

+CPU_CORE

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

+1.5VS

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

con_cpu638_pz6382a-284s-41f_fox

con_cpu638_pz6382a-284s-41f_fox

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

@10U-10-08Y-Z

C493

C493

.1U-16-04Y-Z

.1U-16-04Y-Z

C552

C552

330P-50-04X-K

330P-50-04X-K

+CPU_VDDNB

C364

C364

C457

C457

10U-10-08Y-Z

10U-10-08Y-Z

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.5VS

C571

C571

C433

C433

10U-10-08Y-Z

10U-10-08Y-Z

C563

4.7U-10-08Y-Z

4.7U-10-08Y-Z

C442

C442

C558

C558

C484

C484

C559

C559

10U-10-08Y-Z

10U-10-08Y-Z

10U-10-08Y-Z

10U-10-08Y-Z

10n-50-04X-K

10n-50-04X-K

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C438

C438

C512

C512

@330P-50-04X-K

@330P-50-04X-K

@330P-50-04X-K

@330P-50-04X-K

330P-50-04X-K

330P-50-04X-K

C479

C479

.1U-16-04Y-Z

.1U-16-04Y-Z

C522

C522

10U-10-08Y-Z

10U-10-08Y-Z

C458

C458

C542

C542

10U-10-08Y-Z

10U-10-08Y-Z

10U-10-08Y-Z

10U-10-08Y-Z

C566

C566

.1U-16-04Y-Z

.1U-16-04Y-Z

C550

C550

330P-50-04X-K

330P-50-04X-K

C567

C567

.1U-16-04Y-Z

.1U-16-04Y-Z

C450

C450

10U-10-08Y-Z

10U-10-08Y-Z

10U-10-08Y-Z

10U-10-08Y-Z

C557

C557

C565

C565

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C551

C551

C590

C590

330P-50-04X-K

330P-50-04X-K

@330P-50-04X-K

@330P-50-04X-K

C538

C538

330P-50-04X-K

330P-50-04X-K

C481

C481

C487

C487

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C528

C528

C509

C509

10U-10-08Y-Z

10U-10-08Y-Z

C444

C444

@.1U-16-04Y-Z

@.1U-16-04Y-Z

C595

C595

C449

C449

@330P-50-04X-K

@330P-50-04X-K

@330P-50-04X-K

@330P-50-04X-K

C500

C500

.1U-16-04Y-Z

.1U-16-04Y-Z

C507

C507

10U-10-08Y-Z

10U-10-08Y-Z

10U-10-08Y-Z

10U-10-08Y-Z

C501

C494

C511

C511

C469

C469

C520

C520

C539

C539

.1U-16-04Y-Z

.1U-16-04Y-Z

10n-50-04X-K

10n-50-04X-K

@10n-50-04X-K

@10n-50-04X-K

.1U-16-04Y-Z

.1U-16-04Y-Z

C585

C585

C430

C430

330P-50-04X-K

330P-50-04X-K

.1U-16-04Y-Z

.1U-16-04Y-Z

C564

C564

C540

C540

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C494

C414

C414

330P-50-04X-K

330P-50-04X-K

.1U-16-04Y-Z

.1U-16-04Y-Z

C594

C594

C583

C583

C524

C524

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C579

C579

330P-50-04X-K

330P-50-04X-K

C501

C446

C446

.1U-16-04Y-Z

.1U-16-04Y-Z

330P-50-04X-K

330P-50-04X-K

C537

C537

.1U-16-04Y-Z

.1U-16-04Y-Z

C574

C587

C587

330P-50-04X-K

330P-50-04X-K

C574

C472

C472

.1U-16-04Y-Z

.1U-16-04Y-Z

330P-50-04X-K

330P-50-04X-K

C514

C514

C463

C463

C386

C386

10n-50-04X-K

10n-50-04X-K

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C510

C510

C471

C471

.1U-16-04Y-Z

.1U-16-04Y-Z

330P-50-04X-K

330P-50-04X-K

C466

C466

C476

C476

2.2U-6.3-06R-K

2.2U-6.3-06R-K

2.2U-6.3-06R-K

2.2U-6.3-06R-K

A A

Shuttle Inc

Shuttle Inc

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Shuttle Inc

A14RM

A14RM

A14RM

S1G4 PWR

S1G4 PWR

S1G4 PWR

1.0

1.0

9 37Monday, October 18, 2010

9 37Monday, October 18, 2010

1

9 37Monday, October 18, 2010

1.0

Page 10

VDD

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC

NC

155

CN6

CN6

VSS

156

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

161

162

167

168

172

173

178

179

184

S1

S2

VSS

1

H8 reverse

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA15

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA11

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA28

MEM_MB_DATA24

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA29

MEM_MB_DATA25

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA45

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA40

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA50

MEM_MB_DATA55

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA54

MEM_MB_DATA51

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA[0..63] 7

FOR EMI

MLP_8

2

+3.3V

C322

C322

.1U-16-04Y-Z

.1U-16-04Y-Z

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD3

MEM_MB_ADD5

MEM_MB_ADD2

MEM_MB_ADD4

MEM_MB_ADD7

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD6

MEM_MB_ADD10

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_ADD13

107

83

84

85

89

86

90

91

92

96

97

98

95

A9

A8

A7

A6

A5

A4

A2

A1

A0

A3

125

NC/TEST

30

RESET#

126

VREF_CA

198

TS#

77

NC1

122

NC2

197

SA0

201

SA1

200

SDA

202

SCL

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

113

WE#

115

CAS#

110

RAS#

73

CKE0

74

CKE1

101

CK0

102

CK1

103

CK#0

104

CK#1

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

116

ODT0

120

ODT1

1

VREF_DQ

203

VTT

204

VTT

185

VSS

189

VSS

190

VSS

195

VSS

196

VSS

VSS

VSS

2

3

A11

A10/AP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

9

8

31

26

25

20

19

14

13

75

119

78

80

76

81

82

87

88

199

A13

A14

A12

NC/A15

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

44

43

38

37

32

93

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

71

66

65

61

60

54

49

55

48

+1.5VS

124

123

118

117

112

111

106

105

100

99

94

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

72

127

VSS

144

128

139

138

134

133

145

151

150

FOR EMI

3

MEM_MA_DATA[0..63] 7

MEM_MB_ADD[0..15]7

DDR_VREF1

C385

C385

C391

C391

1U-10-06Y-Z

1U-10-06Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

MEM_MB_RST#7

R314 10K-04R314 10K-04

MEM_MB_CLK1_P7

MEM_MB_CLK2_P7

MEM_MB_CLK1_N7

MEM_MB_CLK2_N7

MEM_MB_DQS0_P7

MEM_MB_DQS1_P7

MEM_MB_DQS2_P7

MEM_MB_DQS3_P7

MEM_MB_DQS4_P7

MEM_MB_DQS5_P7

MEM_MB_DQS6_P7

MEM_MB_DQS7_P7

MEM_MB_DQS0_N7

MEM_MB_DQS1_N7

MEM_MB_DQS2_N7

MEM_MB_DQS3_N7

MEM_MB_DQS4_N7

MEM_MB_DQS5_N7

MEM_MB_DQS6_N7

MEM_MB_DQS7_N7

+0.75VS

MEM_MB0_CS#07

MEM_MB0_CS#17

MEM_MB_WE#7

MEM_MB_CAS#7

MEM_MB_RAS#7

MEM_MB_CKE07

MEM_MB_CKE17

MEM_MB0_ODT07

MEM_MB0_ODT17

1 2

R315 10K-04R315 10K-04

1 2

SDATA0

SCLK0

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

DDR_VREF0

C655

C655

.1U-16-04Y-Z

.1U-16-04Y-Z

CON_DDR3_R80_RK-20401-TP8D

CON_DDR3_R80_RK-20401-TP8D

CON_DDR3_R80_RK-20401-TP8D

CON_DDR3_R80_RK-20401-TP8D

+3.3V

MEM_MB_BANK[0..2]7

MEM_MB_DM[0..7]7

CORRECT!

5

DDR3 SODIMM

D D

MEM_MA_ADD[0..15]7

DDR_VREF111

MEM_MA_BANK[0..2]7

C C

B B

DDR_VREF1

C387

C387

C388

C388

1U-10-06Y-Z

1U-10-06Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

MEM_MA_RST#7

R316 10K-04R316 10K-04

1 2

R320 10K-04R320 10K-04

1 2

SDATA018

SCLK018

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA0_CS#07

MEM_MA_DM[0..7]7

CORRECT!

MEM_MA0_CS#17

MEM_MA_WE#7

MEM_MA_CAS#7

MEM_MA_RAS#7

MEM_MA_CKE07

MEM_MA_CKE17

MEM_MA_CLK1_P7

MEM_MA_CLK2_P7

MEM_MA_CLK1_N7

MEM_MA_CLK2_N7

MEM_MA_DQS0_P7

MEM_MA_DQS1_P7

MEM_MA_DQS2_P7

MEM_MA_DQS3_P7

MEM_MA_DQS4_P7

MEM_MA_DQS5_P7

MEM_MA_DQS6_P7

MEM_MA_DQS7_P7

MEM_MA_DQS0_N7

MEM_MA_DQS1_N7

MEM_MA_DQS2_N7

MEM_MA_DQS3_N7

MEM_MA_DQS4_N7

MEM_MA_DQS5_N7

MEM_MA_DQS6_N7

MEM_MA_DQS7_N7

MEM_MA0_ODT07

MEM_MA0_ODT17

DDR_VREF011

+0.75VS

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

DDR_VREF0

C653

C653

.1U-16-04Y-Z

.1U-16-04Y-Z

CON_DDR3_R40_RK-20401-TP4B

CON_DDR3_R40_RK-20401-TP4B

CON_DDR3_R40_RK-20401-TP4B

CON_DDR3_R40_RK-20401-TP4B

MEM_MA_ADD0

98

A0

125

NC/TEST

30

RESET#

126

VREF_CA

198

TS#

77

NC1

122

NC2

197

SA0

201

SA1

200

SDA

202

SCL

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

113

WE#

115

CAS#

110

RAS#

73

CKE0

74

CKE1

101

CK0

102

CK1

103

CK#0

104

CK#1

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

116

ODT0

120

ODT1

1

VREF_DQ

203

VTT

204

VTT

185

VSS

189

VSS

190

VSS

195

VSS

196

VSS

A15

以以以以

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD4

MEM_MA_ADD7

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD1

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

107

83

84

85

89

86

90

91

92

96

97

95

A9

A8

A7

A6

A5

A4

A2

A1

A3

A11

A10/AP

VSS

2

3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

9

8

31

26

25

20

19

14

13

4

+3.3V

C314

C314

?

.1U-16-04Y-Z

.1U-16-04Y-Z

+1.5VS

124

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

151

H4

CN8

CN8

MEM_MA_DATA0

5

VDD

DQ0

MEM_MA_DATA1

7

DQ1

MEM_MA_DATA6

15

DQ2

MEM_MA_DATA7

17

DQ3

MEM_MA_DATA4

4

DQ4

MEM_MA_DATA5

6

DQ5

MEM_MA_DATA3

16

DQ6

MEM_MA_DATA2

18

DQ7

MEM_MA_DATA9

21

DQ8

MEM_MA_DATA8

23

DQ9

MEM_MA_DATA11

33

MEM_MA_DATA15

35

MEM_MA_DATA12

22

MEM_MA_DATA13

24

MEM_MA_DATA14

34

MEM_MA_DATA10

36

MEM_MA_DATA21

39

MEM_MA_DATA17

41

MEM_MA_DATA23

51

MEM_MA_DATA18

53

MEM_MA_DATA20

40

MEM_MA_DATA16

42

MEM_MA_DATA22

50

MEM_MA_DATA19

52

MEM_MA_DATA25

57

MEM_MA_DATA24

59

MEM_MA_DATA27

67

MEM_MA_DATA26

69

MEM_MA_DATA29

56

MEM_MA_DATA28

58

MEM_MA_DATA30

68

MEM_MA_DATA31

70

MEM_MA_DATA37

129

MEM_MA_DATA33

131

MEM_MA_DATA34

141

MEM_MA_DATA35

143

MEM_MA_DATA36

130

MEM_MA_DATA32

132

MEM_MA_DATA38

140

MEM_MA_DATA39

142

MEM_MA_DATA45

147

MEM_MA_DATA41

149

MEM_MA_DATA46

157

MEM_MA_DATA47

159

MEM_MA_DATA40

146

MEM_MA_DATA44

148

MEM_MA_DATA43

158

MEM_MA_DATA42

160

MEM_MA_DATA48

163

MEM_MA_DATA49

165

MEM_MA_DATA50

175

MEM_MA_DATA51

177

MEM_MA_DATA52

164

MEM_MA_DATA53

166

MEM_MA_DATA54

174

MEM_MA_DATA55

176

MEM_MA_DATA56

181

MEM_MA_DATA57

183

MEM_MA_DATA58

191

MEM_MA_DATA59

193

MEM_MA_DATA60

180

MEM_MA_DATA61

182

MEM_MA_DATA62

192

MEM_MA_DATA63

194

161

VSS

162

VSS

167

VSS

168

VSS

172

VSS

173

VSS

178

VSS

179

VSS

184

VSS

S1

NC

S2

NC

VSS

VSS

VSS

156

155

MLP_8

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD15

75

119

78

80

76

81

82

87

88

94

199

A13

A14

A12

NC/A15

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

44

43

38

37

32

93

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

48

72

71

66

65

61

60

54

49

55

123

118

117

112

111

106

105

100

99

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

144

128

139

138

134

133

127

145

150

A A

Shuttle Inc

Shuttle Inc

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Shuttle Inc

A14RM

A14RM

A14RM

DDR3 SODIMM

DDR3 SODIMM

DDR3 SODIMM

1

1.0

1.0

10 37Monday, October 18, 2010

10 37Monday, October 18, 2010

10 37Monday, October 18, 2010

1.0

Page 11

5

4

3

2

1

+1.5VS

C489

C489

C607

C622

C622

C413

C413

C607

C467

C467

1U-10-06Y-Z

2.2U-6.3-06R-K

2.2U-6.3-06R-K

C420

C420

C553

C553

@.1U-16-04Y-Z

@.1U-16-04Y-Z

C534

C534

1000P-50-04X-K

1000P-50-04X-K

C351

C351

1U-10-06Y-Z

@2.2U-6.3-06R-K

@2.2U-6.3-06R-K

C474

C474

C517

C517

1U-6.3-04Y-Z

1U-6.3-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

1U-10-04R-K

1U-10-04R-K

C441

C441

C518

C518

C353

C353

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

.1U-16-04Y-Z

C453

C453

.1U-16-04Y-Z

.1U-16-04Y-Z

2.2U-6.3-06R-K

2.2U-6.3-06R-K

C473

C473

1U-10-04R-K

1U-10-04R-K

1U-10-04R-K

1U-10-04R-K

C397

C397

C616

C616

C465

C465

C656

C656

C614

C614