Page 1

Page 2

RECORDS OF REVISION

MODEL No. : LK520D3LZ17

SPEC No. : LD-19X10

SPEC No. DATE

REVISED

LD-19X10 2007.10.23

No.

−

PAGE

Changed Contents from LK520D3LZ18

−

- Adjusting Color Tracking to be flat

- Changing input signals to 10bit (8bit+2bit FRC)

SUMMARY NOTE

1st Issue

Page 3

LD- 19X10-1

1. Application

This specification applies to the color 52.0” TFT-LCD module LK520D3LZ17.

* These specification sheets are proprietary products of SHARP CORPORATION (“SHARP”) and include materials

protected under copyright of SHARP. Do not reproduce or cause any third party to reproduce them in any form or by

any means, electronic or mechanical, for any purpose, in whole or in part, without the express written permission of

SHARP.

* In case of using the device for applications such as control and safety equipment for transportation (aircraft, trains,

automobiles, etc.), rescue and security equipment and various safety related equipment which require higher

reliability and safety, take into consideration that appropriate measures such as fail-safe functions and redundant

system design should be taken.

* Do not use the device for equipment that requires an extreme level of reliability, such as aerospace applications,

telecommunication equipment (trunk lines), nuclear power control equipment and medical or other equipment for

life support.

* SHARP assumes no responsibility for any damage resulting from the use of the device that does not comply with

the instructions and the precautions specified in these specification sheets.

* Contact and consult with a SHARP sales representative for any questions about this device.

2. Overview

This module is a color active matrix LCD module incorporating amorphous silicon TFT (Thin Film Transistor). It is

composed of a color TFT-LCD panel, driver ICs, control circuit, power supply circuit, inverter circuit and back light

system etc. Graphics and texts can be displayed on a 1920×RGB×1080 dots panel with 650 million colors by

using LVDS (Low Voltage Differential Signaling) to interface, +12V of DC supply voltages.

This module also includes the DC/AC inverter to drive the CCFT. (+24V of DC supply voltage)

And in order to improve the response time of LCD, this module applies the Over Shoot driving (O/S driving)

technology for the control circuit .In the O/S driving technology, signals are being applied to the Liquid Crystal

according to a pre-fixed process as an image signal of the present frame when a difference is found between image

signal of the previous frame and that of the current frame after comparing them.

With this technology, image signals can be set so that liquid crystal response completes within one frame. As a

result, motion blur reduces and clearer display performance can be realized.

3. Mechanical Specifications

Parameter Specifications Unit

Display size

Active area 1152.0(H) x 648.0 (V) mm

Pixel Format

Pixel pitch 0.600(H) x 0.600 (V) mm

Pixel configuration R, G, B vertical stripe

Display mode Normally black

Unit Outline Dimensions (*1) 1219.0(W) x 706.7(H) x 64.6(D) mm

Mass

Surface treatment

(*1) Outline dimensions are shown in Fig.1 (excluding protruding portion)

132.174 (Diagonal)

52.0 (Diagonal)

1920(H) x 1080(V)

(1pixel = R + G + B dot)

21.0 ±1.0

Anti glare

Hard coating: 2H

cm

inch

pixel

kg

Page 4

4. Input Terminals

4.1. TFT panel driving

CN1 (Interface signals and +12V DC power supply)

Using connector : FI-RE51S-HF (Japan Aviation Electronics Ind. , Ltd.)

Mating connector : FI-RE51HL, FI-RE51CL (Japan Aviation Electronics Ind. , Ltd.)

Mating LVDS transmitter : THC63LVD1023 or equivalent device

Pin No. Symbol Function Remark

1

2 TEST

3 TEST

4

5 R/L

6 U/D

7 SELLVDS

8 TEST

9

10

11 GND

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

Reserved

Reserved

Reserved

Reserved

AIN0- Aport (-)LVDS CH0 differential data input

AIN0+ Aport (+)LVDS CH0 differential data input

AIN1- Aport (-)LVDS CH1 differential data input

AIN1+ Aport (+)LVDS CH1 differential data input

AIN2- Aport (-)LVDS CH2 differential data input

AIN2+ Aport (+)LVDS CH2 differential data input

GND

ACK- Aport LVDS Clock signal(-)

ACK+ Aport LVDS Clock signal(+)

GND

AIN3- Aport (-)LVDS CH3 differential data input

AIN3+ Aport (+)LVDS CH3 differential data input

AIN4- Aport (-)LVDS CH4 differential data input

AIN4+ Aport (+)LVDS CH4 differential data input

GND

GND

BIN0- Bport (-)LVDS CH0 differential data input

BIN0+ Bport (+)LVDS CH0 differential data input

BIN1- Bport (-)LVDS CH1 differential data input

BIN1+ Bport (+)LVDS CH1 differential data input

BIN2- Bport (-)LVDS CH2 differential data input

BIN2+ Bport (+)LVDS CH2 differential data input

GND

BCK- Bport LVDS Clock signal(-)

BCK+ Bport LVDS Clock signal(+)

GND

BIN3- Bport (-)LVDS CH3 differential data input

BIN3+ Bport (+)LVDS CH3 differential data input

BIN4- Bport (-)LVDS CH4 differential data input

BIN4+ Bport (+)LVDS CH4 differential data input

GND

GND

GND

Fix to Low level or open usually.

Fix to Low level or open usually.

Horizontal shift direction [Note1,2]

Vertical shift direction [Note1,2]

Select LVDS data order [Note3,4]

Fix to Low level or open usually.

(Shown in Fig.1)

Pull down : (GND)

Pull down : (GND)

Pull up : (3.3V)

Pull down : (GND)

LD- 19X10-2

Page 5

45

46

47

48

49

50

51

[note]GND of a liquid crystal panel drive part has connected with a module chassis.

GND

GND

VCC +12V Power Supply

VCC +12V Power Supply

VCC +12V Power Supply

VCC +12V Power Supply

VCC +12V Power Supply

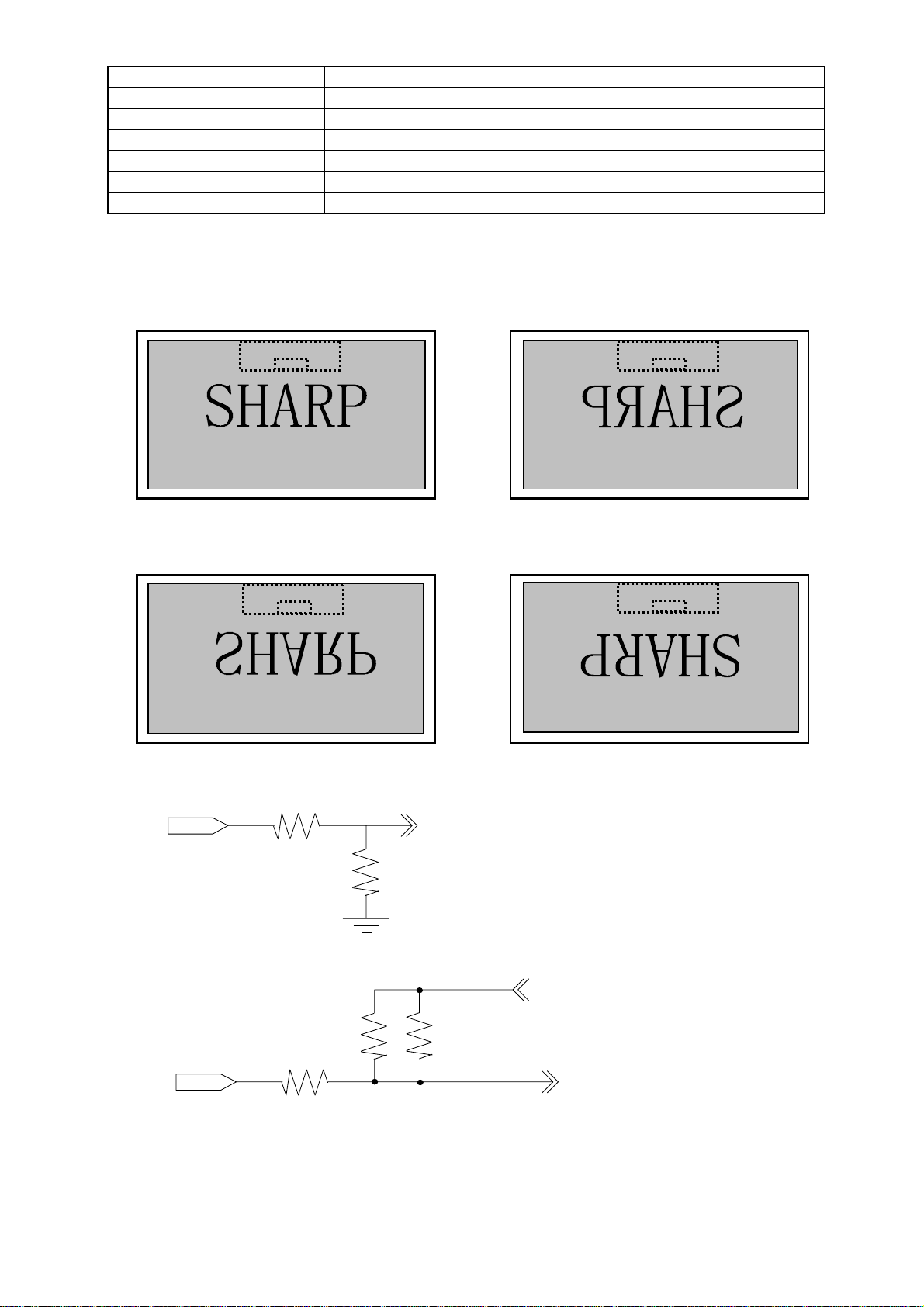

[Note 1] Display reversal function

Normal (Default) Horizontal reverse image

R/L : L (GND) U/D: L (GND) R/L : H (3.3V) U/D: L (GND)

CN1

Vertical reverse image Horizontal and vertical reverse image

R/L : L (GND) U/D: H (3.3V) R/L : H(3.3V) U/D: H (3.3V)

CN1

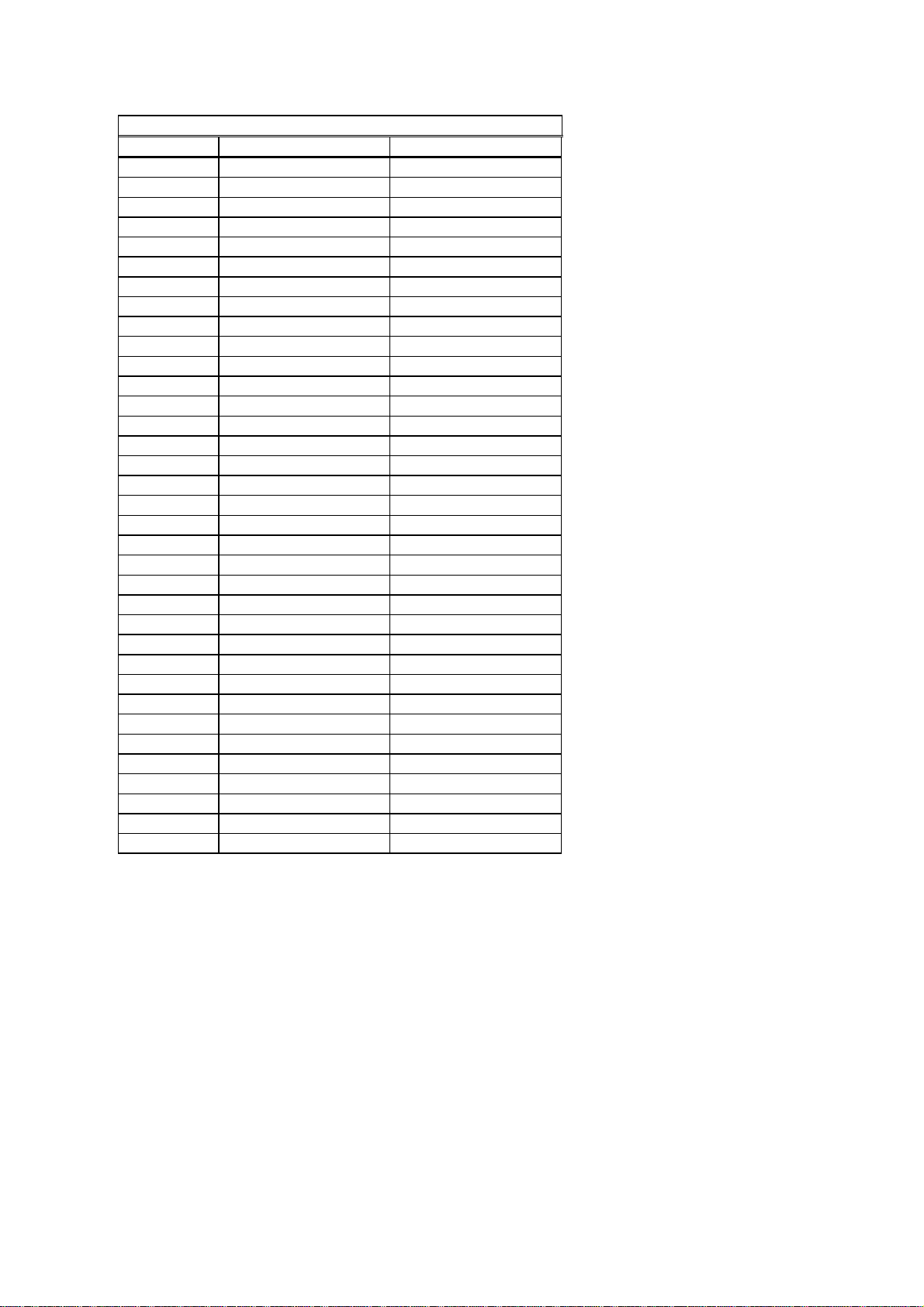

[Note 2]The equivalent circuit figure of the terminal

100Ω

Terminal

LD- 19X10-3

CN1

CN1

Min : 16.5KΩ

Typ : 47KΩ

Max : 330KΩ

[Note 3]The equivalent circuit figure of the terminal

3.3V

4.7KΩ

100Ω

Terminal

Min : 16.5KΩ

Typ : 60KΩ

Max : 330KΩ

Page 6

[Note 4] LVDS Data order

Data L(GND) H(3.3V) or Open

TA0 R2 R4

TA1 R3 R5

TA2 R4 R6

TA3 R5 R7

TA4 R6 R8

TA5 R7 R9(MSB)

TA6 G2 G4

TB0 G3 G5

TB1 G4 G6

TB2 G5 G7

TB3 G6 G8

TB4 G7 G9(MSB)

TB5 B2 B4

TB6 B3 B5

TC0 B4 B6

TC1 B5 B7

TC2 B6 B8

TC3 B7 B9(MSB)

TC4 NA NA

TC5 NA NA

TC6 DE(*) DE(*)

TD0 R8 R2

TD1 R9(MSB) R3

TD2 G8 G2

TD3 G9(MSB) G3

TD4 B8 B2

TD5 B9(MSB) B3

TD6 N/A N/A

TE0 R0(LSB) R0(LSB)

TE1 R1 R1

TE2 G0(LSB) G0(LSB)

TE3 G1 G1

TE4 B0(LSB) B0(LSB)

TE5 B1 B1

TE6 N/A N/A

NA: Not Available

(*)Since the display position is prescribed by the rise of DE(Display Enable)signal, please do not fix DE

signal during operation at ”High”.

LD- 19X10-4

SELLVDS

Page 7

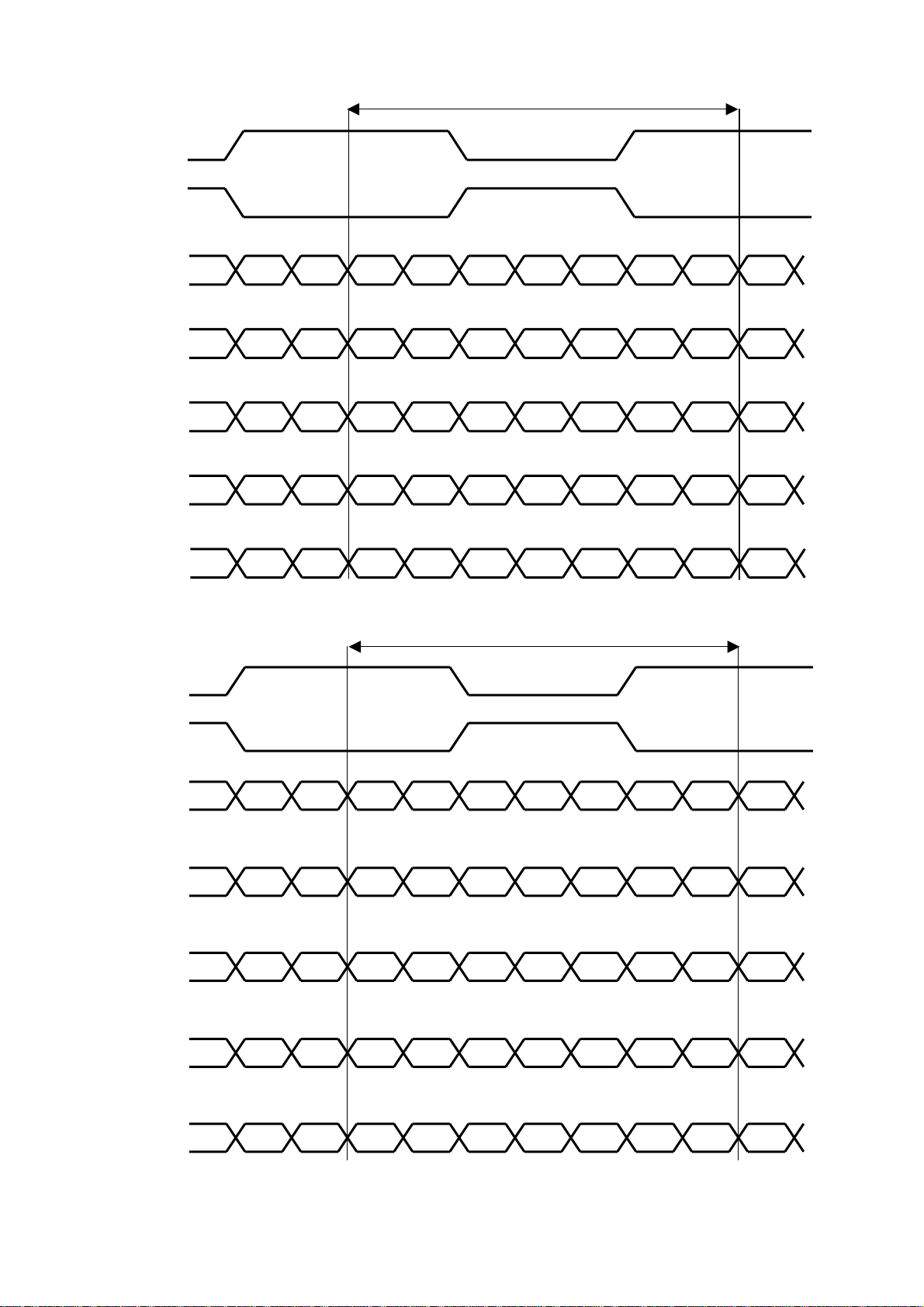

NAN

NAN

NAN

NAN

–

,

–

–

SELLVDS= High (3.3V) or OPEN

ACK+,BCK+

ACK– ,BCK–

AIN0+,BIN0+

AIN0

–,BIN0–

AIN1+,BIN1+

–,BIN1–

AIN1

AIN2+,BIN2+

AIN2

–,BIN2–

AIN3+,BIN3+

AIN3

–,BIN3–

AIN4+,BIN4+

–,BIN4–

AIN4

SELLVDS= Low (GND)

ACK+,BCK+

ACK– ,BCK–

AIN0+,BIN0+

AIN0

BIN0

AIN1+,BIN1+

AIN1

–,BIN1–

AIN2+,BIN2+

AIN2

–,BIN2–

AIN3+,BIN3+

–,BIN3–

AIN3

AIN4+,BIN4+

AIN4

–,BIN4

DE: Display Enable, NA: Not Available (Fixed Low)

LD- 19X10-5

1 cycle

G4 R9 R8 R7 R6 R5 R4 R4 R5 G4

B5 B4 G9 G8 G7 G6 G5 G5 G6 B5

DE

A

A

NA NA

B3 B2 G3 G2 R3 R2 R2 R3

B1 B0 G1 G0 R1 R0 R0 R1

B9 B8 B7 B6 B6 B7

DE

1 cycle

G2 R7 R6 R5 R4 R3 R2 R2 R3 G2

B3 B2 G7 G6 G5 G4 G3 G3 G4 B3

DE

A

A

NA NA

B9 B8 G9 G8 R9 R8 R8 R9

B1 B0 G1 G0 R1 R0 R0 R1

B7 B6 B5 B4 B4 B5

DE

Page 8

LD- 19X10-6

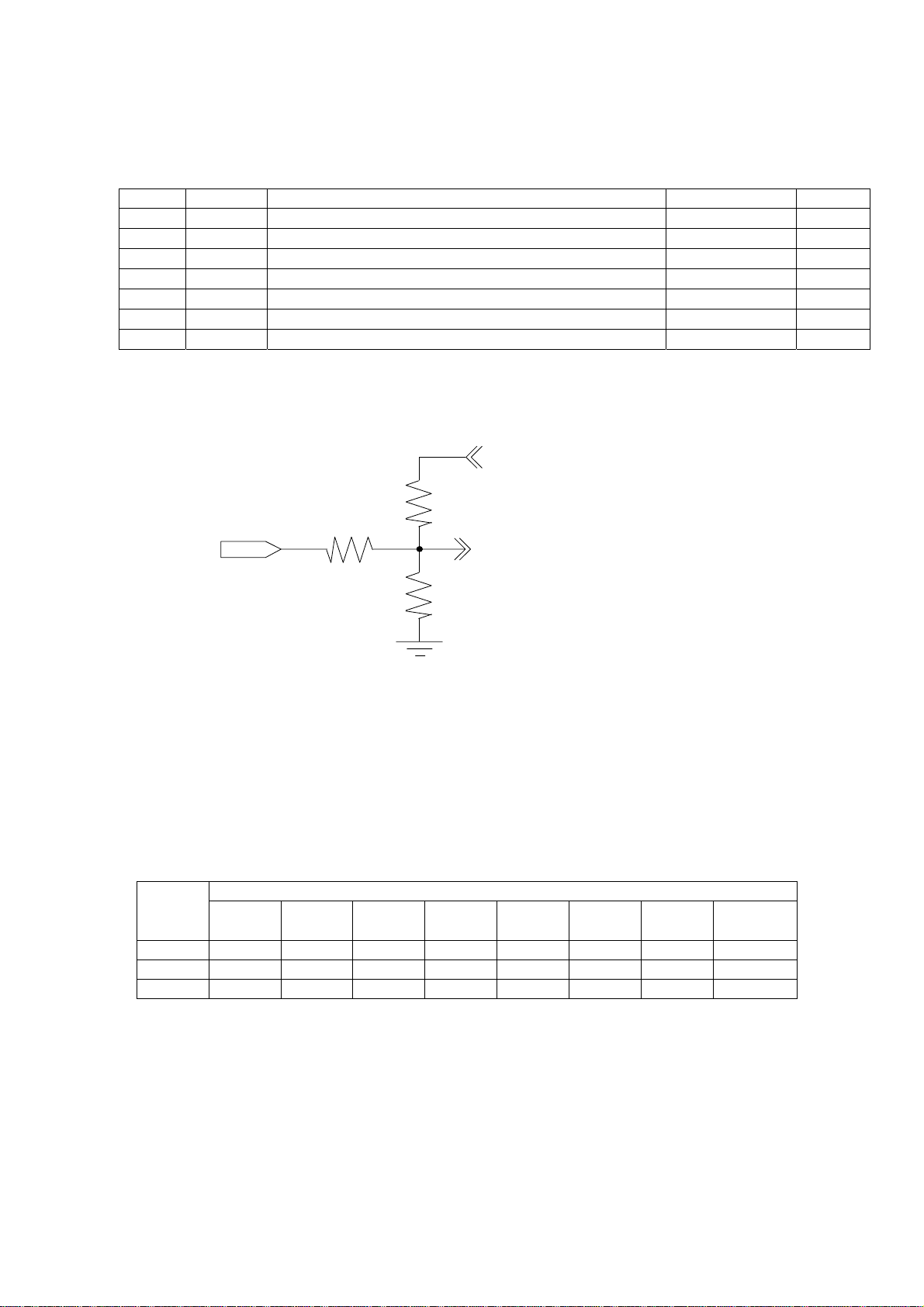

CN2 (O/S control) (Shown Fig 1)

O/S Driving Pin No and function

Using connector : SM07B-SRSS-TB-A (JST)

Mating connector : SHR-07V-S or SHR-07V-S-B(JST)

Pin No. Symbol Function Default Remark

1

FRAME

Frame frequency setting 1:60Hz 0:50Hz

2 O/S set O/S operation setting H:O/S_ON, L:O/S_OFF [Note 1]

3 TEST Not Available

4 Temp3 Data3 of panel surface temperature

5 Temp2 Data2 of panel surface temperature

6 Temp1 Data1 of panel surface temperature

Pull down :GND

Pull up 3.3V [Note 2]

Pull down :GND

Pull up 3.3V

Pull up 3.3V

Pull up 3.3V

7 GND GND

*L: Low level voltage (GND) H: High level voltage(3.3V)

[Note 1] In case of O/S set setting ”L”(O/S_OFF), it should be set the TEMP1~3 to “L”.

[Note 2] The equivalent circuit figure of the terminal

3.3V

4.7KΩ

100Ω

Terminal

[Note 2]

[Note 2]

[Note 2]

Min : 16.5KΩ

Typ : 47KΩ

Max : 330KΩ

According as the surface temperature of the panel, enter the optimum 3 bit signal into pin No.4, 5 and 6.

Measuring the correlation between detected temperature by the sensor on PWB in user’s side and actual

surface temperature of panel at center, convert the temperature detected by the sensor to the surface

temperature of panel to enter the 3 bit temperature data.

For overlapping temperatures (such as 5°C, 10°C, 15°C, 20°C, 25°C, 30°C, 35°C) select the optimum

parameter, judging from the actual picture image.

Surface temperature of panel

Pin no.

0-5°C 5-10°C 10-15°C 15-20°C 20-25°C 25-30°C 30-35°C 35°C and

above

4 0 0 0 0 1 1 1 1

5 0 0 1 1 0 0 1 1

6 0 1 0 1 0 1 0 1

*0: Low level voltage (GND) 1: High level voltage(3.3V)

*For overlapping temperatures (such as 5°C, 10°C, 15°C, 20°C, 25°C, 30°C, 35°C) select the optimum

parameter, judging from the actual picture image.

Page 9

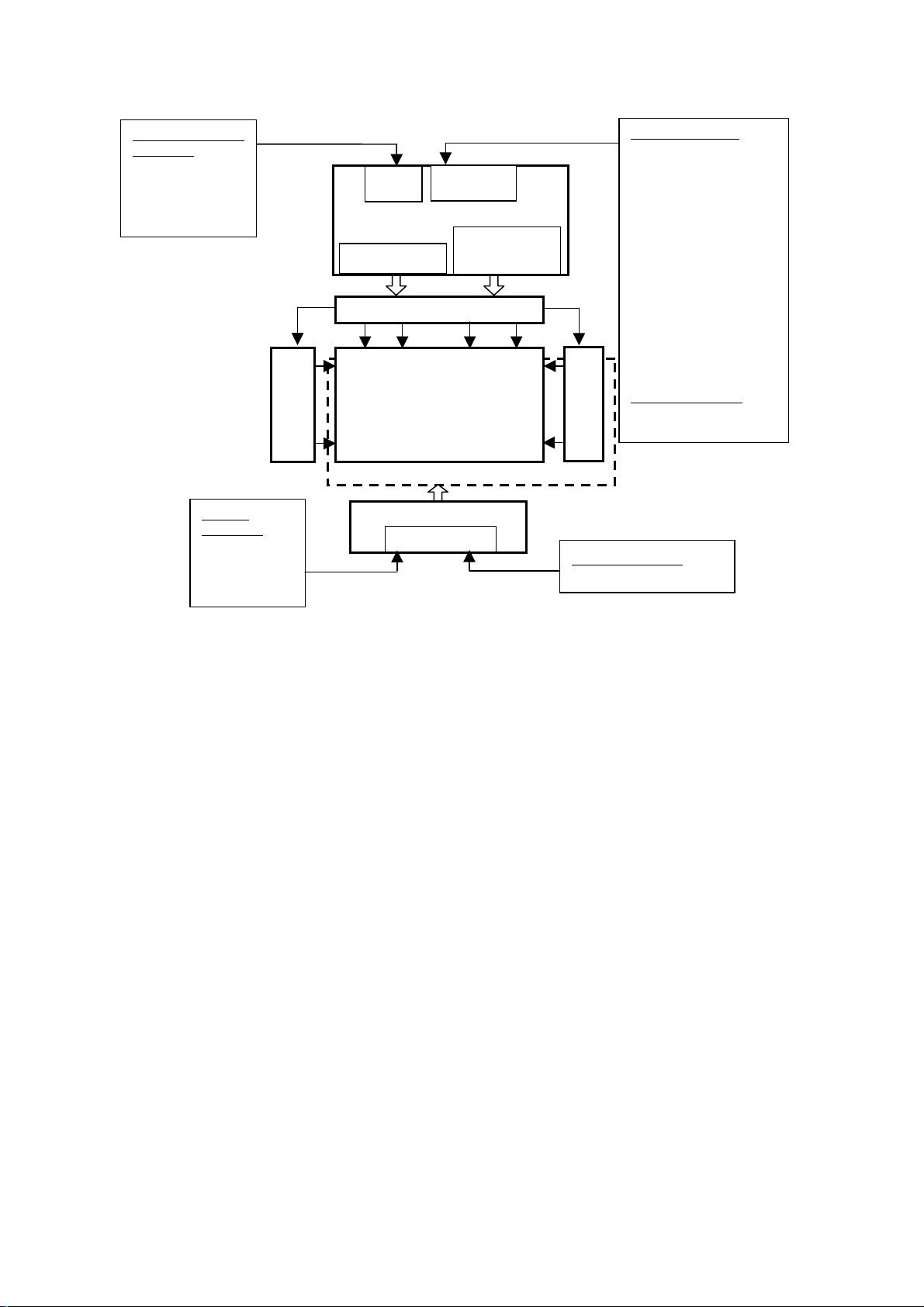

4.2. Interface block diagram

O/S CONTROL

SIGNALS

O/SSET

FRAME

TEMP3

TEMP2

INPUT

SIGNALS

VON,VBRT

Control

1920×3(RGB)×1080

GATEDRIVER

CN2

CONTROLPWB

SOURCE DRIVER

LCDPANEL

INVERTER

CN1

PowerSupply

Circuit

INPUTSIGNALS

R/L

U/D

SELLVDS

AIN0-AIN0+

AIN1-AIN1+

AIN2-AIN2+

AIN3-AIN3+

AIN4-AIN4+

ACK-ACK+

BIN0-BIN0+

BIN1-BIN1+

BIN2-BIN2+

BIN3-BIN3+

BIN4-BIN4+

BCK-BCK+

POWERSUPPLY

+12VDC

GATEDRIVER

BACK LIGHT(CCFT×24)

POWERSUPPLY

+24VDC

LD- 19X10-7

Page 10

LD- 19X10-8

4.3. Backlight driving

CN103 (+24V DC power supply and inverter control)

Using connector: S14B-PH-K-S (LF) (JST)

Mating connector: PHR-14 (JST)

Pin No. Symbol Function Default(OPEN) Input Impedance Remark

1 VINV +24V -

2 VINV +24V -

3 VINV +24V -

4 VINV +24V -

5 VINV +24V -

6 GND -

7 GND -

8 GND -

9 GND -

10 GND -

11 Reserved For LCD module internal

usage, should be open

12 VON Inverter ON/OFF GND : pull down

Inverter OFF

13 VBRT Brightness Control 3.3V : pull up

Brightness 100%

14 VBRT _sel Brightness Control

selection

*GND of an inverter board is not connected to GND of a module chassis and a liquid crystal panel drive part.

CN104(+24V DC power supply)

Using connector: S14B-PH-K-S(LF) (JST)

Mating connector: PHR-14 (JST)

Pin No. Symbol Function Default(OPEN) Input Impedance Remark

1 VINV +24V -

2 VINV +24V -

3 VINV +24V -

4 VINV +24V -

5 VINV +24V -

6 GND -

7 GND -

8 GND -

9 GND -

10 GND -

11 Reserved For LCD module internal

usage, should be open

12 Reserved For LCD module internal

usage, should be open

13 Reserved For LCD module internal

usage, should be open

14 Reserved For LCD module internal

usage, should be open

[Note 1] Inverter ON/OFF

Input voltage Function

0V Inverter : OFF

3.3V Inverter : ON

3.3V : pull up

Selected Analog PWM

22K ohm [Note 1]

950K ohm [Note 3]

26.7K ohm [Note 2]

-

-

Page 11

[Note 2] Brightness Control selection

Pin No.14 is used for the selection of dimming control for V

Input voltage V

BRT

BRT pin (Pin No.13).

0V Pulse dimming

3.3V Analog dimming

[Note 3]Brightness Control

1. Analog Dimming

Brightness control is regulated by analog input voltage (0V to 3.3V).

Input voltage [V

BRT

]

[Reference]

Brightness ratio[%]

MIN TYP MAX Function

0V <-> 3.3V

0V: Dark - 3.3V: Bright

20 <-> 100

[Note] PWM frequency : 275±10Hz

[Note]There is a case that lamp mura may happen, depending on ambient temperature and dimming.

Dimming level should be set according to your evaluation of actual display performance.

(Minimum input voltage 1.4V at below 15℃)

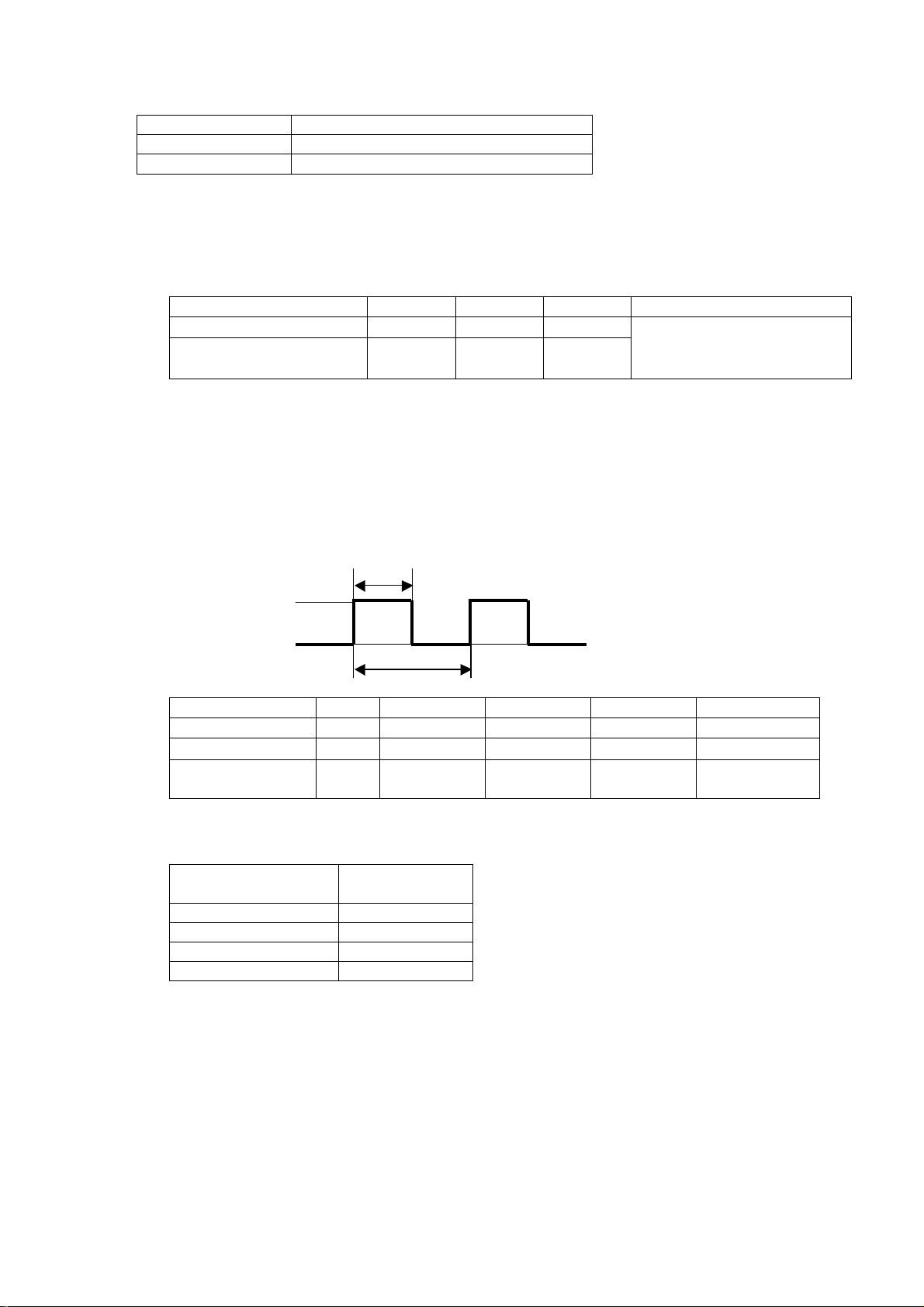

2.Pulse Dimming

Pin No.13 is used for the control of the PWM duty with input pulse from 150Hz to 350Hz.

LD- 19X10-9

Ta=25℃

InputPWMwaveform

Pulse signal [Hz]

DUTY(TON/T) [%] 40 <-> 100

Dimming level

(luminance ratio)

[Reference]The characteristic of the pulse PWM duty vs dimming level

[Note]There is a case that lamp mura may happen, depending on ambient temperature,

[Note]In case of using Pulse Dimming, be careful so that the V

Ton

Highvoltage

Lowvoltage

ON ONOFF

T

Duty=T

ON

/T

MIN TYP MAX

Remark

150 275 350

Ta=25℃

DUTY(TON/T)

[%] 20 <-> 100

Dimming level

Ta=25℃

(luminance ratio)

40% 20%

60% 45%

80% 70%

Input Condition

Pulse Signal=275Hz

Ta=25℃

100% 100%

in dimming. Minimum dimming level should be set according to your evaluation of

actual display performance. (Minimum duty 60% at below 15℃)

signal (Pin 13) doesn’t have glitch.

BRT

Page 12

LD- 19X10-10

4.4. The back light system characteristics

The back light system is direct type with 24 CCFTs (Cold Cathode Fluorescent Tube).

The characteristics of the lamp are shown in the following table. The value mentioned below is at the case of one

CCFT.

Item Symbol Min. Typ. Max. Unit Remarks

Life time TL - 60000 - Hour [Note]

[Note]

• Lamp life time is defined as the time when brightness becomes 50% of the original value in the continuous

operation under the condition of Ta=25°C and brightness control(V

=100%).

BRT

• Above value is applicable when the long side of LCD module is placed horizontally (Landscape position).

(Lamp lifetime may vary if LCD module is in portrait position due to the change of mercury density inside

the lamp.)

5. Absolute Maximum Ratings

Parameter Symbol Condition Ratings Unit Remark

Input voltage

(for Control)

12V supply voltage

(for Control)

Input voltage

(for Inverter)

24V supply voltage

(for Inverter)

I

V

VCC

V

ON

V

BRT

VBRT _sel

V

INV

Ta=25 °C

Ta=25 °C

Ta=25 °C

Ta=25 °C

-0.3 ~ 3.6 V [Note 1]

0 ~ + 14 V

0 ~ + 6 V

0 ~ +29 V

Storage temperature Tstg - -25 ~ +60

Operation temperature

(Ambient)

Topa - 0 ~ +50

[Note 1] SELLVDS, R/L, U/D, FRAME, O/S_set, TEMP1~3

[Note 2] Humidity 95%RH Max.(Ta≦40°C)

Maximum wet-bulb temperature at 39 °C or less.(Ta>40°C)

No condensation.

°C

[Note 2]

°C

Page 13

LD- 19X10-11

6. Electrical Characteristics

6.1. Control circuit driving Ta=25 °C

Parameter Symbol Min. Typ. Max. Uniit Remark

Supply voltage Vcc 11.4 12 12.6 V [Note 1]

+12V supply

voltage

Permissible input ripple voltage VRP - - 100 mVP-P Vcc = +12.0V

threshold voltage

Input High voltage VIH 2.3 - 3.3 V

Input leak current (Low)

Input leak current (High)

[Note]VCM: Common mode voltage of LVDS driver.

[Note 1]

Input voltage sequences Dip conditions for supply voltage

0 < t1 ≦ 20ms a) 6.5V ≦ Vcc < 10.8V

10 < t2 ≦ 20ms td ≦ 10ms

10 < t3 ≦ 50ms b) Vcc < 6.5V

0 < t4 ≦ 1s Dip conditions for supply voltage is

t5 ≧ 200ms based on input voltage sequence.

t6 ≧ 0

t7 ≧ 300ms

Current dissipation Icc - 0.8 1.8 A [Note 2]

I

- 2.0 - A

Inrush current

High VTH - - 100 mV Differential input

Low V

RUSH

T

- 0.1 - ms

RUSH

TL -100 - - mV

V

Input Low voltage VIL 0 - 1.0 V

IIL1 - - 400 µA

IL2 - - 40 µA

I

IIH1 - - 40 µA

I

IH2 - - 400 µA

Terminal resistor RT - 100 -

Ω

Differential

[Note 7]

CM = +1.2V

[Note 6]

[Note 3]

I = 0V

V

[Note 4]

I = 0V

V

[Note 5]

I = 3.3V

V

[Note 4]

I = 3.3V

V

[Note 5]

input

0.9VCC

0.1Vcc

Vcc

Data1

Data2

Back light:V

t1

t2

ON

t3

INV

t5

OFF

t6

t4

t3

0.9Vcc

0.1Vcc

t7

OFF

0.1Vcc

Vcc

V1

V2

td

※ Data1: ACK±, AIN0±, AIN1±, AIN2±, AIN3±, AIN4±,BCK±, BIN0±, BIN1±, BIN2±, BIN3±, BIN4±

*V

voltage pursues the sequence mentioned above

CM

※ Data2: R/L, U/D, SELLVDS, FRAME, O/S_SET, TEMP1, TEMP2, TEMP3

V1:10.8V

V2:6.5V

Page 14

LD- 19X10-12

V

[Note]About the relation between data input and back light lighting, please base on the above-mentioned input

sequence. When back light is switched on before panel operation or after a panel operation stop, it may not

display normally. But this phenomenon is not based on change of an incoming signal, and does not give

damage to a liquid crystal display.

[Note 2] Typical current situation: 1023 gray-bar patterns. (Vcc = +12.0V)

The explanation of RGB gray scale is seen in section 8.

RGB

GS0

RGB

GS1

RGB

GS2

....

RGB

GS1022

RGB

GS1023

Vcc=+12.0V

CK=74.25MHz

Th=14.8µs

[Note 3] R/L, U/D, SELLVDS, FRAME, O/S_SET, TEMP1, TEMP2, TEMP3

[Note 4] SELLVDS, O/S_SET, TEMP1, TEMP2, TEMP3

[Note 5] R/L, U/D, FRAME

[Note 6] ACK±, AIN0±, AIN1±, AIN2±, AIN3±, AIN4±,BCK±, BIN0±, BIN1±, BIN2±, BIN3±, BIN4±

[Note 7] Vcc12V inrush current waveform

2A

cc

Icc

Page 15

V

V

V

V

6.2. Inverter driving for back light

The back light system is

direct type with 24 CCFTs (Cold Cathode Fluorescent Tube).

Parameter Symbol Min. Typ. Max. Unit Remark

LD- 19X10-13

Current dissipation 1 IINV 1 - 11.2 12.5 A

+24V

Current dissipation 2 IINV 2 - 10.3 11.5 A

Supply voltage VINV 22.8 24.0 25.2 V

Permissible input ripple voltage VRF - - 300 mV

Input voltage (Low) V

Input voltage (High) V

0 - 1.0 V

ONL

2.3 - 3.6 V

ONH

[Note 1] 1) V

INV-turn-on condition

INV

21.6V

1.0V

T1 T2

ON,VBRT

0V

2.0V

2) VINV-turn-off condition

, V

BRT

ON

p-p

T1>100µs

≧1ms

T2

t1≧1ms

VINV = 24V, Ta=25°C

= 3.3V

V

BRT

[Note 1,2]

VINV = +24.0V

V

ON,VBRT

VBRT _sel

,

t1

INV

1.0V

0V

21.6V

0V

[Note 2] Current dissipation 1 : Definition within 60 minutes after turn on. (Rush current is excluded.)

Current dissipation 2 : Definition more than 60minutes after turn on.

Page 16

7. Timing characteristics of input signals

7.1. Timing characteristics

Timing diagrams of input signal are shown in Fig.2.

Parameter Symbol Min. Typ. Max. Unit Remark

Clock Frequency 1/Tc

Horizontal period TH

Data enable

signal

[Note]-When vertical period is very long, flicker and etc. may occur.

-Please turn off the module after it shows the black screen.

-Please make sure that length of vertical period should become of an integral multiple of horizontal

length of period. Otherwise, the screen may not display properly.

-As for your final setting of driving timing, we will conduct operation check test at our side, please

inform your final setting.

DE

Aport DATA

(R,G,B)

Bport DATA

(R,G,B)

DE

Horizontal period (High) THd 960 960

Vertical period TV 1109 1125

Vertical period (High) TVd 1080 1080 1080 line

TH

1919

Tc

1

2

TV

3

4 1920 1920

Fig.2 Timing characteristics of input signals

LD- 19X10-14

55

74.25 85 MHz

984 1100 1650 clock

12.0 14.8 - µs

960

1350

clock

line

THd

1919

1 2 1080 1079

TVd

Page 17

7.2. Input data signal and display position on the screen

R1G1 B1 R2 G2B2

(1、1) (1,2)

LD- 19X10-15

1・11・21・3

2・12・2

3・1

RGB

1080・1

Display position of Dat (V,H)

1・1920

1080・1920

Page 18

g

–

8. Input Signal, Basic Display Colors and Gray Scale of Each Color

Colors &

Gray scale

Gray

R0 R1 R2 R3 R4 R5 R6 R7 R8 R9 G0 G1 G2 G3 G4 G5 G6 G7 G8 G9 B0 B1 B2 B3 B4 B5 B6 B7 B8 B9

Scale

Data si

nal

LD- 19X10-16

Black

Blue – 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1

Green – 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0

Cyan – 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Red – 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Basic Color

Magenta – 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1

Yellow – 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0

White – 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Black GS0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

× GS1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Darker GS2 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

×

Ø

Brighter GS1021 1 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

↓

↓

↓

↓

↓

↓

↓

↓

Gray Scale of Red

Ø GS1022 0 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Red GS1023 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Black GS0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

× GS1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Darker GS2 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

×

Ø

Brighter GS1021 0 0 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0

Gray Scale of Green

Ø GS1022 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0

Green GS1023 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0

Black GS0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

↓

↓

↓

↓

↓

↓

↓

↓

× GS1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0

Darker GS2 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0

Ø

Ø

Brighter GS1021 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1

Gray Scale of Blue

Ø GS1022 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1

Blue GS1023 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1

↓

↓

↓

↓

↓

↓

↓

↓

0: Low level voltage, 1: High level voltage.

Each basic color can be displayed in 1024 gray scales from 10 bits data signals. According to the combination of

total 30 bits data signals, the 650-million-color display can be achieved on the screen.

Page 19

9. Optical characteristics

d

Parameter Symbol Condition Min. Typ. Max. Unit Remark

θ

21

θ

22

θ

11

θ

12

τ

r

τ

d

x 0.242 0.272 0.302 y 0.247 0.277 0.307 x 0.610 0.640 0.670 y 0.300 0.330 0.360 x 0.250 0.280 0.310 y 0.570 0.600 0.630 x 0.120 0.150 0.180 y 0.030 0.060 0.090 -

Viewing angle

range

Contrast ratio CRn 1000 1500 - [Note2,4]

Response time

Chromaticity

Gamma - - 2.2 - -

Horizontal

Vertical

White

Red

Green

Blue

Ta=25°C, Vcc=12.0V, VINV =24.0V, V

70 88 - Deg.

CR≧10

70 88 -

- 6 - ms [Note3,4,5]

θ

=0 deg.

LD- 19X10-17

=100%,Timing:60Hz(typ. value)

BRT

[Note1,4]

Deg.

[Note4]

Luminance White YL 360 450 - cd/m2

Luminance

uniformity

White

Measurement condition: Set the value of V

δw

to maximum luminance of white.

BRT

- - 1.25 - [Note 6]

*The measurement shall be executed 60 minutes after lighting at rating.

[Note]The optical characteristics are measured using the following equipment.

Detector(EZ-CONTRAST/ Photodiode)

400mm

Detector(SR-3)

Field=1°

Middle of the screen (

θ

=0°)

Middle of the screen (

TFT-LCD Module

TFT-LCD Module

Fig.4-1 Measurement of viewing angle range an

Response time.

Viewing angle range: EZ-CONTRAST

Response time: Photodiode

Fig.4-2 Measurement of Contrast, Luminance,

Chromaticity.

θ

=0°)

Page 20

LD- 19X10-18

[Note 1]Definitions of viewing angle range :

Normal line

θ

11

θ

21

θ

12

θ

22

6 o’clock direction

[Note 2]Definition of contrast ratio :

The contrast ratio is defined as the following.

Luminance (brightness) with all pixels white

Contrast Ratio

=

Luminance (brightness) with all pixels black

[Note 3]Definition of response time

The response time (τd and τr) is defined as the following figure and shall be measured by switching the input

signal for “any level of gray (0%, 25%, 50%, 75% and 100%)” and “any level of gray (0%, 25%, 50%, 75%

and 100%)”.

0%

0%

25%

50%

75%

100%

td: 25%-0%

td: 50%-0% td: 50%-25%

td: 75%-0% td: 75%-25% td: 75%-50%

td: 100%-0% td: 100%-25% td: 100%-50% td:100%-75%

25% 50% 75%

tr:0%-25%

tr:0%-50% tr:0%-75% tr:0%-100%

tr: 25%-50% tr25%-75% tr: 25%-100%

tr: 50%-75% tr: 50%-100%

100%

tr: 75%-100%

t*:x-y...response time from level of gray(x) to level of gray(y)

τ

= Σ(tr:x-y)/10 , τd = Σ(td:x-y)/10

r

Bright

100%

90%

Dark

Bright

Photodetector

10%

Output

0%

τd τ

time

r

[Note 4]This shall be measured at center of the screen.

[Note 5] This value is valid when O/S driving is used at typical input time value.

Page 21

LD- 19X10-19

[Note 6]Definition of white uniformity ;

White uniformity is defined as the following with five measurements. (A∼E)

Maximum luminance of five points (brightness)

W=

δ

Minimum luminance of five points (brightness)

480

960 1440

A

C

B

pixel

D

E

10. Handling Precautions of the module

a) Be sure to turn off the power supply when inserting or disconnecting the cable.

b) This product is using the parts (inverter, CCFT etc), which generate the high voltage.

Therefore, during operating, please don't touch these parts.

c) Brightness control voltage is switched for “ON” and “OFF”, as shown in Fig.4. Voltage difference generated

by this switching, ∆VINV, may affect a sound output, etc. when the power supply is shared between the

inverter and its surrounding circuit. So, separate the power supply of the inverter circuit with the one of its

surrounding circuit.

270

540

810

pixel

ΔVINV

VINV

IINV

PWM control

signal

0V

0A

ON ONOFF

0V

Fig.4 Brightness control voltage.

*Since inverter board’s GND is not connected to the frame of the LCD module, please connect it with the

Customer’s GND of inverter power supply.

d) Be sure to design the cabinet so that the module can be installed without any extra stress such as warp or

twist.

e) Since the front polarizer is easily damaged, pay attention not to scratch it.

f) Since long contact with water may cause discoloration or spots, wipe off water drop immediately.

g) When the panel surface is soiled, wipe it with absorbent cotton or other soft cloth.

h) Since the panel is made of glass, it may break or crack if dropped or bumped on hard surface. Handle with

care.

Page 22

LD- 19X10-20

i) Since CMOS LSI is used in this module, take care of static electricity and take the human earth into

consideration when handling.

j) The module has some printed circuit boards (PCBs) on the back side, take care to keep them form any stress

or pressure when handling or installing the module; otherwise some of electronic parts on the PCBs may be

damaged.

k) Observe all other precautionary requirements in handling components.

l) When some pressure is added onto the module from rear side constantly, it causes display non-uniformity

issue, functional defect, etc. So, please avoid such design.

m) When giving a touch to the panel at power on supply, it may cause some kinds of degradation. In that case,

once turn off the power supply, and turn on after several seconds again, and that is disappear.

n) When handling LCD modules and assembling them into cabinets, please be noted that long-term storage in

the environment of oxidization or deoxidization gas and the use of such materials as reagent, solvent,

adhesive, resin, etc. which generate these gasses, may cause corrosion and discoloration of the LCD

modules.

o) This LCD module is designed to prevent dust from entering into it. However, there would be a possibility to

have a bad effect on display performance in case of having dust inside of LCD module. Therefore,

please ensure to design your TV set to keep dust away around LCD module.

11. Packing form

a) Piling number of cartons: 2 maximum

b) Packing quantity in one carton: 8 pcs.

c) Carton size: 1320 (W) × 1110 (D) × 940 (H) (mm)

d) Total mass of one carton filled with full modules: 225kg (Max)

12. Reliability test item

No. Test item Condition

1

2

3

4

5

6

7

8

[Result evaluation criteria]

Under the display quality test condition with normal operation state, there shall be no change, which may

affect practical display function.

High temperature storage test

Low temperature storage test

High temperature and high humidity

operation test

High temperature operation test

Low temperature operation test

Vibration test

(non-operation)

Shock test

(non-operation)

ESD

Ta=60°C 240h

Ta=-25°C240h

Ta=40°C ; 95%RH 240h

(No condensation)

Ta=50°C 240h

Ta=0°C 240h

Frequency: 10~57Hz/Vibration width (one side): 0.075mm

: 58~500Hz/Acceleration: 9.8 m/s²

Sweep time: 11 minutes

Test period: 3 hours (1h for each direction of X, Y, Z)

Maximum acceleration: 294m/s

Pulse width: 11ms, sinusoidal half wave

Direction: +/-X, +/-Y, +/-Z, once for each direction.

* At the following conditions, it is a thing without incorrect

operation and destruction.

(1)Non-operation: Contact electric discharge ±10kV

Non-contact electric discharge ±20kV

(2)Operation Contact electric discharge ±8kV

Non-contact electric discharge ±15kV

Conditions: 150pF, 330ohm

2

Page 23

LD- 19X10-21

A

A

(

)

13. Others

1) Lot No. Label ;

The label that displays SHARP, product model (LK520D3LZ17), a product number is stuck on the back of the

module.

LK520D3LZ17

7X S00001 X

production year(the last figures of the Christian Era)

2) Packing Label

社内品番:

LotNO.

4S

Bar code

LK520D3LZ17 X (①)

(1T)2007.*.**(②)

Bar code

Quantity:

Bar code

ユーザ品番

シャープ物流用ラベルです。

(Q)

8

3) Adjusting volume has been set optimally before shipment, so do not change any adjusted value.

If adjusted value is changed, the specification may not be satisfied.

4) Disassembling the module can cause permanent damage and should be strictly avoided.

5) Please be careful since image retention may occur when a fixed pattern is displayed for a long time.

6) The chemical compound, which causes the destruction of ozone layer, is not being used.

7) Cold cathode fluorescent lamp in LCD PANEL contains a small amount of mercury. Please follow local

ordinances or regulations for disposal. This sentence is displayed on the backside of the module.

8) When any question or issue occurs, it shall be solved by mutual discussion.

9) This module is corresponded to RoHS.

ModuleNo.

Barcode

LotNo.

production month (1-9, X,Y, Z)

① Management No. (LK520D3LZ17X)

② Lot No. (Date)

③ Quantity

pcs(③)

How to express Lot No.

○○ ○ ○ ○ ○ ○

○

Serial No.

Management No.

Page 24

LD- 19X10-22

14. Carton storage condition

Temperature 0°C to 40°C

Humidity 95%RH or less

Reference condition : 20°C to 35°C, 85%RH or less (summer)

: 5°C to 15°C, 85%RH or less (winter)

• the total storage time (40°C,95%RH) : 240H or less

Sunlight Be sure to shelter a product from the direct sunlight.

Atmosphere Harmful gas, such as acid and alkali which bites electronic components and/or

wires must not be detected.

Notes Be sure to put cartons on palette or base, don’t put it on floor, and store them with

removing from wall

Please take care of ventilation in storehouse and around cartons, and control

changing temperature is within limits of natural environment

Storage life 1 year

Page 25

LD-19X10-23

Page 26

Fig.1 LK520D3LZ17

OUTLINE DIMENSIONS

LD-19X10-24

Page 27

Records of Revision

Standards

No.

LDK-123E 29-Oct-07

Revision

Date

Rev.

Mark

- first Edition Model Addition : LK520D3LZ17

Contents of Revision

LDK-123E-2

Page 28

Applicable Model List

The grade inspection standard applies to the models as below

Applicable Model

LK520D3LZ17

Revision

Mark

LDK-123E-3

Page 29

Incoming Inspection for TFT-LCD Module

1. Scope

- These Incoming Inspection Standards shall apply to TFT-LCD Modules supplied by AVC LCD Group.

Sharp Corporation to LG Electronics INC

2. Inspection Lot

- Quantity per shipment lot is ONE Inspection lot.

3. Incoming Inspection Condition

3.1 Condition of Lot Judgement

- Unless otherwise agreed in writing, the method of incoming inspection shall be in accordance with

a sampling inspection based on ISO 2859-1

- Sampling Table : Table in ISO 2859-1

- Sampling Type : Single Sampling Plan

- Inspection Level : Level Ⅱ, Normal Inspection

- Acceptable quality level (AQL) : Major defects: AQL: 0.4

: Minor defects: AQL: 1.0

- Defects are classified as major defect and minor defect according to Classification on Defects Minor & Majors of item# 6.

a) Major defect: Major defect is a defect that is likely to result in failure, or to reduce materially

the usability of the product for its intended purpose.

b) Minor defect: Minor defect is a defect that is assumed to be little or no obstacle to usability of inspection unit,

effective usage ro operation of the product.

3.2 Operational Inspection Condition

- The inspection shall be conducted in the standard operative condition described in the specification.

- The external illumination on the Module: 300 ~ 700lx (Standard 500lx)

- The viewing distance between center of panel surface on the Module and the eyes of the inspector.

*Refer to Fig.1 and Fig.2 [Inspection :Viewing Angle from Left to Right ± 45 degrees]

[1] Apply to Foreign material, Bright Dot and Black Dot.

[2] Apply to defect concerned with Mura (Display Uniformity)

- Backlight Luminance: Based on value which is desuribed in the specificatio.(Brightness Control : 100%)

- Ambient temperature: 24℃ ± 2℃ in principle

- Ambient humidity: 65 ± 5% RH in principle

Fig.1) Judgment position of Operational Inspection Inspector

Viewing Angle

the inspector shall be within ± 45 degrees from

Left to Right

LCD Module

[1]750±50mm

[2]2,000± 500 mm

: The surface of the Module and the eyes of

Eyes

Illuminance Meter

( 300 ~ 700 lx on this condition)

LDK-123E-4

Page 30

Fig.2) How to use ND Filter

r

r

[1] Apply to Bright Dot and Tiny Bright Dot (Small dots seem to be bright by foreign material)

ND filter is moved to the panel side closer and judged.

ND Filte

LCD Module

750 ± 50 mm

[2] Apply to defect concerned with Mura (Display Uniformity)

ND filter is moved to the eyes closer and judged.

ND Filte

LCD Module

2,000 ± 500 mm

3.3 Appearance Inspection Condition

*1: In the operational inspection condition, the distance between the Module and eyes of the inspector shall be

750mm or MORE. (Condition of lighting B/L and operating Module on White picture)

*2: In the operational inspection condition, the distance between the Module and eyes of the inspector shall be

750mm or MORE. (Condition of lighting B/L and operating Module on Black picture)

*3: The external illuminance of panel surface; 900-1500lx (Standard: 1200lx)

Shall be conducted with fluorescent lamp lighting on working bench. [Refer to Fig.3]

The visual observation shall be conducted with the judgement distance that is 350±100mm between the panel and

the inspector's eyes. (Condition of Non-operating)

Fig.3) Judgement position of Appearance Inspecion Inspector

Fluorescent Lamp

[Note] Applicable range of Appearance inspection is

out side by 3.0 mm from the effective display area.

Eyes

[Note] Scratch/Dent on the rear polarizer is not counted,

Illuminance Meter

(900 ~ 1500lx on this condition)

if it is not found from the front side by B/L lighting

condition.

350±100mm

LCD Module

LDK-123E-5

Page 31

4. Standards for Display Quality Inspection

4.1 Zone

L

H

4.2 Definition

a) Bright dot

Full-time lighting dot in the black display.

- Visible through 5% ND filter : Counted as Bright dot

- Not visible through 5% ND filter : Non count

b) Tiny bright dot

Small dots seem to be bright by foreign material

- Visible through 5% ND filter : Tiny bright dots(Counted as Bright dot)

- Not visible through 5% ND filter : Bright foreign material

c) Black dot

Dot which seems to come out in black on the white display and Red/Green/Blue monochromatic display.

There are full-dot black dot and half-dot one due to the multi-pixel structure.

・H and L are assumed all the effective display area.

Fig.4) Example: Full black dot & Half black dot

Half black dotFull black dot

d) Scratches on color filter

*White dot on the Black display.

- Visible through 5% ND filter : Tiny bright dots(Counted as Bright dot)

- Not visible through 5% ND filter : Bright foreign material

e) Scratches on black mask

*White dot around R/G/B dot (black mask part) on the black display.

- Visible through 5% ND filter : Tiny bright dots(Counted as Bright dot)

- Not visible through 5% ND filter : Bright foreign material

[Target Area]

Target area is from active area to 1.5mm (High density is NG)

Fig.5) Example: Torn color filter

Fig.6) Example: Torn black mask

f) Line defect (Vertical / Horizontal / Cross)

*All kinds of line defects such as Vertical, Horizontal or Cross are not allowed.

g) Display Mura (Non-Uniformity)

* Non-Uniformity of display brightness.

LDK-123E-6

Page 32

4.3 Bright dot

Check pattern

Black pattern

(Refer to Item# 4.2)

Acceptable total number of Bright dot

0

4.4 Black dot

Check pattern

Half Black dot(A)

Acceptable total number of Black dot

Full Black dot(B)

Joined Black dots(C)

Total=1/2×(A)+(B)+2×(C)

White pattern and at each

pattern of R, G and B (Refer

816

4

8

to Item#4.2)

[ Note ] Flashing dot is counted as a Black dot

[ Note ] Joined Black dots shall be based on “Explanation for Black Dot criterion and Judgement method.”

[ Note ] Joined more than 3 Black dots by Horizontal or Vertical shall be judged NG.

4.5 Distance of Black Dot

- Full Black dot,Joined Black dots - Full Black dot,Joined Black dots : Acceptable if it is more than 15mm

- Half Black dot - Half Black dot : Acceptable if it is Max 3 dots within 5mm φ

- Full Black dot,Joined Black dots - Half Black dot : Acceptable if it is more than 15mm

5. Appearance Inspection Criterion

[ Permissible Nnumber: N, Average Diameter(Fig.7): D (mm), Length(Fig.8): L (mm) ]

Item

Foreign material

(in the polarizer /

backlight / cell)

Bright Foreign material

(in the polarizer / cell)

Circular

Linear

Judgment Criterion

0.3≦D≦0.8 , N≦10

L≦3.0 , N≦3

0.1≦D≦0.5 , N≦10

Not visible through 5% ND filter.

Appearance Inspection

Condition

Condition of operation

(Refer to *1 of Item#3.3)

Condition of operation

(Refer to *1 & *2 of Item#3.3)

Condition of operation

(Refer to *2 of Item#3.3)

Scratches on the polarizer/glass

Dents on the polarizer/glass

Fig.7) Average diameter : D

a+b

D =

a

b

L≦10.0 , N≦4

0.3≦D≦0.8 , N≦10

0.3>D:No count

LDK-123E-7

Condition of Non operation

(Refer to *3 of Item#3.3)

Fig.8) Length : L

L = The longest position

L

Page 33

6. Classification on Defects Minor & Majors

Classifica

tion

Inspection item Criterion for defects / Judgment

A power supply voltage shall be a standard value described in the specification.

Defect type

Operating frequency

Current consumption

Contrast ratio

Display Inspection

Characteristic of electricity and mechanical

Scratches and dent

on the polarizer

Bubble in the polarizer

Foreign material

Bezel Appearance

(1) Does not meet the specified range in the specification

(2) Does not meet the specified range in the specification

(3) Does not meet the specified range in the specification

Correct pattern is not displayed when the display pattern is input.

(4)

(5) Vertical line defect

(6) Horizontal line defect

(7) Cross line defect

(8) Shall be accordance with the Item#

"5.Appearance Inspection Criterion"

(9) Shall be accordance with the Item#

"5.Appearance Inspection Criterion"

(10) Shall be accordance with the Item#

"5.Appearance Inspection Criterion"

(11) Irregular plating / lrregular Coating / Rust on the edge are ignored

(12) a)The lead wire is broken.

Major

Major

Major

Major

Major

Major

Major

Minor

Minor

Minor

Minor

Major

Criterion for External Quality

Damaged Part

b)Although the lead wire is not broken (not disconnected) and does not

affect the operation and reliability of LCD module it has scratch.

c)Failure is found concerning function or performance,

Major

or product value is impaired in appearance.

Bright dot

Scratch on the color filter

Scratch on the black mask

Black dot

Display Mura

(13) Exceed permissible value

(14) Exceed permissible value

(15) Exceed permissible value

(16) Exceed permissible value (Flashing dot is classified as a black dot)

(17) There should not be Non-uniformity through 5%ND filter.

(Non-uniformity)

(18) α zone shall not remain for more than 3seconds soon after cutting

power supply

(External illuminance condition : illuminance 300~700lx(standard 500lx))

Criterion for Display Quality

Electric charge retention Minor

Within 3

seconds

[Inspection condition]

-Signal power is off

α zone

20mm -B/L power is on

Minor

Minor

Minor

Minor

Minor

Minor

LDK-123E-8

Page 34

Classificat

ion

Inspection item

Defect typeCriterion for defects /determinations

Criterion for Display Quality

PI Repellent

Long time

afterimage

Short time

afterimage

Shadowing

(19) One dot-shaped black stain is considered as “good product”.(But, if it seems to be

bright dot when changing viewing angle, it’ll be counted as small bright dot)

(20)

Afterimage of the former pattern is not disappeared within 10 seconds when a pattern was displayed

for 30 minutes and switch to another pattern.

(21) After display same pattern for 5 seconds, the afterimage is not disappeared within 10 seconds.

(22)

The brightness difference between A section and B section is visible through

10%ND filter.

B

(700, 475)

A

(1220, 605)

Ambient: V64

Window : V255

Minor

Minor

Minor

Minor

Outline

(23) Does not meet specified range in the specification

dimensions

Weight

(24) Does not meet specified range in the specification

(25) A) The one that is forgetting, misprinting or not-readable.

Others

Rating label

(Readable one should be a good one.)

(Sealing/Display

label)

B) As for the display label, peel-off is more than the degree of 1/10 of total area .

(except for legible one among discoloration of display label.)

[Note]Regarding the items to use limit samples, limit samples should have priority over others

7.Others

In case any doubts arise on the items, both Parties shall cooperate in an effort to settle it down.

Major

Major

Major

Minor

LDK-123E-9

Page 35

Explanation for Black Dot criterion and Judgment method

R

GBR

GBR

GBR

GBR

GBR

G

R

GBR

G

R

GBR

GBR

G

d

e

R

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

G

R

GBR

GBR

GBR

GBR

GBR

G

R

GBR

GBR

GBR

GBR

GBR

GBR

G

GNGNGRGBR

GBR

GBR

GBR

GBR

GBR

G

GNGNGRGBR

GBR

GBR

G

j

p

Judgment Method

A half dot not lit on each color

screen of R, G or B is judged

Half Black dot with one defect.

Example

R half black dot

G half black dot

B half black dot

one dfect one defect one defect

Judgment Method

Dots seemed continuous

with Horizontal and Slant

on each color screen of

R, G or B is judged

Full Black dot with one defect.

Example

B

Full black dot Full black dot Full black dot

one defect one defect one defect

B

A one dot not lit on each color

screen of R, G or B is judge

Full Black dot with one defect.

Dots seemed continuous

with Horizontal and Slant

on each color screen of

R, G or B is judged

Joined Black dots with

one defect.

A black dot within a pixel on

each color screen of R, G or B

(black mode opened one dot)

is counted one defect.

Distance between the black

dots is not judged.

1 pixel = 1 dot each of R+G+B

Dots seemed joined with

Vertical on each color screen

of R, G or B are NG.

R full black dot G full black dot

one dfect one defect one defect

Joined Black dots

one defect

Joined Black dots

one dfect

B full black dot

Joined Black dots

one defect

Joined Black dots

one dfect

B

Joined Black dots

one defect

Distance between the

black dots exceeding

one pixel on the white

screen is re

ected.

Full black dot

one defect

Full black dot

on

defect

B

Full black dot Full black dot Full black dot

one defect one defect one defect

B

Full black dot Full black dot

one defect one defect

B

Distance to

be judged

Distance to

be judged

Joined 3 dots on each color

screen is judged

of R, G or B are NG.

Distance between black dot

"A" to black dot "B" is

15mm or more in a white

icture

N

N

More than15mm

A

Black dot [A]

・Full Dot

・Joined Dot

B

Black dot [B]

・Full Dot

・Joined Dot

・Half Dot

Half black dot is within 3

pieces in the diameter of

5mm in a white picture

Distance between the

black dots is NG

max 3 dots

Distance between the

black dots is ok

Distance between the

black dots is OK

Circle diameter

of 5mm

Distance between the

black dots is NG

Distance between the

black dots is ok

Distance between the

black dots is NG

B

B

LDK-123E-10

Loading...

Loading...