LH5324000

CMOS 24M (3M × 8) MROM

FEATURES

•• 3,145,7 28 × 8 bi t organ izatio n

•• Access time: 150 ns (MAX.)

•• Supply curre nt :

– Operating: 65 mA (MAX.)

– Standby: 100 µA (MAX.)

•• TTL compatible I/O

•• Three-state output

•• Single +5 V Power supply

•• Static operation

•• When the address in put at both A

19

an d

A

20

is high leve l , outputs become high

impedan ce irresp ectiv e o f CE o r OE.

•• Package:

42-pi n , 600 -mil DIP

•• Others :

– Non programmab le

– Not de sign ed o r rate d as rad iatio n

hardene d

– CMOS process (P typ e sil icon

substrate)

DESCRIPTION

The LH53 24000 i s a 24M-bit CMOS mask-programmable ROM organized as 3,145,728 × 8 bits. It is

fabricated using silico n-gate CMOS process technology.

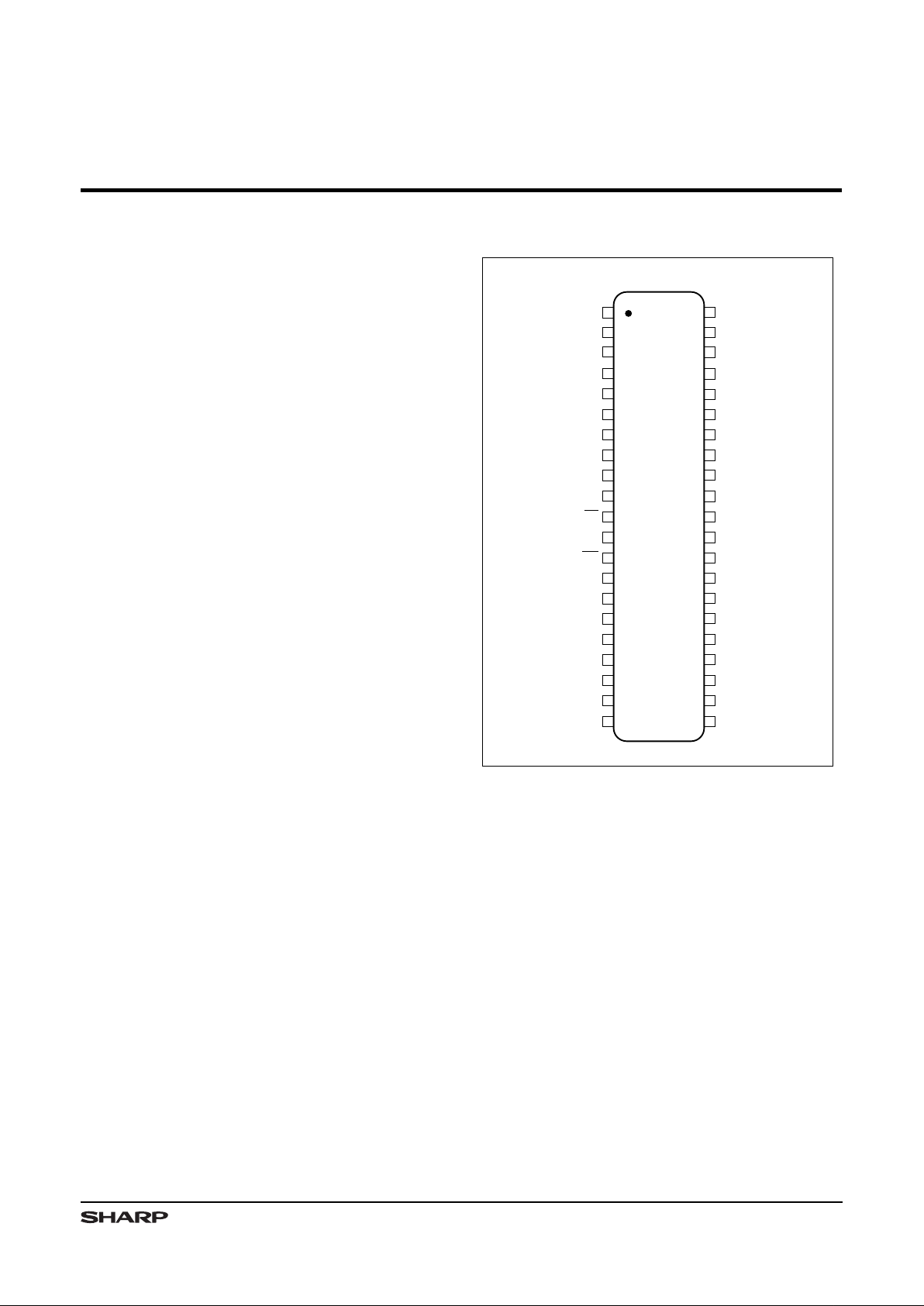

PIN CONNECTIONS

532400-1

TOP VIEW

2

3

4

5

8

9

A

2

A

5

39

38

37

36

35

34

31

28

A

7

A

6

6

7A

3

A

4

33

32

A

10

A

11

A

13

A

15

GND

NC

10

11

12

41

40 A

9

A

1

13 30 A

-1

29 D

7

OE

A

0

CE

A

12

42-PIN DIP

14

15

16

17

18

19

20

21

25

22

27

26

24

23

NC

D

5

NC

D

4

D

2

NC

NC

GND

NC

D

1

D

0

D

3

NC V

CC

A

8

A

14

A

16

D

6

421

A

17

A

18

A

19

A

20

Figure 1. Pin Connecti ons

1

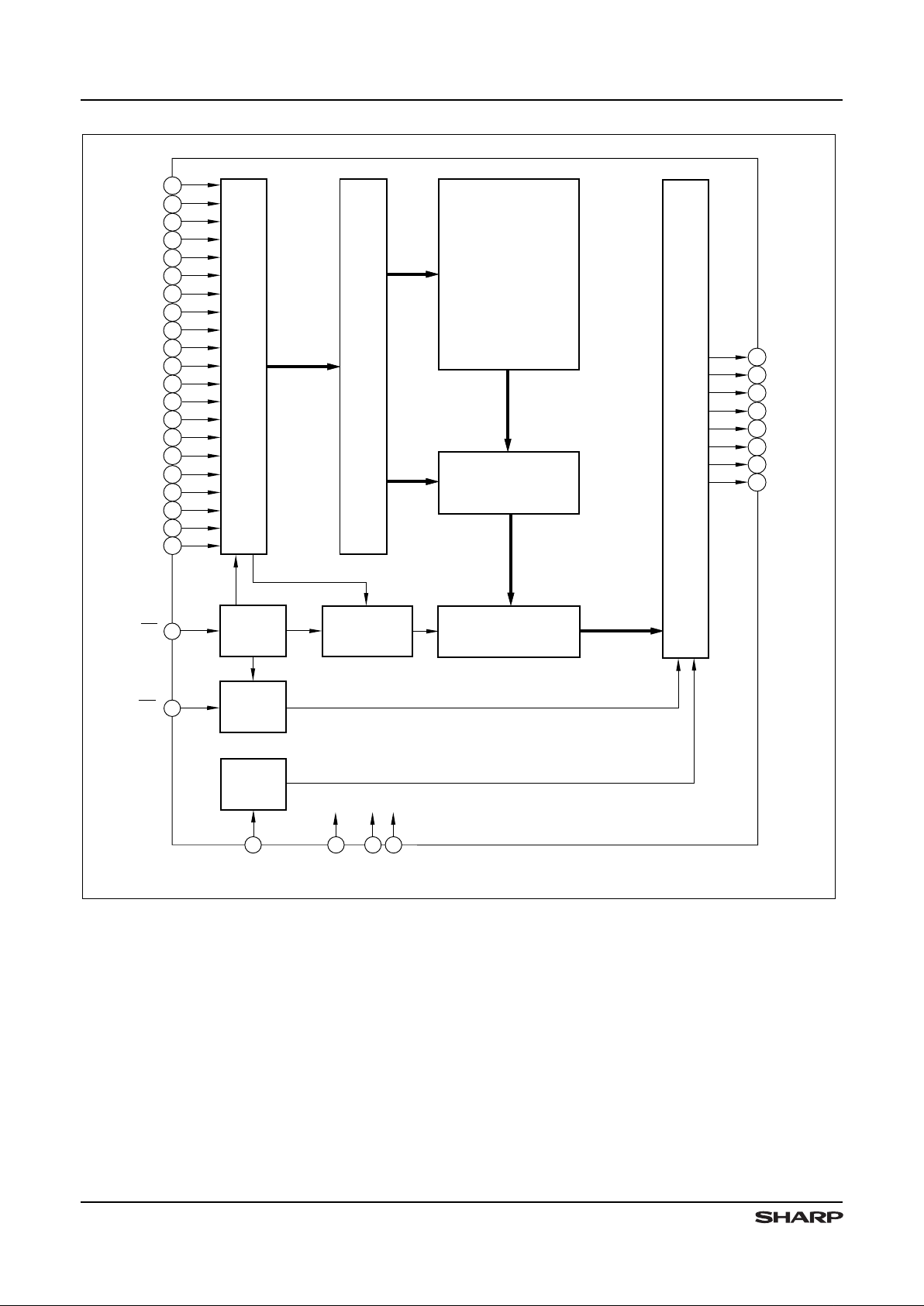

532400-2

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

A

7

A

6

V

CC

A

4

MEMORY

MATRIX

(3,145,728 x 8)

SENSE AMPLIFIER

GND

A

5

A

13

ADDRESS BUFFER

A

0

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

A

14

A

15

TIMING

GENERATOR

A

16

A

-1

DATA SELECTOR/OUTPUT BUFFER

OE

BUFFER

ADDRESS

BUFFER

OE

CE

A

17

A

19

A

18

A

20

37

38

39

40

4

7

8

9

3

6

41

5

36

10

35

34

33

2

42

1

32

11

13

30

22

31

12

D

3

D

2

D

1

D

7

D

6

D

4

D

5

D

0

25

18

16

14

20

29

23

27

Figure 2. LH5324000 Block Diagram

PIN DESCRIPTION

SIGNA L PIN NAME

A-1 - A

20

Addr ess in put

D

0

- D

7

Data ou tput

CE

Chip en abl e in pu t

OE Outp ut e nab le inp ut

SIGNAL PIN NAME

V

CC

Power pi n (+ 5 V)

GND

Groun d

NC

No co nne cti on

LH5324000 CMOS 24M (3M x 8 ) MROM

2

TRUTH TABLE

CE OE A-1 - A

18

A

19

A

20

DATA

OUTPUT

SUPPLY

CURRENT

D0 - D

7

H X X X X High-Z Standby (ISB)

L H X X X High-Z Operating (I

CC

)

L L X L L Output Operating (I

CC

)

L L X L H Output Operating (I

CC

)

L L X H L Output Operating (I

CC

)

L L X H H High-Z Operating (I

CC

)

NOTES:

1. X = Don’t care; High-Z = High-impedance

2. When t he address inputs become HIGH to both A19 and A20, the data does not exist in this address area,

the data out puts become "High Impedance".

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING UNIT

Suppl y v olt age V

CC

-0.3 to +7.0 V

Input vol tage V

IN

-0.3 to VCC + 0.3 V

Output vo lta ge V

OUT

-0.3 to VCC + 0.3 V

Operat ing te mpe ratu re T

OPR

0 to +70

°C

Storag e t emp era ture T

STG

-65 to +150

°C

RECOMMENDED OPERATING CON DITIONS (TA = 0 to +70°C)

PARAMETER SYMBOL MIN. TYP. MAX. UNIT

Suppl y v olt age

V

CC

4.5 5.0 5.5 V

DC ELECTRICAL CHARACTERISTICS (VCC = 5 V ± 10%, TA = 0 to +70°C)

PARAMETER SYMBOL CONDITIONS MIN. MAX. UNIT NOTE

Input ‘Hi gh’ voltage

V

IH

2.2 VCC + 0.3 V

Input ‘Lo w’ voltage V

IL

-0.3 0.8 V

Output ‘H igh ’ vol tag e V

OH

IOH = -400 µA

2.4

V

Output ‘L ow’ v olt age V

OL

IOL = 2 .0 mA

0.4 V

Input leakage current | I

LI

|VIN = 0 V to V

CC

10

µA

Output le aka ge cur ren t | I

LO

|V

OUT

= 0 V to V

CC

10 µA1

Operat ing cu rre nt

I

CC1

tRC = 15 0 n s

65

mA 2

I

CC2

tRC = 1 µs

55

Standb y c urr ent

I

SB1

CE = V

IH

2mA

I

SB2

CE = VCC - 0.2 V

100

µA

Input cap acitan ce C

IN

f = 1 MHz , tA = 25°C

10 pF

Output ca pac ita nce C

OUT

10 pF

NOTES:

1. CE = VIH, OE = V

IH

2. VIN = VIH or VIL, CE = VIL, output is open

CMOS 24M (3M x 8) MROM LH5324000

3

AC ELECTRICAL CHARACTERISTICS (V

CC

= +5 V ± 10%, TA = 0 to +70°C)

PARAMETER SYMBOL MIN. MAX. UNIT NOTE

Read c yc le t ime t

RC

150

ns

Addres s a cc ess ti me t

AA

150 ns

Chip e nab le acc es s ti me t

ACE

150 ns

Output en abl e d ela y t ime

t

OE

70 ns

Output ho ld time t

OH

5

ns

Output fl oat ing tim e

t

CHZ

60 ns

1

t

OHZ

60 ns

t

AHZ

70 ns

NOTE:

1. Determ ined by the time f or the output to be opened. (Irrespective of out put voltage)

AC TEST CONDITIONS

PARAMETER RATING

Input vol tage ampl itude

0.6 V to 2.4 V

Input sig nal rise time 10 ns

Input sig nal fall time 10 ns

Input ref erence level

1.5 V

Output reference level 0.8 V, 2.2 V

Output lo ad con dit ion

1TTL + 100 pF

NOTE:

It is recommended that a decoupling capacitor be connected between VCC and GND-Pin.

LH5324000 CMOS 24M (3M x 8 ) MROM

4

532400-3

t

OE

t

AA

D0 - D

7

t

OHZ

t

CHZ

t

RC

t

ACE

CE

t

OH

DATA VALID

(NOTE)

OE

A

-1

- A

20

(NOTE)

(NOTE)

NOTE: The output data becomes valid when the last

intervals, t

AA

, t

ACE

, or tOE, have concluded.

HI-Z = High Impedance.

HI-ZHI-Z

Figure 3. Byte Mode

532400-4

D

0

- D

15

t

OHZ

t

CHZ

CE

DATA VALID

OE

A

-1

- A

18

A19, A

20

t

AHZ

HI-ZHI-Z

HI-Z = High impedance.

NOTE: The output data becomes valid when the last

intervals, t

AA

, t

ACE

, or tOE, have concluded.

Figure 4. Word Mode

CMOS 24M (3M x 8) MROM LH5324000

5

LH532400

Device Type

D

Package

532400-5

Example: LH532400D (CMOS (24M 3M x 8) Mask-Programmable ROM, 42-pin, 600-mil DIP)

CMOS 24M (3M x 8) Mask-Programmable ROM

42-pin, 600-mil DIP (DIP42-P-600)

ORDERING INFORMATION

13.45 [0.530]

12.95 [0.510]

0.90 [0.035] TYP.

5.40 [0.213]

4.80 [0.189]

3.55 [0.140]

2.95 [0.116]

2.54 [0.100]

TYP.

0.60 [0.024]

0.40 [0.016]

0.30 [0.012]

0.20 [0.008]

DETAIL

DIMENSIONS IN MM [INCHES]

54.10 [2.130]

53.50 [2.106]

0° TO 15°

MAXIMUM LIMIT

MINIMUM LIMIT

4.55 [0.179]

3.95 [0.156]

15.24 [0.600]

TYP.

42DIP (DIP042-P-0600)

1 21

2242

42DIP

PACKAGE DIAGRAM

LH5324000 CMOS 24M (3M x 8 ) MROM

6

Loading...

Loading...