In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP devices shown in

catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

1

DESCRIPTION

The LH1692 is a 300-output TFT-LCD gate driver

IC.

FEATURES

• Number of LCD drive outputs : 300

• LCD drive output sequence :

Output shift direction can be selected

OG

1/OG300 or OG300/OG1

• Cascade connection :

Max. 4 cascades (internal counting system)

• Usable with both positive/negative power supplies

• Output mode selection

– Normal mode (1-pulse scanning)

– Continuous 2-pulse mode (2-pulse scanning)

– Jumping 2-pulse mode (2-pulse scanning)

• LCD drive voltage : +16.0 to +42.0 V

• Operating temperature : –30 to + 85 ˚C

• Package : 319-pin TCP (Tape Carrier Package)

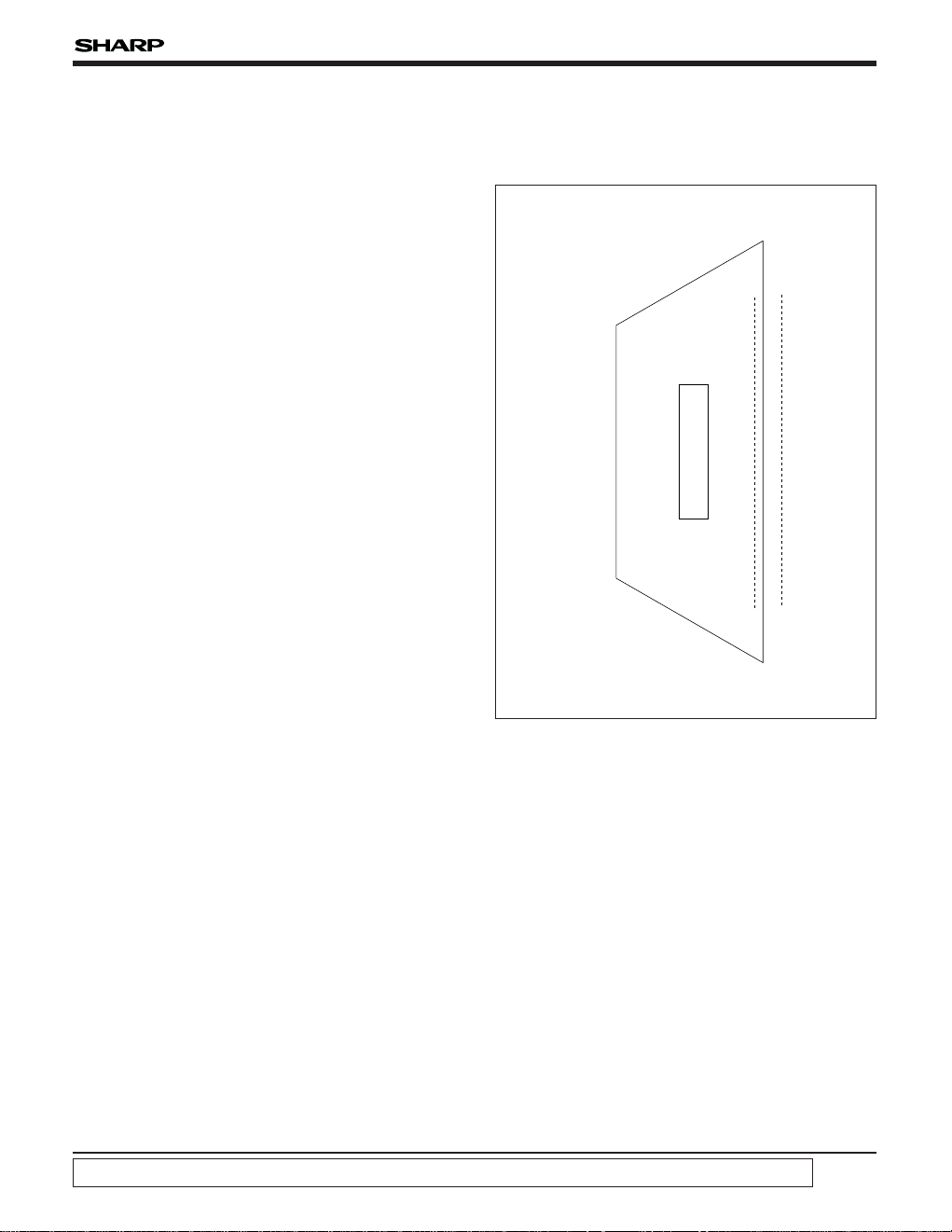

PIN CONNECTIONS

LH1692

LH1692

OG298

OG299

OG300

298

299

300

OG

1

OG2

OG3

1

2

3

CHIP SURFACE

VDD

VEE

VSS

VCC

VLS

TEST1

TEST2

CKV

SPV

CE1

CE2

R/L

MODE1

MODE2

V

LS

VCC

VSS

VEE

VDD

319

318

317

316

315

314

313

312

311

310

309

308

307

306

305

304

303

302

301

319-PIN TCP

TOP VIEW

NOTE :

Doesn't prescribe TCP outline.

300-output TFT-LCD Gate Driver IC

LH1692

2

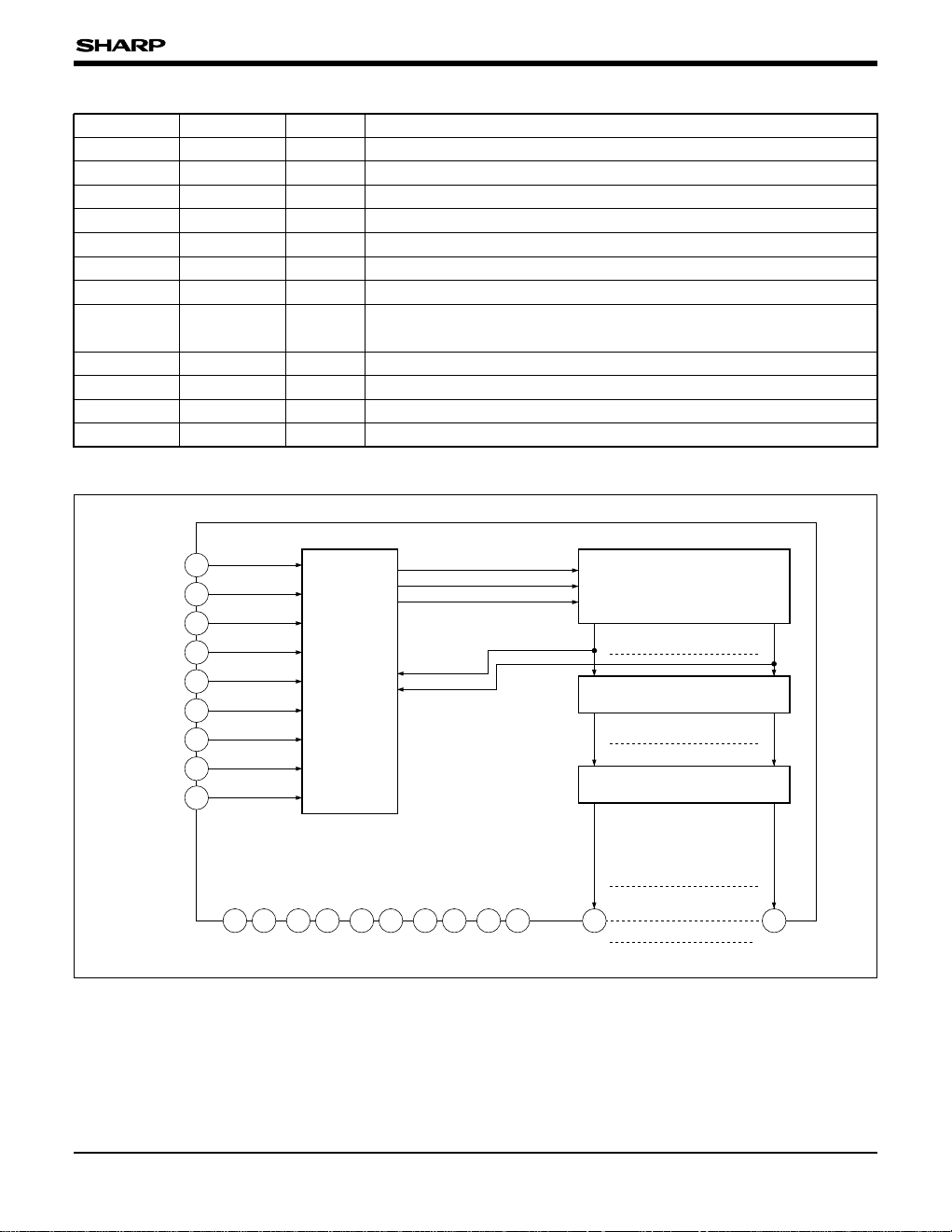

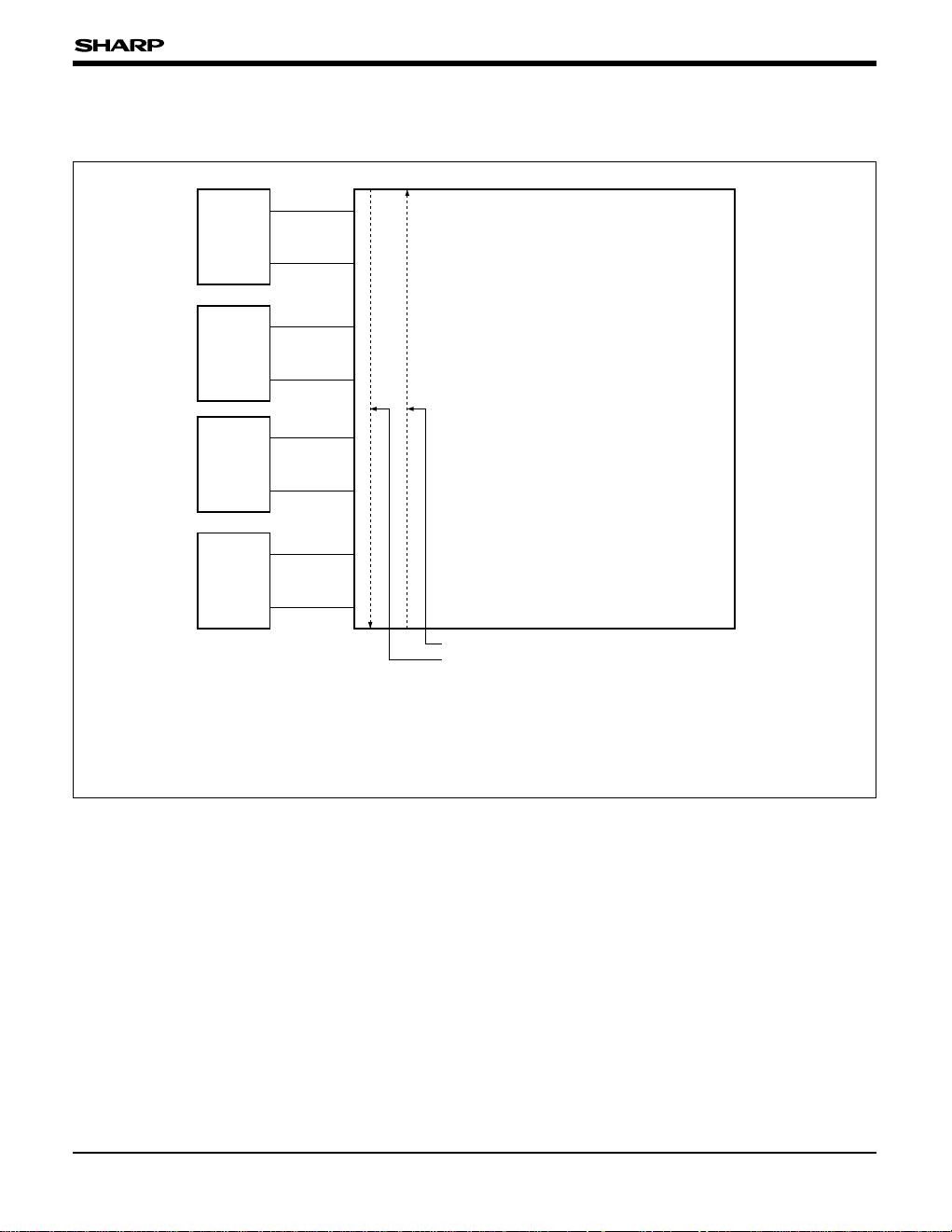

BLOCK DIAGRAM

PIN NO. SYMBOL I/O DESCRIPTION

1 to 300 OG

1-OG300 O LCD drive output pins

301, 309 V

DD – Power supply pins for LCD drive

302, 318 VEE – Power supply pins for LCD drive

303, 317 V

SS – Power supply pins for logic system

304, 316 VCC – Power supply pins for logic system

305, 315 V

LS – Power supply pins for input level shifter

309, 310 CE

2, CE1 I Cascade sequence setting pins

311 SPV I Vertical scanning start pulse input pin

312 CKV I Vertical shift clock input pin

313, 314 TEST

2, TEST1 I IC test pins

301

V

DD

306

307

MODE

2

MODE1

R/L

CE

2

CE1

SPV

CKV

TEST

2

TEST1

308

309

310

311

312

313

314

V

DD

319 305

V

LS VLS

315 304

V

CC VCC

316 302

V

EE VEE

318 303

V

SS VSS

317

OG

1

1

OG

300

300

OUTPUT CIRCUIT

LEVEL SHIFTER

BI-DIRECTIONAL SHIFT

REGISTER

CONTROL

LOGIC

1 300

1 300

1 300

Pin for selecting bi-directional shift register and setting cascade

sequence

IR/L308

Output mode selection pinsI

MODE2, MODE

1

306, 307

PIN DESCRIPTION

LH1692

3

BLOCK FUNCTION

Control Logic

Used to create signals necessary for mode selecting signal, cascade sequence setting

signal and for operation of bi-directional shift register.

Bi-directional Shift

Register

Used as transfer circuit of LCD drive output start signal. It is possible to set LCD drive

output sequence of OG

1/OG300 direction or OG300/OG1 direction.

Level Shifter

Used as circuit which shifts LCD drive output signals transferred by bi-directional shift

register to V

DD-VEE level.

Output Circuit Configured with output buffers to output VDD-VEE level.

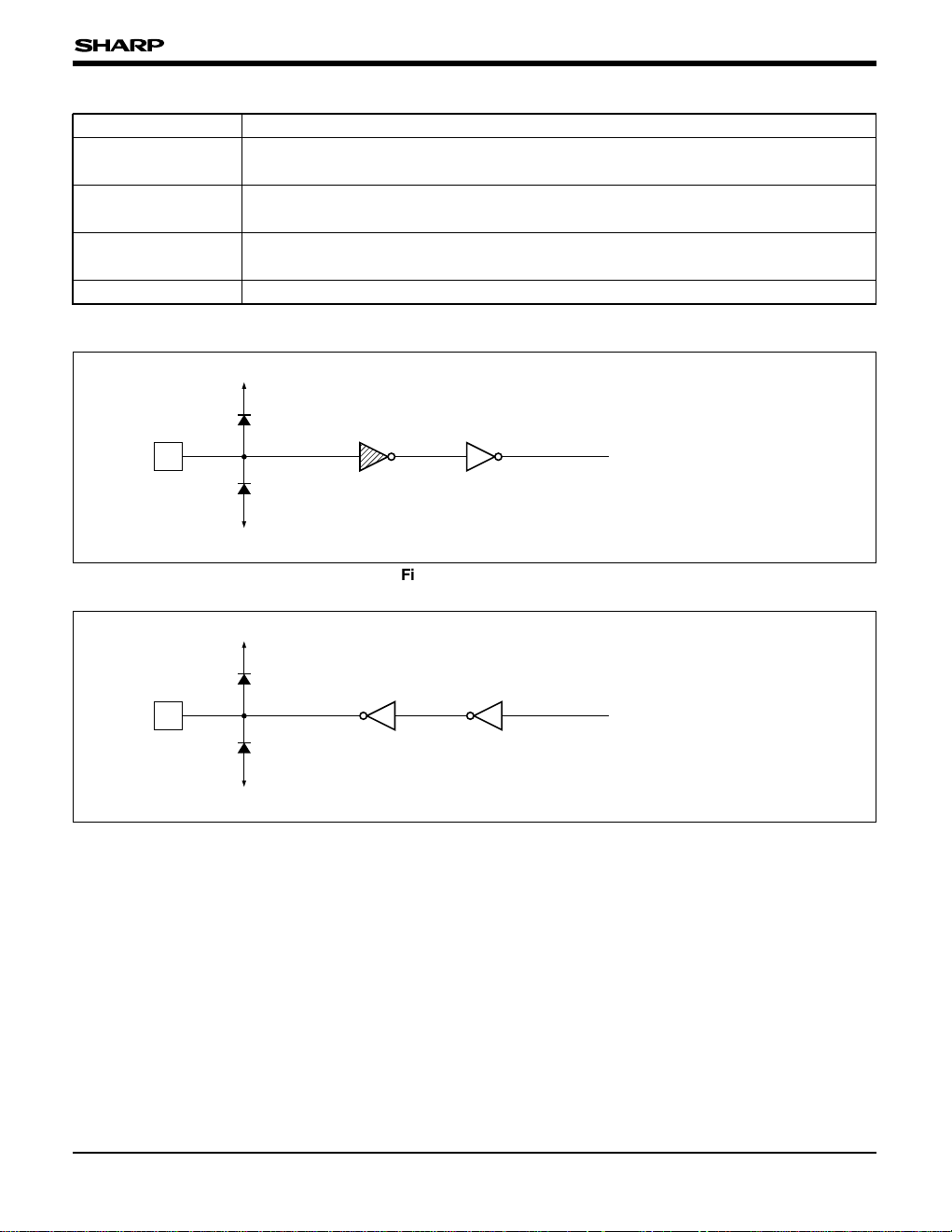

INPUT/OUTPUT CIRCUITS

I

V

LS

Level Shifter

(V

LS-0 V/VCC-VSS)

Internal Logic

(VCC-VSS)

V

SS

To Internal Circuit

Fig. 1 Input Circuit

¿Applicable pins¡

SPV, CKV, CE1, CE2,

R/L, MODE

1, MODE2,

TEST

1, TEST2

O

V

DD

(VDD-VEE)

VEE

From Internal Circuit

Fig. 2 Output Circuit

¿Applicable pins¡

OG

1-OG300

FUNCTIONAL OPERATIONS OF EACH BLOCK

LH1692

4

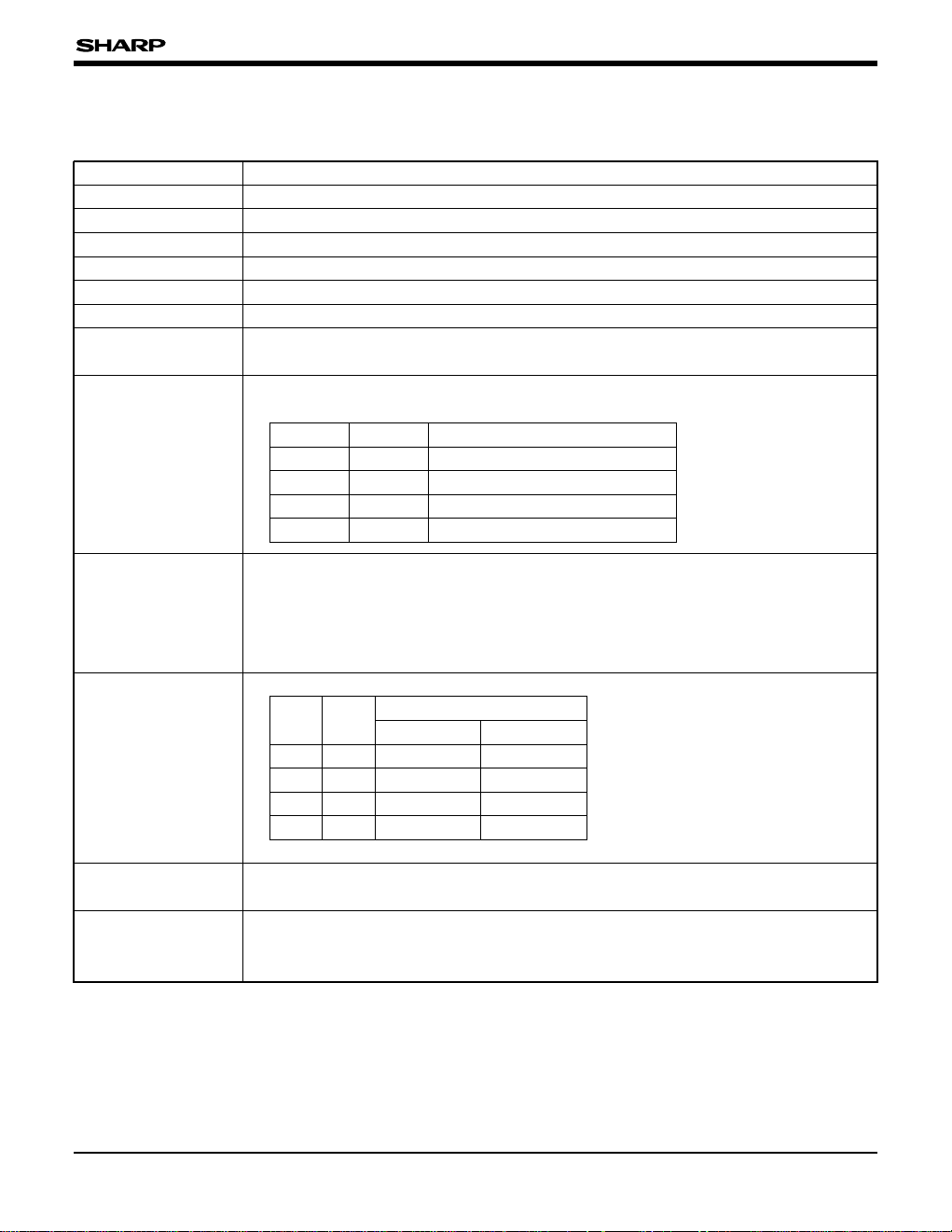

SYMBOL FUNCTION

V

DD Used as power supply pin for high level LCD drive.

V

LS Used as power supply pin for input level shifters.

VCC Used as power supply pin for logic system, normally connected to VSS + 5.0 V.

V

EE Used as power supply pin for low level LCD drive.

VSS Used as logic system power supply pin.

CKV Used as vertical shift clock pulse input pin.

SPV

Used as vertical scanning start pulse input pin. (At least, input one cycle of CKV during "L"

period of SPV.)

MODE

1

MODE2

Used as input pins for selecting output mode.

Output mode is set as shown in the table below by setting MODE1 pin and MODE2 pin.

R/L

Used as input pin for selecting the shift direction of bi-directional shift register and for

setting the sequence of cascade connection.

LCD drive outputs shift from OG

1 to OG300 when set to "H". LCD drive outputs shift from

OG

300 to OG1 when set to "L". At the same time, cascade sequence is set as shown in

the table below.

CE

1

CE2

Used as input pins for setting of chip cascade sequence. (Max. 4 cascades)

With above setting, sets the cascade sequence signal inside the IC.

TEST

1

TEST2

Used as input pins for IC testing.

Must be set to "H".

OG

1-OG300

Used as output pins for LCD drive output, and which output data at 2 levels.

• Selecting data is output at VDD level .

• Non-selecting data is output at V

EE level .

MODE

1 MODE2 Output mode

H H Normal mode (1-pulse scanning)

L H Continuous 2-pulse mode

H L Jumping 2-pulse mode

L L Set all outputs to V

EE level.

CE

1

Cascade sequence

R/L = "H"

1st

2nd

R/L = "L"

4th

3rd

H

L

L 1st4th

H 2nd3rdL

L

H

H

CE

2

FUNCTIONAL DESCRIPTION

Pin Functions

LH1692

5

TFT-LCD Panel

Scanning Direction When R/L = "L".

Scanning Direction When R/L = "H".

OG

1

OG300

OG1

OG300

OG1

CE1 = "H"

CE

2 = "H"

CE

1 = "L"

CE

2 = "H"

CE

1 = "H"

CE

2 = "L"

CE

1 = "L"

CE

2 = "L"

OG

300

OG1

OG300

At this time, normal mode (scanning with 1 pulse) is set when MODE1 = "H" and MODE2 = "H",

jumping 2-pulse mode (scanning with 2 pulses) is set when MODE

1 = "H" and MODE2 = "L",

continuous 2-pulse mode (scanning with 2 pulses) is set when MODE

1 = "L" and MODE2 = "H", and

output V

EE level is set when MODE1 = "L" and MODE2 = "L".

*

Functional Operations

(1) Example of Cascade Sequence (One Side Assembled)

Loading...

Loading...