Page 1

29LF-92E

SERVICE MANUAL

SE0029LF92E00

Issued: 28th July 2004

AK- 45 CHASSIS

PAL B/G / SECAM L/L’, B/G, D/K SYSTEM COLOUR TELEVISION

MODEL 29LF-92EC/IT

In the interests of user safety (required by safety

regulations in some countries) the set should be restored to its original condition and only parts identical to those specified should be used.

In order to service the model 29LF-92E, refer to

the AK-45 Chassis Service Manual

(SE00AK45CHA00).

CONTENTS

ELECTRICAL SPECIFICATIONS ........................................................................................ 3

IMPORTANT SERVICING NOTES ...................................................................................... 4

CONTROLS & TERMINALS ................................................................................................ 5

PRINTED WIRING BOARD LAYOUT ................................................................................. 7

PARTS LISTING ................................................................................................................... 8

HOW TO UPDATE THE TECHNICAL INFORMATION ...................................................... 15

SHARP CORPORATION

1

This document has been published to

be used for after sales service only.

Page 2

29LF-92E

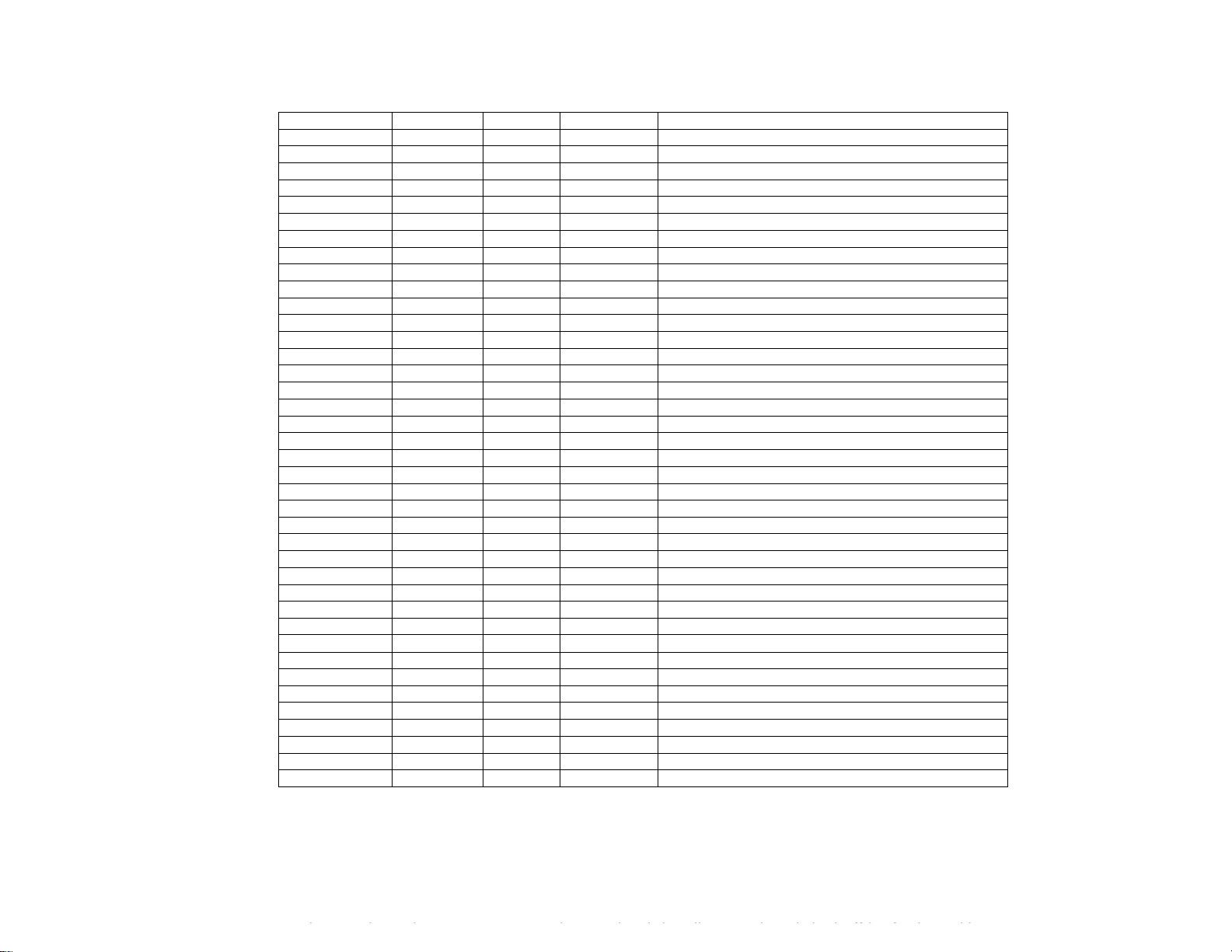

SERVICE MANUAL UPDATE LOG SHEET

Technical Report No.

Technical Bulletin No.

Cause / Solution

Part No.

Page No.

Application

Data /Serial No.

Use this page to keep any special servicing information as Technical Report (Bulletin), Technical Information, etc.

If only part number changes are required, just change part number directly the part number in the Parts Listing Section.

If you need more information, please refer to the Technical Report (Bulletin).

2

Page 3

ELECTRICAL SPECIFICATIONS

29LF-92E

•Power Input .................... 220V-240 Volts AC 50 Hz

•Power Consumption

Normal Operation (Method IEC60107) ............... 83 W

Stand-by Operation .......................................... < 4 W

•Audio Power Output Rating (MPO) / Impedance

Internal Left Speaker ................................. 10 W, 7 Ω

Internal Right Speaker ............................... 10 W, 7 Ω

•Speakers

Full range (2 pcs) ................................... 60 x 120 mm

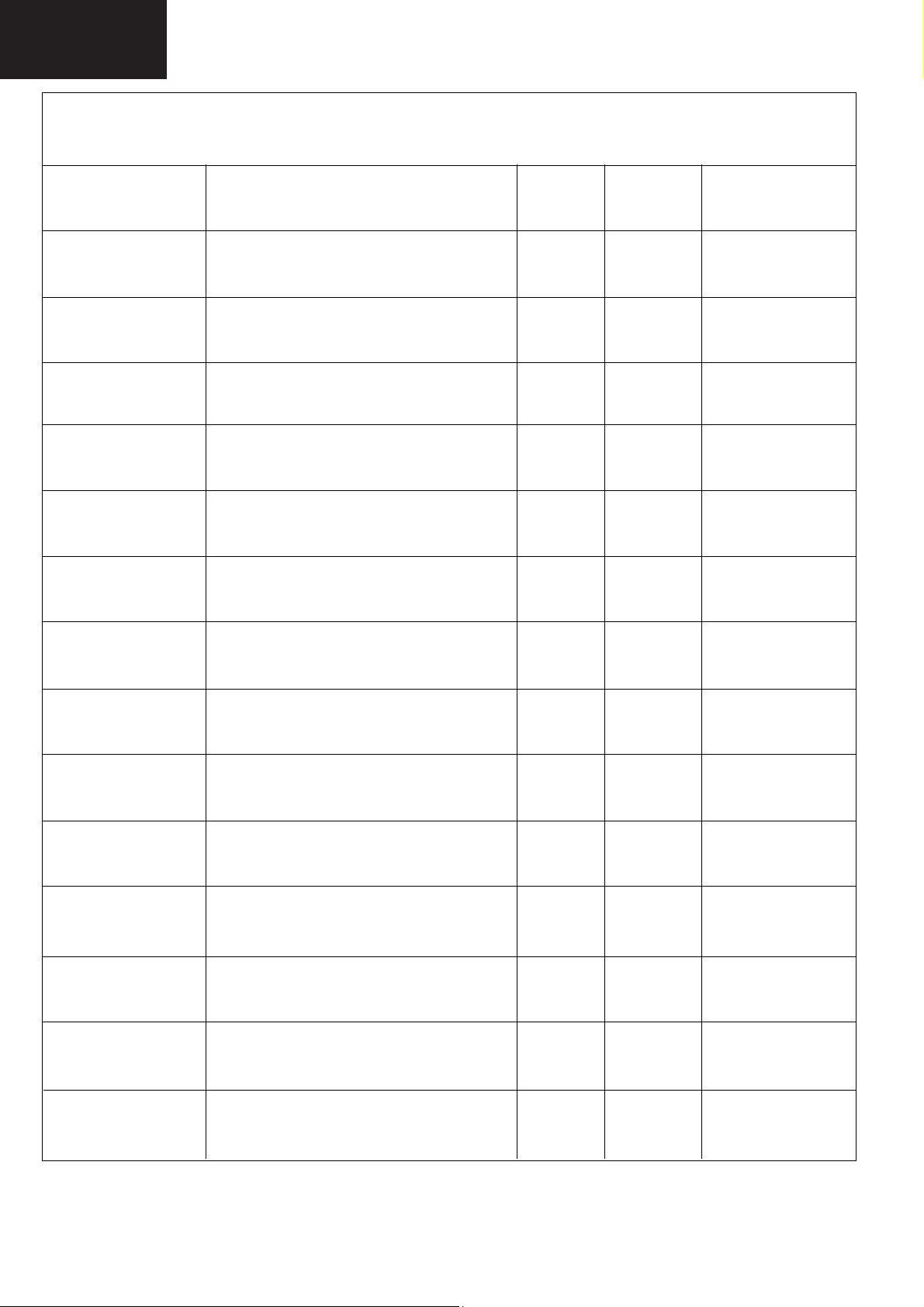

•Convergence (Maximum Misconvergence)

AREA 29”

A0.4

BC 1.0

DE 1.0

FGHJ 1.5

KLMN 1.3

F’G’H’J’ 1.3

STUV 1.0

•Picture Intermediate frequency

L’ ................................................ 33.9MHz

L, B/G, D/K .............................. 38.9MHz

•Sound Carrier Trap

L’ ................................................ 40.4MHz

L, D/K ......................................... 32.4MHz

B/G ............................................ 33.4MHz

•Adjacent Sound Carrier Trap

L’ ................................................ 32.4MHz

L, D/K, B/G ................................ 40.4MHz

•Adjacent Picture Carrier Trap

L’ ................................................ 41.9MHz

L, D/K ...................................... 30.9MHz

B/G ............................................ 31.9MHz

mm

•Aerial Input Impedance

VHF/UHF ................. 75 ohm Unbalanced

•Tuning Ranges ..... 45.75MHz thru 855.25 MHz

VHF: S1 - S41 CH (Hiperband)

E2 - E12 CH / F2 - F10

UHF: E21 - E69 CH

•White Level

Apply the rated voltage at the rated frequency to the TV set, while it is receiving full white pattern RF signal of 60

dB/µV from its RF input via the pattern generator.

Turn all picture controls to maximum value. Measure the colour temperatures at the center of the screen by

using the colour analyzer.

29LF94EC: X=0.304 ± 0.015 Y=0.306 ± 0.015

29LF94EIT: X=0.290 ± 0.015 Y=0.300 ± 0.015

Specifications are subject to change without prior notice.

MODEL DESTINATION (Operation Manual Languages)

28LF-92EC: Czech, English, Hungarian, Polish, Romanian, Russian, Slovakian

28LF-92EIT: Italiano.

WARNING

The chassis in this receiver is partially hot. Use an isolation transformer between the line cord plug

and power receptacle, when servicing this chassis.

To prevent electric shock, do not remove cover. No user-serviceable parts inside. Refer servicing to

qualified service personnel.

3

Page 4

29LF-92E

Only qualified service personnel are allowed to carry out maintenance and repair of this receiver.

Servicing of High Voltage System and CRT

It is important that the static charge is removed from the high voltage system when carrying out work on the

receiver. This can be achieved by connecting a 10K resistor (with a suitably insulated lead) from the CRT

cavity connector to the CRT ground tag. This must be carried out with the AC supply disconnected from the

receiver.

Note the following:

•

• If the CRT has to be changed it MUST be replaced with the correct type for continued safe working.

• DO NOT lift the CRT by its neck.

• When handing the CRT, ensure that shatterproof goggles are worn.

• Ensure that the CRT is discharge before handling.

IMPORTANT SERVICING NOTES

The CRT in this receiver employs Integral Implosion Protection.

X-Ray

This receiver is designed to keep any x-ray emission to an absolute minimum. Some fault conditions and

servicing procedures may produce potentially hazardous x-ray radiation levels. This is a problem when in

close proximity to the receiver for long periods of time. To reduce any risks associated with this, please

observe the following precautions:

1. When undertaking any servicing on this chassis, DO NOT increase the EHT to more than 33 KV, (at a

instantaneous beam current of 1800 µA).

2. Ensure that during normal operation the EHT does not exceed 29.55 KV (at a beam current of 1800 µA).

This level has been preset in the factory. Always check that this level has not been exceeded after

carrying out any repair on the receiver.

3. DO NOT replace the CRT with any other type than that specified in the parts listing as this may cause

excessive x-ray radiation.

Before returning the receiver to the customer

In addition to the above checks, the following should also be carried out before returning the receiver to the

customer.

1. Inspect all the leads to ensure that they are dressed correctly and that they are not obstructed or pinched

by any other parts.

2. Ensure that all protective devices are in good condition. These will include nonmetallic control knobs,

insulating fish papers, cabinets backs, compartment covers or shields, mechanical insulators, etc.

4

Page 5

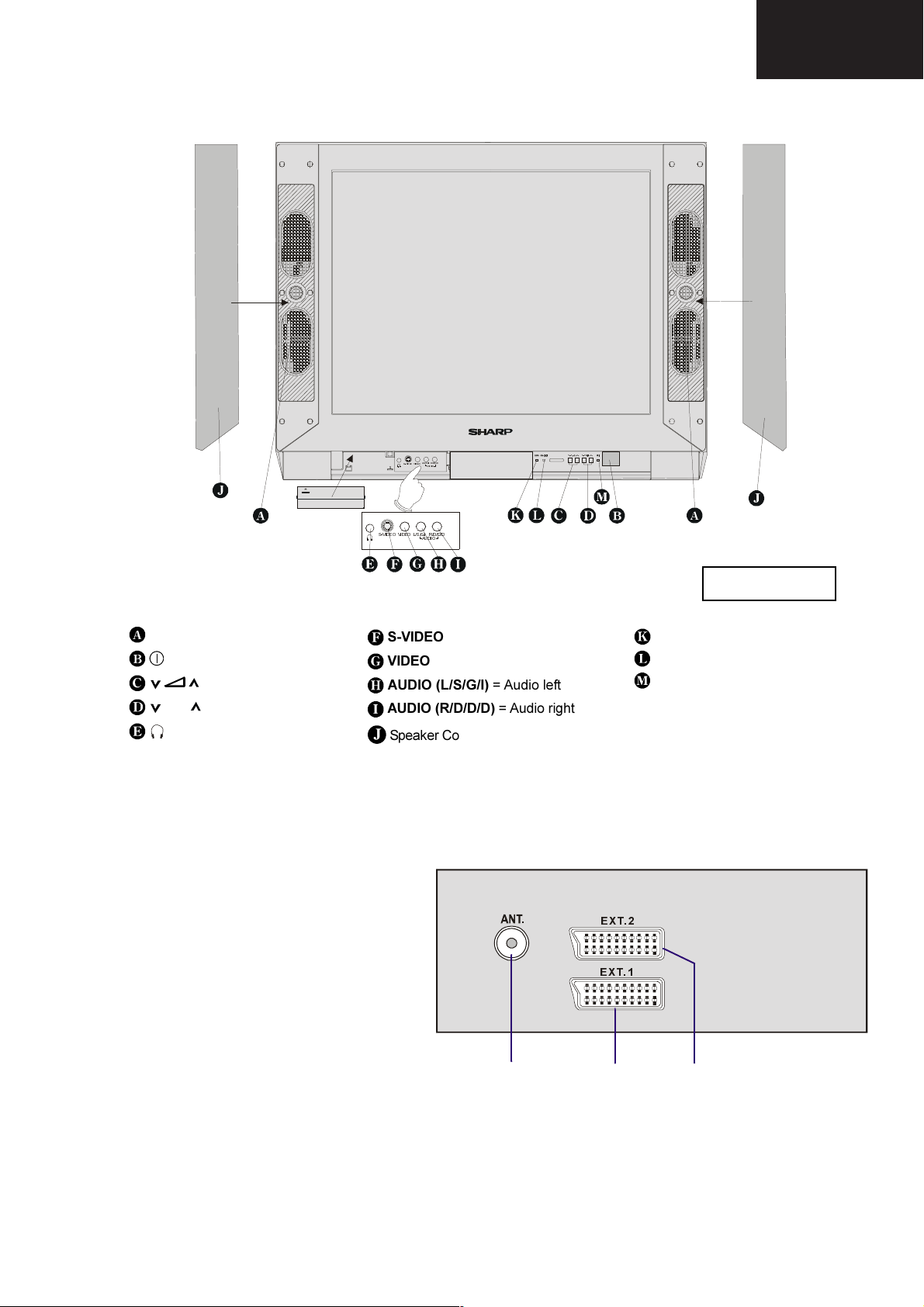

CONTROLS & TERMINALS

/6 *, 5' ''

69,'(29,'(2

$8',2

29LF-92E

Speakers (left + right)

= Power On / Off

= Volume -/+

CH = Program -/+

= Headphone 3,6 mm Ø

REAR TV

RF Input

1. Aerial terminal

21-pin In/Out

2. 21-pin Audio/Video (RGB) (EXT.1) With

PAL/SECAM/NTSC Video Input

3. 21-pin Audio/Video (EXT.2) With

PAL/SECAM/NTSC Video Input

/6*,5'''

9,'(2

69,'(2

$8',2

S-VIDEO

VIDEO

AUDIO (L/S/G/I) = Audio left

AUDIO (R/D/D/D) = Audio right

Speaker Covers

FRONT PANEL

Remote Control Indicator

Sound Indicator

Power Indicator

(;7

(;7

5

Page 6

29LF-92E

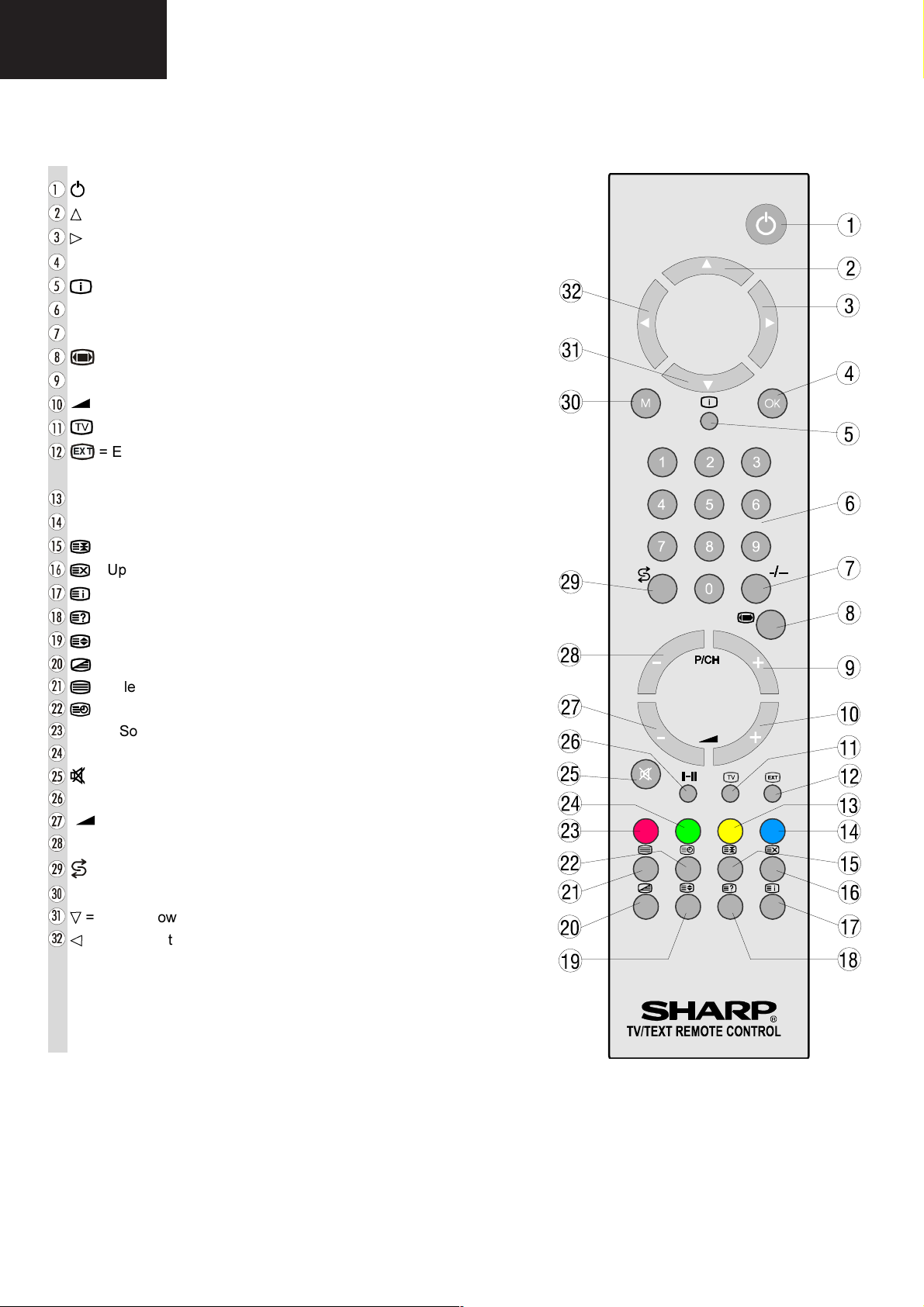

= Stand By

= Cursor Up

= Cursor Right

OK = OK

= Info (Program Menu)

0 - 9 = Direct Program

-/-- = Double Digit

= Wide mode button

P/CH+ = Program +

+ = Volume +

= TV / Quit Menu

(;7

= EXT button

(EXT-1, RGB, EXT-2, F-AV, S-VHS)

Yellow = Feature Menu

Blue = Installation Menu

= Hold

= Update

= Index Page

= Reveal

= Expand

= Mix

= Teletext

= Time

Red = Sound Menu

Green = Picture Menu

= Mute

I-II = Mono/Stereo - Dual I-II

- = - Volume

- P/CH = -Program

= Flash back button

M = Menu

= Cursor Down

= Cursor Left

REMOTE CONTROL

6

Page 7

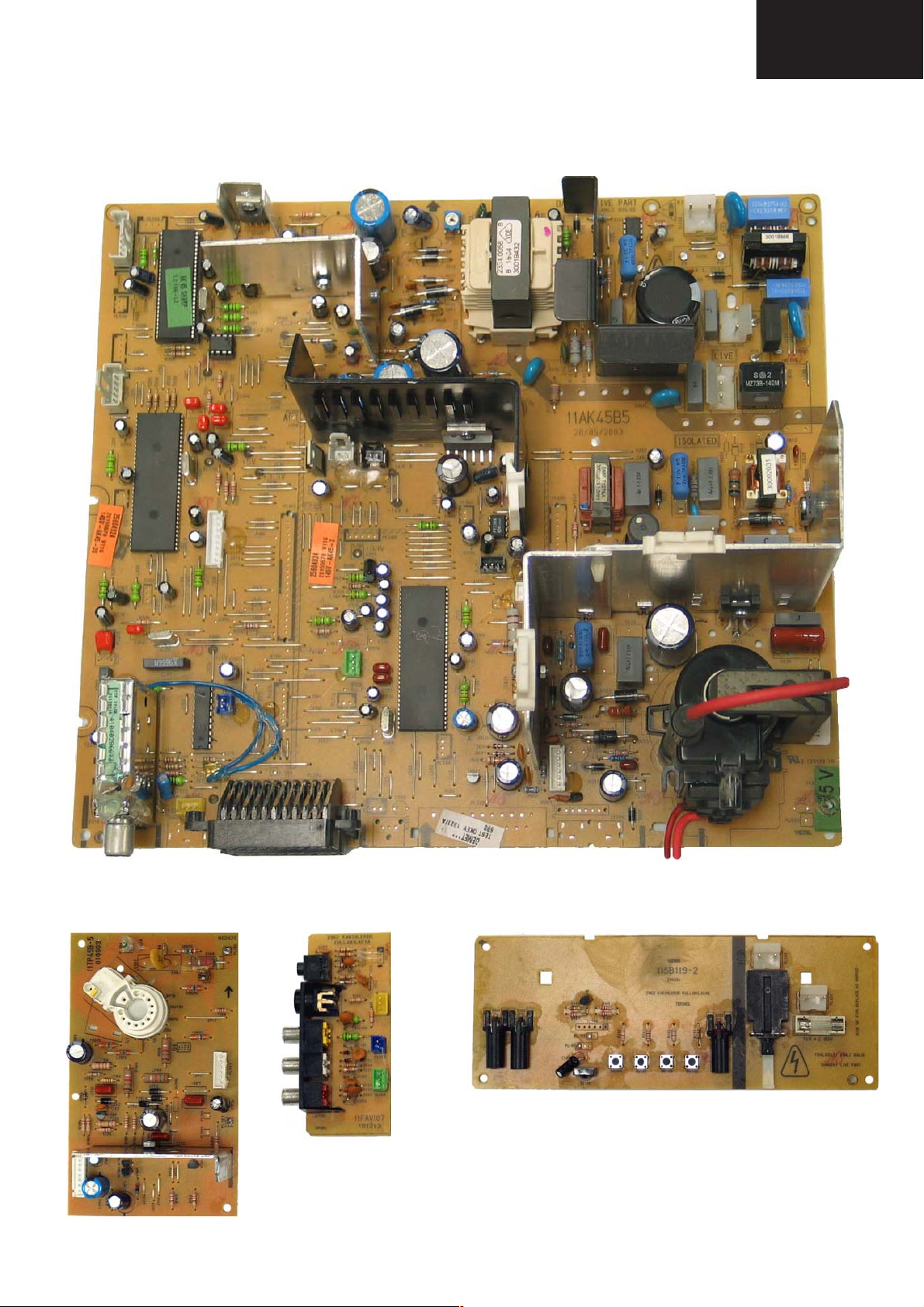

Mother Unit

29LF-92E

CHASSIS LAYOUT

CRT Unit Front AV Unit Keyboard Unit

7

Page 8

TABLE OF CONTENTS

1.INTRODUCTION ........................................................................................................................ 1

2.TUNER.......................................................................................................................................... 1

3.IF PART (TDA9885/86)............................................................................................................. 1

4.VIDEO SWITCH TEA6415....................................................................................................... 2

5.MULTI STANDARD SOUND PROCESSOR....................................................................... 2

6.SOUND OUTPUT STAGE WITH TDA7269A...................................................................... 2

7.BERTICAL OUTPUT STAGE WITH STV9379FA.............................................................. 2

8.VIDEO OUTPUT AMPLIFIER TDA6108 .............................................................................. 2

9.POWER SUPPLY (SMPS)....................................................................................................... 3

10.MICROCONTROLLER SDA55XX....................................................................................... 3

10.1.General Features.................................................................................................................... 3

10.2.External Crystal and Programmable Clock Speed................................................................ 3

10.3.Microcontroller Features ........................................................................................................ 3

10.4.Memory................................................................................................................................... 3

10.5.Display Features..................................................................................................................... 3

10.6.Acquisition Features.............................................................................................................. 4

10.7.Ports........................................................................................................................................ 4

11.CLASS AB STEREO HEADPHONE DRIVER TDA1308............................................... 4

12.SAW FILTERS.......................................................................................................................... 4

13.IC DESCRIPTIONS ................................................................................................................. 5

13.1.LM317T................................................................................................................................ 5

13.1.1.Description....................................................................................................................... 5

13.1.2.Features............................................................................................................................ 5

13.2.TDA1308T........................................................................................................................... 5

13.2.1.General Description......................................................................................................... 5

13.2.2.Features............................................................................................................................ 5

13.2.3.Pinning ............................................................................................................................. 6

13.3.MSP34X0G (MSP3410G)................................................................................................ 6

13.3.1.Description....................................................................................................................... 6

13.3.2.Features............................................................................................................................ 7

13.3.3.Pin connections ............................................................................................................... 7

13.4.VDP313xY .......................................................................................................................... 8

13.4.1.Introduction...................................................................................................................... 8

13.4.2.Features............................................................................................................................ 9

13.4.3.Pin Connections and short descriptions ........................................................................ 9

13.5.TEA6415C .........................................................................................................................10

13.5.1.General Description........................................................................................................10

13.5.2.Features...........................................................................................................................10

Page 9

13.10.SDA5555..........................................................................................................................13

13.10.1.General definition..........................................................................................................13

13.10.2.Features.........................................................................................................................13

13.11.MC44608..........................................................................................................................14

13.11.1.Description....................................................................................................................14

13.11.2.General Features...........................................................................................................15

13.11.3.Pin Connections ............................................................................................................15

13.12.TCET1102G....................................................................................................................16

13.12.1.Description....................................................................................................................16

13.12.2.Applications ..................................................................................................................16

13.12.3.Features.........................................................................................................................16

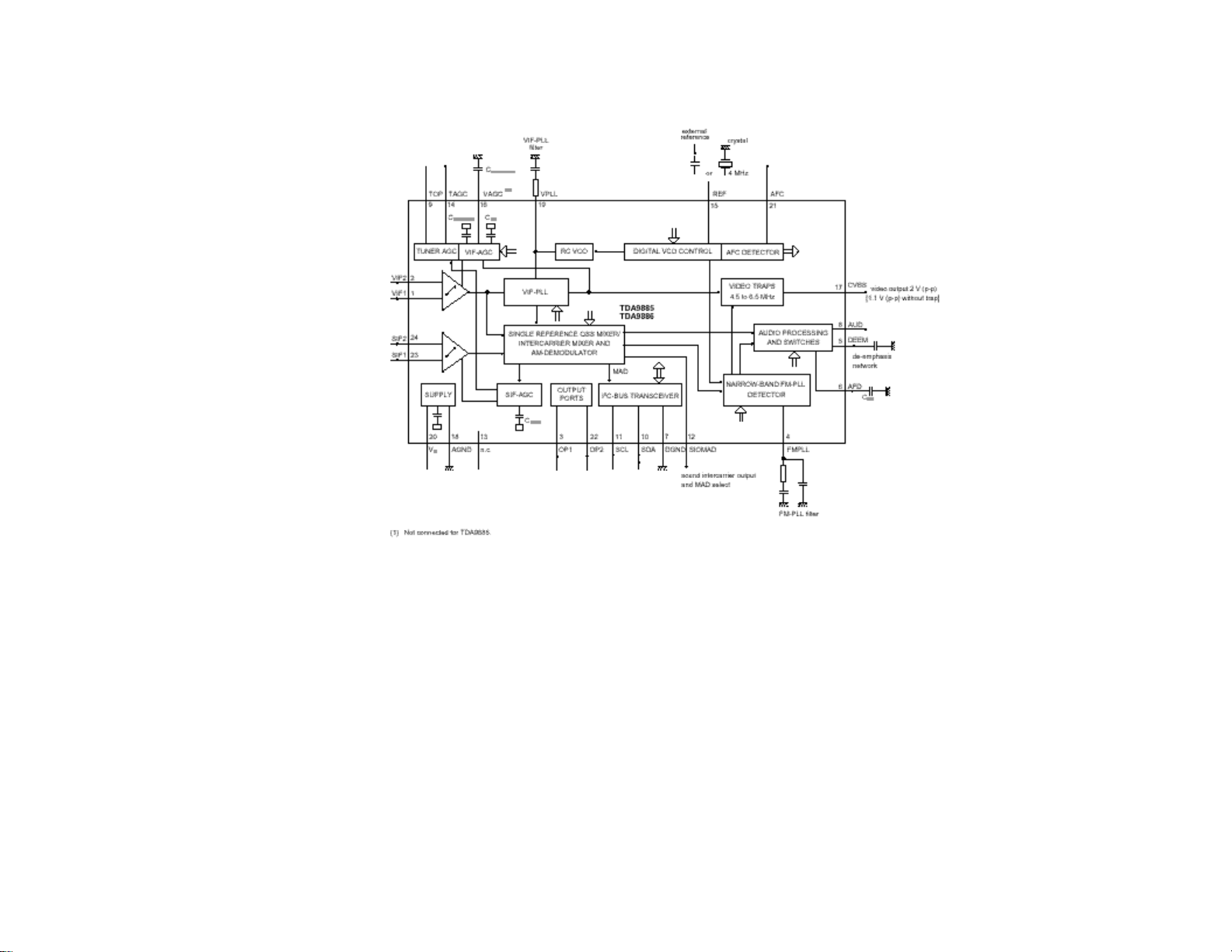

13.13.TDA9885T.......................................................................................................................16

13.13.1.General Description......................................................................................................16

13.13.2.Features.........................................................................................................................16

13.13.3.Pinning...........................................................................................................................17

13.14.PI5V330............................................................................................................................17

13.14.1.General Description......................................................................................................17

14.AK45 CHASSIS PRODUCTION SERVICE MODE ADJUSTMENTS........................18

14.1.SERVICE MENU.....................................................................................................................18

14.2.ADJUST MENU ......................................................................................................................18

14.3.OPTIONS MENU.....................................................................................................................30

Option 0. Video Processor Crystal Indication..........................................................................30

Option 1. (0x01) Video Processor Decoder Mode Register......................................................30

Option 2. (0x18) Video Processor Blanking Control ................................................................30

Option 3. (0x19) Video Processor Cathode Drive Level...........................................................31

Option 4......................................................................................................................................31

Option 5. CTI Avaliable, Mono AVL...........................................................................................31

Option 6......................................................................................................................................31

Option 7. OPTIONHOTELACTIVE, PLL_VST, PIP Zoom Mode, PIP Position...........................31

Option 8. IF Frequency..............................................................................................................32

Option 9. Standard Available.....................................................................................................32

Option 10. Scart, Combfilter, Teletext, Language.....................................................................33

Option 11. PLL Tuner Control 1 Byte........................................................................................33

Option 12. PLL Tuner Control 2 Low Byte................................................................................33

Option 13. PLL Tuner Control 2 Mid Byte.................................................................................34

Option 14. PLL Tuner Control 2 High Byte ...............................................................................34

Option 15. PLL Tuner VHF LOW – VHF HIGH Crossover Low Byte.........................................34

Option 16. PLL Tuner VHF LOW – VHF HIGH Crossover High Byte........................................34

Option 17. PLL Tuner VHF HIGH – UHF Crossover Low Byte..................................................34

Option 18. PLL Tuner VHF HIGH – UHF Crossover High Byte .................................................34

Option 19. PIP PLL Tuner Control 1 Byte .................................................................................35

Option 20. PIP PLL Tuner Control 2 Low Byte..........................................................................35

Option 21. PIP PLL Tuner Control 2 Mid Byte ..........................................................................35

Option 22. PIP PLL Tuner Control 2 High Byte.........................................................................35

Page 10

Option 39. Personal Preferance Equalizer Band 1 ...................................................................39

Option 40. Personal Preferance Equalizer Band 2 ...................................................................39

Option 41. Personal Preferance Equalizer Band 3 ...................................................................39

Option 42. Personal Preferance Equalizer Band 4 ...................................................................39

Option 43. Personal Preferance Equalizer Band 5 ...................................................................39

Option 44. Sound Efect (Standard; Music; Speech; Jazz; Pp).................................................39

Option 45. Volume Offset Left...................................................................................................39

Option 46. Volume Offset Right ................................................................................................39

Option 47. Volume Offset Center ..............................................................................................40

Option 48. Volume Offset Rear..................................................................................................40

Option 49. Surround Delay........................................................................................................40

Option 50. FM Prescale..............................................................................................................40

Option 51. NICAM Prescale.......................................................................................................40

Option 52. Scart Input Prescale ................................................................................................40

Option 53. I2S Prescale .............................................................................................................40

Option 54. Scart Output Prescale..............................................................................................40

Option 55. Speaker Setup..........................................................................................................41

Option 56. Audio Options Available Or Not..............................................................................41

Option 57. Stereo Threshold.....................................................................................................41

Option 58. MSP Audio Flags......................................................................................................42

Option 59. NICAM Threshold.....................................................................................................42

Option 60. Power Delay Time....................................................................................................42

14.4.OPTION TABLE RECOMMENDED VALUES..........................................................................45

14.5.SCREEN ADJUSTMENT (FBT SCREEN)...............................................................................47

14.6.GEOMETRY ADJUSTMENT...................................................................................................48

4:3 FORMATS.............................................................................................................................48

16:9 FORMATS...........................................................................................................................49

16.BLOCK DIAGRAM.................................................................................................................57

Page 11

1.INTRODUCTION

11AK45 is a 50Hz colour television capable of driving 24” + CRT sizes( beginning from 24” 16:9 up to

33”).

The chassis is capable of operation in PAL, SECAM, NTSC (playback) colour standards and multiple

transmission standards as B/G, D/K, I/I’, and L/L´.

Sound system output is supplying 2x10W (10%THD) for left and right outputs of 8ohm speakers.

TV supports FASTTEXT. It is possible to decode transmissions including high graphical data.

The chassis is equipped with three full EuroScarts, only one of them supports RGB input, one

headphone output, one FAV input, one SVHS input (via SCART)

2.TUNER

The hardware and software of the TV is suitable for tuners, supplied by different companies, which are

selected from the Service Menu. These tuners can be combined VHF, UHF tuners suitable for CCIR

systems B/G, H, L, L´, I/I´, and D/K. The tuning is available through the digitally controlled I2C bus

(PLL). Below you will find info on one of the Tuners in use.

General description of UV1316:

The UV1316 tuner belongs to the UV 1300 family of tuners, which are designed to meet a wide range of

applications. It is a combined VHF, UHF tuner suitable for CCIR systems B/G, H, L, L’, I and I’. The low

IF output impedance has been designed for direct drive of a wide variety of SAW filters with sufficient

suppression of triple transient.

Features of UV1316:

1. Member of the UV1300 family small sized UHF/VHF tuners

2. Systems CCIR: B/G, H, L, L’, I and I’; OIRT: D/K

3. Digitally controlled (PLL) tuning via I2C-bus

4. Off-air channels, S-cable channels and Hyperband

5. World standardized mechanical dimensions and world standard pinning

6. Compact size

7. Complies to “CENELEC EN55020” and “EN55013”

Pinning:

1. Gain control voltage (AGC) : 4.0V, Max: 4.5V

2. Tuning voltage

3. I²C-bus address select : Max: 5.5V

4. I²C-bus serial clock : Min:-0.3V, Max: 5.5V

5. I²C-bus serial data : Min:-0.3V, Max: 5.5V

6. Not connected

7. PLL supply voltage : 5.0V, Min: 4.75V, Max: 5.5V

8. ADC input

9. Tuner supply voltage : 33V, Min: 30V, Max: 35V

10. Symmetrical IF output 1

11. Symmetrical IF output 2

3.IF PART (TDA9885/86)

Page 12

4.VIDEO SWITCH TEA6415

In case of three or more external sources are used, the video switch IC TEA6415 is used. The main

function of this device is to switch 8 video-input sources on the 6 outputs.

Each output can be switched on only one of each input. On each input an alignment of the lowest level

of the signal is made (bottom of sync. top for CVBS or black level for RGB signals).

Each nominal gain between any input and output is 6.5dB.For D2MAC or Chroma signal the alignment

is switched off by forcing, with an external resistor bridge, 5VDC on the input. Each input can be used

as a normal input or as a MAC or Chroma input (with external Resistor Bridge). All the switching

possibilities are changed through the BUS. Driving 75ohm load needs an external resistor. It is possible

to have the same input connected to several outputs.

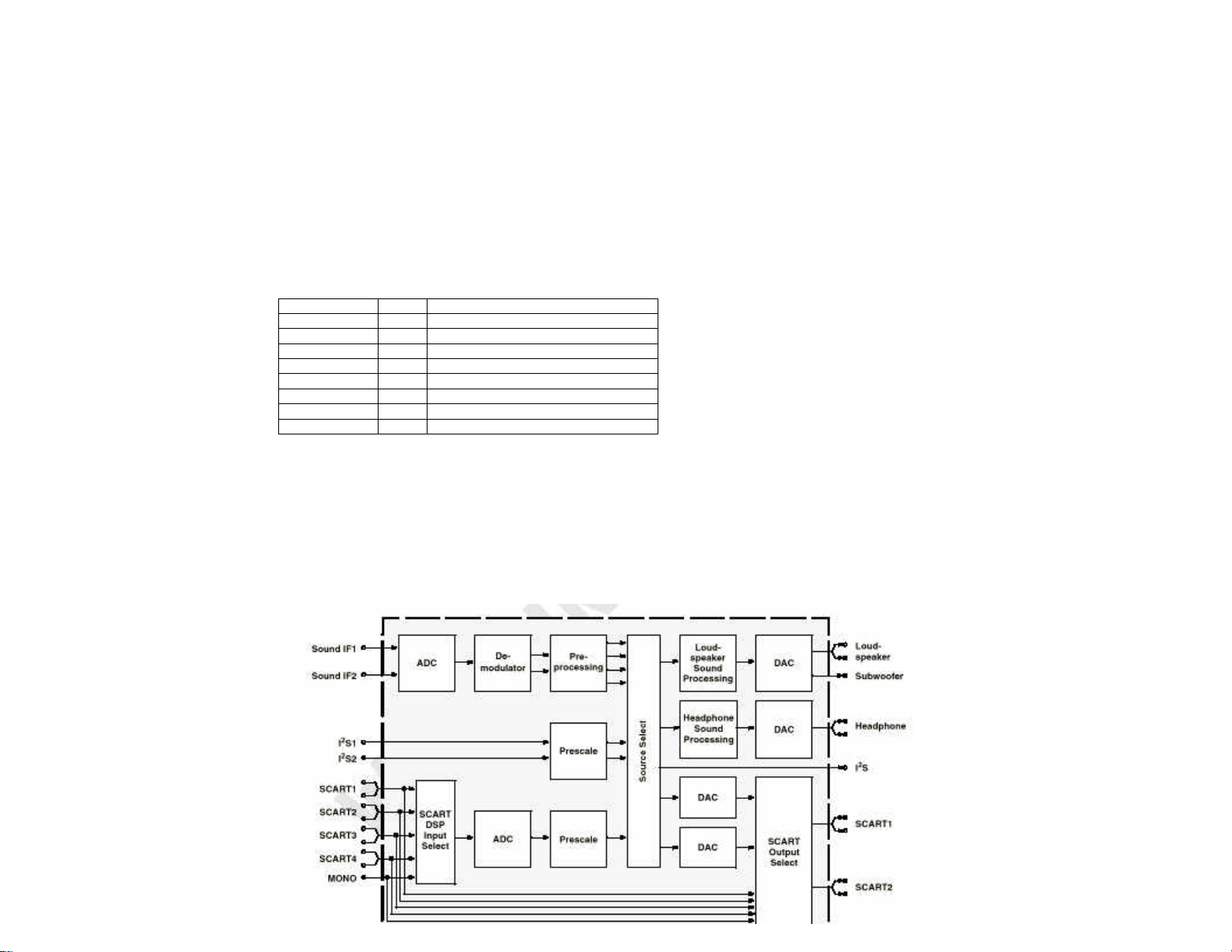

5.MULTI STANDARD SOUND PROCESSOR

The MSP 34x10G family of single-chip Multi-standard Sound Processors covers the sound processing

of all analog TV-Standards worldwide, as well as the NICAM digital sound standards. The full TV sound

processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on

a single chip.

The DBX noise reduction, or alternatively, MICRONAS Noise Reduction (MNR) is performed alignment

free. Other processed standards are the Japanese FM-FM multiplex standard (EIA-J) and the FM

Stereo Radio standard.

Page 13

9.POWER SUPPLY (SMPS)

The DC voltages required at various parts of the chassis are provided by an SMPS transformer

controlled by the IC MC44608, which is designed for driving, controlling and protecting switching

transistor of SMPS. The transformer generates 145V for FBT input, +/-14V for audio amplifier, 5V and

3.3V stand by voltage and 8V, 12V and 5V supplies for other different parts of the chassis.

An optocoupler is used to control the regulation of line voltage and stand-by power consumption. There

is a regulation circuit in secondary side. This circuit produces a control voltage according to the

changes in 145V DC voltage, via an optocoupler (TCET1102G) to pin3 of the IC.

During the switch on period of the transistor, energy is stored in the transformer. During the switch off

period energy is fed to the load via secondary winding. By varying switch-on time of the power

transistor, it controls each portion of energy transferred to the second side such that the output voltage

remains nearly independent of load variations.

10.MICROCONTROLLER SDA55XX

10.1.General Features

• Feature selection via special function register

• Simultaneous reception of TTX, VPS, PDC, and WSS (line 23)

• Supply Voltage 2.5 and 3.3 V

• ROM version package PSDIP52-2, PMQFP64-1

• Romless version package PMQFP100-2, PLCC84-2

10.2.External Crystal and Programmable Clock Speed

• Single external 6MHz crystal, all necessary clocks are generated internally

• CPU clock speed selectable via special function registers.

• Normal Mode 33.33 MHz CPU clock, Power Save mode 8.33 MHz

10.3.Microcontroller Features

• 8bit 8051 instruction set compatible CPU.

• 33.33-MHz internal clock (max.)

• 0.360 ms (min.) instruction cycle

• Two 16-bit timers

• Watchdog timer

• Capture compare timer for infrared remote control decoding

• Pulse width modulation unit (2 channels 14 bit, 6 channels 8 bit)

• ADC (4 channels, 8 bit)

• UART (rxd, txd)

10.4.Memory

• Non-multiplexed 8-bit data and 16 … 20-bit address bus (ROMless Version)

• Memory banking up to 1Mbyte (Romless version)

• Up to 128 Kilobyte on Chip Program ROM

• Eight 16-bit data pointer registers (DPTR)

• 256-bytes on-chip Processor Internal RAM (IRAM)

• 128bytes extended stack memory.

• Display RAM and TXT/VPS/PDC/WSS-Acquisition-Buffer directly accessible via MOVX

Page 14

• Up to 16 Colours per DRCS Character

• One out of Eight Colours for Foreground and Background Colours for 1-bit DRCS and ROM

Characters

• Shadowing

• Contrast Reduction

• Pixel by Pixel Shiftable Cursor With up to 4 Different Colours

• Support of Progressive Scan and 100 Hz.

• 3 X 4Bits RGB-DACs On-Chip

• Free Programmable Pixel Clock from 10 MHz to 32MHz

• Pixel Clock Independent from CPU Clock

• Multinorm H/V-Display Synchronization in Master or Slave Mode

10.6.Acquisition Features

• Multi-standard Digital Data Slicer

• Parallel Multi-norm Slicing (TTX, VPS, WSS, CC, G+)

• Four Different Framing Codes Available

• Data Caption only limited by available Memory

• Programmable VBI-buffer

• Full Channel Data Slicing Supported

• Fully Digital Signal Processing

• Noise Measurement and Controlled Noise Compensation

• Attenuation Measurement and Compensation

• Group Delay Measurement and Compensation

• Exact Decoding of Echo Disturbed Signals

10.7.Ports

• One 8-bit I/O-port with open drain output and optional I2C Bus emulation support (Port0)

• Two 8-bit multifunction I/O-ports (Port1, Port3)

• One 4-bit port working as digital or analogue inputs for the ADC (Port2)

• One 2-bit I/O port with secondary function (P4.2, 4.3, 4.7)

• One 4-bit I/O-port with secondary function (P4.0, 4.1, 4.4) (Not available in P-SDIP 52)

11.CLASS AB STEREO HEADPHONE DRIVER TDA1308

The TDA1308 is an integrated class AB stereo headphone driver contained in a DIP8 plastic package.

The device is fabricated in a 1 mm CMOS process and has been primarily developed for portable digital

audio applications.

12.SAW FILTERS

K3953M:

Standard

B/G, D/K, I, L/L’

Features

TV IF filter with Nyquist slopes at 33,90 MHz and 38,90 MHz

Constant group delay

Suitable for CENELEC EN 55020

Page 15

K9356M:

Standard

B/G, D/K, I, L

Features

TV IF audio filter with pass band for sound carriers at 32,40 MHz (D/K, L), 32,90 MHz (I) and 33,40 MHz

(B/G)

Terminal and Pin configuration are the same with K3953M

K9656M:

Standard

B/G, D/K, I, L/L’

Features

TV IF audio filter with two channels

Channel 1 (L’) with one pass band for sound carriers at 40,40 MHz (L’) and 39,75 MHz (L’- NICAM)

Channel 2 (B/G, D/K, L, I) with one pass band for sound carriers between 32,35 MHz and 33,40 MHz

Terminal and Pin configuration are the same with K3953M

13.IC DESCRIPTIONS

LM317T TDA1308T

MSP3410G VDP3130Y

TEA6415 STV9379FA

TDA7269A LM7805/LM7808

24C08 SDA55XX

MC44608 TCET1102G

TDA9885T

13.1.LM317T

13.1.1.Description

The LM317T is an adjustable 3 terminal positive voltage regulator capable of supplying in excess of 1.5

amps over an output range of 1.25 to 37 volts. This voltage regulator is exceptionally easy to use and

requires only two external resistors to set the output voltage. Further, it employs internal current limiting,

thermal shutdown and safe area compensation, making it essentially blow–out proof. The LM317

serves a wide variety of applications including local, on card regulation. This device can also be used to

make a programmable output regulator, or by connecting a fixed resistor between the adjustment and

output, the LM317 can be used as a precision current regulator.

13.1.2.Features

• Output Current in Excess of 1.5 A

• Output Adjustable between 1.2 V and 37 V

• Internal Thermal Overload Protection

• Internal Short Circuit Current Limiting Constant with Temperature

• Output Transistor Safe–Area Compensation

• Floating Operation for High Voltage Applications

• Available in Surface Mount D2PAK, and Standard 3–Lead Transistor Package

Page 16

• Low power consumption

• Short-circuit resistant

• High performance

• high signal-to-noise ratio

• High slew rate

• Low distortion

• Large output voltage swing.

13.2.3.Pinning

SYMBOL PIN DESCRIPTION

OUTA 1 Output A

INA(neg) 2 Inverting input A

INA(pos) 3 Non-inverting input A

VSS 4 Negative supply

INB(pos) 5 Non-inverting input B

INB(neg) 6 Inverting input B

OUTB 7 Output B

VDD 8 Positive supply

13.3.MSP34X0G (MSP3410G)

13.3.1.Description

The MSP 34x0G family of single-chip Multi standard Sound Processors covers the sound processing of

all analog TV-Standards worldwide, as well as the NICAM digital sound standards. The full TV sound

processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on

a single chip. Figure shows a simplified functional block diagram of the MSP 34x0G.

Page 17

13.3.2.Features

Standard Selection with single I2C transmission

Automatic Standard Detection of terrestrial TV standards

Automatic Sound Selection (mono/stereo/bilingual), new registers MODUS, STATUS

Two selectable sound IF (SIF) inputs

Automatic Carrier Mute function

Interrupt output programmable (indicating status change)

Loudspeaker / Headphone channel with volume, balance, bass, treble, loudness

AVC: Automatic Volume Correction

Subwoofer output with programmable low-pass and complementary high-pass filter

5-band graphic equalizer for loudspeaker channel

Spatial effect for loudspeaker channel

Four Stereo SCART (line) inputs, one Mono input; two Stereo SCART outputs

Complete SCART in/out switching matrix

Two I2S inputs; one I2S output

Dolby Pro Logic with DPL 351xA coprocessor

All analog FM-Stereo A2 and satellite standards; AM-SECAM L standard

Simultaneous demodulation of (very) high-deviation FM-Mono and NICAM

Adaptive deemphasis for satellite (Wegener-Panda, acc. to ASTRA specification)

ASTRA Digital Radio (ADR) together with DRP 3510A

All NICAM standards

Korean FM-Stereo A2 standard

13.3.3.Pin connections

NC = not connected; leave vacant

LV = if not used, leave vacant

X = obligatory; connect as described in circuit diagram

DVSS: if not used, connect to DVSS

AHVSS: connect to AHVSS

Pin No. Pin Name Type

PLCC

68-pin

1 16 14 9 8 ADR_WS OUT LV ADR word strobe

2 - - - - NC LV Not connected

3 15 13 8 7 ADR_DA OUT LV ADR Data Output

4 14 12 7 6 I2S_DA_IN1 IN LV I2S1 data input

5 13 11 6 5 I2S_DA_OUT OUT LV I2S data output

6 12 10 5 4 I2S_WS IN/OUT LV I2S word strobe

7 11 9 4 3 I2S_CL IN/OUT LV I2S clock

8 10 8 3 2 I2C_DA IN/OUT X I2C data

9 9 7 2 1 I2C_CL IN/OUT X I2C data

10 8 - 1 64 NC LV Not connected

11 7 6 80 63 STANDBYQ IN X Stand-by (low-active)

12 6 5 79 62 ADR_SEL IN X I2C bus address select

PSDIP

64-pin

PSDIP

52-pin

PQFP

80-pin

PLQFP

64-pin

Connection

(if not used)

Short Description

Page 18

- - - 64 - NC LV Not connected

- - - 12 - DVSUP

X Digital power supply 5V

- - - 63 - NC LV Not connected

27 56 45 62 48 AVSS X Analog ground

- - - 61 - AVSS X Analog ground

28 55 44 60 47 MONO_IN IN LV Mono input

- - - 59 - NC LV Not connected

29 54 43 58 46 VREFTOP X

Reference voltage IF A/D

converter

30 53 42 57 45 SC1_IN_R IN LV SCART 1 input, right

31 52 41 56 44 SC1_IN_L IN LV SCART 1 input, left

32 51 - 55 43 ASG1 AHVSS Analog Shield Ground 1

33 50 40 54 42 SC2_IN_R IN LV SCART 2 input, right

34 49 39 53 41 SC2_IN_L IN LV SCART 2 input, left

35 48 - 52 40 ASG2 AHVSS Analog Shield Ground 2

36 47 38 51 39 SC3_IN_R IN LV SCART 3 input, right

37 46 37 50 38 SC3_IN_L IN LV SCART 3 input, left

38 45 - 49 37 ASG4 AHVSS Analog Shield Ground 4

39 44 - 48 36 SC4_IN_R IN LV SCART 4 input, right

40 43 - 47 35 SC4_IN_L IN LV SCART 4 input, left

41 - - 46 - NC LV or AHVSS Not connected

42 42 36 45 34 AGNDC X Analog reference voltage

43 41 35 44 33 AHVSS X Analog ground

- - - 43 - AHVSS X Analog ground

- - - 42 - NC LV Not connected

- - - 41 - NC LV Not connected

44 40 34 40 32 CAPL_M X Volume capacitor MAIN

45 39 33 39 31 AHVSUP X Analog power supply 8V

46 38 32 38 30 CAPL_A X Volume capacitor AUX

47 37 31 37 29 SC1_OUT_L OUT LV SCART output 1, left

48 36 30 36 28 SC1_OUT_R OUT LV SCART output 1, right

49 35 29 35 27 VREF1 X Reference ground 1

50 34 28 34 26 SC2_OUT_L OUT LV SCART output 2, left

51 33 27 33 25 SC2_OUT_R OUT LV SCART output 2, right

52 - - 32 - NC LV Not connected

53 32 - 31 24 NC LV Not connected

54 31 26 30 23 DACM_SUB OUT LV Subwoofer output

55 30 - 29 22 NC LV Not connected

56 29 25 28 21 DACM_L OUT LV Loudspeaker out, left

57 28 24 27 20 DACM_R OUT LV Loudspeaker out, right

58 27 23 26 19 VREF2 X Reference ground 2

59 26 22 25 18 DACA_L OUT LV Headphone out, left

60 25 21 24 17 DACA_R OUT LV Headphone out, right

- - - 23 - NC LV Not connected

- - - 22 - NC LV Not connected

61 24 20 21 16 RESETQ IN X Power-on-reset

62 23 - 20 15 NC LV Not connected

63 22 - 19 14 NC LV Not connected

64 21 19 18 13 NC LV Not connected

65 20 18 17 12 I2S_DA_IN2 IN LV I2S2-data input

66 19 17 16 11 DVSS X Digital ground

- - - 15 - DVSS X Digital ground

- - - 14 - DVSS X Digital ground

67 18 16 13 10 DVSUP X Digital power supply 5V

Page 19

13.4.2.Features

Video Decoding and Processing

– four CVBS, one S-VHS input, one YC R C B component input

– integrated high-quality A/D converters and associated clamp and AGC circuits

– adaptive 2H comb filter Y/C separator

– multistandard colour decoder PAL/NTSC/SECAM including all substandards

– multistandard sync decoder

– automatic standard recognition

– black-line detector

– linear horizontal scaling (0.25...4), as well as nonlinear horizontal scaling “Panoramavision”

– black-level expander

– dynamic peaking

– soft limiter (gamma correction)

– colour transient improvement

RGB Processing and Deflection

– programmable RGB matrix

– two analog RGB / Fastblank inputs

– half-contrast switch

– picture frame generator

– scan velocity modulation output

– high-performance H/V deflection

– separate ADC for tube measurements

– EHT compensation

– angle and bow correction

– one 20.25 MHz crystal, few external components

–I2C-Bus Interface

– 64-pin PSDIP package

13.4.3.Pin Connections and short descriptions

NC = not connected LV = if not used, leave vacant

X = obligatory; connect as described in circuit diagram IN = Input

OUT = Output SUPPLY = Supply Pin

Pin no

PSDIP 64-pin

1 TEST IN GNDD Test Input

2 RESQ IN X Reset Input

3 SCL IN/OUT X I2C Bus Clock

4 SDA IN/OUT X I2C Bus Data

5 GNDD SUPPLY X Digital Ground

6 HCS IN LV Half Contrast Switch Input

7 FSY OUT LV Front Sync Output

Pin name Type Connection

(if not used)

Short description

Page 20

25 GNDD SUPPLY X Digital Ground

26 RSW2 OUT GNDAB Range Switch 2 for Measurement ADC

27 RSW1 OUT GNDAB Range Switch 1 for Measurement ADC

28 SENSE IN GNDAB Sense ADC Input

29 GNDM SUPPLY X Ground, MADC ýnput

30 VERTQ OUT LV Inverted Vertical Sawtooth Output

31 VERT OUT LV Vertical Sawtooth Output

32 E/w OUT LV Vertical Parabola Output

33 XREF IN X Reference Input for RGB DACs

34 SVMOUT OUT VSUPAB Analog Scan Velocity Modulation Output

35 GNDAB SUPPLY X Analog Ground Backend

36 VSUPAB SUPPLY X Analog Supply Voltage (5.0V) Backend

37 ROUT OUT VSUPAB Analog Red Output

38 GOUT OUT VSUPAB Analog Green Output

39 BOUT OUT VSUPAB Analog Blue Output

40 VRD IN X DAC Reference

41 RIN IN GNDAB Analog Red Input

42 GIN IN GNDAB Analog Green Input

43 BIN IN GNDAB Analog Blue Input

44 FBLIN IN GNDAB Fast Blank Input

45 RIN2 IN GNDAB Analog Red Input2

46 GIN2 IN GNDAB Analog Green Input2

47 BIN2 IN GNDAB Analog Blue Input2

48 FBLIN2 IN GNDAB Fast Blank Input2

49 CLK20 OUT LV 20.25 MHz System Clock Output

50 HOUT OUT X Horizontal Drive Output

51 XTAL 1 IN X Analog Crystal Input

52 XTAL 2 OUT X Analog Crystal Output

53 CIN 2/CRIN LV Analog Chroma 2/Component CR Input

54 CBIN IN LV Component CB Input

55 GNDAF SUPPLY X Analog Ground Frontend

56 SGND IN GNDAF Signal Ground for Analog Input

57 VRT IN X Reference Voltage Top, Video ADC

58 VSUPAF SUPPLY X Analog Supply Voltage (5.0V) Frontend

59 VOUT OUT LV Analog Video Output

60 CIN1 IN VRT Analog Chroma 1 Input

61 VIN1 IN VRT Analog Video 1 Input

62 VIN2 IN VRT Analog Video 2 Input

63 VIN3 IN VRT Analog Video 3 Input

64 VIN4 IN VRT Analog Video 4 Input

13.5.TEA6415C

13.5.1.General Description

The main function of the IC is to switch 8 video input sources on 6 outputs. Each output can be

switched on only one of each input. On each input an alignment of the lowest level of the signal is made

(bottom of synch. top for CVBS or black level for RGB signals). Each nominal gain between any input

Page 21

• 6.5dB gain between any input and output

• 55dB crosstalk at 5mHz

• Fully ESD protected

13.5.3.Pinning

1. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

2. Data : Low level : -0.3V Max: 1.5V,

High level : 3.0V Max : Vcc+0.5V

3. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

4. Clock : Low level : -0.3V Max: 1.5V,

High level : 3.0V Max : Vcc+0.5V

5. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

6. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

7. Prog

8. Input : Max : 2Vpp, Input Current: 1mA, Max: 3mA

9. Vcc : 12V

10. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

11. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

12. Ground

13. Output : 5.5Vpp, Min : 4.5Vpp

14. Output : 5.5Vpp, Min : 4.5Vpp

15. Output : 5.5Vpp, Min : 4.5Vpp

16. Output : 5.5Vpp, Min : 4.5Vpp

17. Output : 5.5Vpp, Min : 4.5Vpp

18. Output : 5.5Vpp, Min : 4.5Vpp

19. Ground

20. Input : Max : 2Vpp, Input Current : 1mA, Max : 3mA

13.6.STV9379FA

13.6.1.Description

Designed for monitors and high performance TVs, the STV9379FA vertical deflection booster can

handle flyback voltage up to 90V. Further to this, it is possible to have a flyback voltage, which is more

than the double of the supply (Pin 2). This allows to decrease the power consumption, or to decrease

the flyback time for a given supply voltage. The STV9379FA operates with supplies up to 42V and

provides up to 2.6APP output current to drive the yoke. The STV9379FA is offered in HEPTAWATT

package.

13.6.2.Features

Power Amplifier

Thermal Protection

Output Current Up To 2.6APP

Flyback Voltage Up To 90V (on Pin 5)

Suitable For DC Coupling Application

Page 22

13.7.TDA7269A

13.7.1.Description

The TDA7269A is class AB dual Audio power amplifier assembled in the Multiwatt package, specially

designed for high quality sound application as Hi-Fi music centers and stereo TV sets.

13.7.2.Features

Wide Supply Voltage Range Up To ±20V

Split Supply

High Output Power

14 + 14W @THD =10%, R

=8?,V

L

= +16V

S

No Pop at Turn-On/Off

Mute (Pop Free)

Stand-By Feature (Low Iq)

Short Circuit Protection To Gnd

Thermal Overload Protection

13.8.LM7800 (LM7805/LM7808)

13.8.1.Description

The L7800 series of three-terminal positive regulators is available in TO-220 TO-220FP TO-3 and D 2

PAK packages and several fixed output voltages, making it useful in a wide range of applications.

These regulators can provide local on-card regulation, eliminating the distribution problems associated

with single point regulation. Each type employs internal current limiting, thermal shutdown and safe

area protection, making it essentially indestructible. If adequate heat sinking is provided, they can

deliver over 1A output current. Although designed primarily as fixed voltage regulators, these devices

can be used with external components to obtain adjustable voltages and currents.

13.8.2.Features

Output Current Up To 1.5 A

Output Voltages of 5; 5.2; 6; 8; 8.5; 9; 12; 15; 18; 24V

Thermal Over load protection

Short Circuit Protection

Output Transition SOA Protection

13.9.AT24C08

13.9.1.Description

The AT24C01A/02/04/08/16 provides 1024/2048/4096/8192/16384 bits of serial electrically erasable

and programmable read-only memory (EEPROM) organized as 128/256/512/1024/2048 words of 8 bits

each. The device is optimized for use in many industrial and commercial applications where low-power

and low-voltage operation are essential. The AT24C01A/02/04/08/16 is available in space-saving 8-pin

PDIP, (AT24C01A/02/04/08/16), 8-lead TSSOP (AT24C01A/02/04/08/16) and 8-lead JEDEC SOIC

Page 23

• 8-byte Page (1K, 2K), 16-byte Page (4K, 8K, 16K) Write Modes

• Partial Page Writes are Allowed

• Self-timed Write Cycle (10 ms max)

• High-reliability

– Endurance: 1 Million Write Cycles

– Data Retention: 100 Years

• Automotive Grade and Extended Temperature Devices Available

• 8-lead JEDEC SOIC, 8-pin PDIP and 8-lead TSSOP Packages

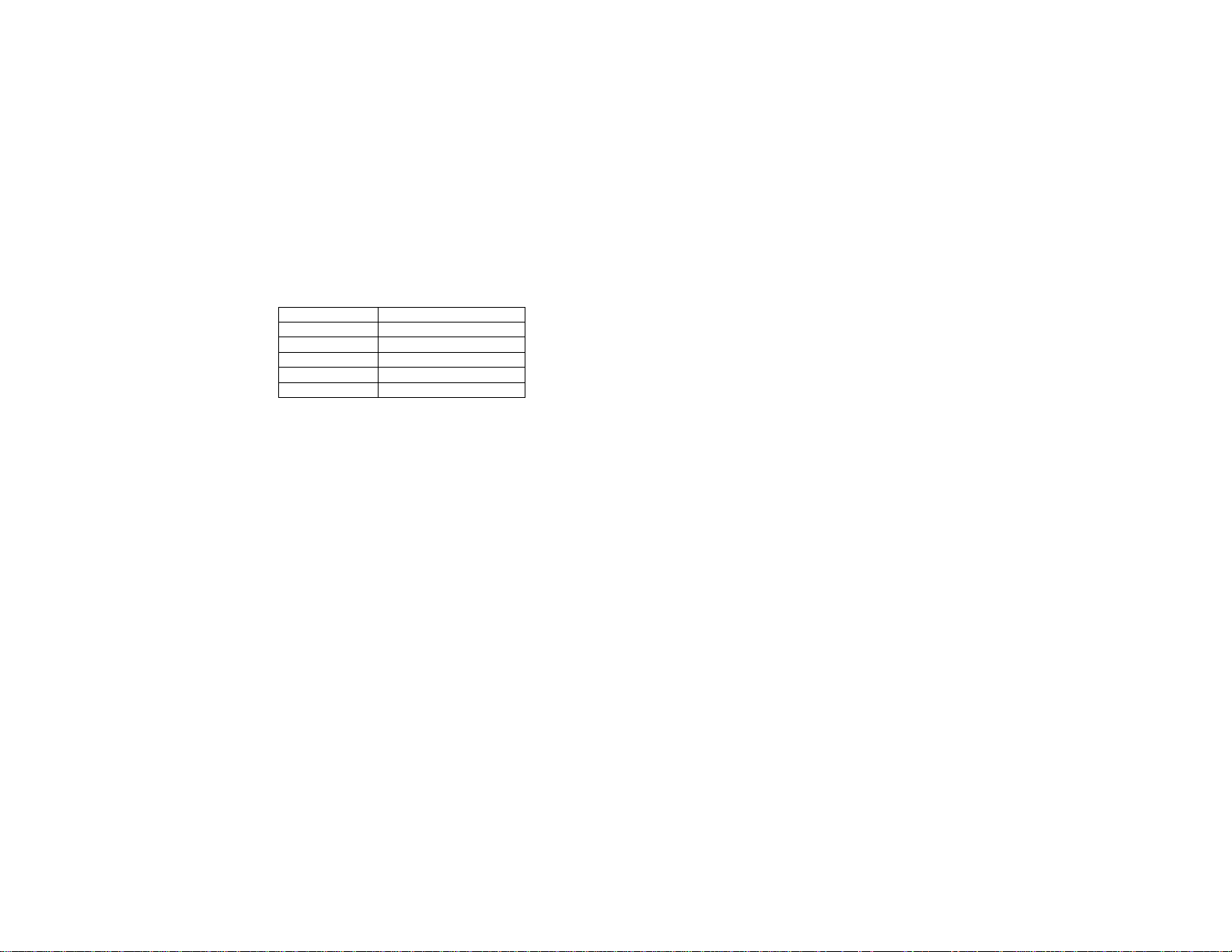

13.9.3.Pin Configurations

Pin name Function

A0-A2 Address Inputs

SDA Serial Data

SCL Serial Clock Input

WP Write Protect

NC No Connect

13.10.SDA5555

13.10.1.General definition

The SDA55XX is a single chip teletext decoder for decoding World System Teletext data as well as

Video Programming System (VPS), Program Delivery Control (PDC), and Wide Screen Signalling

(WSS) data used for PAL plus transmissions (Line 23). The device also supports Closed caption

acquisition and decoding. The device provides an integrated general-purpose, fully 8051-compatible

Microcontroller with television specific hardware features. Microcontroller has been enhanced to provide

powerful features such as memory banking, data pointers, and additional interrupts etc. The on-chip

display unit for displaying Level 1.5 teletext data can also be used for customer defined on screen

displays. Internal XRAM consists of up to 16 Kbytes. Device has an internal ROM of up to 128 KBytes.

ROMless versions can access up to 1 MByte of external RAM and ROM. The SDA 55XX supports a

wide range of standards including PAL, NTSC and contains a digital slicer for VPS, WSS, PDC, TTX

and Closed Caption, an accelerating acquisition hardware module, a display generator for Level 1.5

TTX data and powerful On screen Display capabilities based on parallel attributes, and Pixel oriented

characters (DRCS).

13.10.2.Features

General

• Feature selection via special function register

• Simultaneous reception of TTX, VPS, PDC, and WSS (line 23)

• Supply Voltage 2.5 and 3.3 V

• ROM version package PSDIP52-2, PMQFP64-1

• Romless version package PMQFP100-2, PLCC84-2

External Crystal and Programmable Clock Speed

• Single external 6MHz crystal, all necessary clocks are generated internally

Page 24

Memory

• Non-multiplexed 8-bit data and 16 … 20-bit address bus (ROMless Version)

• Memory banking up to 1Mbyte (Romless version)

• Up to 128 Kilobyte on Chip Program ROM

• Eight 16-bit data pointer registers (DPTR)

• 256-bytes on-chip Processor Internal RAM (IRAM)

• 128bytes extended stack memory.

• Display RAM and TXT/VPS/PDC/WSS-Acquisition-Buffer directly accessible via MOVX

• UP to 16KByte on Chip Extended RAM (XRAM) consisting of;

- 1 Kilobyte on-chip ACQ-buffer-RAM (access via MOVX)

- 1 Kilobyte on-chip extended-RAM (XRAM, access via MOVX) for user software

- 3 Kilobyte Display Memory

Display Features

• ROM Character Set Supports all East and West European Languages in single device

• Mosaic Graphic Character Set

• Parallel Display Attributes

• Single/Double Width/Height of Characters

• Variable Flash Rate

• Programmable Screen Size (25 Rows x 33...64 Columns)

• Flexible Character Matrixes (HxV) 12 x 9...16

• Up to 256 Dynamical Redefinable Characters in standard mode; 1024 Dynamical Redefinable

Characters in Enhanced Mode

• CLUT with up to 4096 colour combinations

• Up to 16 Colours per DRCS Character

• One out of Eight Colours for Foreground and Background Colours for 1-bit DRCS and ROM

Characters

• Shadowing

• Contrast Reduction

• Pixel by Pixel Shiftable Cursor With up to 4 Different Colours

• Support of Progressive Scan and 100 Hz.

• 3 X 4Bits RGB-DACs On-Chip

• Free Programmable Pixel Clock from 10 MHz to 32MHz

• Pixel Clock Independent from CPU Clock

• Multinorm H/V-Display Synchronization in Master or Slave Mode

Acquisition Features

• Multistandard Digital Data Slicer

• Parallel Multi-norm Slicing (TTX, VPS, WSS, CC, G+)

• Four Different Framing Codes Available

• Data Caption only Limited by available Memory

• Programmable VBI-buffer

• Full Channel Data Slicing Supported

• Fully Digital Signal Processing

• Noise Measurement and Controlled Noise Compensation

Page 25

external components while offering a high flexibility and reliability. The device also features a very high

efficiency stand–by management consisting of an effective Pulsed Mode operation. This technique

enables the reduction of the stand–by power consumption to approximately 1W while delivering 300mW

in a 150W SMPS.

• Integrated Start–Up Current Source

• Lossless Off–Line Start–Up

• Direct Off–Line Operation

• Fast Start–Up

13.11.2.General Features

• Flexibility

• Duty Cycle Control

• Under voltage Lockout with Hysteresis

• On Chip Oscillator Switching Frequency 40, or 75kHz

• Secondary Control with Few External Components

Protections

• Maximum Duty Cycle Limitation

• Cycle by Cycle Current Limitation

• Demagnetization (Zero Current Detection) Protection

• “Over VCC Protection” Against Open Loop

• Programmable Low Inertia Over Voltage Protection Against Open Loop

• Internal Thermal Protection

GreenLineTM Controller

• Pulsed Mode Techniques for a Very High Efficiency Low Power Mode

• Lossless Startup

• Low dV/dT for Low EMI Radiations

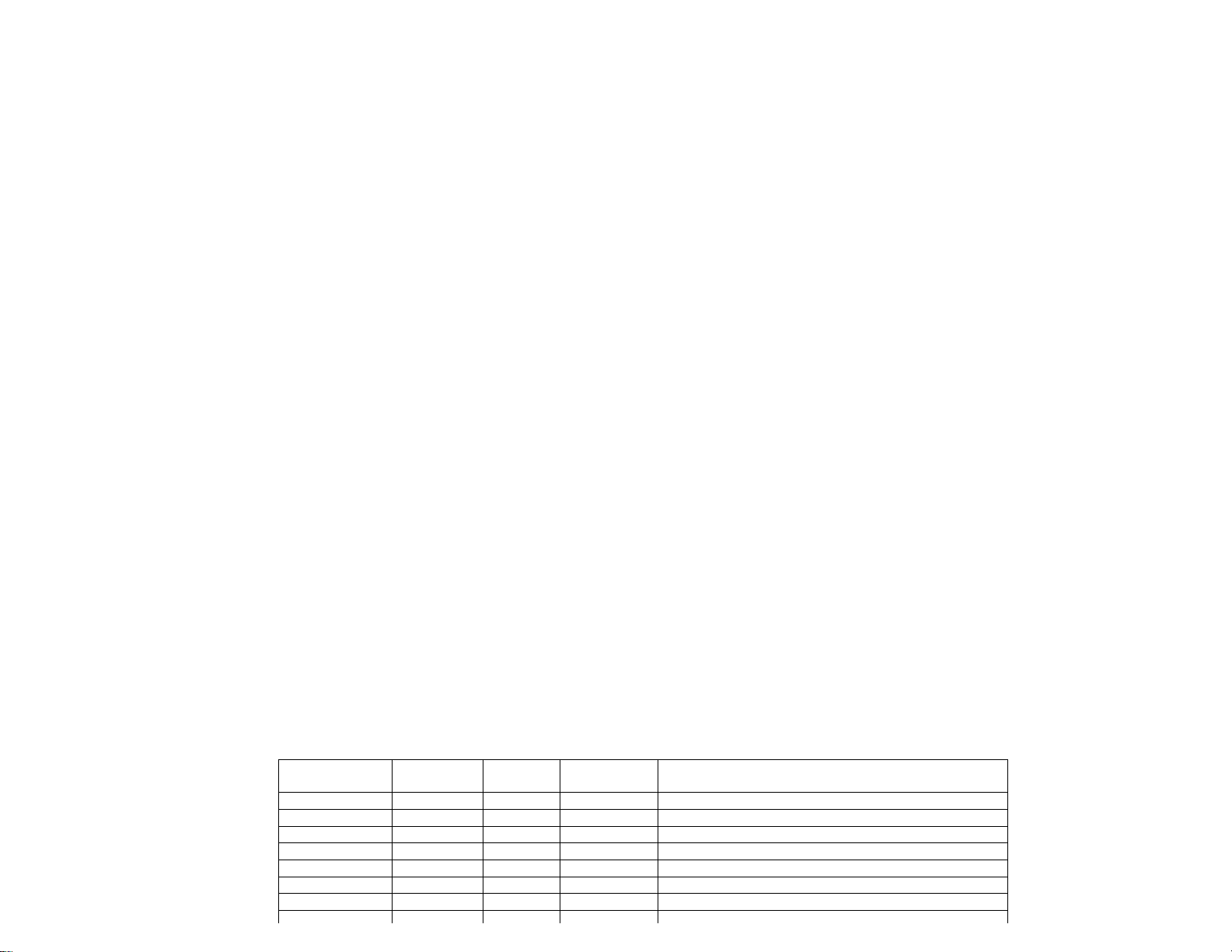

13.11.3.Pin Connections

13.11.4.Pin Function description

Pin Name Description

1 Demag The Demag pin offers 3 different functions: Zero voltage crossing detection (50mV), 24mA current

2 ISENSE The Current Sense pin senses the voltage developed on the series resistor inserted in the source

detection and 120mA current detection. The 24mA level is used to detect the secondary

reconfiguration status and the 120mA level to detect an Over Voltage status called Quick OVP.

Page 26

13.12.TCET1102G

13.12.1.Description

The TCET110/ TCET2100/ TCET4100 consists of a phototransistor optically coupled to a gallium

arsenide infrared-emitting diode in a 4-lead up to 16-lead plastic dual inline package. The elements are

mounted on one lead frame using a coplanar technique, providing a fixed distance between input and

output for highest safety requirements.

13.12.2.Applications

Circuits for safe protective separation against electrical shock according to safety class II (reinforced

isolation):

For appl. class I – IV at mains voltage ?300 V

For appl. class I – III at mains voltage ?600 V

According to VDE 0884, table 2, suitable for: Switch-mode power supplies, line receiver, computer

peripheral interface, microprocessor system interface.

13.12.3.Features

VDE 0884 related features:

Rated impulse voltage (transient overvoltage) V IOTM = 8 kV peak

Isolation test voltage (partial discharge test voltage) V pd = 1.6 kV

Rated isolation voltage (RMS includes DC) V IOWM = 600 V RMS (848 V peak)

Rated recurring peak voltage (repetitive) V IORM = 600 V RMS

General features:

CTR offered in 9 groups

Isolation materials according to UL94-VO

Pollution degree 2 (DIN/VDE 0110 / resp. IEC 664)

Climatic classification 55/100/21 (IEC 68 part 1)

Special construction: Therefore, extra low coupling capacity of typical 0.2pF, high Common Mode

Rejection

Low temperature coefficient of CTR

G = Leadform 10.16 mm; provides creepage distance > 8 mm, for TCET2100/ TCET4100 optional;

suffix letter ‘G’ is not marked on the optocoupler

Coupling System U

13.13.TDA9885T

13.13.1.General Description

The TDA9885 is an alignment-free single standard (without positive modulation) vision and sound IF signal

PLL.

13.13.2.Features

• 5 V supply voltage

Page 27

• SIF AGC for gain controlled SIF amplifier; single reference QSS mixer able to operate in high performance

single reference QSS mode and in intercarrier mode, switchable via I2C-bus

• AM demodulator without extra reference circuit

• Alignment-free selective FM-PLL demodulator with high linearity and low noise

• I2C-bus control for all functions

• I2C-bus transceiver with pin programmable Module Address (MAD).

13.13.3.Pinning

SYMBOL PIN DESCRIPTION

VIF1 1

VIF2

OP1

FMPLL

DEEM

AFD

DGND

AUD

TOP

SDA

SCL

SIOMA

n.c.

TAGC

REF

VAGC

CVBS

AGND

VPLL

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

VP 20

AFC

OP2

SIF1

SIF2

21

22

23

24

VIF differential input 1

VIF differential input 2

output 1 (open-collector)

FM-PLL for loop filter

de-emphasis output for capacitor

AF decoupling input for capacitor

digital ground

audio output

tuner AGC TakeOver Point (TOP)

I2C-bus data input/output

I2C-bus clock input

sound intercarrier output and MAD select

not connected

tuner AGC output

4 MHz crystal or reference input

VIF-AGC for capacitor; note 1

video output

analog ground

VIF-PLL for loop filter

supply voltage (+5 V)

AFC output

output 2 (open-collector)

SIF differential input 1

SIF differential input 2

13.14.PI5V330

13.14.1.General Description

The PI5V330 is well suited for video applications when switching composite or RGB analog. A picturein-picture application will be described in this brief. The pixel-rate creates video overlays so two or more

pictures can be viewed at the same time. An inexpensive NTSC titler can be implemented by

superimposing the output of a character generator on a standard composite video background.

Page 28

14.AK45 CHASSIS PRODUCTION SERVICE MODE ADJUSTMENTS

14.1.SERVICE MENU

All system, geometry and white balance alignments are performed in production service mode. Before

starting the production mode alignments, make sure that all manual adjustments are done correctly. To

start production mode alignments enter the MAIN MENU and then press the digits 4, 7, 2 and 5

respectively or press MUTE and INFO buttons at the same time. The following first menu appears on

the screen.

ADJUST...

OPTIONS...

You can select Adjust or Options items by pressing Up/Down buttons. Selected parameter will be

highlighted. Inorder to enter the selected parameter, press Left or Right button. To exit the service

menu press MENU button. Entire service menu parameters of AK45 CHASSIS are listed below.

14.2.ADJUST MENU

Select the parameter by pressing up/down buttons. Adjust the parameter by pressing Left/Right

buttons. In ADJUST menu, changed values are stored automatically.

000 255

001 036

002 019

003 020

004 030

005 026

006 003

007 004

008 005

009 005

White Point Red, White Point Green, White Point Blue:

Not used.

AGC

Apply PAL BG signal, VHF-3 Channel-12 and 60dBµV signal level. Adjust AGC (Automatic Gain

SERVICE

AK45JA0XX

AK45JA0XX

ADJUST...

Page 29

Y-Delay SECAM

Enter a SECAM B/G colour and black-white bar test pattern via RF. Adjust Y-Delay SECAM till the

colour transients on the colour bar of the pattern become as sharper and colours between transients do

not mix with each other as possible.

Y-Delay NTSC

Enter an NTSC colour and black-white bar test pattern via RF. Adjust Y-Delay NTSC till the colour

transients on the colour bar of the pattern become as sharper and colours between transients do not

mix with each other as possible.

Y-Delay other

Not used.

Vertical Pozition Offset

This value is fixed (127)

Vertical Pozition Offset

This value is fixed (127)

Horizontal Pozition Offset

This value is fixed (127)

Horizontal Pozition Offset

This value is fixed (127)

Vertical Blank Start

This register will be used only at 4:3 tube for 16:9 mode adjustment. It adjusts the vertical blank start

position.

Vertical Blank Stop

This register will be used only at 4:3 tube for 16:9 mode adjustment. It adjusts the vertical blank stop

position.

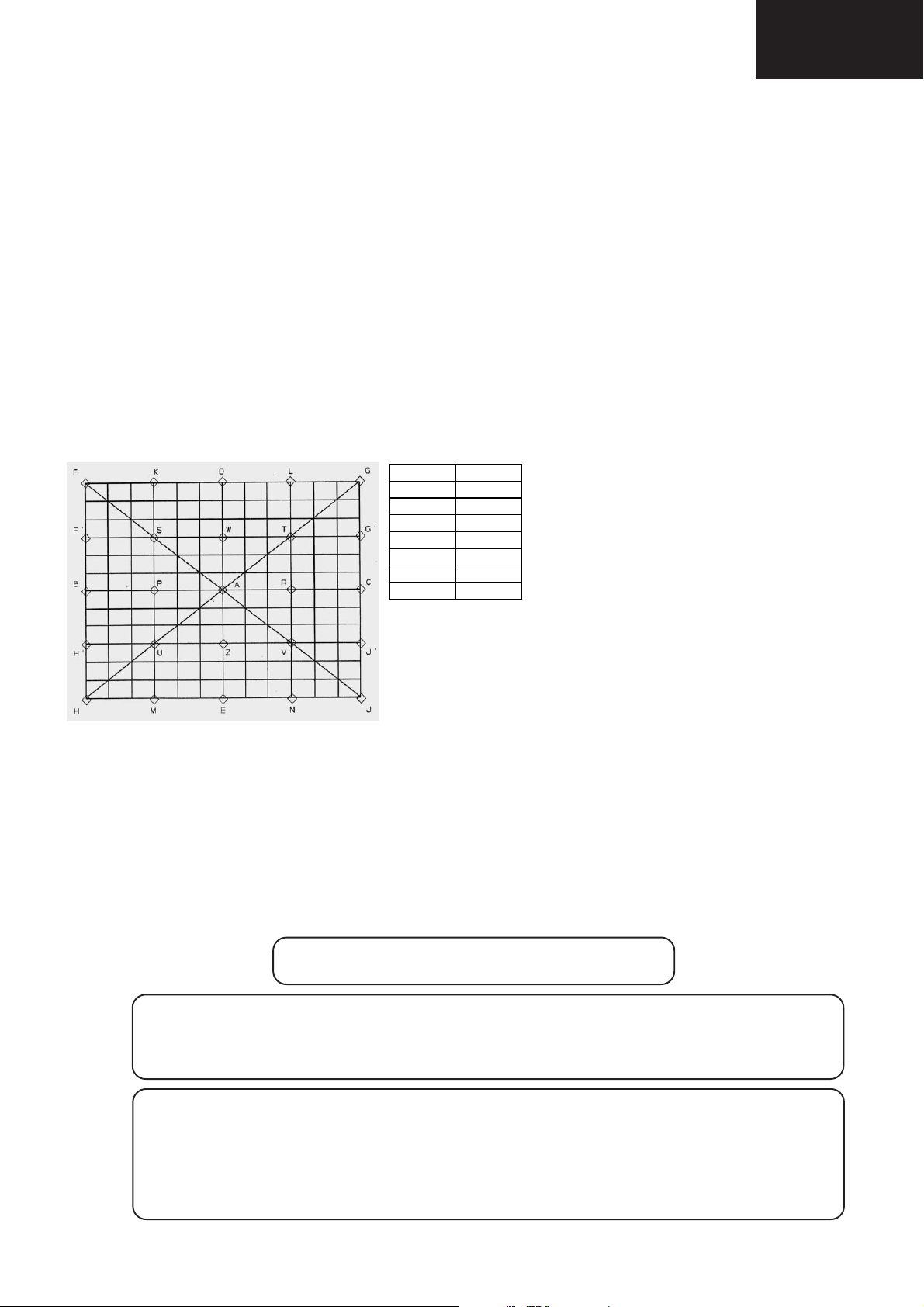

Angle

Change Angle by pressing Left/Right buttons till the vertical lines of the crosshatch pattern become

completely perpendicular to horizontal lines without any angle of vertical deviation. Check and readjust

ANGLE item if the adjustment becomes improper after some other geometric adjustments are done.

Bow

Change Bow by pressing Left/Right buttons till the vertical lines especially ones close to the left and

right sides will of equal and symmetrical bending, i.e. they together will neither be towards left side nor

right side. Check and readjust BOW item if the adjustment becomes improper after some other

geometric adjustments are done.

4:3 Horizontal Blank Start

Page 30

WDR

The amplitude of R of RGB output can be adjusted with the drive parameter WDR.

WDG

The amplitude of G of RGB output can be adjusted with the drive parameter WDG.

WDB

The amplitude of B of RGB output can be adjusted with the drive parameter WDB.

CR

The DC offset values of R of RGB output can be adjusted with the cutoff parameter CR.

CG

The DC offset values of G of RGB output can be adjusted with the cutoff parameter CG.

CB

The DC offset values of B of RGB output can be adjusted with the cutoff parameter CB.

COR coring level

The amplitude of the correction signal is adjustable. Small noise amplitudes in the correction signal are

suppressed by an adjustable coring circuit.

REGULAR VERT_POS (Regular mode Vertical Position)

Enter a PAL B/G circle test pattern via RF. Change Vertical Position till the test pattern is vertically

centered. Horizontal line at the center pattern is in equal distance both to upper and lower side of the

picture tube. Check and readjust Vertical Position item if the adjustment becomes improper after some

other geometric adjustments are done.

It’s used to adjust the vertical position of regular mode.

REGULAR VERT_AMPL (Regular mode Vertical Amplitude)

It’s used to adjust the vertical amplitude of regular mode.

REGULAR VERT_SCOR (Regular mode Vertical S-Correction)

It’s used to adjust the vertical s-correction of regular mode.

REGULAR VERT_SSYM(Regular mode Vertical S Symmetry)

It’s used to adjust the vertical s-symetry of regular mode.

REGULAR TRAPEZE (Regular mode Trapeze)

Change Trapezium by pressing Left/Right buttons till vertical lines, especially lines at the sides of the

picture frame became parallel to the both sides of picture tube as close as possible. Check and readjust

TRPEZ item if the adjustment becomes improper after some other geometric adjustments are done.

It’s used to adjust the trapeze of regular mode.

REGULAR CUSHION (Regular mode Cushion)

Page 31

PANORAMIC VERT_POS (Panoramic mode Vertical Position)

It’s used to adjust the vertical position of panoramic mode.

PANORAMIC VERT_AMPL (Panoramic mode Vertical Amplitude)

It’s used to adjust the vertical amplitude of panoramic mode.

PANORAMIC VERT_SCOR (Panoramic mode Vertical S-Correction)

It’s used to adjust the vertical s-correction of panoramic mode.

PANORAMIC VERT_SSYM (Panoramic mode Vertical S-Symmetry)

It’s used to adjust the vertical s-symmetry of panoramic mode.

PANORAMIC TRAPEZE (Panoramic mode Trapeze)

It’s used to adjust the trapeze of panoramic mode.

PANORAMIC CUSHION (Panoramic mode Cushion)

It’s used to adjust the cushion of panoramic mode.

PANORAMIC HOR_COR_SYM (Panoramic mode Horizontal corner symmetry)

It’s used to adjust the horizontal corners symmetry of panoramic mode.

PANORAMIC HOR_CORNER (Panoramic mode Horizontal corner)

It’s used to adjust the horizontal corners of panoramic mode.

PANORAMIC HORZ_POS (Panoramic mode Horizontal position)

It’s used to adjust the horizontal position of panoramic mode.

PANORAMIC HORZ_AMPL (Panoramic mode Horizontal amplitude)

It’s used to adjust the horizontal amplitude of panoramic mode.

14:9 ZOOM VERT_POS (14:9 Zoom mode Vertical Position)

It’s used to adjust the vertical position of 14:9 zoom mode.

14:9 ZOOM VERT_AMPL (14:9 Zoom mode Vertical Amplitude)

It’s used to adjust the vertical amplitude of 14:9 zoom mode.

14:9 ZOOM VERT_SCOR (14:9 Zoom mode Vertical S-Correction)

It’s used to adjust the vertical s-correction of 14:9 zoom mode.

14:9 ZOOM VERT_SSYM (14:9 Zoom mode Vertical Symmetry)

It’s used to adjust the vertical s-symmetry of 14:9 zoom mode.

14:9 ZOOM TRAPEZE (14:9 Zoom mode Trapeze)

It’s used to adjust the trapeze of 14:9 zoom mode.

Page 32

16:9 ZOOM VERT_POS (16:9 Zoom mode Vertical Position)

It’s used to adjust the vertical position of 16:9 zoom mode.

16:9 ZOOM VERT_AMPL (16:9 Zoom mode Vertical Amplitude)

It’s used to adjust the vertical amplitude of 16:9 zoom mode.

16:9 ZOOM VERT_SCOR (16:9 Zoom mode Vertical S-Correction)

It’s used to adjust the vertical s-correction of 16:9 zoom mode.

16:9 ZOOM VERT_SSYM (16:9 Zoom mode Vertical S-Symmetry)

It’s used to adjust the vertical s-symmetry of 16:9 zoom mode.

16:9 ZOOM TRAPEZE (16:9 Zoom mode Trapeze)

It’s used to adjust the trapeze of 16:9 zoom mode.

16:9 ZOOM CUSHION (16:9 Zoom mode Cushion)

It’s used to adjust the cushion of 16:9 zoom mode.

16:9 ZOOM HOR_COR_SYM (16:9 Zoom mode Horizontal corner symmetry)

It’s used to adjust the horizontal corners symmetry of 16:9 zoom mode.

16:9 ZOOM HOR_CORNER (16:9 Zoom mode Horizontal corner)

It’s used to adjust the horizontal corners of 16:9 zoom mode.

16:9 ZOOM HORZ_POS (16:9 Zoom mode Horizontal position)

It’s used to adjust the horizontal position of 16:9 zoom mode.

16:9 ZOOM HORZ_AMPL (16:9 Zoom mode Horizontal amplitude)

It’s used to adjust the horizontal amplitude of 16:9 zoom mode.

16:9 ZOOM SUBTITLE VERT_POS (16:9 Zoom Subtitle mode Vertical position)

It’s used to adjust the vertical position of 16:9 zoom subtitle mode.

16:9 ZOOM SUBTITLE VERT_AMPL (16:9 Zoom Subtitle mode Vertical amplitude)

It’s used to adjust the vertical amplitude of 16:9 zoom subtitle mode.

16:9 ZOOM SUBTITLE VERT_SCOR (16:9 Zoom Subtitle mode Vertical S-Correction)

It’s used to adjust the vertical s-correction of 16:9 zoom subtitle mode.

16:9 ZOOM SUBTITLE VERT_SSYM (16:9 Zoom Subtitle mode Vertical Symmetry)

It’s used to adjust the vertical s-symmetry of 16:9 zoom subtitle mode.

16:9 ZOOM SUBTITLE TRAPEZE (16:9 Zoom Subtitle mode Trapeze)

It’s used to adjust the trapeze of 16:9 zoom subtitle mode.

Page 33

OSD Position

It’s used to adjust the horizontal position of the OSD.

BCLTHR

Beam current threshold

BCLG

Beam current loop gain

ROTATION (TILT)

This adjustment only works when the TV has rotation option. Change TILT by pressing Left/Right

buttons to rotate the complete raster clock-wise and counter clock-wise depending on the CRT. Check

and readjust TRPEZ item if the adjustment becomes improper after some other geometric adjustments

are done.

LSLSA, LSLSB, LSL2, LSLTA, LSLTB (Luma soft limiter)

LSLSA: Luma soft limiter slope A (fixed)

LSLSB: Luma soft limiter slope B (fixed)

LSL2: Luma soft limiter absolute limit (fixed)

LSLTA: Luma soft limiter segment A tilt point (fixed)

LSLTB: Luma soft limiter segment A tilt point (fixed)

REFERENCE WDR RED (NORMAL)

The amplitude of R of RGB output can be adjusted with the drive parameter WDR for the colour

temperature of normal mode.

REFERENCE WDR GREEN (NORMAL)

The amplitude of G of RGB output can be adjusted with the drive parameter WDR for the colour

temperature of normal mode.

REFERENCE WDR BLUE (NORMAL)

The amplitude of B of RGB output can be adjusted with the drive parameter WDR for the colour

temperature of normal mode.

REFERENCE CUTOFF RED

It’s fixed.

REFERENCE CUTOFF GREEN

It’s fixed.

REFERENCE CUTOFF BLUE

It’s fixed.

IBRM

Internal Brightness, the brightness for measurement can be set to measure at higher cutoff current. The

Page 34

POFS2 (RGB HORIZONTAL SHIFT)

It’s used to adjust the horizontal position of RGB signal.

REFERENCE WDR RED COOL

The amplitude of R of RGB output can be adjusted with the drive parameter WDR for the colour temp of

cool mode.

REFERENCE WDR GREEN COOL

The amplitude of G of RGB output can be adjusted with the drive parameter WDR for the colour temp of

cool mode.

REFERENCE WDR BLUE COOL

The amplitude of B of RGB output can be adjusted with the drive parameter WDR for the colour temp of

cool mode.

REFERENCE WDR RED WARM

The amplitude of R of RGB output can be adjusted with the drive parameter WDR for the colour temp of

warm mode.

REFERENCE WDR GREEN WARM

The amplitude of G of RGB output can be adjusted with the drive parameter WDR for the colour temp of

cool mode.

REFERENCE WDR BLUE WARM

The amplitude of B of RGB output can be adjusted with the drive parameter WDR for the colour temp of

cool mode.

STANDARD MODE BRIGHTNESS

It’s used to adjust the brightness value of standard mode.

STANDARD MODE COLOUR

It’s used to adjust the colour value of standard mode.

STANDARD MODE CONTRAST

It’s used to adjust the contrast value of standard mode.

FULL VERT_POS (16:9 MODE)

It’s used to adjust the vertical position of 16:9 mode (full mode).

FULL VERT_AMPL

It’s used to adjust the vertical amplitude of 16:9 mode (full mode).

FULL VERT_SCOR

It’s used to adjust the vertical s-correction of 16:9 mode (full mode).

Page 35

FULL HORZ_POS

It’s used to adjust the horizontal position of 16:9 mode (full mode).

FULL HORZ_AMPL

It’s used to adjust the horizontal amplitude of 16:9 mode (full mode).

BRIGHT MODE BRIGHTNESS

It’s used to adjust the brightness value of bright mode.

BRIGHT MODE COLOUR

It’s used to adjust the colour value of bright mode.

BRIGHT MODE CONTRAST

It’s used to adjust the contrast value of bright mode.

SOFT MODE BRIGHTNESS

It’s used to adjust the brightness value of soft mode.

SOFT MODE COLOUR

It’s used to adjust the colour value of soft mode.

SOFT MODE CONTRAST

It’s used to adjust the contrast value of soft mode.

PERSONAL MODE FACTORY SETTING BRIGHTNESS

It’s fixed.

PERSONAL MODE FACTORY SETTING COLOUR

It’s fixed.

PERSONAL MODE FACTORY SETTING CONTRAST

It’s fixed.

SCINC FOR PANAROMIC MODE

scaler1 coefficient, this scaler is compressing the signal.

SCINC1 FOR PANAROMIC MODE

scaler2 coefficient, this scaler is expanding the signal.

VOLUME AFTER APS

It’s used to adjust the volume level after APS.

VERTICAL SCROLL

It’s used to adjust the step width for scroll function.

Page 36

14:9 RGB CUSHION

It’s used to adjust the cushion in 14:9 mode for RGB signals.

PANAROMIC RGB HORIZONTAL AMPLITUDE

It’s used to adjust the horizontal amplitude in panoramic mode for RGB signals.

16:9 RGB HORIZANTOL AMPLITUDE

It’s used to adjust the horizontal amplitude in 16:9 mode for RGB signals.

16:9 SUBTITLE RGB HORIZONTAL AMPLITUDE

It’s used to adjust the horizontal amplitude in 16:9 subtitle mode for RGB signals.

FULL RGB HORIZONTAL AMPLITUDE

It’s used to adjust the horizontal amplitude in full mode for RGB signals.

TELETEXT HORZ_POS

It’s used to adjust the horizontal position of teletext signal.

Page 37

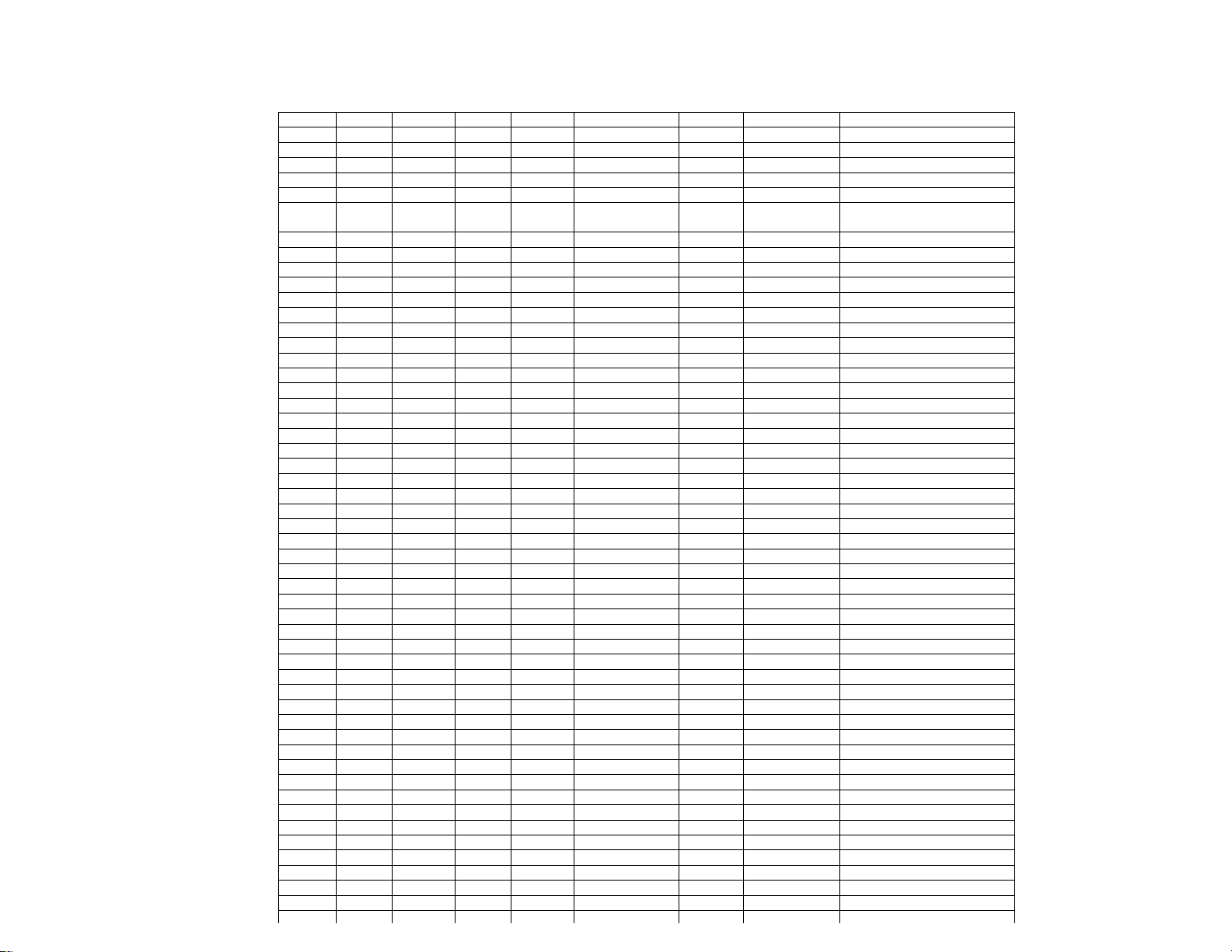

2835 2835W ADJUST EXPLANATION

MULTI MULTI - PAL I

000 White Point RED 255 255

001 White Point GREEN 126 036

002 Whit Point BLUE 127 019

003 AGC (Automatic Gain Control) 20

It will be adjusted to

below 1V of Max. AGC

for each TV.

004 IF-PLL Negative 030 030

005 IF-PLL Positive 026 026

006 Y-Delay 003 002

007 Y-Delay SECAM 004 003

008 Y-Delay NTSC 005 005

009 Y-Delay OTHER 005 005

010 Vertical Position Offset 127 127

011 Vertical Amplitude Offset 127 127

012 Horizontal Position Offset 127 127

013 Horizontal Amplitude Offset 127 127

014 Vertical Blank Start (It will be used only at 4:3 tube for 16:9

mode adjustment)

015 Vertical Blank Stop (It will be used only at 4:3 tube for 16:9

mode adjustment)

016 Angle 132 132

017 Bow 126 131

018 4:3 Horz. Blank Start (It will be used only at 16:9 tube for 4:3

mode adjustment)

019 4:3 Horz. Blank Stop (It will be used only at 16:9 tube for 4:3

mode adjustment)

020 EHTV compensation 054 066

021 EHTTM compensation 004 001

022 EHTEW compensation 219 160

023 WDR

024 WDG

025 WDB

026 CR

027 CG

028 CB

029 COR coring level 015 031

030 REGULAR VERT_POS (Vertical Position) 128 129

031 REGULAR VERT_AMPL (Vertical Amplitude) 081 055

032 REGULAR VERT_SCOR (Vertical S Correction) 131 129

149 119

013 034

021 042

140 175

VIDEO PROCESSOR

ADJUSTS ITSELF.

Page 38

049 PANORAMIC HORZ_AMPL - 013

050 14:9 ZOOM VERT_POS - 129

051 14:9 ZOOM VERT_AMPL - 043

052 14:9 ZOOM VERT_SCOR - 129

053 14:9 ZOOM VERT_SSYM - 140

054 14:9 ZOOM TRAPEZE - 125

055 14:9 ZOOM CUSHION - 159

056 14:9 ZOOM HOR_COR_SYM - 141

057 14:9 ZOOM HOR_CORNER - 110

058 14:9 ZOOM HORZ_POS - 053

059 14:9 ZOOM HORZ_AMPL - 032

060 16:9 ZOOM VERT_POS - 129

061 16:9 ZOOM VERT_AMPL - 035

062 16:9 ZOOM VERT_SCOR - 129

063 16:9 ZOOM VERT_SSYM - 148

064 16:9 ZOOM TRAPEZE - 125

065 16:9 ZOOM CUSHION - 164

066 16:9 ZOOM HOR_COR_SYM - 138

067 16:9 ZOOM HOR_CORNER - 104

068 16:9 ZOOM HORZ_POS - 036

069 16:9 ZOOM HORZ_AMPL - 020

070 16:9 ZOOM SUBTITLE VERT_POS - 137

071 16:9 ZOOM SUBTITLE VERT_AMPL - 039

072 16:9 ZOOM SUBTITLE VERT_SCOR - 124

073 16:9 ZOOM SUBTITLE VERT_SSYM - 146

074 16:9 ZOOM SUBTITLE TRAPEZE - 119

075 16:9 ZOOM SUBTITLE CUSHION - 164

076 16:9 ZOOM SUBTITLE HOR_COR_SYM - 162

077 16:9 ZOOM SUBTITLE HOR_CORNER - 081

078 16:9 ZOOM SUBTITLE HORZ_POS - 035

079 16:9 ZOOM SUBTITLE HORZ_AMPL - 021

080 OSD Position 217 205

081 BCLTHR Beam current threshold 050 060

082 BCLG Beam current loop gain 008 007

083 ROTATION (TILT) 000 000

084 LSLSA Luma soft limiter 000 003

085 LSLSB Luma soft limiter 000 000

086 LSL2 Luma soft limiter 255 255

087 LSLTA Luma soft limiter 000 000

088 LSLTB Luma soft limiter 000 001

089 REFERENCE WDR RED (NORMAL) 088 092

090 REFERENCE WDR GREEN (NORMAL) 074 083

091 REFERENCE WDR BLUE (NORMAL) 075 082

Page 39

108 STANDARD MODE COLOUR 050 047

109 STANDARD MODE CONTRAST 022 029

110 FULL VERT_POS (16:9 MODE) 128 129

111 FULL VERT_AMPL 093 055

112 FULL VERT_SCOR 131 129

113 FULL VERT_SSYM 133 136

114 FULL TRAPEZE 127 126

115 FULL CUSHION 148 153

116 FULL HOR_COR_SYM 137 136

117 FULL HOR_CORNER 109 109

118 FULL HORZ_POS 055 035

119 FULL HORZ_AMPL 057 020

120 BRIGHT MODE BRIGHTNESS 027 043

121 BRIGHT MODE COLOUR 050 050

122 BRIGHT MODE CONTRAST 030 032

123 SOFT MODE BRIGHTNESS 027 043

124 SOFT MODE COLOUR 050 058

125 SOFT MODE CONTRAST 017 020

126 PERSONAL MODE FACTORY SETTING BRIGHTNESS 027 043

127 PERSONAL MODE FACTORY SETTING COLOUR 050 050

128 PERSONAL MODE FACTORY SETTING CONTRAST 030 032

129 SCINC FOR PANORAMIC MODE 032 056

130 SCINC1 FOR PANORAMIC MODE 032 125

131 VOLUME AFTER APS 005

132 VERTICAL SCROLL 005 008

133 14:9 HORIZONTAL START (It will be used only at 16:9 tube

for 14:9 mode adjustment)

134 14:9 HORIZONTAL STOP (It will be used only at 16:9 tube

for 14:9 mode adjustment)

135 4:3 RGB HORIZONTAL AMPLITUDE 055 074

136 4:3 RGB CUSHION 163 150

137 14:9 RGB HORIZONTAL AMPLITUDE - 055

138 14:9 RGB CUSHION - 158

139 PANAROMIC RGB HORIZONTAL AMPLITUDE - 031

140 16:9 RGB HORIZONTAL AMPLITUDE - 027

141 16:9 SUBTITLE RGB HORIZONTAL AMPLITUDE - 027

142 FULL RGB HORIZONTAL AMPLITUDE 054 027

143 TELETEXT HORIZONTAL POSITION 101 095

- 031

- 185

Page 40

14.3.OPTIONS MENU

Select the parameter by pressing up/down buttons. Adjust the parameter by pressing Left/Right

buttons. . In OPTIONS menu, some of the changed parameters are not stored automatically. To store

the adjusted parameters, you should turn off and on TV.

OPTIONS...

000 02

001 00

002 22

003 08

004 00

005 10

006 00

007 56

008 39

009 0F

00000010

00000000

00100010

00001000

00000000

00010000

00000000

01010110

00111001

00001111

Option 0. Video Processor Crystal Indication

B7: x = x

B6: x = x

B5: x = x

B4: x = x

B3: x = x

B2: x = x

B1: Xa = note1 (Crystal indication)

B0: Xb = note1 (Crystal indication)

note 1:

Xa,Xb

0,1 : Pal M, Pal N, NTSC M

Pin 34 : 3.58 (1, 2 or 3 crystals)

Pin 35 : No crystal

1,0 : Pal BG, Pal DK, Pal I/I+, Secam BG, Secam DK, Secam L/L’, Secam K1

Pin 34 : No crystal

Pin 35 : 4.43 (1 crystal)

1,1 : Pal BG, Pal DK, Pal I/I+, Secam BG, Secam DK, Secam L/L’, Secam K1, Pal M, Pal N, Ntsc M

Pin 34 : 3.58 (1, 2 or 3 crystals)

Pin 35 : 4.43 (1 crystal)

Option 1. (0x01) Video Processor Decoder Mode Register

Page 41

B4: x = x

B3: x = x

B2: x = x

B1: LUMA = 1 Luma Soft Limiter Enabled

B0: BB = 1 Blue Background Option

Option 3. (0x19) Video Processor Cathode Drive Level

B7: x = x

B6: x = x

B5: x = x

B4: x = x

B3: x = x

B2: x = x

B1: x = x