PRODUCT SELECTION GUIDE

PARAMETER WS27C256L-12 WS27C256L-15 WS27C256L-20

Address Access Time (Max) 120 ns 150 ns 200 ns

Chip Select Time (Max) 120 ns 150 ns 200 ns

Output Enable Time (Max) 35 ns 40 ns 40 ns

WS27C256L

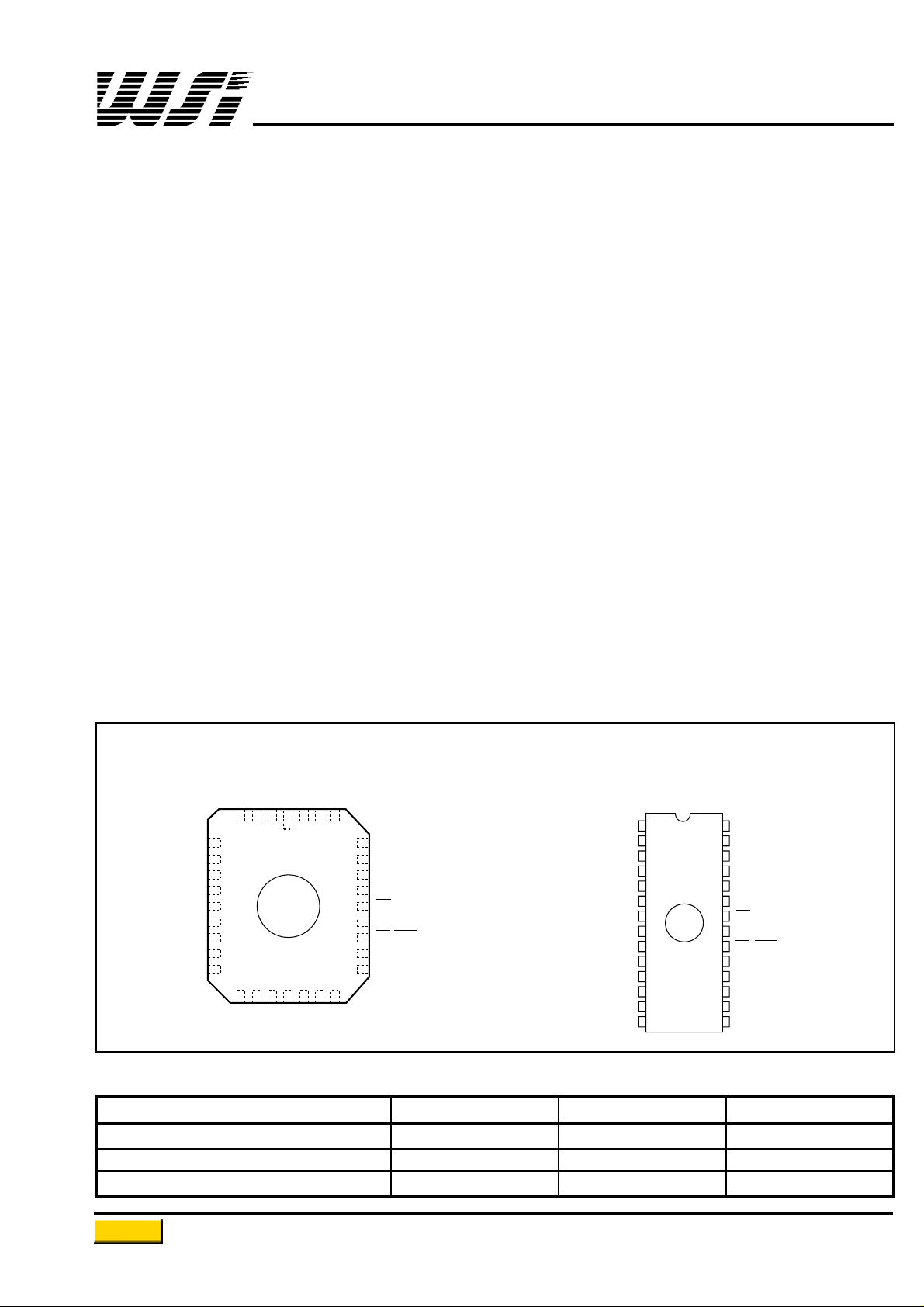

TOP VIEW

Chip Carrier CERDIP

PIN CONFIGURATION

4-19

Military 32K x 8 CMOS EPROM

KEY FEATURES

• High Performance CMOS • Ceramic Leadless Chip Carrier (CLLCC)

— 120 ns Access Time

• EPI Processing

• Fast Programming

— Latch-Up Immunity to 200 mA

• DESC SMD No. 5962-86063

— ESD Protection Exceeds 2000 Volts

• 300 Mil DIP or Standard 600 Mil DIP • JEDEC Standard Pin Configuration

GENERAL DESCRIPTION

The WS27C256L is a performance oriented 256K UV Erasable Electrically Programmable Read Only Memory

organized as 32K words x 8 bits/word. It is manufactured using an advanced CMOS technology which enables it to

operate at speeds up to 120 nsecs. The memory was designed utilizing WSI's patented self-aligned split gate

EPROM cell, resulting in a low power device with a very cost effective die size.

The WS27C256L 256K EPROM provides 32K of 8 bit wide code store capacity for DSP, microprocessor, and

microcontroller-based systems. Its 120 nsec access time over the full Military temperature range provides the

potential of no-wait state operation. And where this parameter is important, the WS27C256L provides the user with

a very fast 35 nsec TOEoutput enable time.

The WS27C256L is offered in a 28 pin 300 mil skinny CERDIP or the standard 600 mil CERDIP, and also in a

32 pad Ceramic Leadless Chip Carrier (CLLCC) for surface mount applications. All packages incorporate the

standard JEDEC EPROM pinout.

A

8

A

9

A

11

NC

OE

A

10

CE/PGM

O

7

O

6

A

6

A

5

A

4

A

3

A

2

A

1

A

0

NC

O

0

A7A12VPPNC

VCCA14A

13

O1 O2 NC O3 O4 O

5

1

432

32 31

30

29

28

27

26

25

24

23

22

21

5

6

7

8

9

10

11

12

13

14 15 1617181920

GND

V

CC

A

14

A

13

A

8

A

9

A

11

OE

A

10

CE/PGM

O

7

O

6

O

5

O

4

O

3

V

PP

A

12

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

O

0

O

1

O

2

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Return to Main Menu

AC READ CHARACTERISTICS

Over Operating Range (See Above)

SYMBOL PARAMETER

WS27C256L-12 WS27C256L-15 WS27C256L-20

UNITS

MIN MAX MIN MAX MIN MAX

t

ACC

Address to Output Delay 120 150 200

t

CE

CE to Output Delay 120 150 200

t

OE

OE to Output Delay 35 40 40

t

DF

Output Disable to Output Float

35 40 40

ns

(Note 3)

Output Hold From Addresses,

t

OH

CE or OE, Whichever Occurred 0 0 0

First (Note 3)

DC READ CHARACTERISTICS

Over Operating Range. (See Above)

SYMBOL PARAMETER TEST CONDITIONS MIN MAX UNITS

V

IL

Input Low Voltage –0.5 0.8 V

V

IH

Input High Voltage 2.0 V

CC

+ 1 V

V

OL

Output Low Voltage IOL= 2.1 mA 0.4 V

V

OH

Output High Voltage IOH= –400 µA 3.5 V

I

SB1

VCCStandby Current (CMOS) CE = V

CC

± 0.3 V (Note 2) 100 µA

I

SB2

VCCStandby Current CE = V

IH

1mA

ICCVCCActive Current

CE = OE = V

IL

F = 5 MHz 40 mA

(Note 1)

F = 8 MHz 50 mA

I

PP

VPPSupply Current VPP= V

CC

100 µA

V

PP

V

PP

Read Voltage V

CC

–0.4 V

CC

V

I

LI

Input Leakage Current VIN= 5.5 V or Gnd –10 10 µA

I

LO

Output Leakage Current V

OUT

= 5.5 V or Gnd –10 10 µA

WS27C256L

4-20

OPERATING RANGE

RANGE TEMPERATURE V

CC

Military –55°C to +125°C +5V ± 10%

ABSOLUTE MAXIMUM RATINGS*

Storage Temperature............................–65° to + 150°C

Voltage on any Pin with

Respect to Ground ....................................–0.6V to +7V

VPPwith Respect to Ground...................–0.6V to + 14V

V

CC

Supply Voltage with

Respect to Ground ....................................–0.6V to +7V

ESD Protection..................................................>2000V

NOTES: 1. The supply current is the sum of I

CC

and IPP. The maximum current value is with Outputs O0to O7unloaded.

2. CMOS inputs: VIL= GND ± 0.3V, VIH= VCC± 0.3 V.

*

NOTICE:

Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to the device.

This is a stress rating only and functional operation of

the device at these or any other conditions above

those indicated in the operational sections of this

specification is not implied. Exposure to absolute

maximum rating conditions for extended periods of

time may affect device reliability.

NOTE: 3.

This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven – see timing

diagram.

SYMBOL PARAMETER CONDITIONS TYP

(6)

MAX UNITS

C

IN

Input Capacitance VIN= 0V 4 6 pF

C

OUT

Output Capacitance V

OUT

= 0V 8 12 pF

C

VPP

VPPCapacitance VPP= 0 V 18 25 pF

4-21

WS27C256L

AC READ TIMING DIAGRAM

t

ACC

t

OH

ADDRESS VALID

VALID OUTPUT

ADDRESSES

V

IH

V

IL

t

OE

t

DF

t

CE

CE

OE

V

IH

V

IH

V

IL

V

IH

V

IL

V

IL

HIGH ZHIGH Z

(5)

(4)

(4)

OUTPUT

CAPACITANCE

(5)

TA= 25°C, f = 1 MHz

100 pF

(INCLUDING SCOPE

AND JIG

CAPACITANCE)

820 Ω

2.01 V

D.U.T.

A.C. TESTING INPUT/OUTPUT WAVEFORMTEST LOAD

(High Impedance Test Systems)

2.4

0.4

2.0

0.8

2.0

0.8

TEST

POINTS

NOTES: 5. This parameter is only sampled and is not 100% tested.

6. Typical values are for TA= 25°C and nominal supply voltages.

A.C. testing inputs are driven at 2.4 V for a logic "1" and 0.4 V

for a logic "0." Timing measurements are made at 2.0 V for a

logic "1" and 0.8 V for a logic "0".

NOTE: 4. OE may be delayed up to t

CE

– tOEafter the falling edge of CE without impact on tCE.

NOTE: 7. Provide adequate decoupling capacitance as close as possible to this device to achieve the published A.C. and D.C. parameters.

A 0.1 microfarad capacitor in parallel with a 0.01 microfarad capacitor connected between VCCand ground is recommended.

Inadequate decoupling may result in access time degradation or other transient performance failures.

PROGRAMMING INFORMATION

DC CHARACTERISTICS

(TA= 25 ± 5°C, VCC= 6.0 ± 0.25 V, VPP= 12.5 ± 0.5 V. See Notes 8, 9 and 10)

SYMBOLS PARAMETER MIN MAX UNITS

I

LI

Input Leakage Current (VIN= VCCor Gnd) –10 10 µA

I

PP

VPPSupply Current During

60 mA

Programming Pulse (CE/PGM = VIL)

I

CC

VCCSupply Current 40 mA

V

IL

Input Low Voltage –0.1 0.8 V

V

IH

Input High Voltage 2.0 VCC+ 0.3 V

V

OL

Output Low Voltage During Verify (IOL= 2.1 mA) 0.4 V

V

OH

Output High Voltage During Verify (IOH= –400 µA) 3.5 V

SYMBOLS PARAMETER MIN TYP MAX UNITS

t

AS

Address Setup Time 2 µs

t

COH

CE High to OE High 2 µs

t

OES

Output Enable Setup Time 2 µs

t

OS

Data Setup Time 2 µs

t

AH

Address Hold Time 0 µs

t

OH

Data Hold Time 2 µs

t

DF

Chip Disable to Output Float Delay 0 55 ns

t

OE

Data Valid From Output Enable 55 ns

t

VS

VPPSetup Time 2 µs

t

PW

PGM Pulse Width 500 1000 µs

t

OCX

OE Low to CE "Don't Care" 2 µs

WS27C256L

4-22

NOTES: 8. V

CC

must be applied either coincidentally or before V

PP

and removed either coincidentally or after VPP.

9. V

PP

must not be greater than 14 volts including overshoot. During CE/PGM = VIL, V

PP

must not be switched from 5 volts

to 12.5 volts or vice-versa.

10. During power up the CE/PGM pin must be brought high (≥ VIH) either coincident with or before power is applied to VPP.

AC CHARACTERISTICS

(TA= 25 ± 5°C, VCC= 6.0 ± 0.25 V, VPP= 12.5 ± 0.5 V)

PROGRAMMING WAVEFORM

ADDRESS STABLE

ADDRESSES

V

PP

V

PP

V

CC

CE/PGM

DATA

t

AS

t

PW

t

OS

t

OH

t

OE

t

AH

t

DF

t

VS

t

CES

t

OES

t

OCX

t

COH

DATA OUT

DATA IN STABLE

OE

V

IH

V

IL

V

IH

V

IL

VALID

HIGH Z

ORDERING INFORMATION

OPERATING WSI

PART NUMBER TEMPERATURE MANUFACTURING

RANGE PROCEDURE

WS27C256L-12CMB* 120 32 Pad CLLCC C2 Military MIL-STD-883C

WS27C256L-12DMB* 120 28 Pin CERDIP, 0.6" D2 Military MIL-STD-883C

WS27C256L-12TMB* 120 28 Pin CERDIP, 0.3" T2 Military MIL-STD-883C

WS27C256L-15DMB* 150 28 Pin CERDIP, 0.6" D2 Military MIL-STD-883C

WS27C256L-15TMB* 150 28 Pin CERDIP, 0.3" T2 Military MIL-STD-883C

WS27C256L-20DMB* 200 28 Pin CERDIP, 0.6" D2 Military MIL-STD-883C

4-23

WS27C256L

NOTE: The actual part marking will not include the initials "WS."

*SMD product. See page 4-1 for SMD number.

PROGRAMMING/ALGORITHMS/ERASURE/PROGRAMMERS

REFER TO

PAGE 5-1

The WS27C256L is programmed using Algorithm C shown on page 5-7.

SPEED PACKAGE PACKAGE

(ns) TYPE DRAWING

MODE

PINS

CE/PGM OE A

9

A

0

V

PP

V

CC

OUTPUTS

Read V

IL

V

IL

XXVCC5.0 V D

OUT

Output Disable X V

IH

XXVCC5.0 V High Z

Standby V

IH

XXXVCC5.0 V High Z

Programming V

IL

V

IH

XXV

PP

(12)

5.8 V D

IN

Program Verify X V

IL

XXV

PP

(12)

5.8 V D

OUT

Program Inhibit V

IH

V

IH

XXV

PP

(12)

5.0 V High Z

Signature

Manufacturer

(13)

V

IL

V

IL

V

H

(12)

V

IL

V

CC

5.0 V 23 H

Device

(13)

V

IL

V

IL

V

H

(12)

V

IH

V

CC

5.0 V C0 H

MODE SELECTION

The modes of operation of the WS27C256L are listed below. A single 5 V power supply is required in the read

mode. All inputs are TTL levels except for VPPand A9for device signature.

NOTES: 11. X can be VILor VIH.

12. VH= VPP= 12.5 ± 0.5 V.

13. A1– A8, A10– A14= VIL.

Return to Main Menu

Loading...

Loading...