SGS Thomson Microelectronics VNS3NV04D Datasheet

®

Februa ry 2003 1/14

VNS3NV04D

“OMNIFE T II” :

FULLY AUTOPROTECTED POWER MOSFET

1

n

LINEAR CURRENT LIMITATION

n

THERMAL SHUT DOWN

n

SHORT CIRCUIT PROTECTION

n

INTEGRATED CLAMP

n

LOW CURRENT DRAWN FRO M INPUT PIN

n

DIAGNOSTIC FEEDBACK THROUGH INPUT

PIN

n

ESD PROTECTION

n

DIRECT ACCESS TO THE GATE OF THE

POWER MOSFET (ANALOG DRIVING)

n

COMPATIBLE WITH STANDARD POWER

MOSFET

DESCRIPTION

The VNS3NV04D is a device formed by two

monolithic OMNIFET II chips housed in a

standard SO-8 package. The OMNIFET II are

designed in STMicroelectronics VIPower M0-3

Technology: they ar e intended for rep lacement of

standard Po wer M OS FETS fr om DC up t o 50 KHz

applications. Built in thermal shutdown, linear

current limitation and overvoltage clamp protects

the chip in harsh environments.

Fault feedback ca n be dete c ted by mo nitori ng the

voltage at the input pin.

TYPE R

DS(on)

I

lim

V

clamp

VNS3NV04D 120 mΩ (*) 3.5 A (*) 40 V (*)

SO-8

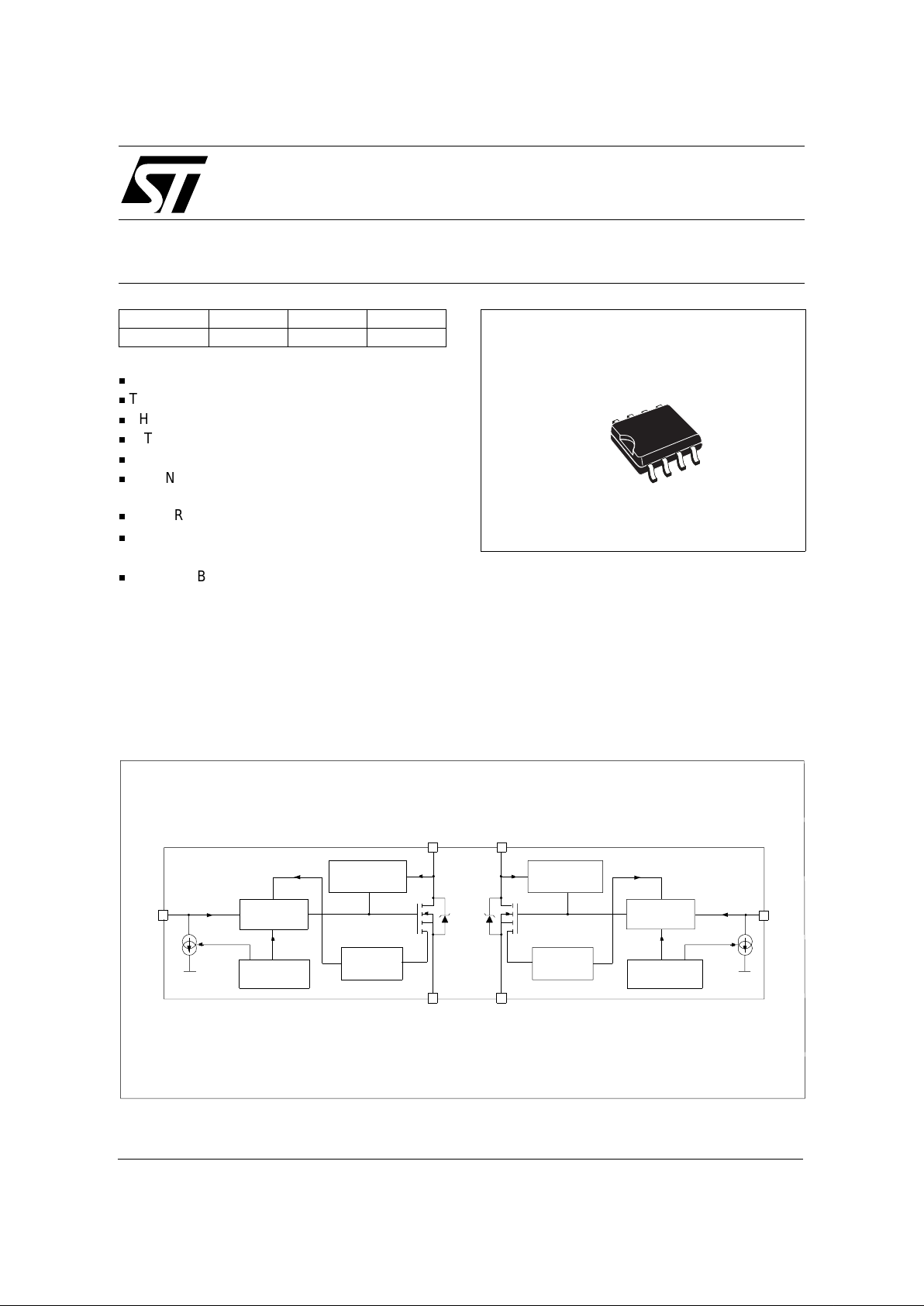

BLOCK DIAGRAM

SOURCE2

OVERVOLTAGE

LINEAR

DRAIN1

SOURCE1

CLAMP

CURRENT

LIMITER

OVER

TEMPERATURE

GATE

CONTROL

DRAIN2

OVERVOLTAGE

CLAMP

LINEAR

CURRENT

LIMITER

GATE

CONTROL

OVER

TEMPERATURE

INPUT2

INPUT1

(*)Per each device

2/14

VNS3NV04D

ABSOLUTE MAXIMUM RATI NG

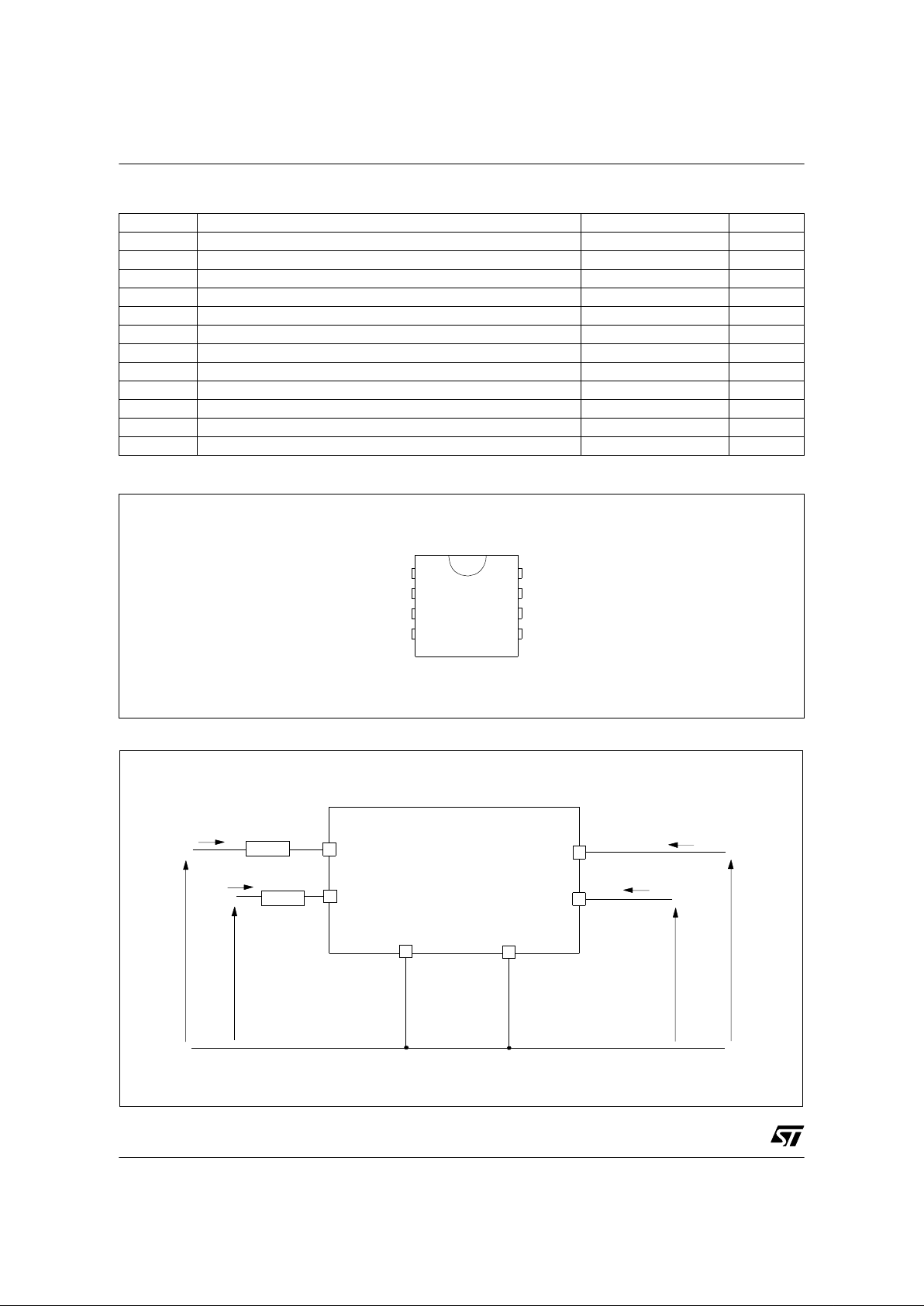

CONNECTION DIAGRAM (TO P VI EW)

Symbol Parameter Value Unit

V

DSn

Drain-source Voltage (V

INn

=0V) Intern ally Clamped V

V

INn

Input Vol tage Internally Clamp ed V

I

INn

Input Current +/-20 mA

R

IN MINn

Minimum I nput Series Impedance 220 Ω

I

Dn

Drain Current Internally Limited A

I

Rn

Reverse DC Output Current -5.5 A

V

ESD1

Electros tatic Discharge (R=1.5KΩ, C=100pF) 4000 V

V

ESD2

Electros tatic Discharge on output pins only (R=330Ω, C=150pF) 16500 V

P

tot

Total Dissipation at Tc=25°C 4 W

T

j

Operating Junction Temperature Internally limited °C

T

c

Case Operating Temperature Internally limited °C

T

stg

Storage Temperature -55 to 150 °C

1

CURRENT AND VOLTAGE CONV ENTIONS

DRAIN 2

DRAIN 1

DRAIN 2

DRAIN 1

INPUT 2

SOURCE 1

SOURCE 2

INPUT 1

1

4

5

8

DRAIN 1

INPUT 1

SOURCE 2

I

IN1

V

IN1

INPUT 2

I

IN2

SOURCE 1

DRAIN 2

V

IN2

I

D2

I

D1

V

DS1

V

DS1

R

IN1

R

IN2

3/14

VNS3NV04D

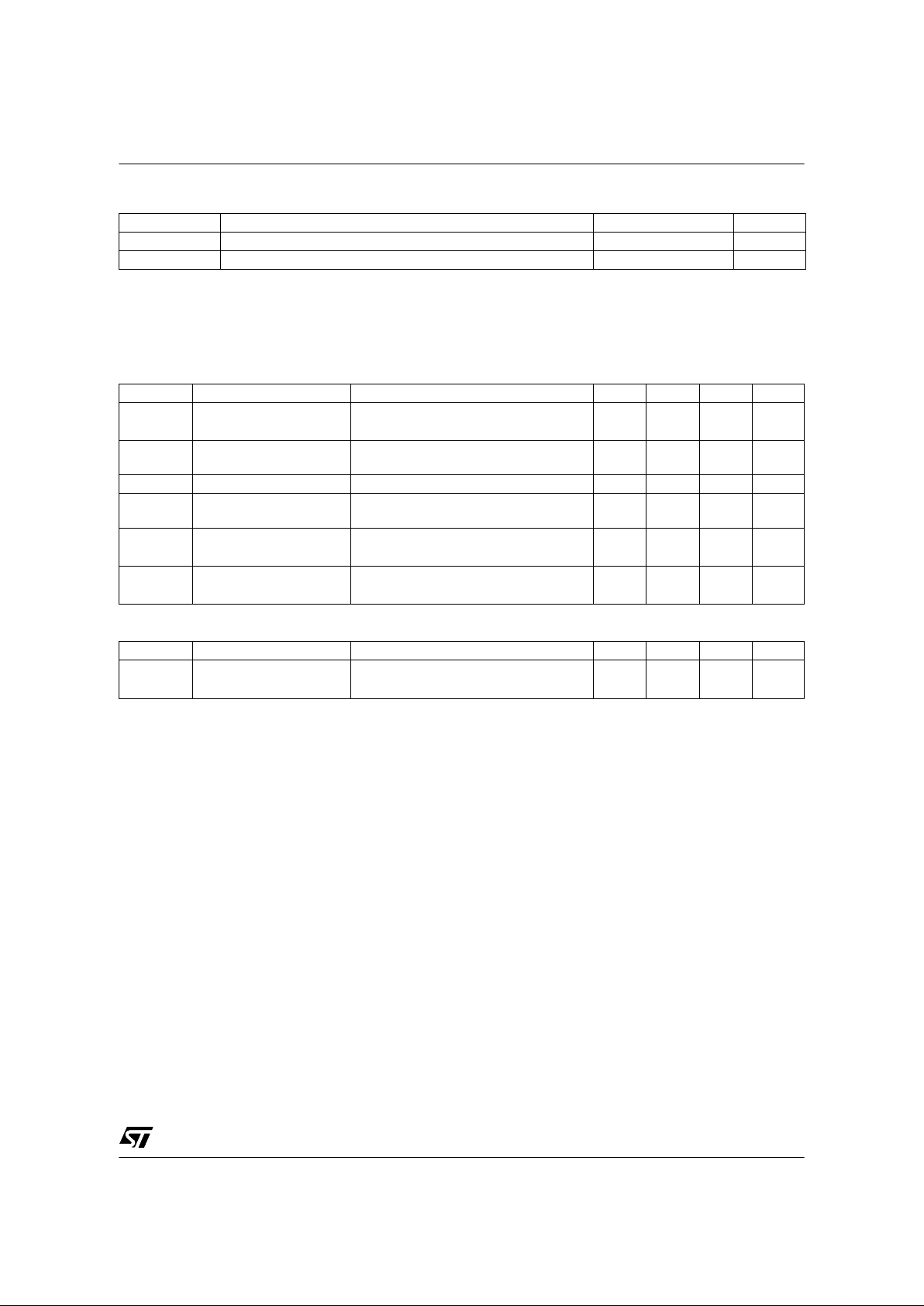

THERMAL DATA

(*) When mounted on a standard s ingle-sided FR4 boar d with 50mm

2

of Cu (at least 35 µm thick) connected to all DRAIN pins of the relative

channel.

ON

Symbol Parameter Value Unit

R

thj-lead

Ther m al Re s i st an ce Junction-lead (per channe l ) MAX 30 °C/W

R

thj-amb

Thermal Resistance Junction-ambient MAX 80(*) °C/W

Symbol Parameter Test Conditions Min Typ Max Unit

V

CLAMP

Drain-source Clamp

Voltage

V

IN

=0V; ID=1.5A 40 45 55 V

V

CLTH

Drain-source Clamp

Threshold Voltage

VIN=0V; ID=2mA 36 V

V

INTH

Input Thre shold Voltage VDS=VIN; ID=1mA 0.5 2.5 V

I

ISS

Supply Current from Input

Pin

VDS=0V; VIN=5V 100 150 µA

V

INCL

Input-Source Clamp

Voltage

IIN=1mA

I

IN

=-1mA

6

-1.0

6.8 8

-0.3

V

I

DSS

Zero Input Voltage Drain

Current (VIN=0V)

V

DS

=13V; VIN=0V; Tj=25°C

V

DS

=25V; VIN=0V

30

75

µA

Symbol Parameter Test Conditions Min Typ Max Unit

R

DS(on)

Static Drain-source On

Resistance

V

IN

=5V; ID=1.5A; Tj=25°C

V

IN

=5V; ID=1.5A

120

240

mΩ

ELECTRICAL CHARACTERISTICS (-40°C < Tj < 150°C, unless otherwise specified)

OFF

(Per each device)

1

4/14

VNS3NV04D

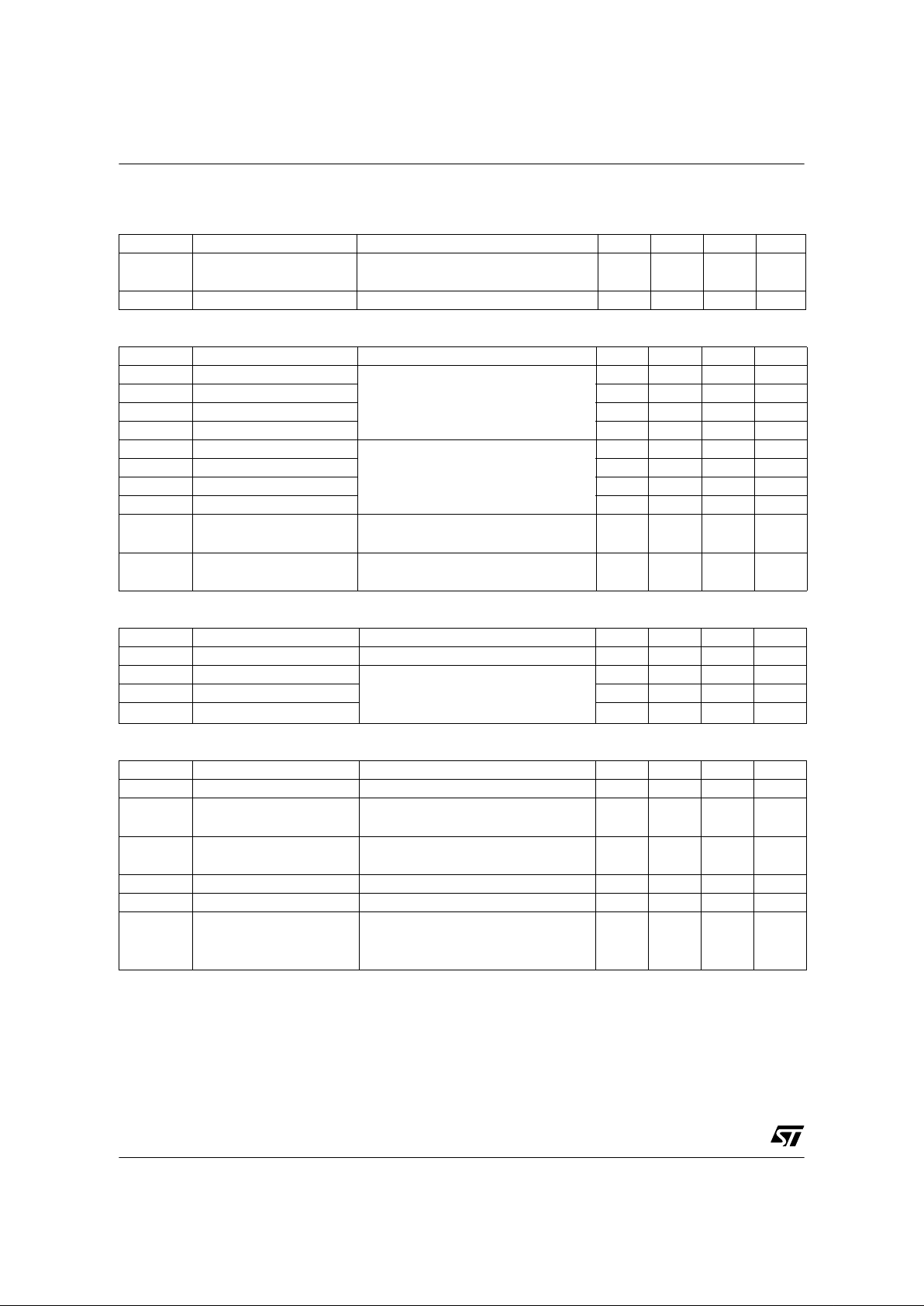

ELECTRICAL CHARACTERISTICS (continued) (Tj=25°C, unless otherwise specified)

DYNAMIC

SWITCHING

SOURCE DRAIN DIODE

PROTECTIONS (-40°C < Tj < 150°C, unless otherwise specified)

(*) Pulsed: Pu ls e duration = 300µs, duty c y c le 1.5%

Symbol Parameter Test Condit ions Min Typ Max Unit

gfs (*)

Forward

Transconductanc e

VDD=13V; ID=1.5A 5.0 S

C

OSS

Output Capacitance VDS=13V; f=1MHz; VIN=0V 150 pF

Symbol Parameter Test Conditi ons Min Typ Max Unit

t

d(on)

Turn-on Delay Time

V

DD

=15V; ID=1.5A

V

gen

=5V; R

gen=RIN MINn

=220Ω

(see figure 1)

90 300 ns

t

r

Rise Time 250 750 ns

t

d(off)

Turn-off Delay Time 450 1350 ns

t

f

Fall Time 250 750 ns

t

d(on)

Turn-on Delay Time

V

DD

=15V; ID=1.5A

V

gen

=5V; R

gen

=2.2K Ω

(see figure 1)

0.45 1.35 µs

t

r

Rise Time 2.5 7.5 µs

t

d(off)

Turn-off Delay Time 3.3 10.0 µs

t

f

Fall Time 2.0 6.0 µs

(dI/dt)

on

Turn-on Current Slope

V

DD

=15V; ID=1.5A

V

gen

=5V; R

gen=RIN MINn

=220Ω

4.7 A/µs

Q

i

Total Input Charge

V

DD

=12V; ID=1.5A; VIN=5V

I

gen

=2.13mA (see figure 5)

8.5 nC

Symbol Parameter Test Conditions Min Typ Max Unit

V

SD

(*) Forward On Voltage ISD=1.5A; VIN=0V 0.8 V

t

rr

Reverse Recovery Time ISD=1.5A; dI/dt=12A/µs

V

DD

=30V; L= 20 0 µ H

(see test circuit, figure 2)

107 ns

Q

rr

Reverse Recovery Charge 37 µC

I

RRM

Reverse Recovery Current 0.7 A

Symbol Parameter Test Conditions Min Typ Max Unit

I

lim

Drain Current Limit VIN=5V; VDS=13V 3.5 5 7 A

t

dlim

Step Response Current

Limit

V

IN

=5V; VDS=13V

10 µs

T

jsh

Overtemperature

Shutdown

150 175 200 °C

T

jrs

Overtemperature Reset 135 °C

I

gf

Fault Sink Current VIN=5V; VDS=13V; Tj=T

jsh

10 15 20 mA

E

as

Sing l e Pu lse

Avala nche Energy

starti ng T

j

=25°C; VDD=24V

V

IN

=5V; R

gen=RIN MINn

=220Ω; L=24mH

(see figures 3 & 4)

100 mJ

2

5/14

VNS3NV04D

PROTECTION FEATURES

During normal operation, the INPUT pin is

electrically connected to the gate of the internal

power MOSFET through a low impedance path.

The device then behaves like a standard power

MOSFET and can be used as a switch from DC to

50KHz. The only difference from the user’s

standpoint is that a small DC current I

ISS

(typ.

100µA) flows into the INPUT pin in order to supply

the internal circuitry.

The de vice integrates :

- OVERVOLTAGE CLAMP PROTECTION:

internally set at 45V, along with the rugged

avalanche characteristics o f the Power MOSFET

stage giv e this device unrivall ed ruggedne ss and

energy handl ing capability. This feat ure is mainly

important when driving inductive loads.

- LINEAR CURRENT LIMITER CIRCUIT: limits

the drain current ID to I

lim

whatever the INPUT pin

voltage. When the current limiter is active, the

device operates in the linear region, so power

dissipation may exceed the capability of the

heatsink. Both case and junction temperatures

increase, and if this phase lasts long enough,

junction temperature may reach the

overtemperature threshold T

jsh

.

- OVERTEMPERATURE AND SHORT CIRCUIT

PROTECTION: these are based on sensing the

chip temperature and are not dependent on the

input voltage. The location of the sensi ng eleme nt

on the chip in the power st age ar ea ensures f ast,

accurate detection of the junction temperature.

Overtemperature cutout occurs in the range 150 to

190 °C, a typical value being 170 °C. The device is

automatically restarted when the chip temperature

falls of about 15°C below shut-down temperature.

- STATUS FEEDBACK: in the case of an

overtemperature fault condition (Tj > T

jsh

), the

device tries to sink a diagnostic current Igf thro ug h

the INPUT pin in order to indicate fault condition. If

driven from a l ow impedance sou rce, this curre nt

may be used in orde r to warn the contr ol circ uit of

a device shut down. If the drive impeda nc e is h i gh

enough so that the INPUT pin dri ver is not abl e to

supply the current Igf, the INPUT pin will fall to 0V.

This will not however affect the device

operation: no requirement is put on the current

capability of t he IN PUT pin dr ive r e xcep t t o b e

able to supply the normal operation drive

current I

ISS

.

Additional features of this device are ESD

protection according to the Human Body model

and the ability to be driven from a TTL Logic

circuit.

1

Loading...

Loading...