HMOS PARALLEL INTERFACE/TIMER

.TS68000 BUS COMPATIBLE

.PORT MODES INCLUDE:

BIT I/O

UNIDIRECTIONAL8 BIT AND 16 BIT

BIDIRECTIONAL8 BITAND 16 BIT

.PROGRAMMABLE HANDSHAKINGOPTIONS

.24-BIT PROGRAMMABLE TIMERMODES

.FIVE SEPARATE INTERRUPT VECTORS

.SEPARATE PORT AND TIMER INTERRUPT

SERVICE REQUESTS

.REGISTERSAREREAD/WRITEANDDIRECT-

LY ADDRESSABLE

.REGISTERS ARE ADDRESSED FOR MOVEP

(MovePeripheral) AND DMACCOMPATIBILITY

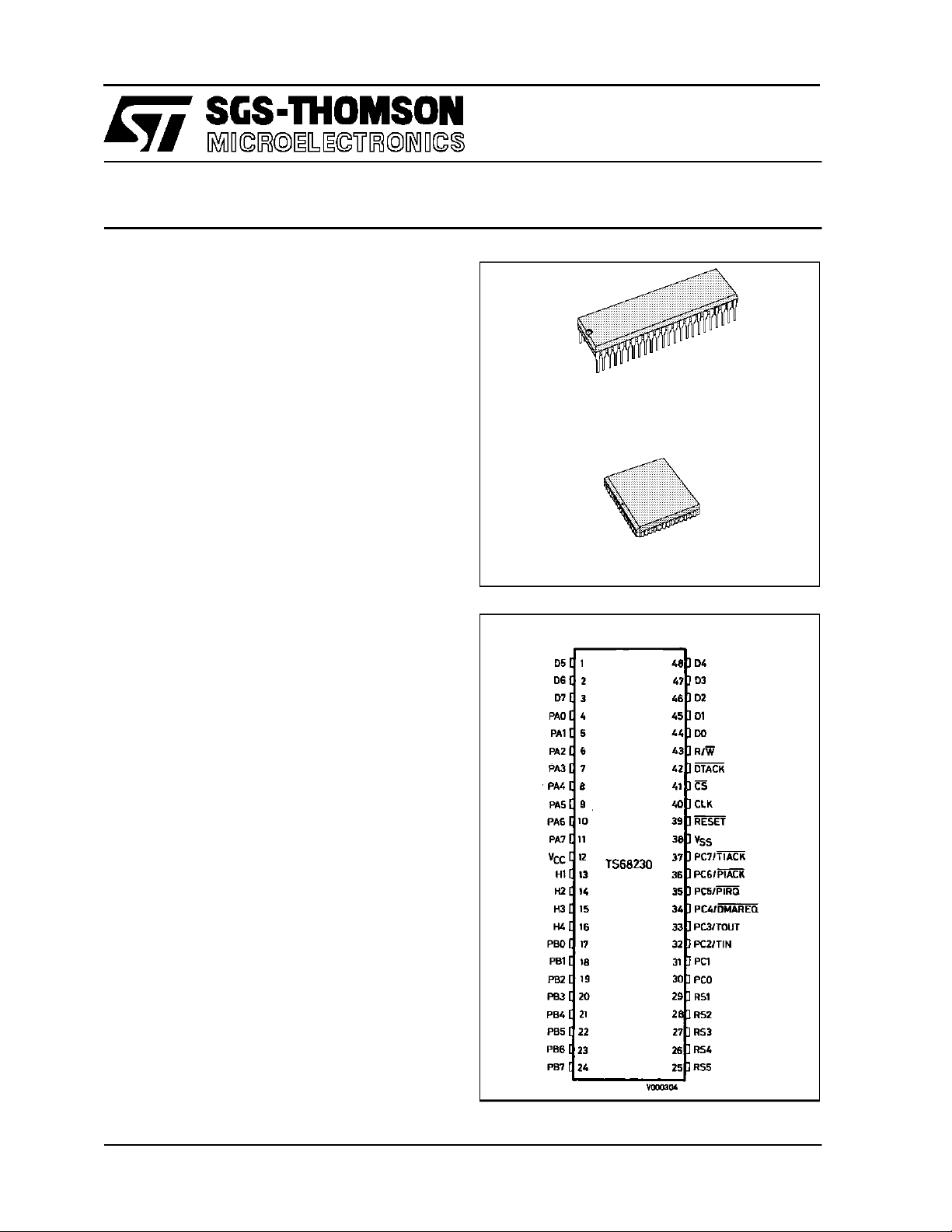

TS68 23 0

1

P

(PDIP48)

FN

(PLCC52)

DESCRIP TI ON

TheTS68230 parallelinterface/timer (PI/T)provides

versatile double buffered parallel interfaces and a

systemorientedtimerforTS68000 systems.Theparallelinterfaces operate inunidirectional orbidirectional modes, either 8 or 16 bits wide. In the

unidirectional modes, an associated data direction

register determines whether each port pinisaninput

or output. In the bidirectional modes the data direction registers are ignored and the direction isdetermined dynamically by the state of four handshake

pins. These programmable handshake pinsprovide

an interface flexible enough for connection to a wide

variety of low,medium, orhigh speedperipherals or

other computersystems.ThePI/Tports allow use of

vectored or auto-vectored interrupts, and also providea DMArequest pin for connection to the 68440

directmemory accesscontroller (DMAC)or a similar

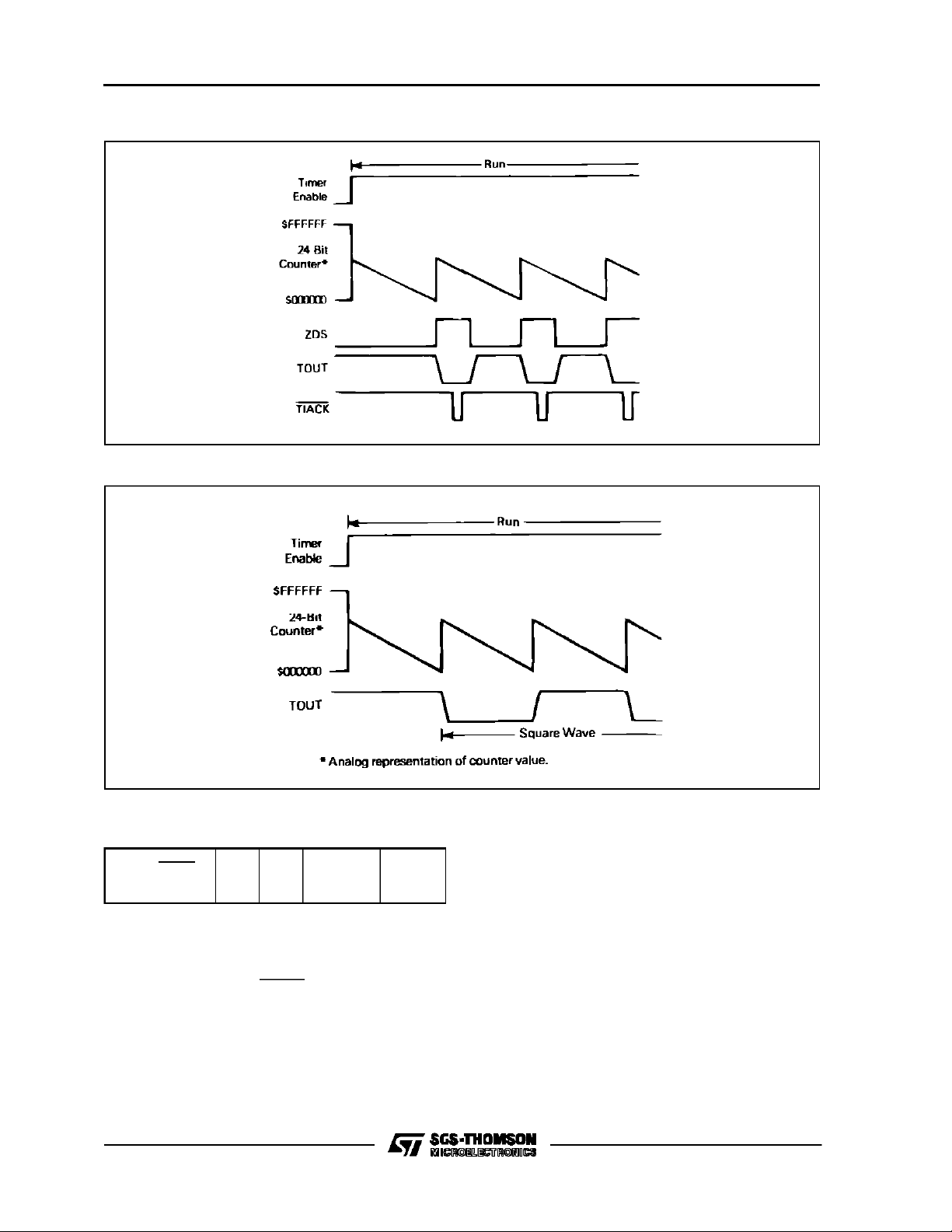

circuit. The PI/Ttimercontains a 24-bit widecounter

anda 5-bit prescaler. The timermay beclocked by

the system clock (PI/T CLK pin) or by an external

clock(TINpin), and a 5-bit prescaler canbe used.It

can generate periodic interrupts, a square wave, or

a singleinterrupt aftera programmed time period. It

can also be used for elapsed time measurement or

asa device watchdog.

PIN CO N NECTI O N S

January1989

1/61

TS68230

SECT IO N 1

INTR ODU CTI ON

TheTS68230parallel interface/timer(PI/T)provides

versatile double buffered parallel interfaces and a

system oriented timer for TS68000 systems. The

parallel interfaces operate in unidirectional or bidirectionalmodes, either 8 or 16 bits wide. In the unidirectional modes, an associated data direction

registerdetermines whether eachport pinisaninput

or output. Inthe bidirectional modes the data direction registers are ignoredand thedirectionis determined dynamically by the state of four handshake

pins.Theseprogrammable handshakepinsprovide

an interface flexible enough forconnection toa wide

varietyoflow,medium, orhighspeedperipherals or

other computer systems. The PI/T ports allow use

ofvectoredor autovectored interrupts,and alsoprovide a DMArequest pin for connection tothe 68440

directmemoryaccesscontroller(DMAC)or asimilar

circuit.The PI/T timercontains a24-bitwide counter

and a 5-bit prescaler. The timer maybe clockedby

the system clock (PI/T CLK pin) or by an external

clock (TIN pin), and a 5-bit prescaler can be used.

It can generate periodic interrupts, a square wave,

ora singleinterrupt aftera programmed timeperiod.

It can also be used for elapsed timemeasurement

or as a devicewatchdog.

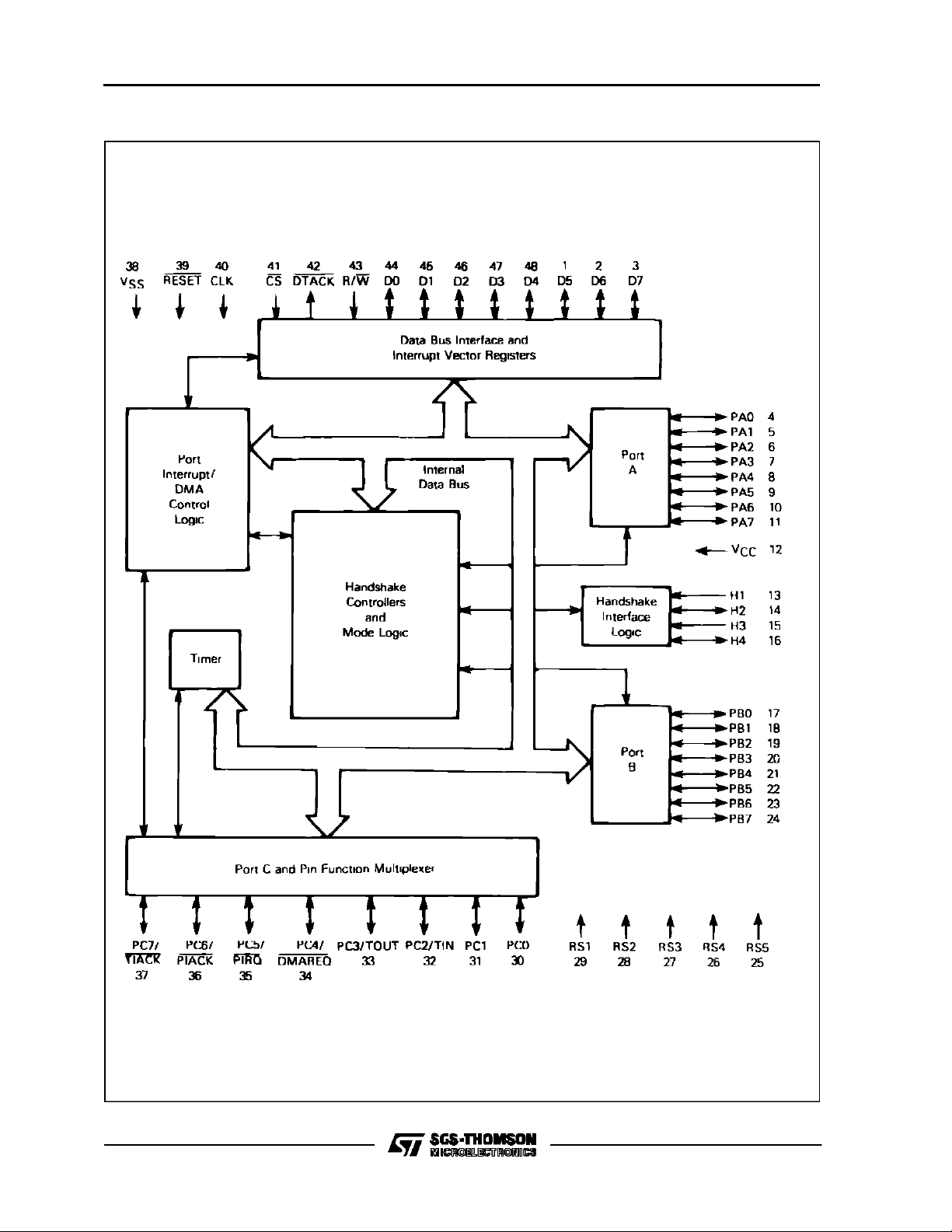

The PI/T consists of two logically independent sections : the ports and the timer. The port section

consistsofportA (PA0-PA7), port B(PB0-PB7), four

handshake pins (H1, H2,H3, and H4), twogeneral

input/output (I/O) pins, and six dual-function pins.

The dual-function pins can individually operate asa

thirdport (port C) or an alternate function relatedto

eitherport A, port B, or thetimer.The four programmable handshake pins, depending on the mode,

can control data transfer to and from the ports, or

can be used as interrupt generating inputs or I/O

pins. Refer to figure1.1.

The timer consists of a 24-bit counter, optionally

clocked by a 5-bit prescaler. Three pins provide

complete timer I/O : PC2/TIN, PC3/TOUT, and

PC7/TIACK. Only the ones needed for the given

configuration perform thetimerfunction,whilethe others remain port C I/O.

The system bus interface provides for asynchronoustransfer ofdata fromthe PI/T to a bus master

over the data bus (D0-D7). Data transfer acknowledge (DTACK), register selects (RS1-RS5), timer

interrupt acknowledge (TIACK), read/write line

(R/W), chip select (CS), or port interrupt acknowledge (PIACK) control data transfer between the

PI/T andan TS68000.

Features of the PI/T include :

.TS68000 Bus Compatible

.Port Modes Include:

Bit I/O

Unidirectional 8 Bit and 16 Bit

Bidirectional 8 Bit and 16 Bit

.Programmable Handshaking Options

.24-Bit Programmable Timer Modes

.Five Separate Interrupt Vectors

.Separate Port and Timer Interrupt Service

Requests

.Registersare Read/Write and Directly

Addressable

.Registersare Addressed for MOVEP(Move

Peripheral) and DMAC Compatibility

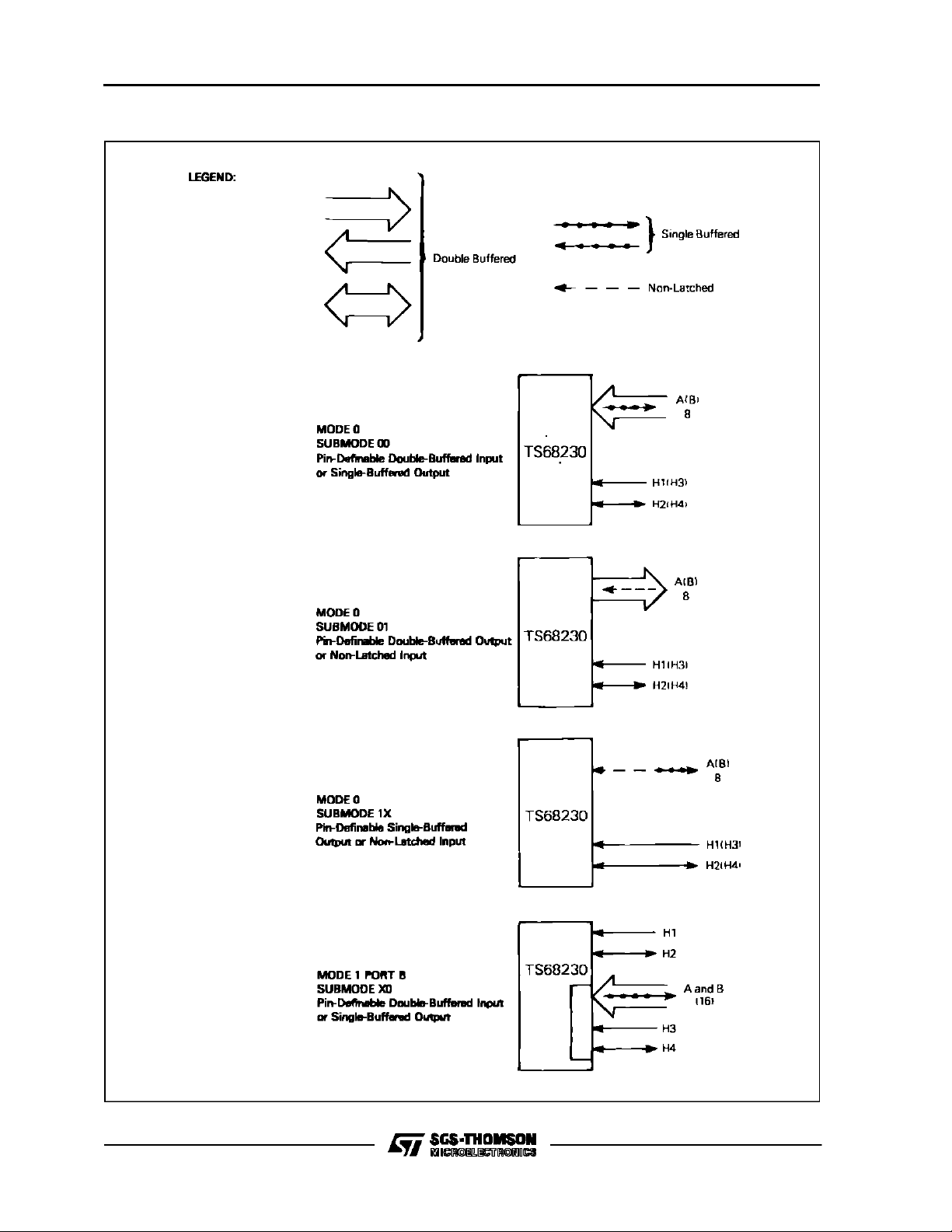

1.1.PORT MODEDESCRIPTION

The primary focus of most applications will be on

portA,port B,the handshake pins,theportinterrupt

pins, andthe DMArequest pin.They are controlled

inthefollowingway: theportgeneralcontrolregister

contains a 2-bit field that specifies one offour operationmodes.Thesegoverntheoverall operation of

the ports and determine their interrelation-ships.

Some modes require additional information from

eachport’s control register to further define its operation. In each port control register, there is a 2-bit

submode field that serves this purpose. Each port

mode/submode combination specifies a setof programmable characteristics that fully define the behavior of that port and two of the handshake pins.

This structure is summarized in table 1.1 and figure 1.2.

2/61

Figure 1.1 : Block Diagram.

TS68230

3/61

TS68230

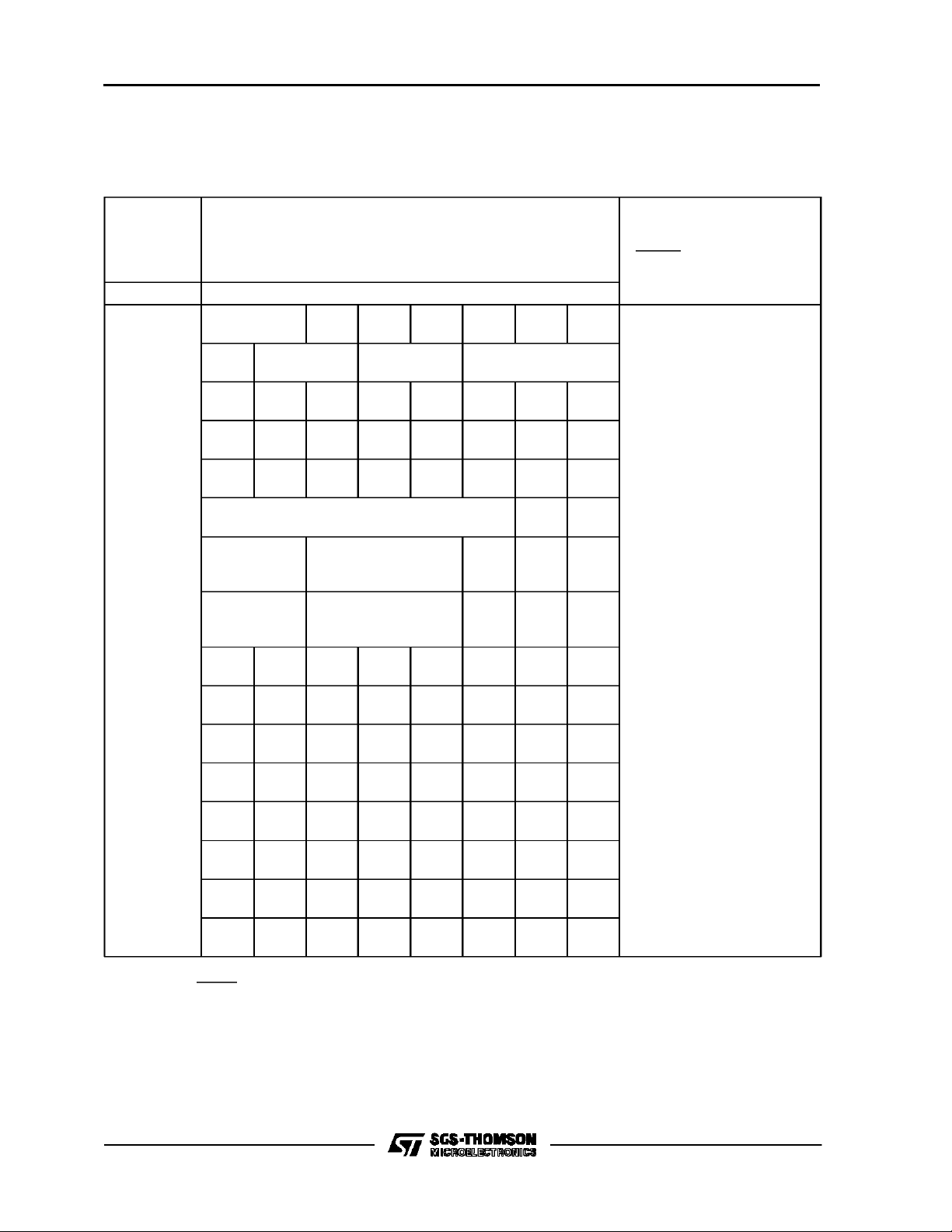

Table1.1 :PortMode ControlSummary.

Mode 0 (unidirectional 8-bit mode)

Port A

Submode 00 - Pin-definable Double-buffered Input or Single-buffered Output

H1 - Latches Input Data

H2 - Status/interrupt Generating Input, General-purpose Output, or Operation with H1 in the Interlocked or

Pulsed Handshake Protocols

Submode 01 - Pin-definable Double-buffered Output or Non-latched Input

H1 - Indicates Data Received by Peripheral

H2 - Status/interrupt Generating Input, General-purpose Output, or Operation with H1 in the Interlocked or

Pulsed Handshake Protocols

Submode 1X - Pin-definable Single-buffered Output or non-latched Input

H1 - Status/interrupt Generating Input

H2 - Status/interrupt Generating Input or General-purpose Output

Port B

H3 and H4 - Identical to Port A, H1 and H2

Mode 1 (unidirectional 16-bit mode)

Port A - Most-significant Data Byte or non-latched Input or Single-buffered Output

Submode XX - (not used)

H1 - Status/interrupt Generating Input

H2 - Status/interrupt Generating Input or General-purpose Output

Port B - Least-significant Data Byte

Submode X0 - Pin-definable Double-buffered Input or Single-buffered Output

H3 - Latches Input Data

H4 - Status/interrupt Generating Input, General-purpose Output, or Operation with H3 in the Interlocked or

pulsed handshake Protocols

Submode X1 - Pin-definable Double-buffered Output or Non-latched Input

H3 - Indicates Data Received by Peripheral

H4 - Status/interrupt Generating Input, General-purpose Output, or Operation with H3 in the Interlocked or

Pulsed Hanshake Protocols

Mode 2 (bidirectional 8-bit mode)

Port A - Bit I/O

Submode XX - (not used)

Port B - Double-buffered Bidirectional Data

Submode XX - (not used)

H1 - Indicates Output Data Received by the Peripheral and Controls Output Drivers

H2 - Operation with H1 in the Interlocked or Pulsed Output Handshake Protocols

H3 - Latches Input Data

H4 - Operation with H3 in the Interlocked or Pulsed Input Handshake Protocols

Mode 3 (bidirectional 16-bit mode)

Port A - Double-buffered Bidirectional Data (most-signifiant data byte)

Submode XX - (not used)

Port B - Double-buffered Bidirectional Data (least-signifiant data byte)

Submode XX - (not used)

H1 - Indicates Output Data Received by the Peripheral and Controls Output Drivers

H2 - Operation with H1 in the Interlocked or Pulsed Output Handshake Protocols

H3 - Latches Input Data

H4 - Operation with H3 in the Interlocked or Pulsed Input Handshake Protocols

4/61

Figure 1.2 : Port Mode Layout.

TS68230

5/61

TS68230

Figure 1.2 : Port Mode Layout (continued).

1.2. SIGNALDESCRIPTION

Throughout thisdatasheet, signalsarepresented u-

sing the terms active and inactive or asserted and

negated independent ofwhether thesignal isactive

in the high-voltage state or low-voltage state. (The

activestate of each logic pin is given below). Active

low signals are denoted by a superscript bar. R/W

indicates a writeisactivelow anda readactivehigh.

Table1.2 further describes each pin and the logical

pin assignments are given in figure1.3.

6/61

1.2.1. BIDIRECTIONAL DATA BUS (D0-D7). The

data buspinsD0-D7 forman 8-bitbidirectionaldata

busto/fromanTS68000busmaster.Thesepins are

activehigh.

1.2.2.REGISTERSELECTS(RS1-RS5). Theregister select pins, RS1-RS5, are active high highimpedance inputs that determine which of the 23

internal registers is beingselected. They are provided by theTS68000 bus master or other bus master.

Table 1.2 :Signal Summary.

TS68230

SignalName Input/Output ActiveState

CLK Input Falling and Rising

CS Input Low Level

D0-D7 Input/output High = 1, Low = 0 Level High, Low, High Impedance

DMAREQ Output Low High, Low

DTACK Output Low High, Low, High Impedance*

H1(H3)*** Input Low or High Asserted Edge

H2(H4)** Input or Output Low or High Asserted Edge High, Low, High Impedance

PA0-PA7**, PB0-PB7**,

PC0-PC7

PIACK Input Low Level

PIRQ Output Low Low, High Impedance*

RS1-RS5 Input High = 1, Low = 0 Level

R/W Input High Read, Low Write Level

RESET Input Low Level

TIACK Input Low Level

TIN (external clock) Input Rising Edge

TIN (run/halt) Input High Level

TOUT (square wave) Output Low High, Low

TOUT (TIRQ) Output Low Low, High Impedance*

Input/output,

Input or Output

High = 1, Low = 0 Level High, Low, High Impedance

Edge/Level

Sensitive

Edge

Output States

* Pullup resistors required.

** Note these pins have internal pullup resistors.

Figure 1.3 : Logical Pin Connection.

7/61

TS68230

1.2.3. READ/WRITE (R/W). R/W is a high impedanceread/writeinput signalfrom theTS68000 bus

master, indicating whetherthe current bus cycle is

a read (high) or write (low) cycle.

1.2.4.CHIPSELECT (CS).CS isa high-impedance

input that selects the PI/T registers for the current

bus cycle. Addressstrobe and the data strobe(upper or lower) of the bus master,along with the appropriate address bits, must be included in the

chip-select equation. A low level correspondsto an

assertedchip select.

1.2.5. DATA TRANSFER ACKNOWLEDGE

(DTACK). DTACK is an active low output that signals the completion of the bus cycle. During read

orinterrupt acknowledge cycles,DTACKisasserted

afterdatahasbeen provided onthedatabus;during

writecyclesitisasserted afterdata hasbeen accepted at the data bus. Data transfer acknowledge is

compatible with the TS68000 and with other

TS68000 busmasterssuchasthe 68440 directmemory accesscontroller (DMAC). A pullupresistor is

required to maintainDTACK high between bus cycles.

1.2.6. RESET (RESET). RESET is a high-impedance input used to initialize all PI/T functions. All

controland data direction registers are cleared and

mostinternal operations are disabled by the assertion of RESET (low).

1.2.7.CLOCK (CLK). The clock pinis a high-impedance TTL-compatible signal with the same specifications as the TS68000. The PI/T contains

dynamiclogicthroughout, andhencethisclockmust

not be gatedoff atany time. It is not necessary that

thisclockmaintain any particular phase relationship

with the TS68000 system clock. It may be connected to an independent frequency source (faster or

slower)as longas allbus specificationsare met.

1.2.8.PORT A AND PORT B (PA0-PA7 AND PB0PB7). Ports A and B are 8-bit ports that may be

concatenatedto forma 16-bit port in certain modes.

The ports may be controlled inconjunction with the

handshake pinsH1-H4. Forstabilization duringsystempower up,portsAand Bhave internal pullupresistorsto VCC. Allports pins are active high.

1.2.9. HANDSHAKE PINS (H1-H4). Handshake

pins H1-H4 are multi-purpose pins that (depending

on the operational mode) may provide an interlocked handshake, a pulsed handshake, an interrupt input(independent of data transfers), or simple

I/O pins. For stabilization during system power up,

H2andH4 haveinternal pullup resistors toVCC. The

sense of H1-H4 (active high or low) may be programmed in the port general control register bits

3-0.Independent ofthemode,the instantaneous levelof the handshake pinscan beread from theport

status register.

1.2.10. PORT C (PC0-PC7/ALTERNATE FUNCTION).This port can be used as eight general purposeI/O pins (PC0-PC7) or any combination of six

special function pins and two general purpose I/O

pins (PC0-PC1). Each dual-function pin can be a

standardI/Oor aspecialfunctionindependent ofthe

otherport C pins. Whenused as a port C pin, these

pins are active high. They may be individually programmed as inputs or outputs by the port Cdata direction register. The dual-function pins are defined

in the following paragraphs.

The alternatefunctionsTIN, TOUT, and TIACK are

timerI/Opins.TINmaybeusedasarising-edge triggered external clock input or an external run/halt

controlpin (thetimer isin the run stateif run/halt is

high and in the halt state if run/halt is low). TOUT

may provide an active low timer interrupt request

outputor a general-purpose square-wave output, initially high. TIACKis an activelow high-impedance

inputused for timer interrupt acknowledge.

Port A and B functions have an independent pairof

activelowinterrupt request (PIRQ)and interrupt acknowledge (PIACK) pins.

The DMAREQ (direct memory access request) pin

provides an active low direct memory access controller request pulse for three clock cycles,completelycompatiblewith the 68440 DMAC.

8/61

1.3. REGISTER MODEL

A registermodel that includes the corresponding register selectsis shown in table 1.3.

Table1.3 : Register Model.

Register

Register

SelectBits

5432176543210

0 0 0 0 0 Port Mode

Control

00001

00010 Bit7Bit

00011 Bit7Bit

00100 Bit7Bit

0 0 1 0 1 Interrupt Vector

0 0 1 1 0 Port A

0 0 1 1 1 Port B

01000 Bit7Bit

01001 Bit7Bit

01010 Bit7Bit

01011 Bit7Bit

01100 Bit7Bit

01101 H4

01110

V SVCRQ

Submode

Submode

LevelH3LevelH2LevelH1Level

VVVVVVVV 0 0 (null)

Select

6

6

6

6

6

6

6

6

H34

Enable

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

H12

EnableH4SenseH3SenseH2SenseH1Sense

IPF

Select

Bit

5

5

5

Number

5

5

5

5

5

4

Bit

4

Bit

4

H2 Control H2

H4 Control H4

Bit

4

Bit

4

Bit

4

Bit

4

Bit

4

Port Interrupt

Priority Control

Bit

3

Bit

3

Bit

3

Bit

Bit

Bit

Bit

2

2

2

1

Bit

1

Bit

1

Bit

0

Bit

0

Bit

0

VV 0 F Port Interrupt

H1

Int

SVCRQ

Enable

Enable

Bit

3

Bit

3

Bit

3

Bit

3

Bit

3

H4S H3S H2S H1S

Int

Bit

Bit

Bit

Bit

Bit

2

2

2

2

2

Enable

H3

SVCRQ

Enable

Bit

1

Bit

1

Bit

1

Bit

1

Bit

1

H1

Stat

Ctrl

H3

Stat

Ctrl

Bit

0

Bit

0

Bit

0

Bit

0

Bit

0

Value

after

RESET

(hex

value)

0 0 Port General

0 0 Port Service

0 0 Port A Data

0 0 Port B Data

0 0 Port C Data

0 0 Port A Control

0 0 Port B Control

VV Port A Data

VV Port B Data

VVV Port A Alternate

VVV Port B Alternate

VVVV Port C Data

VVVV Port Status

TS68230

Control Register

Request Register

Direction Register

Direction Register

Direction Register

Vector Register

Register

Register

Register

Register

Register

Register

Register

Register

01111

VVVVVVVV 0 0 (null)

* Unused, read as zero.

** Val ue before RESET.

*** C urrent value o n p ins.

9/61

TS68230

Table1.3 : Register Model (continued).

Register

SelectBits

5432176543210

1 0 0 0 0 TOUT/TIACK

Control

10001 Bit7Bit

6

10010

VVVVVVVV 0 0 (null)

Bit

ZD

Ctrl

Bit

5

4

V Clock

Control

Bit

3

Bit

2

Bit

Timer

Enable

Bit

1

0

Register

Value

after

RESET

(hex

value)

0 0 Timer Control

Register

0 F Timer Interrupt

Vector Register

10011 Bit23Bit

22

10100 Bit15Bit

14

10101 Bit7Bit

10110

10111 Bit23Bit

11000 Bit15Bit

11001 Bit7Bit

11010

11011

11100

11101

11110

VVVVVVVV 0 0 (null)

22

14

VVVVVVVZDS 0 0 Timer Status

VVVVVVVV 0 0 (null)

VVVVVVVV 0 0 (null)

VVVVVVVV 0 0 (null)

VVVVVVVV 0 0 (null)

Bit

21

Bit

13

Bit

6

6

5

Bit

21

Bit

13

Bit

5

Bit

20

Bit

12

Bit

Bit

20

Bit

12

Bit

Bit

19

Bit

11

Bit

4

4

3

Bit

19

Bit

11

Bit

3

Bit

18

Bit

10

Bit

Bit

18

Bit

10

Bit

Bit

17

Bit

9

Bit

2

2

1

Bit

17

Bit

9

Bit

1

Bit

16

Bit

Bit

Bit

16

Bit

Bit

VV Counter Preload

Register (high)

VV Counter Preload

8

Register (mid)

VV Counter Preload

0

Register (low)

VV Count Register

(high)

VV Count Register

8

(mid)

VV Count Register

0

(low)

Register

11111

VVVVVVVV 0 0 (null)

* Unused, read as zero.

10/61

TS68230

1.4. BUS INTERFACE OPERATION

The PI/Thas anasynchronous businterfaceprima-

rilydesigned for usewithan TS68000 microprocessor.With care,however, itcan beconnected tosynchronous microprocessor buses. This section

completelydescribes thePI/T’sbus interface,andis

intended for the asynchronous busdesigner unless

otherwise mentioned.

Inan asynchronous systemthePI/T clock mayoperate at a significantlydifferent frequency, either higherorlower,thanthebusmasterandothersystem

components, as long as all bus specifications are

met. TheTS68230 CLK pin hasthesame specificationsas the TS68000 CLK pin, andmust not begated off at any time.

The following signals generate normal read and

write cycles to the PI/T : CS (chip select), R/W

(read/write), RS1-RS5(five register select bits), D0D7 (the 8-bit bidirectional data bus), and DTACK

(data transfer acknowledge). To generate interrupt

acknowledge cycles, PC6/PIACK or PC7/TIACK is

usedinstead of CS, andthe register select pinsare

ignored. No combination of the following pin functionsmay be asserted simultaneously : CS, PIACK,

or TIACK.

1.4.1.READCYCLES. Thiscategory includesallregisterreads, except port or timer interrupt acknowledgecycles. WhenCS is asserted, theregister select and R/W inputs are latched internally. They

mustmeet smallsetup and hold timerequirements

with respect to the asserted edge of CS. (Refer to

6.6 AC Electrical Specifications for further information). The PI/T is not protected againstaborted

(shortened) bus cyclesgenerated byan address error or bus errorexception in which it is addressed.

Certain operations triggered by normal read (or

write)buscyclesarenot complete withinthe timeallotted to the bus cycle. One example is transfers

to/from the double-buffered latches that occur as a

result of the bus cycle. If the bus master’s clock is

significan-tly faster than the PI/T’s the possibility

exists that, following the bus cycle, CS can be negated then re-asserted before completion of these

internaloperations.InthissituationthePI/Tdoes not

recognize there-assertion of CSuntilthese operations are complete. Only at that time does it begin

theinternalsequencing necessaryto reacttotheasserted CS. Since CS also controls the DTACK response, this ”buscycle recovery time” can be related to the clock edge on which DTACK is asserted

for that cycle. The PI/T will recognize the subsequent assertionofCSthreeclockperiodsafterthe

clockedge on which DTACKwas previously asserted.

The register select andR/W inputspass through an

internal latchthat is transparent when the PI/T can

recognize a new CS pulse (see above paragraph).

Since the internal data bus of the PI/T is continuouslyengaged forreadtransfers, thereadaccess

time(tothe databus buffers)begins whentheregister selects are stabilized internally. Also, when the

PI/Tis ready tobegina newbus cycle,the assertion

of CS enables the data bus buffers within a short

propagation delay.Thisdoesnotcontribute tothe overall read access time unless CSis assertedsignificantlyafter the register select and R/W inputs are

stabilized (as may occur with synchronous bus

microprocessors).

Inaddition tothe chipselect’spreviously mentioned

duties, it controls the assertion of DTACK and latchingof read data at the data bus interface. Except

for controlling input latches and enabling the data

busbuffers,allofthesefunctionsoccuronlyafterCS

has been recognized internally and synchronized

withthe internal clock. Chip select isrecognized on

the falling edge of the clock if the setup time is met

; DTACK is asserted (low) on the next falling edge

of the clock. Read datais latched at the PI/T’s data

bus interface at the sametime DTACKis asserted.

It is stable as long as chip select remains asserted

independent of other external conditions.

Fromthe above discussion it isclear that if the chip

selectsetuptimeprior tothefallingedgeofthe clock

is met, the PI/T can consistently respond to a new

reador write bus cycleevery four clock cycles.This

factis especially usefulin designing the PI/T’sclock

in synchronous bus systems not using DTACK. (An

extra clock period is required in interrupt acknowledge cycles, see 1.4.2 Interrupt Acknowledge

Cycles).

In asynchronous bus systems in which the PI/T’s

clock differs from that of the bus master, generally

thereisno waytoguarantee thatthechip select setup time with respect to the PI/T clock is met. Thus,

the only way to determine that the PI/T recognized

the assertion of CS is to wait for the assertion of

DTACK.In thissituation,alllatchedbusinputstothe

PI/T must be held stable until DTACK is asserted.

These include register select, R/W, and write data

inputs (see below).

System specifications impose a maximum delay

fromthe trailing(negated) edgeofCS tothenegated

edgeofDTACK. Assystemspeedsincreasethisbecomesmoredifficult to meetwith asimplepullup resistor tied to the DTACK line. Therefore, the PI/T

provides an internal active pullup deviceto reduce

the rise time, and a level-sensitive circuit that later

turns this device off. DTACK is negated asynchronouslyas fast as possiblefollowing the rising edge

11/61

TS68230

of chip select, then three-stated to avoid interferencewith the nextbus cycle.

The systemdesignermust takecare thatDTACK is

negated andthree-statedquicklyenough aftereach

bus cycle to avoid interference with the next one.

With an TS68000this necessitates a relatively fast

external path from the data strobe negation to CS

bus master negation.

1.4.2. INTERRUPT ACKNOWLEDGE CYCLES.

Special internal operations take placeon PI/T interrupt acknowledge cycles. The port interrupt vector

register or the timer vector register are implicitly addressed by the assertion of PC6/PIACK or

PC7/TIACK, respectively. The signals are first synchronized with the falling edge of the clock. One

clockperiod after they arerecognized, thedata bus

buffers areenabled andthe vectorisdrivenontothe

bus. DTACK is assertedafter another clock period

toallowthe vector somesetuptimeprior toDTACK.

DTACK is negated, then three-stated, as with normal read or write cycles,when PIACK or TIACK is

negated.

1.4.3.WRITE CYCLES. In manyways, writecycles

are similar to normal read cycles. On write cycles,

data at the D0-D7 pins must meet the same setup

specificationsas the register select and R/W lines.

Like these signals, write data is latched on the asserted edgeof CS,and must meet small setup and

hold time requirements with respect to that edge.

The samebus cyclerecovery conditions existas for

normal read cycles.No other differences exist.

12/61

SECT IO N 2

TS68230

PORT GENERAL INFORM AT ION AND

CONVENTI O NS

This sectionintroduces concepts that are generally

applicable to the PI/Tports independent ofthe chosen mode and submode. For this reason, no particular port or handshake pins are mentioned ; the

notation H1(H3) indicates that, depending on the

chosen mode and submode, the statement given

may be true for either the H1or H3 handshake pin.

2.1. UNIDIRECTIONALVS BIDIRECTIONAL

Figure 1.2showsthe configuration of portsA and B

and each of the handshake pinsin each port mode

andsubmode.In modes0and 1,adatadirectionregisteris associatedwith eachoftheports. These registerscontainonebitfor eachport pinto determine

whether that pin is an input or an output. Modes 0

and 1 are, thus, called unidirectional modes becauseeach pinassumes aconstantdirection, changeableonly by a resetcondition or a programming

change. These modes allow double-buffered data

transfersinonedirection. Thisdirection, determined

by the mode and submode definition, is known as

the primary direction. Data transfers in the primary

directionare controlledbythehandshake pins. Data

transfers not in the primary direction are generally

unrelated, andsingleorunbuffered datapathsexist.

In modes 2 and3 thereis no concept of primary direction as in modes 0 and 1. Except for port A in

mode2 (bit I/O),thedatadirectionregisters haveno

effect. These modesare bidirectional, in thatthe directionof each transfer(always 8 or 16 bits,double

buffered) is determined dynamically by the state of

thehandshakepins.Thus,forexample, datamaybe

transferred out of the ports, followed very shortlyby

a transfer into the same port pins. Transfers to and

from the ports are independent and may occur in

any sequence. Since the instantaneous direction is

always determined by the external system, a small

amount of arbitration logic may be required.

2.1.1.CONTROL OF DOUBLE-BUFFERED DATA

PORTS. Generally speaking, the PI/T is a doublebuffereddevice.Intheprimarydirection, doublebuffering allows orderly transfers by using the handshakepinsin anyofseveral programmable protocols.

(When bit I/O is used, double buffering is not available and the handshake pins are used as outputs

or status/interrupt inputs).

Use of double buffering is most beneficial in situations where a peripheral device and the computer

system are capable of transferring data at roughly

the samespeed. Double bufferingallows the fetch

operation of the data transmitter to be overlapped

with the store operation of the data receiver. Thus,

throughput measured inbytesor words-per-second

may be greatly enhanced. If there is a large mismatch in transfer capability between the computer

and the peripheral, little or no benefit isobtained. In

these cases there isno penalty in using double buffering.

2.1.2. DOUBLE-BUFFERED INPUTTRANSFERS.

Inall modes, thePI/Tsupports double-buffered input

transfers. Data that meets the port setupand hold

times is latched on the asserted edge of H1(H3).

H1(H3) isedgesensitive, and mayassumeanyduty

cycleaslongasbothhighandlowminimumtimesare

observed. The PI/T contains a port status register

whose H1S(H3S) statusbit is set anytime any input

datathathasnot beenread bythe busmasterispresent in the double-buffered latches. The action of

H2(H4) is programmable ; it may indicate whether

thereis room for more data in the PI/T latches or it

mayserveotherpurposes. Thefollowingoptions are

available, depending on the mode.

1. H2(H4) may be anedge-sensitive input that is

independent ofH1(H3)andthe transferof port

data. On the asserted edge of H2(H4), the

H2S(H4S) status bit is set. It is clearedby the

direct method (refer to 2.3 Direct Method of

Resetting Status), the RESET pin being asserted,or when the H12 enable (H34 enable)

bit of the portgeneral control register is zero.

2. H2(H4) may be a general purpose output pin

that is always negated. The H2S(H4S) status

bit is always zero.

3. H2(H4) may be a general purpose output pin

thatis always asserted. The H2S(H4S)status

bit is always zero.

4. H2(H4)maybe an output pinin theinterlocked

input handshake protocol. It is asserted when

the port input latches are ready to accept new

data.Itisnegated asynchronously followingthe

asserted edge of theH1(H3)input. As soonas

the input latches become ready, H2(H4) is again asserted. When both double-buffered

latches are full, H2(H4) remains negated until

dataisremovedbyareadofportA(portB)data

register.Thus,anytimetheH2(H4)output isasserted, new input data may be entered by asserting H1(H3). At other times transitions of

H1(H3) areignored. TheH2S(H4S)statusbitis

alwayszero.WhenH12enable(H34 enable) is

zero,H2(H4) is heldnegated.

13/61

TS68230

5. H2(H4) maybe anoutput pin in thepulsed input handshake protocol. It is asserted exactly

as in the interlocked input protocol, but never

remains asserted longer than four clock cycles. Typically, a four clock cycle pulse is generated. But in the case that a subsequent

H1(H3)asserted edge occursbefore terminationof the pulse, H2(H4)is negated asynchronously.Thus,anytimeaftertheleading edgeof

the H2(H4) pulse, new data maybe entered in

the PI/T double-buffered input latches. The

H2S(H4S)statusbit isalwayszero. WhenH12

enable(H34enable) iszero,H2(H4)isheldnegated.

2.1.3. DOUBLE-BUFFERED OUTPUT TRANSFERS. The PI/T supports double-buffered output

transfers inall modes. Data, written bythebus mastertothePI/T,isstoredin theport’soutputlatch.The

peripheral accepts the data by asserting H1(H3),

whichcausesthe nextdatatobemovedto theport’s

output latch as soon as it is available. The function

ofH2(H4)isprogrammable ;it mayindicatewhether

data has been moved to the output latch or it may

serveotherpurposes.TheH1S(H3S)statusbitmay

be programmed for two interpretations. First, the

status bit is a one when there is atleast one latchin

the double-buffered data path that can accept new

data.Afterwritingone byte/wordofdatatotheports,

aninterruptserviceroutinecouldcheckthisbittodetermineifitcouldstoreanother byte/word, thus filling

both latches. Second, whenthe bus master is finished, itis oftenuseful to be ableto checkwhetherall

of the data has been transferred to the peripheral.

The H1S(H3S) status bit is set when both output

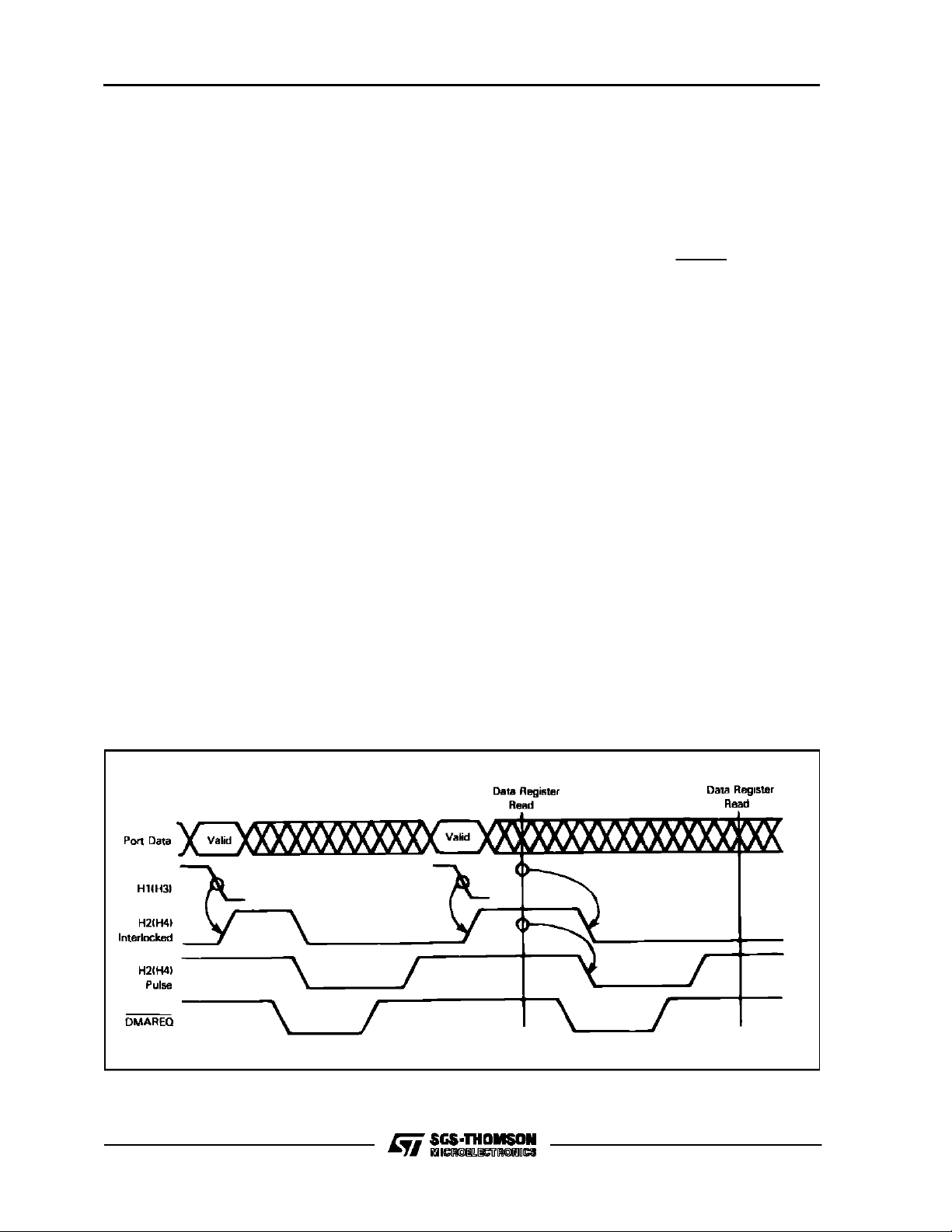

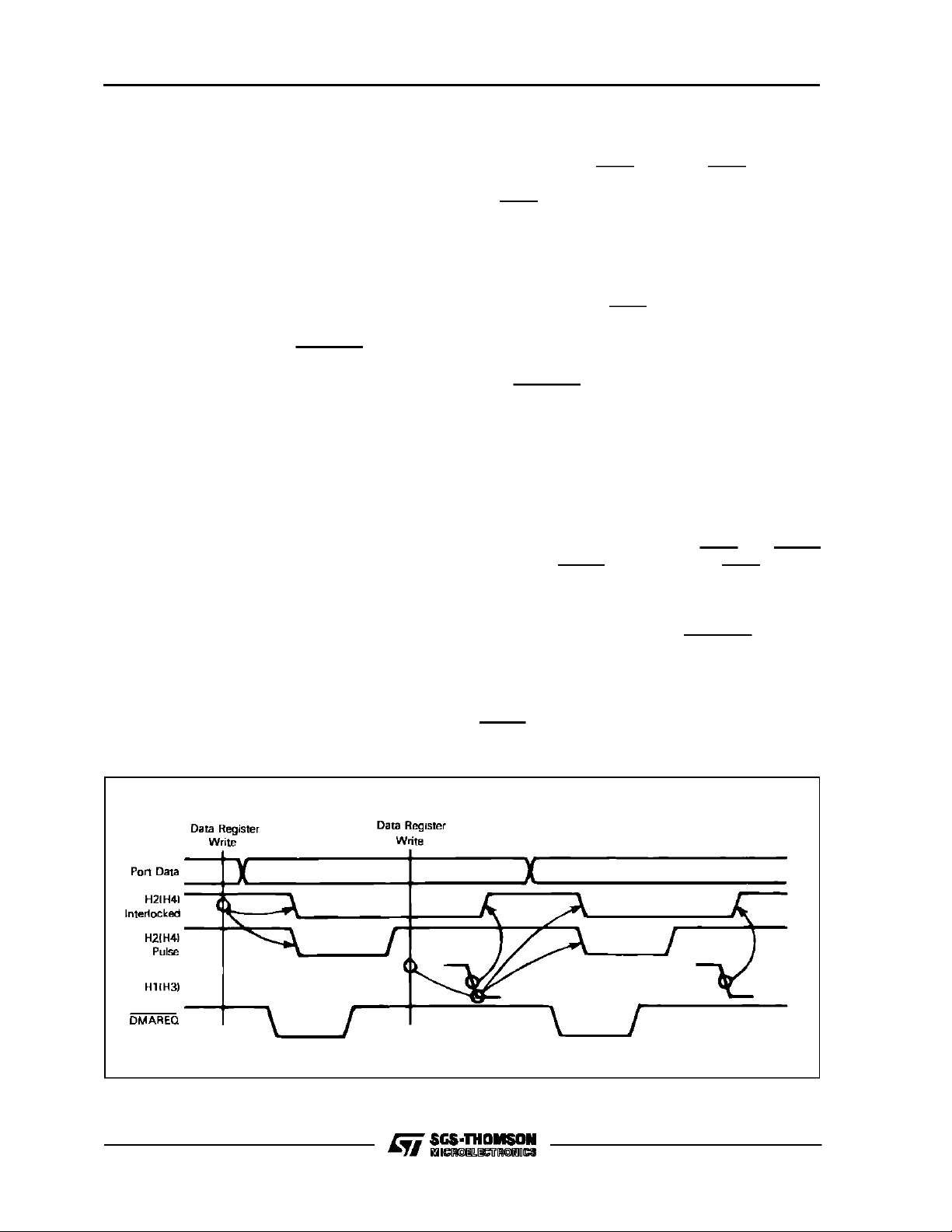

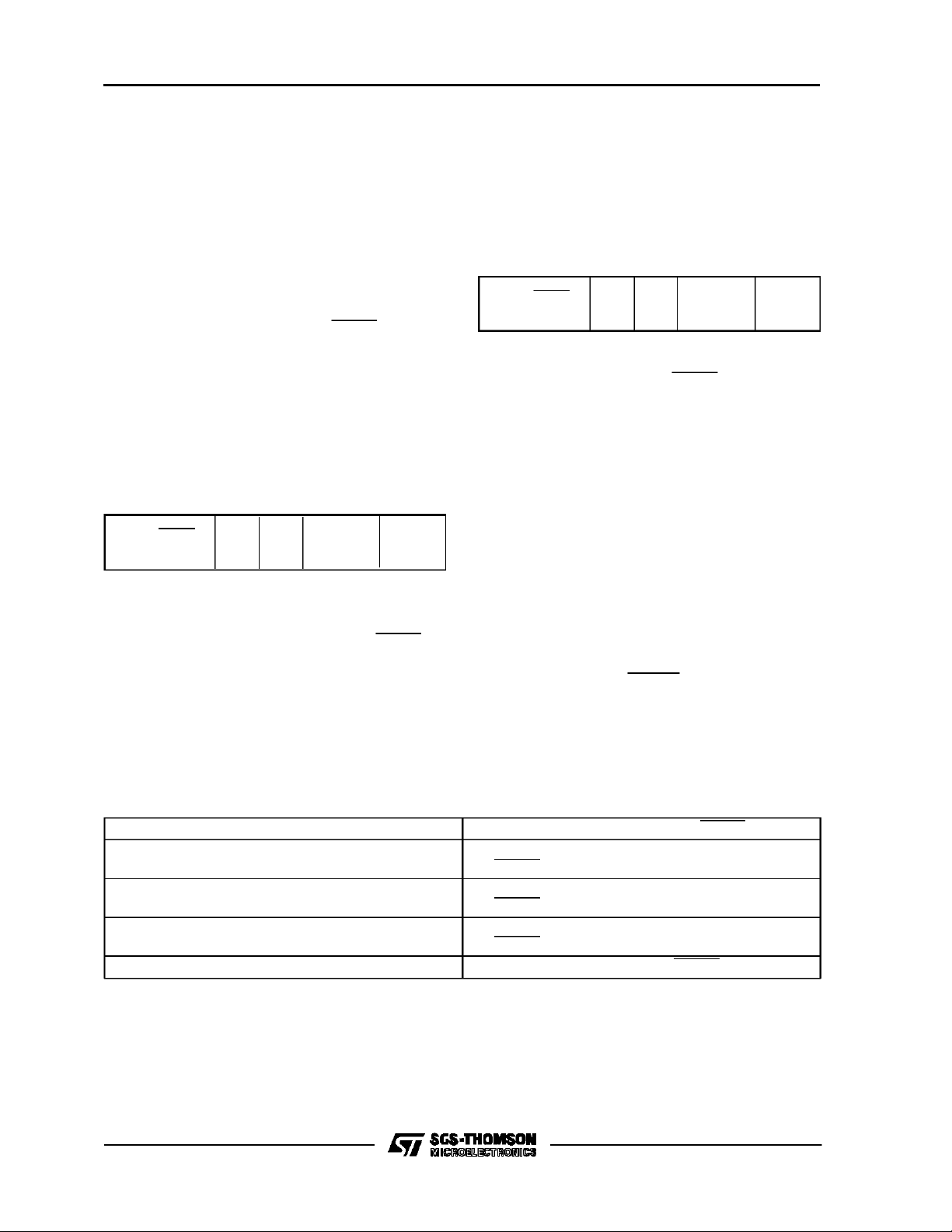

Figure 2.1 : Double-Buffered Input Transfers Timing Diagram.

latchesareempty.The programmableoptionsofthe

H2(H4) pin are given below, depending on the

mode.

1. H2(H4) may bean edge-sensitive input pinin-

2. H2(H4) may be a general-purpose output pin

3. H2(H4) may be a general-purpose output pin

4. H2(H4)maybe anoutputpinintheinterlocked

dependent of H1(H3) and the transfer of port

data. On the asserted edge of H2(H4), the

H2S(H4S) status bit is set. It is clearedby the

direct method (refer to 2.3 Direct Method of

Resetting Status), the RESET pin being asserted,or when the H12 enable (H34 enable)

bit of the portgeneral control register is zero.

thatis alwayszero.

that is always asserted.The H2S(H4s)status

bit is always zero.

output handshake protocol. H2(H4) is assertedtwo clockcyclesafterdata istransferred to

the double-buffered output latches. The data

remains stable and H2(H4) remains asserted

until the next asserted edge of the H1(H3) input.Atthattime,H2(H4) isasynchronously negated.As soonas the next datais available, it

is transferred tothe output latches andH2(H4)

is asserted. When H2(H4) is negated, assertedtransitionson H1(H3)have noeffect onthe

data paths. As is explained later, however, in

modes2 and 3 H1does controlthethree-state

output buffers of the bidirectional port(s). The

H2S(H4S)statusbitisalwayszero.WhenH12

enable(H34enable)is zero,H2(H4) isheldnegated.

14/61

TS68230

5. H2(H4)maybe anoutput pininthe pulsed output handshake protocol. It is asserted exactly

asintheinterlocked outputprotocol above,but

neverremains asserted longer than fourclock

cycles.Typically, a four clockpulse is generated.But in the case that a subsequent H1(H3)

assertededge occursbeforeterminationof the

pulse, H2(H4) is negated asynchronously,

thus shortening the pulse. The H2S(H4S) status bit is alwayszero. When H12 enable (H34

enable) is zero, H2(H4) is held negated.

A sampletiming diagram isshownin figure2.2.The

H2(H4) interlocked and pulsed output handshake

protocols are shown. The DMAREQ pin is also

shown assuming it is enabled. All handshake pin

sense bits are assumed to be zero ; thus,the pins

arein the lowstate whenasserted.Due to thegreat

similaritybetweenmodes, thistimingdiagram isapplicable to all double-buffered output transfers.

2.2. REQUESTING BUS MASTER SERVICE

The PI/Thas severalmeans of indicating a need for

service by a bus master. First, the processor may

poll the port status register. It contains a status bit

for each handshake pin, plus a level bit that always

reflects the instantaneous state of that handshake

pin.Astatusbit isonewhenthePI/Tneedsservicing

(i.e., generally when the bus masterneeds to read

or write data to the ports)or whena handshake pin

used as a simple status input has been asserted.

The interpretation of these bitsis dependent on the

chosen modeand submode.

Second, the PI/T may be placedin the processor’s

interrupt structure. As mentioned previously, the

PI/T contains port A and B control registers that

configure thehandshakepins.Otherbitsintheseregisters enable an interrupt associated with each

handshake pin. This interrupt is made available

through the PC5/PIRQ pin, if the PIRQ function is

selected. Three additional conditions are required

for PIRQto be asserted : 1) the handshake pin status bitis set, 2) the corresponding interrupt (service

request) enable bit is set,and 3) DMA requests are

not associated with that data transfer (H1 and H3

only). The conditions from each of the four handshake status bits and corresponding status bits are

ORedto determine PIRQ.Toclearthe interrupt, the

proper status bit must be cleared (see 2.3. Direct

Methodof Resetting Status).

The third method of requesting service is via the

PC4/DMAREQ pin. This pin canbe associatedwith

double-buffered transfersin eachmode. If itis used

as a DMA controller request, it can initiate requests

to keep the PI/T’s input/output double-buffering

empty/fullasmuchaspossible.Itwillnot overrunthe

DMA controller. The pin is compatible with the

68440direct memory access controller(DMAC).

2.2.1. VECTORED, PRIORITIZED PORT INTERRUPTS.Use ofTS68000compatible vectoredinterrupts with the PI/T requires the PIRQ and PIACK

pins.When PIACKis asserted while PIRQ is asserted,the PI/T places an 8-bit vector on the datapins

D0-D7.Under normalconditions, this vector correspondsto the highest priority enabled active port interrupt source with which the DMAREQ pin is not

currently associated. The most-significant six bits

are provided by the port interrupt vector register

(PIVR), with the lower two bits supplied by prioritization logic according to conditions present when

PIACKis asserted.It isimportant tonotethattheon-

Figure 2.2 : Double-Buffered OutputTransfers TimingDiagram.

15/61

TS68230

ly effect on the PI/T caused by interrupt acknowledgecycles is that the vectoris placed on the data

bus. Specifically, no registers, data,status, or other

internal states of the PI/T are affectedby the cycle.

Several conditions may bepresentwhenthe PIACK

inputis assertedto thePI/T. These conditionsaffect

the PI/T’sresponse and the termination of the bus

cycle.If thePI/T has no interrupt function selected,

or is not asserting PIRQ, the PI/Twill make no responsetoPIACK(DTACKwillnot beasserted). Ifthe

PI/Tis asserting PIRQwhen PIACKis received, the

PI/Twilloutputthecontentsoftheport interrupt vectorregisterandthe prioritization bits.Ifthe PIVRhas

not been initialized, $0F will be read fromthis register.These conditions are summarized in table 2.1.

The vector table entries for the PI/T appear as a

contiguous block of four vector numbers whose

commonuppersixbitsare programmed inthePIVR.

The following table pairs each interrupt sourcewith

the 2-bit value provided by the prioritization logic

when interrupt acknowledge is asserted (see 4.2.

Port Service Request Register (PSRR)).

H1 source - 00 H2 source - 01

H3 source - 10 H4 source - 11

2.2.2. AUTOVECTORED PORT INTERRUPTS.

Autovectored interrupts use only thePIRQ pin. The

operation of thePI/Twithvectoredand autovectored

interruptsis identical exceptthatnovectors aresuppliedand thePC6/PIACK pincan beused as a port

C pin.

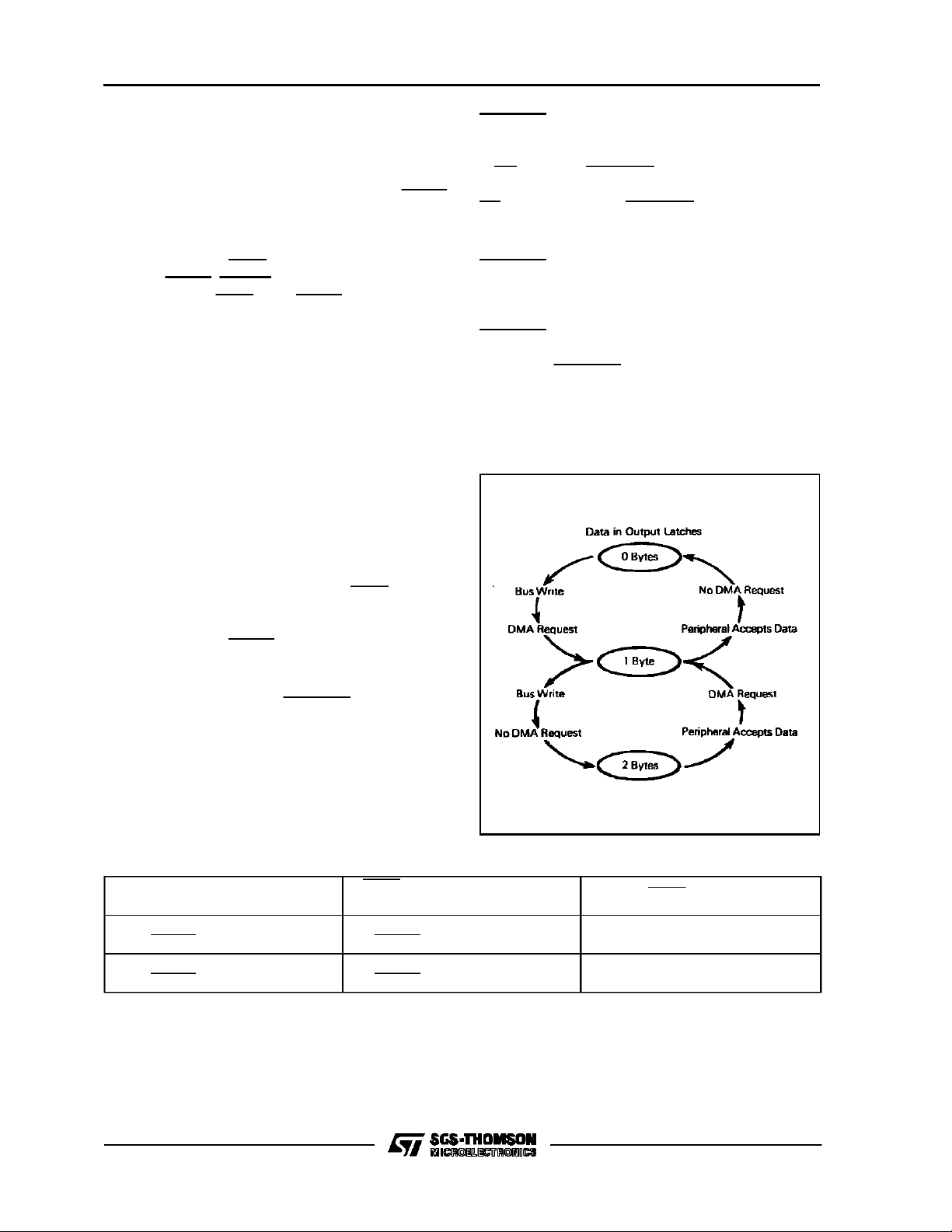

2.2.3. DMA REQUEST OPERATION. The direct

memory access request (DMAREQ) pulse (when

enabled) isassociated withoutput or input transfers

tokeepthe initialand finaloutput latchesfullorinitial

and final input latches empty, respectively. Figures

2.3and 2.4showallthepossible pathsin generating

DMArequests. See4.2. Port ServiceRequest Re-

gister(PSRR)for programming the operationof the

DMA request bit.

DMAREQ is generated on the bus side of the

TS68230 by the synchronized* chip select. If the

conditionsof figures2.3or 2.4aremet, anassertion

ofCS willcauseDMAREQ tobeassertedthreePI/T

clocks(plusthedelay timefromthe clockedge)after

CS is synchronized. DMAREQ remains asserted

threeclockcycles(plusthedelaytimefromtheclock

edge) andis then negated.

DMAREQ pulses are associated with peripheral

transfers or are generated by the synchronized*

H1(H3) input. If the conditions of figures2.3 or 2.4

aremet, an assertion of theH1(H3) input will cause

DMAREQ to be asserted 2.5PI/T clock cycles(plus

the delaytime fromclockedge) afterH1(H3)is synchronized. DMAREQ remains asserted threeclock

cycles(plus thedelaytimefrom the clockedge)and

is then negated.

Figure 2.3: DMAREQAssociated withOutput

Transfers.

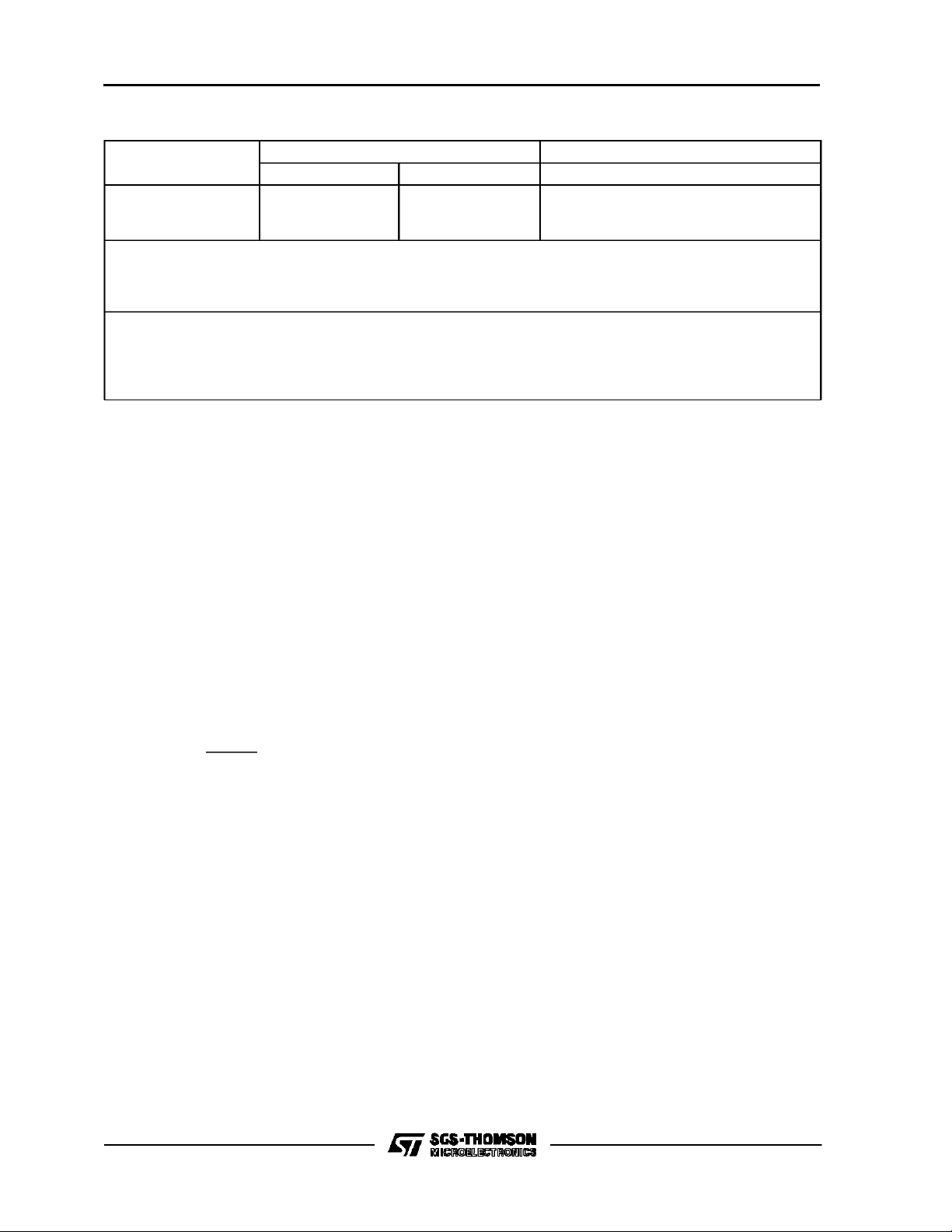

Table 2.1 : Responseto Port InterruptAcknowledge.

Conditions

PIVR has not been initialized

since RESET.

PIVR has been initialized

since RESET.

PIR Q N egated OR Interrupt

Request Function not Selected

No Response from PI/T.

No DTACK.

No Response from PI/T.

No DTACK.

PIR Q Asserted

PI/T provides $0F, the Uninitialized

Vector*.

PI/T provides PIVR contents with

prioritization bits.

* The uninitialized vector is the value returned from an interrupt vector register before it has been initialized.

* Synchronized means that the appropriate input signal (H1, H3, or CS) has been sampled by the PI/T on the appropriatre

edge of the

clock (rising edge for H1(H3) and falling edge for CS). Refer to 1.4 BUS INTERFACE OPERATION for the exception concer-

16/61

TS68230

Figure 2.4 : DMAREQ Associated with Input

Transfers.

V000313

2.3. DIRECT METHODOF RESETTING STATUS

In certain modes one or more handshake pins can

be used as edge-sensitive inputs for the sole purposeof settingbits intheport statusregister. These

bitsconsistof simpleflip-flops.Theyareset (toone)

by the occurrence of the asserted edge of the

handshake pin input.Resetting ahandshake status

bit can be done by writingan 8-bitmask to the port

statusregister.Thisiscalledthedirect methodofresetting.To reseta statusbit that is resettable by the

direct method, the mask must contain a onein the

bitposition of theportstatus register corresponding

to the desired status bit. For statusbits that are not

resettableby thedirectmethodin thechosen mode,

the datawrittento the portstatus register hasno effect. For status bitsthat are resettable by thedirect

methodinthe chosen mode, a zeroin themaskhas

no effect.

2.4. HANDSHAKE PIN SENSECONTROL

The PI/Tcontains exclusive-OR gates tocontrol the

sense of eachof the handshakepins,whetherused

as inputs or outputs. Four bits in the port general

control register may be programmed to determine

whether the pins are asserted in the low- or highvoltage state.As with other controlregisters, these

bits arereset tozero whenthe RESET pin is asserted, defaulting the asserted level to be low.

2.5. ENABLING PORTS A ANDB

Certain functions involved with double-buffered da-

ta transfers, thehandshake pins, andthe statusbits

may be disabled by the external system or by the

programmer during initialization. The port general

control register contains two bits, H12 enable and

H34 enable, which control these functions. These

bits are cleared to the zero state when the RESET

pin isasserted, and the functions are disabled. The

functionsare the following :

1.Independent of other actions by the bus master or peripheral (viathe handshake pins), the

PI/T’s disabledhandshakecontroller is held to

the ”empty”state; i.e.,no dataispresent inthe

double-buffered data path.

2.When any handshake pinis used toset a simple status flip-flop, unrelated to double-buffered transfers, theseflip-flops are heldreset to

zero (seetable 1.1).

3.When H2(H4) is used in an interlocked or pulsed handshake with H1(H3), H2(H4) is held

negated,regardless ofthe chosenmode,submode,and primary direction. Thus,fordoublebuffered input transfers,the programmer may

signal a peripheral when the PI/T is ready to

begin transfers by setting the associated

handshake enable bit to one.

2.6. PORT A ANDB ALTERNATE REGISTERS

Inaddition totheportAandBdataregisters, thePI/T

contains port A and B alternate registers. These registersarereadonly,andsimplyprovide the ins-tantaneous (non-latched) level of each port pin. They

have no effect on the operation of the hand-shake

pins,double-buffered transfers,statusbits,or anyother aspect ofthePI/T,andtheyaremode/submode

independent. Refer to 4.7. Port Alternate Regis-

ters for further information.

17/61

TS68230

SECT IO N 3

PORT MODES

This sectioncontains information that distinguishes

the various port modes and submodes. General

characteristics common to allmodes are definedin

Section 2Port GeneralInformationand Conventions. A description of the port A control register

(PACR) and port Bcontrol register (PBCR)is given

beforeeach modedescription. Aftereach submode

description,the programmable options arelistedfor

that submode.

3.1. PORT A CONTROLREGISTER (PACR)

7 6543 2 1 0

Port A

Submode

H2 Control

H2

Interrupt

Enable

H1

SVCRQ

Enable

H1

Status

Control

The port A control register, in conjunction with the

programmed mode and the port B submode,

controls the operation of port A and the handshake

pinsH1and H2. TheportA control register contains

fivefields : bits7 and 6 specifythe port Asubmode;

bits5, 4, and3controlthe operation oftheH2 handshake pin and the H2S status bit ; bit 2 determines

whetheraninterrupt willbegenerated whentheH2S

statusbitgoes toone ; andbit1 determines whether

aservicerequest (interrupt requestorDMArequest)

willoccur;bit0controls theoperationof theH1Sstatus bit. The PACR is always readable andwritable.

All bits are cleared to zero when the RESET pin is

asserted.When theport Asubmodefieldisrelevant

ina mode/submode definition,it must notbealtered

unless the H12enable bitin theportgeneral control

register is clear (seetable 1.3 located at theend of

this document). Altering these bits will give unpredictable results.

3.2. PORT B CONTROLREGISTER (PBCR)

7 6543 2 1 0

Port B

Submode

H4 Control

H4

Interrupt

Enable

H3

SVCRQ

Enable

H3

Status

Control

Theport Bcontrolregister specifies theoperation of

port Band the handshakepins H3and H4. Theport

B control register contains five fields : bits 7 and 6

specifythe portB submode ; bits5, 4,and 3 control

theoperation ofthe H4handshake pin and H4Sstatus bit; bit 2 determines whetheran interrupt willbe

generated when the H4S status bit goes to a one ;

bit1determines whethera servicerequest (interrupt

request or DMA request) will occur ; and bit 0

controls the operation of the H3S status bit. The

PBCRis alwaysreadable and writable. There isnever a consequence to reading the register.

All bits are cleared to zero when the RESET pin is

asserted. WhentheportB submodefieldisrelevant

ina mode/submode definition, itmustnot bealtered

unlessthe H34enable bit in theport general control

register is clear (see table 1.3 located at the end of

thisdocument).

3.3.MODE 0 - UNIDIRECTIONAL 8-BIT MODE

In mode 0, ports A and B operate independently.

Eachmay beconfigured inany of its three possible

submodes :

Submode 00-Pin-Definable Double-Buffered Input orSingle-Buffered Output

Submode 01 - Pin-Definable Double-Buffered

Output orNon-Latched Input

Submode 1X- Bit I/O(Pin-Definable Single-Buffered Output or Non-Latched Input)

Handshake pinsH1and H2 areassociatedwithport

A andconfigured by programming theportA control

register. (The H12 enable bit of the port general

control register enables port A transfers). Handshake pins H3 and H4 are associated with port B

and configured by programming the port B control

register. (The H34 enable bit of the port general

control register enables port B transfers).The port

A and B data direction registers operate in all three

submodes. Alongwith the submode, theyaffect the

data read andwrite at the associated data register

according to table3.1. They also enable the output

buffer associated with each portpin. TheDMAREQ

pin may be associated with either (not both) port A

orportB,butdoesnotfunctionifthebitI/Osubmode

(submode 1X) is programmed for the chosen port.

18/61

Table 3.1 : Mode 0 Port Data Paths.

TS68230

Mode

0 Submode 00

0 Submode 01

0 Submode 1X

Abbreviations :

IOL - Initial Output Latch

FOL - Final Output Latch

FIL - Final Input Latch

Note 1 : Data is latched in the output data registers (final output latch) and will be single buffered at the pin if

the DDR is 1. The output buffers will be turned off if the DDR is 0.

Note 2 : Data is latched in the double-buffered output data registers. The data in the final output latch will

appear on the port pin if the DDR is a 1.

Note 3 : The output drivers that connect the final output latch to the pins are turned on

3.3.1.SUBMODE 00 - PIN-DEFINABLE DOUBLE-

BUFFERED INPUT OR SINGLE-BUFFERED

OUTPUT. In mode 0, double-buffered input transfersof up toeightbits areavailable by programming

submode 00 in the desired port’s control register.

Datathat meets theport setupand holdtimesis latchedon the asserted edge of H1(H3)and isplaced

in the initial or finalinput latch. H1(H3)is edge sensitive and may assume any duty cycle as long as

bothhighandlowminimumtimesareobserved. The

PI/Tcontainsa portstatusregisterwhoseH1S(H3S)

status bit is set anytime anyinput data thathas not

been read by thebus masteris present in the double-buffered latches. The action of H2(H4) is programmable. The following options are available :

1. H2(H4) maybe an edge-sensitive status input

thatis independent of H1(H3) and the transfer

of port data. On the assertededge of H2(H4),

the H2S(H4S) status bit isset. It is cleared by

eithertheRESETpin being asserted,writinga

oneto theparticular statusbit inthe portstatus

register (PSR), or when the H12enable (H34

enable) bit of the port general register is clear.

2. H2(H4) may be a general-purpose output pin

that is always negated. In this case the

H2S(H4S) status bit is always clear.

3. H2(H4) may be a general-purpose output pin

that is always asserted. In this case the

H2S(H4S) status bit is always clear.

4. H2(H4)maybe anoutput pinin theinterlocked

inputhandshake protocol. It is assertedwhen

the port input latches are ready to acceptnew

data. It is negated asynchronously following

Read P ort A/B Data Register Write Port A/B Data Register

DDR = 0 DDR = 1 DDR = X

FIL, D. B.

Pin

Pin

FOL Note 3

FOL Note 3

FOL Note 3

S. B. - Single Buffered

D. B. - Double Buffered

DDR - Data Direction Register

FOL, S. B.

IOL/FOL, D. B.

FOL, S. B.

Note 1

Note 2

Note 1

as the input latches become ready, H2(H4) is

again asserted. When the inputdouble-buffered latches are full, H2(H4) remains negated

until data is removed. Thus, anytime the

H2(H4) outputisasserted, new inputdatamay

be entered by asserting H1(H3). At other

times, transitions on H1(H3) are ignored. The

H2S(H4S) status bit is always clear. When

H12 enable (H34 enable) in the port general

controlregister is clear, H2(H4) is held negated.

5. H2(H4) may be an output pin in the pulsedinput handshake protocol. It is asserted exactly

as in the interlockedinput protocol above, but

neverremains assertedlongerthan fourclock

cycles.Typically, afourclockcyclepulseis generated. But in the case of a subsequent

H1(H3) asserted edge occurring beforetermination of the pulse, H2(H4) is negated asynchronously. Thus, anytime after the leading

edge of the H2(H4) pulse, new data may be

entered in the double-buffered input latches.

TheH2S(H4S)statusbitisalwaysclear.When

H12 enable (H34 enable) is clear, H2(H4) is

heldnegated.

For pins used as outputs,the datapath consists of

a singlelatch driving the output buffer.Data written

to the port’s data register does not affectthe operationof any handshake pin or status bit. Output pins

may be used independently of the input transfers.

However, readbus cyclesto thedata register do remove datafrom theport. Therefore, care should be

taken to avoid processor instructions that perform

unwanted read cycles.

theassertededgeoftheH1(H3)input. Assoon

19/61

TS68230

Programmable Options Mode 0 - Port A Submode 00 and Port B Submode00

PACR

7 6 PortA Submode

0 0 Submode 00

PACR

5 4 3 H2 Control

0 XX Input pin - edge-sensitive statusinput, H2Sis set on an asserted edge.

1 0 0 Outputpin - negated, H2S is always clear.

1 0 1 Outputpin - asserted,H2S is always clear.

1 1 0 Outputpin - interlocked input handshake protocol, H2S is always clear.

1 1 1 Outputpin - pulsed inputhandshake protocol, H2Sis alwaysclear.

PACR

2 H2 InterruptEnable

0 The H2 interrupt is disabled.

1 The H2 interrupt is enabled.

PACR

1 H1 SVCR Enable

0 The H1 interrupt and DMA request are disabled.

1 The H1 interrupt and DMA request are enabled.

PACR

0 H1 StatusControl

X The H1S status bit is setanytime input data is present in thedouble-buffered input path.

PBCR

7 6 PortB Submode

0 0 Submode 00

PBCR

5 4 3 H4 Control

0 XX Input pin - edge-sensitive statusinput, H4Sis set on an asserted edge.

1 0 0 Outputpin - negated, H4S is always cleared.

1 0 1 Outputpin - asserted,H4S is always cleared.

1 1 0 Outputpin - interlocked input handshake protocol, H4S is always cleared.

1 1 1 Outputpin - pulsed inputhandshake protocol,H4S is alwayscleared.

20/61

Programmable Options Mode 0 - Port A Submode 00 and Port B Submode00 (continued)

PBCR

2 H4 InterruptEnable

0 The H4 interrupt is disabled.

1 The H4 interrupt is enabled.

PBCR

1 H3 SVCRQEnable

0 The H3 interrupt and DMA request are disabled.

1 The H3 interrupt and DMA request are enabled.

PBCR

0 H3 StatusControl

X The H3S status bit is setanytime input data is present in thedouble-buffered input path.

TS68230

3.3.2.SUBMODE 01 - PIN-DEFINABLE DOUBLEBUFFEREDOUTPUTORNON-LATCHED INPUT.

In mode0, double-buffered outputtransfers ofup to

eight bits are available by programming submode

01 inthe desired port’s control register. The operation ofH2 andH4 may beselectedby programming

the port A and B control registers, respectively. Data, writtenby thebus master to thePI/T, is storedin

theport’soutput latches. Theperipheral acceptsthe

databyassertingH1(H3),whichcausesthenext data to be movedto theport’s output latchas soon as

it is available.

The H1S(H3S) status bit may be programmed for

two interpretations :

1. The H1S(H3S) statusbitisset wheneitherthe

port initial or final output latchcan accept new

data. It is cleared when both latches are full

and cannot acceptnew data.

2. The H1S(H3S) status bit is set when both of

the port output latches are empty.It is cleared

whenat leastone latchis full.

The programmable options of the H2(H4)pin are :

1. H2(H4) maybe an edge-sensitive input pin independent of H1(H3) and the transfer of port

data. On the asserted edge of H2(H4), the

H2S(H4S) status bit is set. It is cleared by either the RESET pin being asserted, writing a

oneto theparticular statusbit inthe portstatus

register (PSR), or when the H1(H2) enable

(H3(H4) enable) bit of the portgeneralcontrol

register is clear.

2. H2(H4) may be a general-purpose output pin

that is always negated. The H2S(H4S) status

bit is always clear.

3. H2(H4) may be a general-purpose output pin

thatis always asserted. The H2S(H4S)status

bit is always clear.

4. H2(H4)maybe anoutputpinintheinterlocked

output handshake protocol. H2(H4) is assertedtwo clockcyclesafterdata istransferred to

the double-buffered output latches. The data

remains stable at the portpins and H2(H4) remainsasserteduntilthenext assertededge of

the H1(H3) input. At that time,H2(H4) is asynchronously negated. As soon asthe next data

is available, it is transferred to the output

latches. When H2(H4) is negated, asserted

transitions of H1(H3) have no affect on data

paths.TheH2S(H4S)statusbitisalwaysclear.

When H12 enable (H34 enable) is clear,

H2(H4) is held negated.

5. H2(H4)maybe anoutput pininthe pulsedoutput handshake protocol. It is asserted exactly

as inthe interlocked protocolabove, butnever

remains asserted longer than four clock cycles.Typically, a fourclockpulseisgenerated.

But in the casethat a subsequentH1(H3) asserted edge occurs before termination of the

pulse, H2(H4) is negated asynchronously

shorteningthe pulse.The H3S(H4S) statusbit

is always clear. When H12 enable (H34

enable) isclear H2(H4) is held negated.

For pins used asinputs,data writtento theassociated data register is double-buffered and passed to

the initial orfinal output latch, but, the output buffer

is disabled.

21/61

TS68230

Programmable Options Mode 0 - Port A Submode 01 and Port B Submode01

PACR

7 6 PortA Submode

0 1 Submode 01

PACR

5 4 3 H2 Control

0 XX Input pin - edge-sensitive statusinputs, H2S isset onan assertededge.

1 0 0 Outputpin - negated, H2S is always clear.

1 0 1 Outputpin - asserted,H2S is always clear.

1 1 0 Outputpin - interlocked input handshake protocol, H2S is always clear.

1 1 1 Outputpin - pulsed inputhandshake protocol,H2S is alwaysclear.

PACR

2 H2 InterruptEnable

0 The H2 interrupt is disabled.

1 The H2 interrupt is enabled.

PACR

1 H1 SVCRQEnable

0 The H1 interrupt and DMA request are disabled.

1 The H1 interrupt and DMA request are enabled.

PACR

0 H1 StatusControl

0 The H1S status bit is setwhen either the portA initial or final output latch can accept new data

It is clear when both latches are fulland cannot accept new data.

1 The H1S status bit is one when both ofthe port A output latches are empty.It is clear when at

least one latchis full.

PBCR

7 6 PortB Submode

0 1 Submode 01

PBCR

5 4 3 H4 Control

0 XX Input pin - edge-sensitive statusinput, H4Sis set on an asserted edge.

1 0 0 Outputpin - negated, H4S is always cleared.

1 0 1 Outputpin - asserted,H4S is always cleared.

1 1 0 Outputpin - interlocked input handshake protocol, H4S is always cleared.

1 1 1 Outputpin - pulsed inputhandshake protocol,H4S is alwayscleared.

22/61

TS68230

Programmable Options Mode 0 - Port A Submode 01 and Port B Submode01 (continued)

PBCR

2 H4 InterruptEnable

0 The H4 interrupt is disabled.

1 The H4 interrupt is enabled.

PBCR

1 H3 SVCRQEnable

0 The H3 interrupt and DMA request are disabled.

1 The H3 interrupt and DMA request are enabled.

PBCR

0 H3 StatusControl

0 The H3S status bit is setwhen either the portB initial or final output latch can accept new data.

It is clear when both latches are fulland cannot accept new data.

1 The H3S status bit is one when both ofthe port B output latches are empty.It is clear when at

least one latchis full.

3.3.3. SUBMODE 1X - BIT I/O (PIN-DEFINABLE

SINGLE-BUFFERED OUTPUT OR NON-LATCHEDINPUT). In mode0,simplebit I/Oisavailable

by programming submode 1X in the desired port’s

controlregister. This submode is intended forapplications in whichseveral independent devices must

be controlled or monitored. Data written to the associated(input/output) register is single buffered. If

the data direction register bit for that pin is a one

(output), the output buffer is enabled. If it is a zero

(input)data writtenisstilllatched,butis notavailable

at the pin.Data readfrom the data register is the instantaneous valueof the pin or what was written to

the data register, depending on the contents of the

data direction register. H1(H3) is an edge-sensitive

status input pin only and it controls no data related

function.TheH1S(H3S)statusbitissetfollowing the

assertededgeof theinput waveform. Itiscleared by

eitherthe RESET pin being asserted,writing a one

tothe associated statusbit intheportstatusregister

(PSR),or whenthe H12enable (H34 enable) bit of

the port general control register isclear. H2 maybe

programmed as :

1. H2(H4) may bean edge-sensitive status input

thatis independent of H1(H3) and the transfer

of port data. On the asserted edgeof H2(H4),

the H2S(H4S) status bit is set.It iscleared by

either the RESETpinbeing asserted, writinga

oneto theparticularstatusbitin theportstatus

register (PSR), or whenthe H12 enable(H34

enable) bit of the port general control register

is clear.

2. H2(H4) may be a general-purpose output pin

that is always negated. In this case the

H2S(H4S) status bit is always clear.

3. H2(H4) may be a general-purpose output pin

that is always asserted. In this case the

H2S(H4S) status bit is always clear.

23/61

TS68230

Programmable OptionMode 0 - Port A Submode 1X and Port B Submode 1X

PACR

7 6 PortA Submode

1 X Submode 1X

PACR

5 4 3 H2 Control

0 XX Input pin - edge-sensitive statusinput, H2Sis set on an asserted edge.

1 X0 Output pin -negated, H2S is always cleared.

1 X1 Output pin -asserted, H2S is always cleared.

PACR

2 H2 InterruptEnable

0 The H2 interrupt is disabled.

1 The H2 interrupt is enabled.

PACR

1 H1 SVCRQEnable

0 The H1 interrupt is disabled.

1 The H1 interrupt is enabled.

PACR

0 H1 StatusControl

X H1 isan edge-sensitive status input, H1S is set by an assertededge of H1.

PBCR

7 6 PortB Submode

1 X Submode 1X.

PBCR

5 4 3 H4 Control

0 XX Input pin - edge-sensitive statusinput, H4Sis set on an asserted edge.

1 X0 Output pin -negated, H4S is always cleared.

1 X1 Output pin -asserted, H4S is always cleared.

PBCR

2 H4 InterruptEnable

0 The H4 interrupt is disabled.

1 The H4 interrupt is enabled.

PBCR

1 H3 SVCRQEnable

0 The H3 interrupt is disabled.

1 The H3 interrupt is enabled.

24/61

Programmable Options Mode 0 - Port A Submode 1X and Port B Submode 1X (continued)

PBCR

0 H3 StatusControl

X H3 isan edge-sensitive status input, H3S is set by an assertededge of H3.

TS68230

3.4. MODE 1 - UNIDIRECTIONAL16-BIT MODE

In mode 1,ports A and B are concatenated to form

a single 16-bit port. The port B submode field

controlstheconfiguration ofbothports.Thepossible

submodes are :

Port B Submode X0 - Pin-Definable Double-Buffered Input or Single-Buffered Output

Port B Submode X1 - Pin-Definable Double-Buffered Output or Non-Latched Input

HandshakepinsH3and H4,configured byprogrammingthe port B control register, are associated with

the 16-bit double-buffered transfer. These 16-bit

transfersare enabled by settingthe H34 enable bit

in the port general control register (PGCR). HandshakepinsH1 andH2may beusedas simplestatus

inputs not related to the 16-bit data transfer or H2

maybeanoutput.Enabling ofthe H1andH2handshake pins is done by setting the H12 enable bit of

the port general control register. The port A and B

data direction registers operate in each submode.

Along with the submode, they affect the data read

and written at the data register according to table

3.2.Thedatadirection register alsoenables theoutput buffer associated with each port pin. The DMAREQpin may be associatedonly withH3.

Table 3.2 : Mode 1 Port Data Paths.

Mode

1, Port B

Submode X0

1, Port B

Submode X1

Note 1 : Data written to Port A goes to a temporary latch. When the Port B data register is later written, Port A

data is transferred to IOL/FOL.

Note 2 : Data is latched in the output data registers (final output latch) and will be single buffered at the pin if

the DDR is 1. The output buffers will be turned off if the DDR is 0.

Note 3 : The output drivers that connect the final output latch to the pins are turned on.

Abbreviations :

IOL - Initial Output Latch

FOL - Final Output Latch

FIL - Final Input Latch

Re a d Port A/B R eg i ster Writ e Port A/B Re g ister

DDR = 0 DDR = 1 DDR = 0 DDR = 1

FIL, D. B.

Pin

FOL

Note 3

FOL

Note 3

S. B. - Single Buffered

D. B. - Double Buffered

DDR - Data Direction Register

FOL, S. B.

Note 2

IOL/FOL, D. B.

Note 1

FOL, S. B.

Note 2

IOL/FOL, D. B.

Note 1

Mode 1 can provide convenient high-speed 16-bit

transfers. The port A and port B data registers are

addressed forcompatibility withthe TS68000 move

peripheral (MOVEP) instruction and with the 68440

direct memory access controller (DMAC). To take

advantage of this, port A should contain the mostsignificant byteof dataandalwaysbereadorwritten

by the bus master first. The interlocked and pulsed

handshake protocols, statusbits,andDMAREQare

keyed to theaccess of port B data register in mode

1. Transfers proceed properly with interlocked or

pulsedhandshakes whenthe port B dataregister is

accessedlast.

25/61

TS68230

3.4.1.PORT A CONTROLREGISTER(PACR).

765432 1 0

Port A

Submode H2 Control

H2

Interrupt

Enable

H1

SVCRQ

Enable

H1

Status

Control

The port A control register, in conjunction with the

programmed mode and the port B submode,

controls the operation of port A and the handshake

pinsH1and H2. TheportA control register contains

fivefields : bits7 and 6 specifythe port Asubmode;

bits5, 4, and3controlthe operation oftheH2 handshakepinand H2Sstatusbit; bit2 determines whether an interrupt will be generated when the H2S

status bit goes to one ; bit 1 determines whether a

servicerequest (interrupt request or DMA request)

willoccur;andbit0controls theoperation oftheH1S

status bit. The PACR is always readable andwritable.There isnevera consequenceto reading theregister.

Allbitsarecleared tozerowhentheRESETpinis asserted.When the port Asubmode fieldis relevant in

amode/submodedefinition,itmustnotbealtered unlesstheH12 enable bitin the portgeneral controlregisterisclear(see table 1.3 located at theend ofthis

document). Altering these bits may give unpredictable results if the H12 enable bit in the PGCRis

set.

3.4.2.PORT B CONTROLREGISTER(PBCR).

7 6543 2 1 0

Port B

Submode H4Control

H4

Interrupt

Enable

H3

SVCRQ

Enable

H3

Status

Control

The port Bcontrolregister specifies the operation of

portB and thehandshake pins H3and H4.The port

B control register contains five fields : bits 7 and 6

specifythe port B submode ; bits 5, 4, and 3control

theoperation oftheH4handshake pinandH4S statusbitgoesto aone;bit1determines whether aservicerequest (interrupt request or DMA request) will

occur ; and bit 0 controls the operation of the H3S

status bit. The PBCR is always readable andwritable.

All bits are cleared to zero when the RESET pin is

asserted.When theport Bsubmodefieldisrelevant

ina mode/submode definition,it must notbealtered

unless the H34enable bitin theportgeneral control

register is clear (seetable 1.3 located at theend of

thisdocument). Altering these bitsmay give unpredictableresultsif the H12 enablebit inthe PGCRis

set.

3.4.3.SUBMODE X0- PIN-DEFINABLE DOUBLEBUFFERED INPUT OR SINGLE-BUFFERED

OUTPUT.In mode 1 submodeX0, double-buffered

inputtransfers ofupto 16 bitsmaybeobtained.The

level of each pin is asynchronously latched withthe

asserted edge of H3 and placed in the initial input

latch or the final input latch. The processor may

checkthe H3S status bitto determine ifnew data is

present. The DMAREQ pin maybe used to signala

DMA controller to empty the input buffers. Regardlessof the bus master, portA data shouldbe read

first and port B data should be read last. The operationof theinternal handshake controller, theH3S

bit,and theDMAREQarekeyedtothereadingofthe

port Bdata register. (The 68440DMAC canbe programmed toperform theexact transfersneeded for

compatibilitywiththePI/T.)H4maybeprogrammed

as :

1. H4 may be an edge-sensitive status inputthat

is independent of H3 and the transfer of port

data.OntheassertededgeofH4,theH4Sstatus bit is set. It is cleared by either theRESET

pin being asserted, writinga one to the particular statusbitintheportstatusregister(PSR),

or whenthe H34enable bit of the port general

controlregister is clear.

2. H4 may be a general-purpose output pin that

is always negated. In thiscase the H4Sstatus

bit is always clear.

3. H4 may be a general-purpose output pin that

is always asserted.In thiscasetheH4S status

bit is always clear.

4. H4 maybe an output pin in the interlocked input handshake protocol. It is asserted when

the port inputlatches are ready to accept new

data. It is negated asynchronously following

the asserted edge of the H3 input.As soon as

the input latches become ready, H4 is again

asserted. When the input double-buffered

latchesare full,H4 remainsnegated until data

isremoved.Thus,anytime theH4 output isasserted,new input data may be entered by asserting H3.Atothertimestransitionson H3are

ignored. The H4S status bit is always clear.

When H34 enable in the port general control

register is clear, H4is heldnegated.

26/61

TS68230

5. H4 may be an output pin in the pulsed input

handshake protocol. It isasserted exactlyas in

the interlocked input protocolabove,but never

remainsasserted longer thanfourclockcycles.

Typically, afourclockcyclepulseis generated.

But inthe case that a subsequent H3 asserted

edgeoccursbeforeterminationofthepulse,H4

isnegatedasynchronously. Thus,anytimeafter

theleadingedgeoftheH4pulse,newdatamay

beenteredinthedouble-buffered inputlatches.

The H4Sstatus bit is alwaysclear.When H34

enable isclear, H4 is held negated.

For pins used as outputs,the datapath consists of

a singlelatch driving the output buffer. Data written

to the port’s data register does notaffectthe operationofanyhandshake pin, statusbit,oranyotheraspect of the PI/T. Thus, output pins may be used

independently of theinput transfer.

Programmable Options Mode 1 - Port A Submode XX and Port B SubmodeX0

PACR

7 6 PortA Submode

0 0 Submode XX

The programmable options of the H2 pin are:

1. H2 may be an edge-sensitive input pin independent ofH1and thetransferof port data. On

the assertededge of H2, the H2S statusbit is

set.It iscleared byeithertheRESETpinbeing

asserted, writing a oneto the particularstatus

bitin theportstatusregister (PSR),orwhenthe

H12 enable bit of the port general control registeris clear.

2. H2 may be a general-purpose output pin that

is always negated. The H2S status bit is alwaysclear.

3. H2 may be a general-purpose output pin that

is always asserted. The H2S status bit is alwaysclear.

PACR

5 4 3 H2 Control

0 XX Input pin - edge-sensitive statusinput, H2Sis set on an asserted edge.

1 X0 Output pin -negated, H2S is always cleared.

1 X1 Output pin -asserted, H2S is always cleared.

PACR

2 H2 InterruptEnable

0 The H2 interrupt is disabled.

1 The H2 interrupt is enabled.

PACR

1 H1 SVCRQEnable

0 The H1 interrupt is disabled.

1 TheH1 interrupt is enabled.

PACR

0 H1 StatusControl.

X H1 isan edge-sensitive status input. H1S is set by an assertededge of H1.

PBCR

7 6 PortB Submode

0 0 Submode X0.

27/61

TS68230

Programmable Options Mode 1 - Port A Submode XX and Port B SubmodeX0 (continued)

PBCR

5 4 3 H4 Control

0 XX Input pin - edge-sensitive statusinput, H4Sis set on an asserted edge.

1 0 0 Outputpin - negated, H4S is always cleared.

1 0 1 Outputpin - asserted, H4S is always cleared.

1 1 0 Outputpin - interlocked input handshake protocol.

1 1 1 Outputpin - pulsed inputhandshake protocol.

PBCR

2 H2 InterruptEnable

0 The H4 interrupt is disabled.

1 The H4 interrupt is enabled.

PBCR

1 H3 SVCRQEnable

0 The H3 interrupt and DMA request are disabled.

1 The H3 interrupt and DMA request are enabled.

PBCR

0 H3 StatusControl

X The H3S status bit is setanytime input data is present in thedouble-buffered input path.

3.4.4.SUBMODE X1- PIN-DEFINABLE DOUBLEBUFFEREDOUTPUTORNON-LATCHED INPUT.

In mode 1 submode X1, double-buffered output

transfers of up to 16 bits may be obtained. Data is

written by the bus master (processor or DMA controller)in two bytes. The firstbyte (mostsignificant)

is written to the port A data register. It is storedin a

temporary latch until the next byte is written to the

portB dataregister.Then all 16 bits aretransferred

to one of the output latches of ports A and B. The

DMAREQpin maybeused tosignala DMAcontroller to transfer another word to the port output

latches. (The 68440 DMAC can be programmed to

perform the exacttransfers needed forcompatibility

withthe PI/T.)H4 may be programmed as :

1. H4 may be an edge-sensitive status input that

is independent of H3 and the transfer of port

data.OntheassertededgeofH4, theH4Sstatus bit is set. It iscleared by eitherthe RESET

pin being asserted, writing a one to the particularstatusbitinthe portstatusregister(PSR),

or whenthe H34 enable bitof the port general

controlregister is clear.

2. H4 may be a general-purpose output pin that

is always negated. In this casethe H4Sstatus

bit is always clear.

3. H4 may be a general-purpose output pin that

is always asserted.In thiscasetheH4S status

bit is always clear.

4. H4 maybe anoutput pininthe interlocked output handshake protocol. H4 is asserted two

clockcyclesafterdatais transferredtothedouble-buffered output latches. Thedata remains

stable at the port pins and H4 remains asserteduntilthenext assertededgeof theH3 input.

Atthattime,H4isasynchronously negated. As

soon as the next data is available, it is transferredto the output latches.WhenH4 is negated, asserted transitions of H3 have no affect

on data paths. The H4S status bit is always

clear. WhenH34enableis clear, H4is heldnegated.

5. H4 maybe an output pinin the pulsed output

handshake protocol. Itis assertedexactlyasin

the interlocked protocol above, but never remains asserted longer than four clock cycles.

Typically, a four clock pulse is generated. But

in the case that a subsequent H3 asserted

edge occurs before termination of the pulse,

H4 is negated asynchronously shortening the

pulse. The H4S status bit is always cleared.

WhenH34enable isclear,H4 is heldnegated.

28/61

TS68230

The H3S statusbit may be programmed for two interpretations :

1. The H3S statusbit is set when either the port

initialor finaloutput latchcan acceptnewdata.

Itis clearwhenbothlatchesarefulland cannot

accept new data.

2. The H3S statusbitis set whenboth of theport

output latches are empty. It is clear when at

least onelatch is full.