TS616

DUAL WIDE BAND OPERATIONAL AMPLIFIER

WITH HIGH OUTPUT CURRENT

■ LOW NOISE : 2.5nV/√Hz

■ HIGH OUTPUT CURRENT : 420mA

■ VERY LOW HARMONIC AND INTERMODU-

LATION D I S TORTIO N

■ HIGH SLEW RA TE : 420V/µs

■ -3dB BANDWIDTH : 40MHz@gain=12dB on

25Ω load single ended.

■ 20.7Vp-p DIFFERENTIAL OUTPUT SWING

on 50Ω load, 12V power supply

■ CURRENT FEEDBACK STRUCTURE

■ 5V to 12V POWER SUPPLY

■ SPECIFIED FOR 20Ω and 50Ω

DIFFERENTIAL LOAD

DESCRIPTION

The TS616 is a dual operational am plifier featuring a high output current o f 410m A. T he drivers

can be configured differentially for driving signals

in telecommunication systems using multiple carriers. The TS616 is ideally suited for xDSL (High

Speed Asymmetrical Digital Subscriber Line) applications. This circuit is c apable of driving a 10 Ω

or 25Ω load at ±2.5V, 5V, ±6V or +12V power

supply. The TS616 is able to reach a -3dB bandwidth of 40MHz on 25Ω load with a 12dB gain.

This device is designed for high slew rates supporting low harmonic distortion and intermodulation.

DW

SO8 Exposed-Pad

(Plastic Micro package)

ORDER CODE

Part Number Temperature Range Package

TS616IDW -40, +85°C DW

TS616IDWT -40, +85°C DW

DW = Small Outline Package with Exposed-Pad, T = Tape & Real

PIN CONNECTIONS (top view)

Output1

Output1

1

1

2

VCC -

VCC -

2

-

-

+

+

3

3

4

4

Inverting Input1 Output2

Inverting Input1 Output2

Non Inverting Input1

Non Inverting Input1

VCC +

VCC +

8

8

7

7

Inverting Input2

Inverting Input2

6

6

-

-

+

+

Non Inverting Input2

Non Inverting Input2

5

5

APPLICATION

■ Line driver for xDSL

■ Multiple Video Line Driver

December 2002

Cross Section View Showing Exposed-Pad

Cross Section View Showing Exposed-Pad

This pad can be connected to a (-Vcc) copper area on the PCB

This pad can be connected to a (-Vcc) copper area on the PCB

1/27

TS616

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

T

T

R

R

P

ESD

only pins

1, 4, 7, 8

ESD

only pins

2, 3, 5, 6

Supply voltage

CC

V

Differential Input Voltage

id

V

Input Voltage Range

in

Operating Free Air Temperature Range -40 to + 85 °C

oper

Storage Temperature -65 to +150 °C

std

T

Maximum Junction Temperature 150 °C

j

Thermal Resistance Junction to Case 16 °C/W

thjc

Thermal Resistance Junction to Ambient Area 60 °C/W

thja

Maximum Power Dissipation (@Ta=25°C) for Tj=150°C 2 W

max.

CDM : Charged Device Model

HBM : Human Body Model

MM : Machine Model

CDM : Charged Device Model

HBM : Human Body Model

MM : Machine Model

Output Short Circuit

1. All voltage values, except differential voltage are with respect to network terminal.

2. Differential voltage are non-inverting input terminal with respect to the inverting input terminal.

3. The magnitude of input and output voltage must never exceed V

4. An output current limitation protects the circuit from transient currents. Short-circuits can cause excessive heating.

Destructive dissipation can result from short circuit on amplifiers.

1)

2)

3)

±7 V

±2 V

±6 V

1.5

2

200

1.5

2

100

4)

+0.3V.

CC

kV

kV

V

kV

kV

V

OPERATING CONDITIONS

Symbol Parameter Value Unit

V

V

Power Supply Voltage ±2.5 to ±6 V

CC

+1.5V to +VCC-1.5V

Common Mode Input Voltage

icm

-V

CC

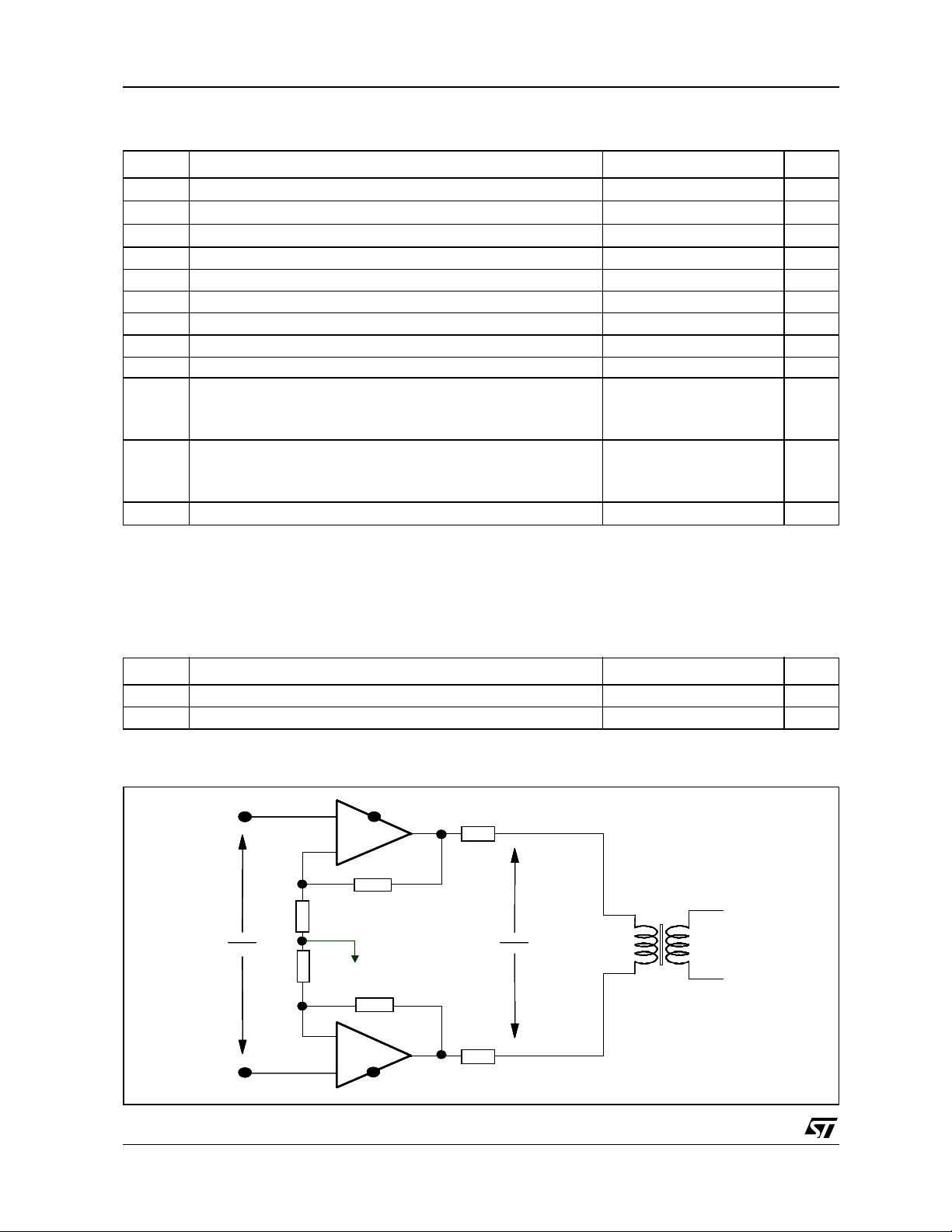

TYPICAL APPLICATION:

Differential Line Driver for xDSL Applications

8

8

3

3

2

2

Vi

Vi

Vi

Vi

R1

R1

R4

R4

Vi Vo

Vi Vo

Vi Vo

Vi Vo

4

4

5

5

+

+

+

+

1/2TS615

1/2TS616

1/2TS615

1/2TS616

_

_

_

_

R2

R2

GND

GND

R3

R3

_

_

_

_

1/2TS615

1/2TS616

1/2TS615

1/2TS616

+

+

+

+

4

4

+Vcc

+Vcc

+Vcc

+Vcc

-Vcc

-Vcc

-Vcc

-Vcc

Ω

Ω

Ω

Ω

12.5

12.5

12.5

12.5

1

1

1

1

Vo

Vo

Vo

12.5

12.5

12.5

12.5

Vo

25

25

25

25

Ω

Ω

Ω

Ω

Ω

Ω

Ω

Ω

1:2

1:2

1:2

1:2

100

100

100

100

Ω

Ω

Ω

Ω

V

2/27

TS616

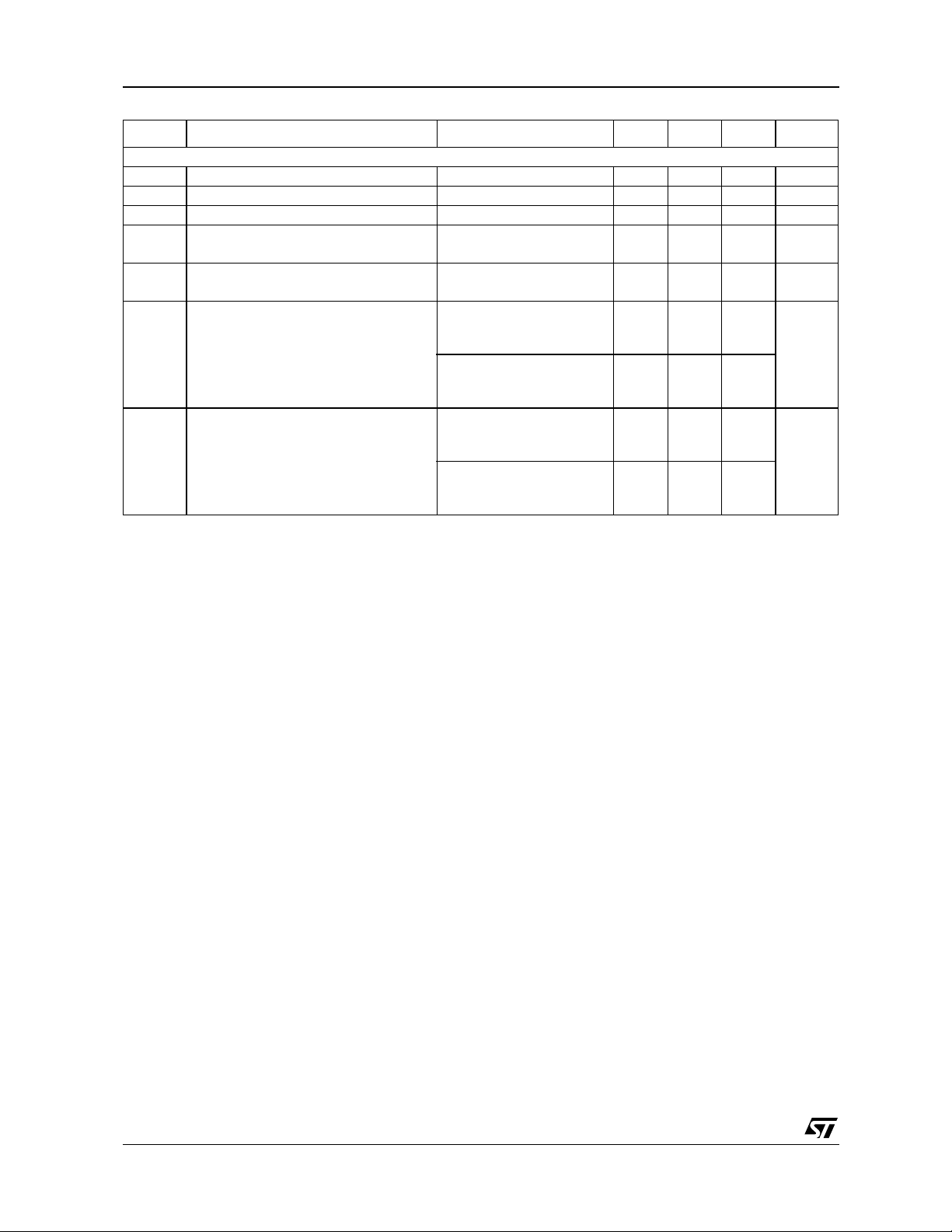

ELECTRICAL CHARACTERISTICS

V

= ±6Volts, Rfb=910Ω,T

CC

Note: As described on page 24 (table 71), the TS616 requires a 620Ω feedback resistor for an optimized bandwidth with a gain of 12B for

a 12V power supply. Nevertheless, due to production test constraints, the TS616 is tested with the same feedback resistor for 12V and 5V

power su ppl i es (910Ω).

Symbol Parameter Test Condition Min. Typ. Max. Unit

DC PERFORMANCE

V

Input Offset Voltage

io

V

∆

Z

C

CMR

SVR

Differential Input Offset Voltage

io

I

Positive Input Bias Current

ib+

I

Negative Input Bias Current

ib-

Input(+) Impedance 82 k

IN+

Z

Input(-) Impedance 54

IN-

Input(+) Capacitance 1 pF

IN+

Common Mode Rejection Ratio

20 log (∆V

/∆Vio)

ic

Supply Voltage Rejection Ratio

20 log (∆V

I

Total Supply Current per Operator No load 13.5 17 mA

CC

/∆Vio)

cc

DYNAMIC PERFORMANCE and OUTPUT CHARACTERISTIC

R

Open Loop Transimpedance

OL

-3dB Bandwidth

Full Power Bandwidth

BW

Gain Flatness @ 0.1dB

Tr Rise Time

Tf Fall Time

Ts Settling Time

SR Slew Rate

V

High Level Output Voltage

OH

V

Low Level Output Voltage

OL

Output Sink Current

I

out

Output Source Current

= 25°C (unless otherwise specified)

amb

T

amb

< T

T

min.

T

amb

T

amb

T

min.

T

amb

T

min.

V

∆

ic

T

min.

V

∆

cc

T

min.

V

out

T

min.

< T

amb

= 25°C

< T

< T

amb

< T

< T

amb

= ±4.5V

< T

< T

amb

=±2.5V to ±6V

< T

< T

amb

= 7Vp-p, RL = 25

< T

amb.

Small Signal V

A

= 12dB, RL = 25

V

Large Signal V

= 12dB, RL = 25

A

V

Small Signal V

= 12dB, RL = 25

A

V

V

= 6Vp-p, AV = 12dB, RL

out

= 25

Ω

= 6Vp-p, AV = 12dB, RL

V

out

= 25

Ω

= 6Vp-p, AV = 12dB, RL

V

out

= 25

Ω

= 6Vp-p, AV = 12dB, RL

V

out

= 25

Ω

R

=25Ω Connected to GND

L

R

=25Ω Connected to GND

L

V

= -4Vp

out

< T

T

min.

V

out

T

min.

amb

= +4Vp

< T

amb

< T

< T

< T

max.

max.

max.

max.

max.

max.

<20mVp

out

Ω

=3Vp

out

Ω

<20mVp

out

Ω

max.

max.

1 3.5

1.6

mV

2.5 mV

530

7.2

315

3.1

A

µ

A

µ

Ω

Ω

58 64

62

72 81

80

Ω

5 13.5

5.7

dB

dB

M

Ω

25 40

MHz

26

7 MHz

10.6 ns

12.2 ns

50 ns

330 420 V/µs

4.8 5.05 V

-5.3 -5.1 V

-320 -490

-395

330 420

mA

370

3/27

TS616

Note: As described on page 24 (table 71), the TS616 requires a 620Ω feedback resistor for an optimized bandwidth with a gain of 12B for

a 12V power supply. Nevertheless, due to production test constraints, the TS616 is tested with the same feedback resistor for 12V and 5V

power su ppl i es (910Ω).

Symbol Parameter Test Condition Min. Typ. Max. Unit

NOISE AND DISTORTION

eN Equivalent Input Noise Voltage F = 100kHz 2.5 nV/√Hz

iNp Equivalent Input Noise Current (+) F = 100kHz 15 pA/√Hz

iNn Equivalent Input Noise Current (-) F = 100kHz 21 pA/√Hz

= 14Vp-p, AV = 12dB

HD2

HD3

IM2

IM3

2nd Harmonic Distortion

(differential configuration)

3rd Harmonic Distortion

(differential configuration)

2nd Order Intermodulation Product

(differential configuration)

3rd Order Intermodulation Produ ct

(differential configuration)

V

out

F= 110kHz, R

= 14Vp-p, AV = 12dB

V

out

F= 110kHz, R

= 50Ω diff.

L

= 50Ω diff.

L

F1= 100kHz, F2 = 110kHz

= 16Vp-p, AV = 12dB

V

out

= 50Ω diff.

R

L

F1= 370kHz, F2 = 400kHz

= 16Vp-p, AV = 12dB

V

out

R

= 50Ω diff.

L

F1 = 100kHz, F2 = 110kHz

= 16Vp-p, AV = 12dB

V

out

= 50Ω diff.

R

L

F1 = 370kHz, F2 = 400kHz

= 16Vp-p, AV = 12dB

V

out

= 50Ω diff.

R

L

-87 dBc

-83 dBc

-76

dBc

-75

-88

dBc

-87

4/27

TS616

ELECTRICAL CHARACTERISTICS

V

= ±2.5Volts, Rfb=910Ω,T

CC

Symbol Parameter Test Condition Min. Typ. Max. Unit

DC PERFORMANCE

V

Input Offset Voltage

io

V

∆

Z

C

CMR

SVR

Differential Input Offset Voltage

io

I

Positive Input Bias Current

ib+

I

Negative Input Bias Current

ib-

Input(+) Impedance 71 k

IN+

Z

Input(-) Impedance 62

IN-

Input(+) Capacitance 1.5 pF

IN+

Common Mode Rejection Ratio

20 log (∆V

/∆Vio)

ic

Supply Voltage Rejection Ratio

20 log (∆V

I

Total Supply Current per Operator No load 11.5 15 mA

CC

/∆Vio)

cc

DYNAMIC PERFORMANCE and OUTPUT CHARACTERISTICS

R

Open Loop Transimpedance

OL

-3dB Bandwidth

BW

Full Power Bandwidth

Gain Flatness @ 0.1dB

Tr Rise Time

Tf Fall Time

Ts Settling Time

SR Slew Rate

V

High Level Output Voltage

OH

V

Low Level Output Voltage

OL

Output Sink Current

I

out

Output Source Current

= 25°C (unless otherwise specified)

amb

T

amb

< T

T

min.

T

amb

T

amb

T

min.

T

amb

T

min.

V

∆

ic

T

min.

V

∆

cc

T

min.

V

out

T

min.

< T

amb

= 25°C

< T

< T

amb

< T

< T

amb

= ±1V

< T

< T

amb.

=±2V to ±2.5V

< T

< T

amb.

= 2Vp-p, RL = 10

< T

< T

amb.

Small Signal V

= 12dB, RL = 10

A

V

Large Signal V

= 12dB, RL = 10

A

V

Small Signal V

A

= 12dB, RL = 10

V

V

= 2.8Vp-p, AV = 12dB

out

= 10

R

Ω

L

V

= 2.8Vp-p, AV = 12dB

out

= 10

R

Ω

L

= 2.2Vp-p, AV = 12dB

V

out

= 10

R

Ω

L

= 2.2Vp-p, AV = 12dB

V

out

R

= 10

Ω

L

R

=10Ω Connected to GND

L

R

=10Ω Connected to GND

L

= -1.25Vp

V

out

< T

T

min.

V

out

T

min.

< T

amb

= +1.25Vp

< T

< T

amb

max.

max.

max.

max.

max.

Ω

max.

<20mVp

out

Ω

= 1.4Vp

out

Ω

<20mVp

out

Ω

max.

max.

0.2 2.5

1

2.5 mV

430

7

1.1 11

1.2

55 61

60

63 79

78

24.2

1.5

20 28

MHz

20

5.7 MHz

11 ns

11.5 ns

39 ns

100 130 V/µs

1.5 1.7 V

-1.9 -1.7 V

-300 -400

-360

200 270

240

mV

A

µ

A

µ

Ω

Ω

dB

dB

M

Ω

mA

5/27

TS616

Symbol Parameter Test Condition Min. Typ. Max. Unit

NOISE AND DISTORTION

eN Equivalent Input Noise Voltage F = 100kHz 2.5 nV/√Hz

iNp Equivalent Input Noise Current (+) F = 100kHz 15 pA/√Hz

iNn Equivalent Input Noise Current (-) F = 100kHz 21 pA/√Hz

= 6Vp-p, AV = 12dB

HD2

HD3

IM2

IM3

2nd Harmonic Distortion

(differential configuration)

3rd Harmonic Distortion

(differential configuration)

2nd Order Intermodulation Product

(differential configuration)

3rd Order Intermodulation Produ ct

(differential configuration)

V

out

F= 110kHz, R

= 6Vp-p, AV = 12dB

V

out

F= 110kHz, R

= 20Ω diff.

L

= 20Ω diff.

L

F1= 100kHz, F2 = 110kHz

= 6Vp-p, AV = 12dB

V

out

R

= 20Ω diff.

L

F1= 370kHz, F2 = 400kHz

V

= 6Vp-p, AV = 12dB

out

= 20Ω diff.

R

L

F1 = 100kHz, F2 = 110kHz

= 6Vp-p, AV = 12dB

V

out

= 20Ω diff.

R

L

F1 = 370kHz, F2 = 400kHz

V

= 6Vp-p, AV = 12dB

out

R

= 20Ω diff.

L

-97 dBc

-98 dBc

-86

-88

-90

-85

dBc

dBc

6/27

TS616

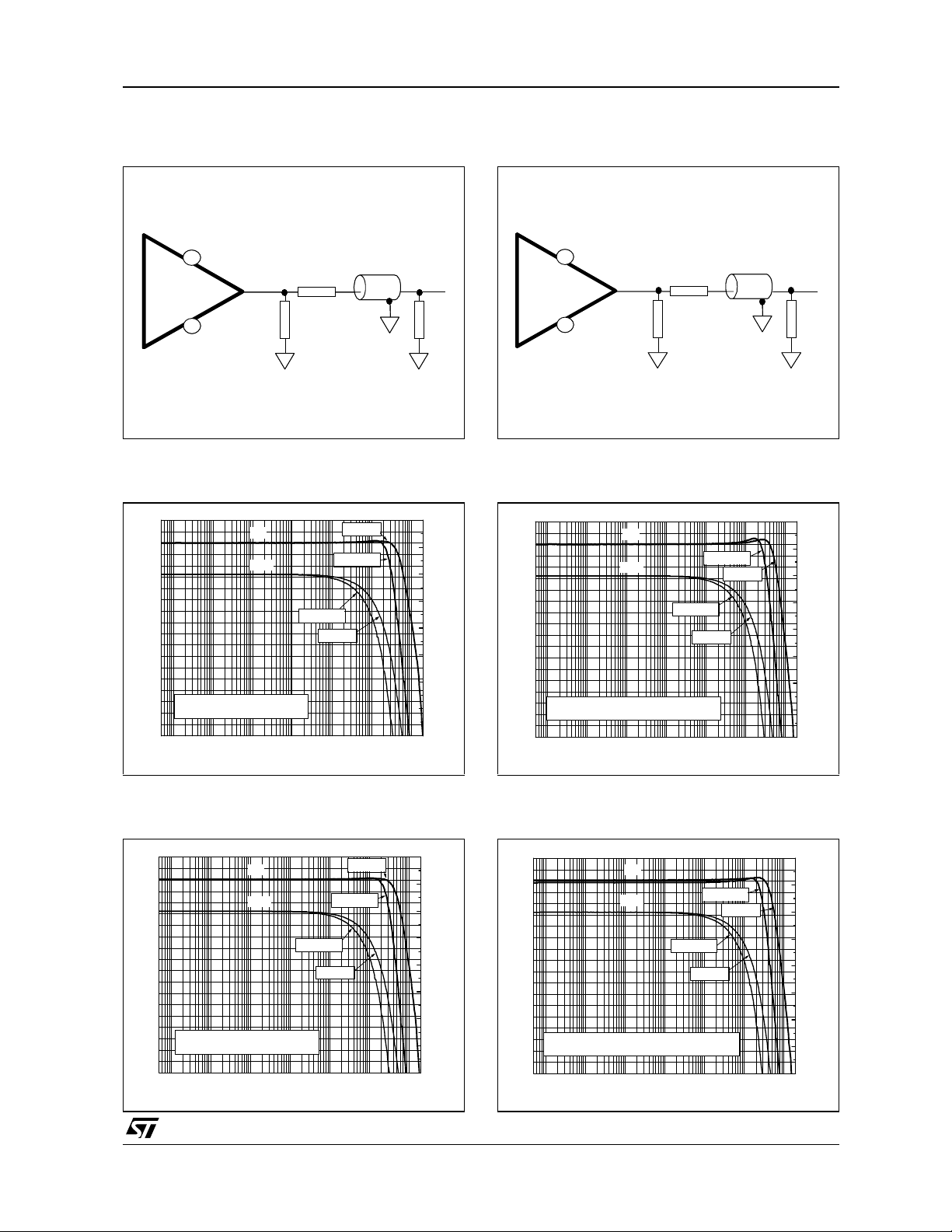

Figure 1: Load Configuration

Load: RL=25Ω, VCC=±6V

+6V

TS616

TS616

+6V

-6V

-6V

+

+

_

_

25Ω

25Ω

50Ω

50Ω

cable

49.9Ω

49.9Ω

33Ω

33Ω

1W

1W

cable

Figure 2: Closed Loop Gain vs. Frequency

AV=+1

2

0

-2

-4

-6

-8

(gain (dB)

-10

-12

-14

(Vcc=±2.5V, Rfb=1.1kΩ, Rload=10Ω)

(Vcc=±6V, Rfb=750

-16

100 1k 10k 100k 1M 10M 100M

gain

phase

Ω, Rload=25Ω)

Frequency (Hz)

(Vcc=±6V)

(Vcc=±2.5V)

(Vcc=±2.5V)

(Vcc=±6V)

50Ω

50Ω

40

20

0

-20

-40

-60

-80

-100

-120

Figure 4: Load Configuration

Load: RL=10Ω, VCC=±2.5V

+2.5V

TS616

TS616

+2.5V

-2.5V

-2.5V

10Ω

10Ω

+

+

_

_

11Ω

11Ω

0.5W

0.5W

49.9Ω

49.9Ω

Figure 5: Closed Loop Gain vs. Frequency

AV=-1

2

0

-2

)

°

Phase (

-4

-6

-8

(gain (dB))

-10

-12

-14

(Vcc=±2.5V, Rfb=1kΩ, Rin=1kΩ , Rload=10Ω)

(Vcc=±6V, Rfb=680

-16

100 1k 10k 100k 1M 10M 100M

gain

phase

(Vcc=±2.5V)

Ω, Rin=680Ω, Rload=25Ω)

Frequency (Hz)

(Vcc=±2.5V)

(Vcc=±6V)

50Ω

50Ω

cable

cable

(Vcc=±6V)

50Ω

50Ω

-140

-160

-180

-200

-220

-240

-260

-280

-300

)

°

Phase (

Figure 3: Closed Loop Gain vs. Frequency

AV=+2

8

6

4

2

0

-2

(gain (dB))

-4

-6

(Vcc=±2.5V, Rfb=1kΩ, Rload=10Ω)

-8

(Vcc=±6V, Rfb=680

-10

100 1k 10k 100k 1M 10M 100M

gain

phase

(Vcc=±2.5V)

Ω, Rload=25Ω)

Frequency (Hz)

(Vcc=±6V)

(Vcc=±2.5V)

(Vcc=±6V)

40

20

0

-20

-40

-60

-80

-100

-120

Figure 6: Closed Loop Gain vs. Frequency

AV=-2

8

6

4

)

°

Phase (

2

0

-2

(gain (dB))

-4

-6

(Vcc=±2.5V, Rfb=1kΩ, Rin=510Ω, Rload=10Ω)

-8

(Vcc=±6V, Rfb=680

-10

100 1k 10k 100k 1M 10M 100M

gain

phase

(Vcc=±2.5V)

Ω, Rin=750//620Ω, Rload=25Ω)

Frequen c y (Hz)

(Vcc=±2.5V)

(Vcc=±6V)

(Vcc=±6V)

-140

-160

-180

-200

-220

-240

-260

-280

-300

)

°

Phase (

7/27

TS616

Figure 7: Closed Loop Gain vs. Frequency

AV=+4

14

12

10

8

6

4

(gain (dB))

2

0

-2

(Vcc=±2.5V, Rfb=910Ω, Rg=300Ω, Rload=10Ω)

(Vcc=±6V, Rfb=620

-4

100 1k 10k 100k 1M 10M 100M

gain

phase

(Vcc=±2.5V)

(Vcc=±6V)

Ω, R g =560//330Ω, Rload=25Ω)

Frequency (Hz)

(Vcc=±2.5V)

(Vcc=±6V)

Figure 8: Closed Loop Gain vs. Frequency

AV=+8

20

18

16

14

12

10

(gain (dB))

8

6

4

(Vcc=±2.5V, Rfb=680Ω, Rg=240//160Ω, Rload=10Ω)

(Vcc=±6V, Rfb=510

2

100 1k 10k 100k 1M 10M 100M

gain

phase

(Vcc=±2.5V)

(Vcc=±6V)

Ω, Rg=270//100Ω, Rload=25Ω)

Frequency (Hz)

(Vcc=±2.5V)

(Vcc=±6V)

40

20

0

-20

-40

-60

-80

-100

-120

40

20

0

-20

-40

-60

-80

-100

-120

)

°

Phase (

Figure 10: Closed Loop Gain vs. Frequency

AV=-4

14

12

10

8

)

°

Phase (

6

4

(gain (dB))

2

0

(Vcc=±2.5V, Rfb=1kΩ, Rin=320//360Ω, Rload=10Ω)

-2

(Vcc=±6V, Rfb=620

-4

100 1k 10k 100k 1M 10M 100M

gain

phase

(Vcc=±2.5V)

(Vcc=±6V)

Ω, Rin=360//270Ω, Rload=25Ω)

Frequency (Hz)

Figure 11: Closed Loop Gain vs. Frequency

AV=-8

20

18

16

14

12

10

(gain (dB))

8

6

4

(Vcc=±2.5V, Rfb=680Ω, Rin=160//180Ω, Rload=10Ω)

(Vcc=±6V, Rfb=510

2

100 1k 10k 100k 1M 10M 100M

gain

phase

(Vcc= ± 2. 5V)

(Vcc=±6V)

Ω, Rin=150//110Ω, Rload=25Ω)

Frequency (Hz)

(Vcc=±2.5V)

(Vcc=±6V)

(Vcc=±2.5V)

(Vcc= ± 6V )

-140

-160

-180

-200

-220

-240

-260

-280

-300

-140

-160

-180

-200

-220

-240

-260

-280

-300

)

°

Phase (

)

°

Phase (

Figure 9: Bandwidth vs. Temperature

AV=+4, Rfb=910

50

45

40

35

Bw (MHz)

30

25

20

-40-200 20406080

8/27

Ω

Vcc=±6V

Load=25

Vcc=±2.5V

Load=10

Ω

Ω

Temperature (°C)

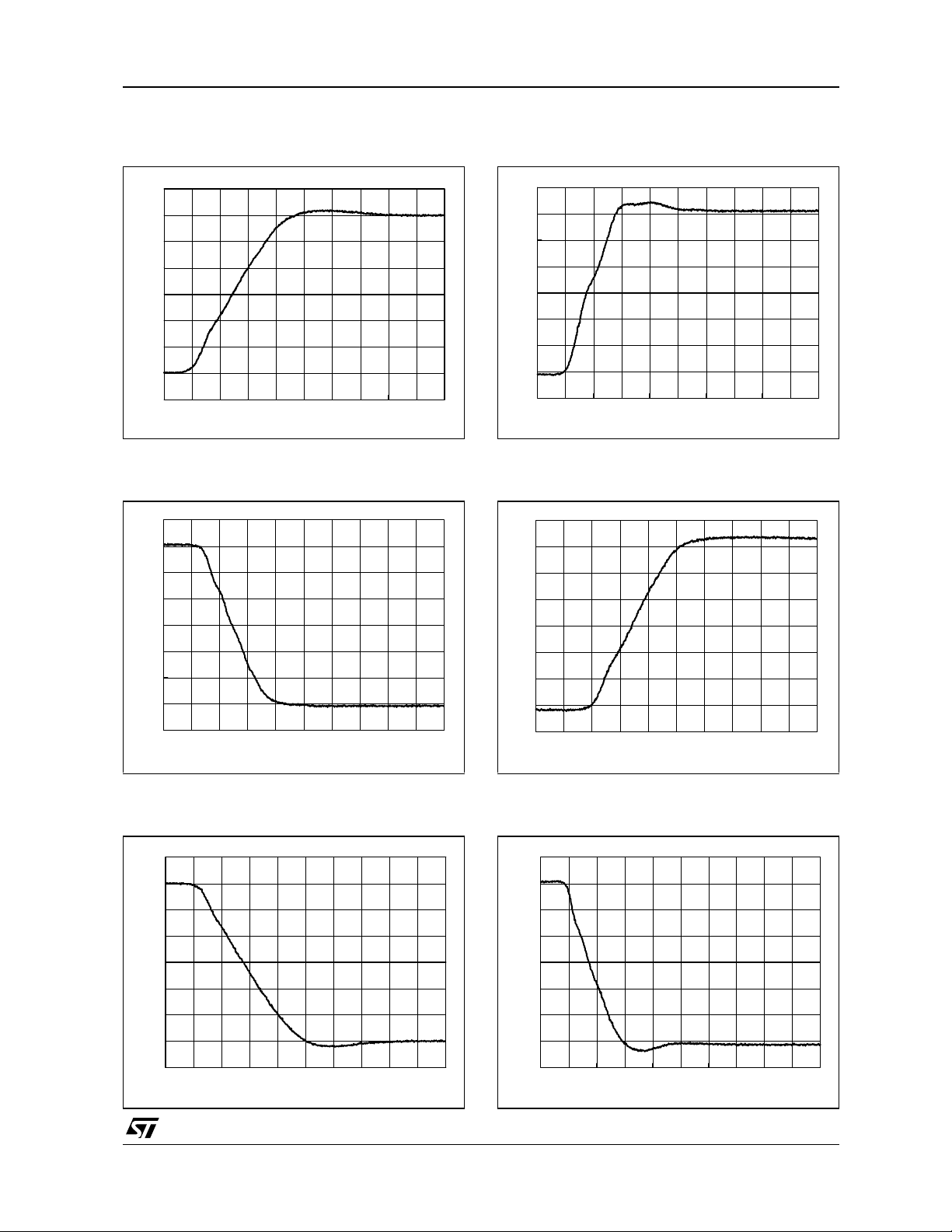

Figure 12: Positive Slew Rate

AV=+4, Rfb=620

4

2

(V)

0

OUT

V

-2

-4

0.0 10.0n 20.0n 30.0n 40.0n 50.0n

, V

Ω

=±6V, RL=25

CC

Time (s)

Ω

TS616

Figure 13: Positive Slew Rate

AV=+4, Rfb=910

2

1

(V)

0

OUT

V

-1

-2

0.0 10.0n 20.0n 30.0n 40.0n 50.0n

, V

Ω

CC

=±2.5V, RL=10

Time (s)

Ω

Figure 14: Negative Slew Rate

AV=+4, Rfb=620Ω, VCC=±6V, RL=25

4

2

Ω

Figure 16: Positive Slew Rate

AV= - 4, Rfb=620

4

2

(V)

0

OUT

V

-2

-4

0.0 10.0n 20.0n 30.0n 40.0n 50.0n

, V

Ω

=±6V, RL=25

CC

Time (s)

Ω

Figure 17: Positive Slew Rate

AV= - 4, Rfb=910

2

1

, V

Ω

CC

=±2.5V, RL=10

Ω

(V)

0

OUT

V

-2

-4

0.0 10.0n 20.0n 30.0n 40.0n 50.0n

Time (s)

Figure 15: Negative Slew Rate

AV=+4, Rfb=910

2

1

(V)

0

OUT

V

-1

-2

0.0 10.0n 20.0n 30.0n 40.0n 50.0n

, V

Ω

CC

=±2.5V, RL=10

Time (s)

Ω

(V)

0

OUT

V

-1

-2

0.0 10.0n 20.0n 30.0n 40.0n 50.0n

Time (s)

Figure 18: Negative Slew Rate

AV= - 4, Rfb=620Ω, VCC=±6V, RL=25

4

2

(V)

0

OUT

V

-2

-4

0.0 10.0n 20.0n 30.0n 40.0n 50.0n

Time (s)

Ω

9/27

TS616

Figure 19: Negative Slew Rate

AV= - 4, Rfb=910

2

(V)

0

OUT

V

-2

0.0 10.0n 20.0n 30.0n 40.0n 50.0n

, V

Ω

CC

=±2.5V, RL=10

Time (s)

Ω

Figure 20: Slew Rate vs. Temperature

AV=+4, Rfb=910

200

150

100

s)

µ

50

0

-50

Slew Rate (V/

-100

-150

-200

-40-200 20406080

, V

Ω

Positive SR

Negative SR

=±2.5V, RL=10

CC

Temperature (°C)

Ω

Figure 22: Input Voltage Noise Level

AV=+92, Rfb=910Ω, Input+ connected to Gnd via 10

5.0

+ 6V

+ 6V

+ 6V

+ 6V

+

+

+

+

Output

Output

Output

4.5

Hz)

√

4.0

3.5

3.0

Input Voltage Noise (nV/

2.5

2.0

100 1k 10k 100k 1M

10

10

10

10

(Frequency (Hz)

Output

_

_

_

_

6VΩ-

6VΩ-

- 6V

- 6V

910Ω

910

910Ω

910

Ω

Ω

Ω

Ω

Figure 23: Transimpedance vs. Temperat ure

Open Loop

)

Ω

(M

R

30

25

Vcc=±6V

20

15

OL

10

Vcc=±2.5V

5

0

-40-200 20406080

Temperature (°C)

Ω

Figure 21: Slew Rate vs. Temperature

AV=+4, Rfb=910

600

500

400

300

200

s)

µ

100

0

-100

-200

Slew Rate (V/

-300

-400

-500

-600

-40-200 20406080

10/27

, V

=±6V, RL=25

Ω

CC

Positive&Negative SR

Ω

Rfb=620

Temperature (°C)

Ω

Positive&Negative SR

Ω

Rfb=910

Figure 24: Icc vs. Power Supply

Open loop, no load

30

20

10

0

(mA)

CC

I

-10

-20

-30

0123456789101112

Icc(+)

Icc(-)

VCC (V)

TS616

Figure 25: Iib vs. Power Supply

Open loop, no load

7

IB+

6

5

4

A)

µ

(

B

3

I

IB-

2

1

0

5 6 7 8 9 10 11 12

Vcc (V)

Figure 26: I

Open loop, no load

5

4

3

A)

µ

(

IB(-)

2

I

1

0

ib(-) vs. Temperature

Vcc=±6V

Vcc=±2.5V

-40-200 20406080

Temper ature (°C)

Figure 28: I

ib(+) vs. Temperature

Open loop, no load

8

7

6

5

4

A)

µ

(

3

IB(+)

I

2

1

0

-1

-40-200 20406080

Figure 29: V

Open loop, RL=25

6

5

4

3

2

(V)

1

OL

0

& V

-1

OH

V

-2

-3

-4

-5

-6

56789101112

Vcc=±6V

Vcc=±2.5V

Temperature (° C)

oh & Vol vs. Power Supply

Ω

VOH

VOL

Vcc (V)

Figure 27: I

cc vs. Temperature

Open loop, no load

14

12

10

Icc(+) for Vcc=±2.5V

8

Icc(+) for Vcc=±6V

6

4

2

0

(mA)

-2

CC

I

-4

-6

Icc(-) for Vcc=±6V

-8

-10

-12

-14

Icc(-) for Vcc=±2.5V

-40-200 20406080

Tem perature ( °C)

Figure 30: V

oh vs. Temperature

Open loop

6

5

4

3

(V)

OH

V

2

1

0

-40-200 20406080

Vcc=±6vV

Ω

Load=25

Vcc=±2.5V

Ω

Load=10

Temperature (°C)

11/27

TS616

Figure 31: Vol vs. Temperature

Open loop

0

Vcc=±2.5V

Load=10

-1

-2

-3

(V)

OL

V

-4

-5

-6

-40-200 20406080

Figure 32: Differential V

Open loop, no load

450

400

350

V)

µ

(

IO

V

∆

300

250

200

-40-200 20406080

Ω

Vcc=±6V

Load=25

Ω

Temperature (°C)

Vcc=±6V

Temperature (°C)

io vs. Temperature

Vcc=±2.5V

Figure 34: CMR vs. Temperature

Open loop, no load

70

68

66

64

62

60

58

CMR (dB)

56

54

52

50

-40-200 20406080

Vcc=±2.5V

Temperature (°C)

Vcc=±6V

Figure 35: SVR vs . Temperature

Open loop, no load

84

82

80

SVR (dB)

78

76

Vcc=±2.5V

-40-200 20406080

Vcc=±6V

Temperature (°C)

Figure 33: V

io vs. Temperature

Open loop, no load

2.0

Vcc=±6V

1.5

1.0

(mV)

IO

V

0.5

0.0

Vcc=±2.5V

-0.5

-40-20 0 20406080

Temperature (°C)

12/27

Figure 36: Iout vs. Temperature

Open loop, VCC=±6V, RL=10Ω

300

250

200

150

100

Isource

50

0

-50

-100

-150

Iout (mA)

-200

-250

-300

-350

-400

-450

Isink

-40-200 20406080

Temperature (°C)

TS616

Figure 37: Iout vs. Temperature

Open loop, VCC=±2.5V, RL=25Ω

300

250

200

150

100

50

Isource

0

-50

-100

-150

Iout (mA)

-200

-250

-300

-350

-400

-450

Isink

-40-200 20406080

Temperature (°C)

Figure 38: Maximum Output Amplitude vs. Load

AV=+4, Rfb=620Ω, VCC=±6V

12

Vcc=±6V

10

Figure 40: Isource vs. Output Amplitude.

VCC=±2.5V, Open Loop, no Load

700

600

500

400

300

Isource (mA)

200

100

0

0.0 0.5 1.0 1.5 2.0 2.5

Vout (V )

Figure 41: Isink vs. Output Amplitude

VCC=±6V, Open Loop, no Load

0

-100

)

8

P-P

(V

6

OUT-MAX

V

4

2

0

0 50 100 150 200

R

(Ω)

LOAD

Figure 39: Isink vs. Output Amplitude.

VCC=±2.5V, Open Loop, no Load

0

-100

-200

-300

-400

Isink (mA)

-500

Vcc=±2.5V

-200

-300

-400

Isink (mA)

-500

-600

-700

-6 -5 -4 -3 -2 -1 0

Vout (V)

Figure 42: Isource vs. Output Amplitude

VCC=±6V, Open Loop, no Load

700

600

500

400

300

Isource (mA)

200

-600

-700

-2.5 -2.0 -1.5 -1.0 -0.5 0.0

Vout (V)

100

0

0123456

Vout (V)

13/27

TS616

Figure 43: Group Delay

VCC=±6V, VCC=±2.5V

100

90

80

70

60

50

Delay (ns)

40

30

20

10

300k

1M 10M

Frequency (Hz)

Av=4

Vcc=±6V, Rfb=620Ω, Load= 25Ω

Vcc=±2.5V, Rfb=910Ω, Loa d= 10Ω

IF Bw = 10Hz

Smoothing=19.247MHz

on 10ns/div scale

50M

SAFE OPERATING AREA

Figure 44: Safe Operating Area

100

700

90

Vcc=+/-6V

Ta=25°C

600

80

G=12dB

RL=100Ω

70

500

)

RMS

60

400

(mV

50

Delay (ns)

300

INPUT

V

40

200

30

100

20

10

0

300k

1M 10M 100M

1M 10M

Av=4

Vcc=±6V, Rf b=62 0Ω, Load=25Ω

Vcc=±2.5 V, R f b=91 0Ω, Load = 10Ω

IF Bw = 10Hz

Smoothing=19.247MHz

on 10ns/div scale

SAFE

OPERATING

AREA

Frequency (Hz)

Frequency (Hz)

50M

Figure 44 shows the safe operating condition. This

curve shows the input level vs. the i nput frequen-

cy. It’s necessary to consider this characteristic to

guarantee the design . In the dash-lined zone, the

consumption increases . Moreover, this increas ed

consumption could do dam age to the chip if the

temperature increases.

14/27

TS616

INTERMODULATION DISTORTION PRODUCT

Non-ideal output of the amplifier can be described

by the following series:

Vout C0C1VinC2V

++ +=

2

in

…

CnV

n

in

due to non-li nearity in the input-output am plitude

transfer, where the input is V

DC component, C

) is the fundamental and C

1(Vin

=Asinωt, C0 is the

in

is the amplitude of the harmonics of the output sig-

out

.

nal V

A one-frequency (one-tone) input signal contrib-

utes to harmonic distortion. A two-tone input signal contributes to harmonic distortion and intermodulation product.

The study of the intermodulation/distortionfor a

two-tone input signal is the first step in characterizing the driving capability of multi-tone input signals.

In this case :

C

+A

()

2

C

A

+

…

()

n

VinA

V

outC0C1

+=

tsin B

ω

1

tsin B

ω

1

tsin B

ω

1

A

ω

()

1

2

tsin+

ω

2

n

tsin+

ω

2

tsin+=

ω

2

tsin B

tsin+

ω

2

and :

C+

A

()

1

C

2

2

–

2+C2AB

cos t B

------- A

2

()

3

C

A

+

3

tsin B

ω

1

2

ω

1

–

ω1ω

()

+

t

2

C

3

3

------4

3

tsin B33

ω

1

tsin+

ω

2

2

cos– tcos

tcos+

2

ω

2

–

ω

()

1

tsin+

ω

2

ω

2

In this expression, we recognize the second order

intermodulation IM2 by the frequencies (ω

and (ω

IM3 by the frequencies (2ω

+2ω2) and (ω1+2ω2).

(−ω

1

) and the third order intermodulation

1+ω2

1-ω2

The measurement of the intermodulation product

of the driver is achieved by using the driver as a

n

mixer by a summing amplifier configuration. In this

way, the non-linearity probl em of an ex ternal m ixing device is avoided.

Figure 45: Non-inverting Summing Amplifier for

Intermodulation measurem ents

1kΩ

1kΩ

1kΩ

1kΩ

49.9Ω

Vin1

Vin1

1:√2

1:√2

50Ω 100Ω

50Ω 100Ω

49.9Ω

Vin1

Vin1

1:√2

1:√2

50Ω 100Ω

50Ω 100Ω

49.9Ω

49.9Ω

49.9Ω

49.9Ω

49.9Ω

49.9Ω

1kΩ

1kΩ

+

+

1/2TS616

1/2TS616

_

_

910Ω

910Ω

300Ω

300Ω

300Ω

300Ω

910Ω

910Ω

_

_

1/2TS616

1/2TS616

1kΩ

1kΩ

+

+

+Vcc

+Vcc

-Vcc

-Vcc

Vout diff.

Vout diff.

49.9Ω

49.9Ω

Rout1

Rout1

Rout2

Rout2

49.9Ω

49.9Ω

The following graphs show the IM2 and the IM3 of

the amplifier in different configurations. The

two-tone input signal was generat ed by the multisource generator Marconi 2026. Each tone has

the same amplitude. The measurement was performed using a HP3585A spectrum analyzer.

1-ω2

), (2ω1+ω2),

√2:1

√2:1

50Ω

100Ω

100Ω

50Ω

)

3C3A2B

----------------------- -+2

3C3A2B

----------------------- -+

3

A

ω

ω

()

2

2

V

outC0C2

3

tsin B

1

1

–

ω

()

1

C

+

…

+=

t2A2B

ω

2

1

–

tsin

-- -– 2

ω

2

2

1

–

2ω+

tsin

-- 2

2

n

V

()

n

in

A2B2+

---------------------

2

ω

+

ω1ω

()

ω

()

1

tsin 2AB

1

tsin

2

2ω+

tsin

2

2

tsin++sin+

ω

2

15/27

TS616

Figure 46: Intermodulation vs. Output Amplitude

370kHz & 400kHz, AV=+1.5, Rfb=1kΩ, RL=14Ω diff.,VCC=±2.5V

IM2

30kHz

IM3

1140kHz, 1170kHz

-30

-40

-50

-60

IM3

-70

340kHz, 430kHz

-80

IM2 and IM3 (dBc)

-90

-100

012345678

IM2

770kHz

Differential Output Voltage (Vp-p)

Figure 47: Intermodulation vs. Output Amplitude

370kHz & 400kHz, AV=+1.5, Rfb=1kΩ, RL=28Ω diff.,VCC=±2.5V

IM2

30kHz

IM2

770kHz

IM3

1140kHz, 1170kHz

-30

-40

-50

-60

IM3

340kHz, 430kHz

-70

-80

IM2 and IM3 (dBc)

-90

-100

012345678

Differential Output Voltage (Vp-p)

Figure 49: Intermodulation vs. Load

370kHz & 400kHz, AV=+1.5, Rfb=1kΩ, Vout=6.5Vpp, VCC=±2.5V

-30

-40

-50

-60

-70

-80

IM2 and IM3 (dBc)

-90

-100

-110

0 20 40 60 80 100 120 140 160 180 200

IM3

340kHz, 430kHz, 1140kHz, 1170kHz

IM2

30kHz

IM2

770kHz

Differential Load (Ω)

Figure 50: Intermodulation vs. Output Amplitude

100kHz & 110kHz, AV=+4, Rfb=620Ω, RL=200Ω diff.,VCC=±6V

IM3

320kHz

IM2

210kHz

-30

-40

-50

IM3

90kHz, 120kHz

-60

-70

-80

IM2 and IM3 (dBc)

-90

-100

-110

246810121416182022

IM3

310kHz

Differential Output Voltage (Vp-p)

Figure 48: Intermodulation vs. Gain

370kHz & 400kHz, RL=20Ω diff., Vout=6Vpp, VCC=±2.5V

-30

-40

-50

-60

-70

-80

IM2 and IM3 (dBc)

-90

-100

-110

1.0 1.5 2.0 2.5 3.0 3.5 4.0

IM3

340kHz, 430kHz, 1140kHz, 1170kHz

IM2

30kHz

Closed Lo op Gain (Linear)

16/27

IM2

770kHz

Figure 51: Intermodulation vs. Output Amplitude

100kHz & 110kHz, AV=+4, Rfb=620Ω, RL=50Ω diff., VCC=±6V

-30

-40

-50

-60

-70

-80

IM2 and IM3 (dBc)

-90

-100

-110

2 4 6 8 10121416182022

IM3

90kHz, 120kHz, 310kHz, 320kHz

Differential Output Voltage (Vp -p)

IM2

210kHz

TS616

Figure 52: Intermodulation vs. Frequency Range

AV=+4, Rfb=620Ω, RL=50Ω diff., Vout=16Vp p, VCC=±6V

f1=400kHz

f2=430kHz

f1=1MHz

f2=1.1MHz

1.1M

-60

Quadratic Summation of all IM2 and IM3 components

generated by each two-tones signal

-65

-70

f1=100kHz

-75

f2=110kHz

(dB)

-80

-85

-90

-95

-100

f1=200kHz

f2=230kHz

100k 200k 300k 400k 500k 600k 700k 800k 900k 1M 1M

Frequency (Hz)

Figure 53: Intermodulation vs. Output Amplitude

370kHz & 400kHz, AV=+4, Rfb=620Ω, RL=200Ω diff.,VCC=±6V

-30

-40

-50

-60

-70

IM3

-80

340kHz, 430kHz

IM2 and IM3 (dBc)

-90

IM3

1140kHz, 1170kHz

IM2

770kHz

IM2

30kHz

Figure 54: Intermodulation vs. Output Amplitude

370kHz & 400kHz, AV=+4, Rfb=620Ω, RL=50Ω diff., VCC=±6V

-30

-40

-50

-60

-70

-80

IM2 and IM3 (dBc)

-90

-100

-110

0246810121416182022

IM3

340kHz, 430kHz

Differential Output Voltage (Vp-p)

IM3

1140kHz, 1170kHz

IM2

30kHz

IM2

770kHz

-100

-110

0246810121416182022

Differential Output Voltage (Vp-p)

17/27

TS616

PRINTED CIRCUIT BOARD LAYOUT

CONSIDERATIONS

In the ADSL frequency range, printed circuit board

parasites can affect the closed-loop performance.

The implementation of a proper ground plane on

both sides of the PCB is mandatory to provide low

inductance and low resistance common return.

The most imp ortant factors affecting gai n f latness

and bandwidth are stray capa citances at the output and inverting input. To minimize these capacitances, the space between signal lines and

ground plane should be increased. Feedback

components connections must be as short as possible in order to decrease the associated inductance which affects high frequency gain errors. It

is very important to c hoose the smallest pos sible

external components, for example, surface

mounted devices (SMD) in order to minimize the

size of all DC and AC connections.

THERMAL INFORMATION

The TS616 is housed in an Exposed-Pad plastic

package. As depicted in figure 55, this package

uses a lead frame upon which the die is mounted.

This lead frame is exposed as a thermal pa d on

the underside of the package. The thermal contact

is direct with the dice. This thermal path provides

excellent colling.

Figure 55: Exposed-Pad Package

DICE

DICE

Bottom View

Side View

Side View

Bottom View

DICE

DICE

Cross Section View

Cross Section View

Figure 56: Evaluation Board

1

1

The thermal pad is electrically isolated from all

pins in the package. It should be soldered to a

copper area o f th e PC B underneath the package.

Through these thermal paths within this copper area, heat can b e conducted away from the pack age. In this case, the copp er area should be connected to (-

V

).

CC

18/27

Figure 57: Schematic Diagram

J205

J205

J205

J206

J206

J206

J207

J207

J207

J208

J208

J208

J209

J209

J209

R206

R206

R206

3

3

R207

R207

R207

R202 R201

R202 R201

R202 R201

R203

R203

R203

R208

R208

R208

R209

R209

R209

R204

R204

R204

R210

R210

R210

R205

R205

R205

3

+

+

+

1/2TS616

1/2TS616

1/2TS616

_

_

_

1

1

1

2

2

2

R214

R214

R214

R211

R211

R211

R212

R212

R212

R215

R215

R215

6

6

6

_

_

_

1/2TS616

1/2TS616

1/2TS616

7

7

7

+

+

+

5

5

5

R213

R213

R213

TS616

Non-Inverting

Non-Inver ti ng

3

R207

J206

R218

R218

R218

R216

R216

R216

R219

R219

R219

R217

R217

R217

J210

J210

J210

R220

R220

R220

J211

J211

J211

R221

R221

R221

J206

Inverting

Inverting

J208

J208

Summing Am plifier

Summing Am plifier

R207

R202

R202

R209

R209

R204

R204

3

+

+

1/2TS616

1/2TS616

_

_

1

1

2

2

R214

R214

R211

R211

R215

R215

_

_

6

6

1/2TS616

1/2TS616

7

7

+

+

5

5

R213

R213

R218

R218

R216

R216

R219

R219

R217

R217

J210

J210

R220

R220

J211

J211

R221

R221

Differential Amplifier

Differential Amplifier

Differential Amplifier

J206

J206

J206

R202

R202

R202

J209

J209

J209

R205

R205

R205

R207

R207

R207

R210

R210

R210

J205

J205

J206

J206

3

3

3

+

+

+

1/2TS616

1/2TS616

1/2TS616

_

_

_

1

1

1

2

2

2

R214

R214

R214

R211

R211

R211

R212

R212

R212

R215

R215

R215

6

6

6

_

_

_

1/2TS616

1/2TS616

1/2TS616

7

7

7

+

+

+

5

5

5

R213

R213

R213

R218

R218

R218

R216

R216

R216

R219

R219

R219

R217

R217

R217

J210

J210

J210

R220

R220

R220

Power Supply

Power Supply

Power Supply

J211

J211

J211

R221

R221

R221

J201

J201

J201

J201

+Vcc

+Vcc

+Vcc

+Vcc

J202

J202

J202

J202

GND

GND

GND

GND

J303

J303

J303

J303

-Vcc

-Vcc

-Vcc

-Vcc

J20412

J20412

J20412

J20412

R206

R206

3

R207

R207

R202 R201

R202 R201

C202

C202

C202

C202

100nF

100nF

100nF

100nF

C203

C203

C203

C203

C203

100nF

100nF

100nF

100nF

100nF

3

3

3

3

3

+

+

1/2TS616

1/2TS616

_

_

1

1

2

2

R214

R214

R211

R211

+Vcc

+Vcc

+Vcc

+Vcc

C205

C205

C205

C205

+Vcc

+Vcc

+Vcc

+Vcc

100nF

100nF

100nF

C201

C201

C201

C201

100uF

100uF

100uF

100uF

C204

C204

C204

C204

100uF

100uF

100uF

100uF

+Vcc

+Vcc

+Vcc

+Vcc

-Vcc

-Vcc

-Vcc

-Vcc

100nF

8

8

8

8

3

3

3

3

+

+

+

+

1/2TS616

1/2TS616

1/2TS616

1/2TS616

_

_

_

_

2

2

2

2

4

4

4

4

C206

C206

C206

C206

100nF

100nF

100nF

100nF

-Vcc

-Vcc

-Vcc

-Vcc

-Vcc

-Vcc

-Vcc

-Vcc

_

_

_

_

6

6

6

6

1/2TS616

1/2TS616

1/2TS616

1/2TS616

+

+

+

+

5

5

5

5

R218

R218

R216

R216

1

1

1

1

-Vcc

-Vcc

-Vcc

-Vcc-Vcc

Exposed-Pad

Exposed-Pad

Exposed-Pad

Exposed-Pad

7

7

7

7

J210

J210

R220

R220

19/27

TS616

Figure 58: Component Locations - Top Side

Figure 59: Component Locations - Bottom Side

Figure 60: Top Side Board Layout

Figure 61: Bottom Side Board Layout

20/27

TS616

g

NOISE MEASUREMENT

Figure 62: Noise Model

+

eN

eN

+

TS616

TS616

_

_

R2

R2

iN+

N3

N3

iN+

iN-

iN-

N2

N2

R1

R1

N1

N1

R3

R3

output

output

HP3577

HP3577

Input noise:

Input noise:

8nV/√Hz

8nV/√Hz

eN : input voltage noise of the amplifier

iNn : negative input current noise of the amplifier

iNp : positive input current noise of the amplifier

The closed loop gain is :

R

AVg1

The six noise sources are :

=

V1eN

×

fb

--------- -+==

R

2

R

------ -

1

+

1

R

k is the Boltzmann’s constant, equal to

1,374.10-23J/°K. T is the temperature (°K).

The output noise eNo is c alculated using the Su-

perposition Theorem. However it is not the simple

sum of all noi se sources. The squ are root of the

sum of the square of each noise source.

eNo V12V22V32V42V52V6

+++++ eq1

2

,=

()

2

2

=

eNo2eN2g2iNn2R

2

2

R

------ -

+

4

× eq2(),

1

R

+

× R

kTR

14

21

++

kTR

2

+

×

iNp

2

R

-------

+

1

R

× g2×

2

4

kTR

×

2

3

3

The input noise of the instrumentation must be extracted from the measured noise value. Th e real

output noise value of the driver is:

eNo Measured

()

2

instrumentation

– eq3

()

2

,=

()

The input noise is called the Equivalent Input

Noise as it is not directly measured but it is evaluated from the meas urement of the output divided

by the closed loop gain (eNo/g).

After simplification of the fourth and the fifth term

of (eq2) we obtain:

2

2

=

eNo2eN2g2iNn2R

+

… g4kTR

× eq4(),

+

× R

21

×

2

R

------ -

+

+

1

R

2

+

iNp

2

4

kTR

×

3

× g2×

3

2

2

=

V

iNn R2×

2

R

-------

+

××

1

R

4

1

kTR

2=

kTR

4

3=

kTR

=

V3iNp R

2

R

------ -

4

–=

V

61

V

1

R

54

V

+

31

×

2

R

------ -

1

R

We assume that the thermal noise of a resistance

R is:

4kTR∆F

wher ∆F is the specified bandwidth.

On 1Hz bandwidth the thermal noise is reduced to

4kTR

Measurement of eN:

We assume a short-circuit on the non-inverting input (R3=0). (eq4) comes:

=

eNo eN2g2iNn2R

+

× eq5(),

×

2

+

g4kTR

2

×

2

In order to easily extract the value of eN, the resistance R2 will be chosen as low as possible. In the

other hand, the gain must be large enough.

R1=10Ω, R2=910Ω, R3=0, Gai n=92

Equivalent Input Noise: 2.57nV/√Hz

Input Voltage Noise: eN=2.5nV/√Hz

Measurement of iNn:

R3=0 and the output noise equation is still the

(eq5). This time the gain must be decreased to decrease the thermal noise contribution.

R1=100Ω, R2=910Ω, R3=0, Gain=10.1

Equivalent Input Noise: 3.40nV/√Hz

Negative Input Current Noise: iNn =21pA/√Hz

Measurement of iNp:

To extract iNp from (eq3), a resist ance R3 is connected to the non-inverting input. The val ue of R3

must be chose n in o rder to keep i ts therm al noise

21/27

TS616

+

-VCC

+VCC

10µF

+

10nF

TS616

10µF

+

10nF

-

+

-VCC

+VCC

10µF

+

10nF

TS616

10µF

+

10nF

-

contribution as low as possible against the iNp

contribution.

R1=100Ω, R2=910Ω, R3=100Ω, Gain=10.1

Equivalent Input Noise: 3.93nV/√Hz

Positive Input Current Noise: iNp=15pA/√Hz

Condit i ons: frequency=100kHz, V

Instrumentation: Spectrum Analyz er HP3585A

(input noi se of the HP3585A: 8nV/√Hz)

CC

=±2.5V

POWER SUPPLY BYPASSIN G

Correct power supply by pa ssing is very important

for optimizing the performance in high frequency

ranges. Bypass capacitors should be placed as

close as pos sible to the IC pins t o improve high

frequency bypassing. A capacitor greater than

1µF is necessary to minim ize the distortion. For a

better quality bypassing a capac itor of 10nF can

be added usin g the same implementation con ditions. Bypass capacit ors mu st be incorporat ed f or

both the negative and the positive supply.

Figure 63: Circuit for Power Supply Bypassing

The following figure shows the case of a 5V single

power suppl y configuration

Figure 64: Circuit for +5V single supply

+5V

+5V

10µF

10µF

+

IN

IN

+5V

+5V

R1

R1

820Ω

820Ω

R2

R2

820Ω

820Ω

Rin

Rin

1kΩ

1kΩ

+ 1µF

+ 1µF

10nF

10nF

+

½ TS616

½ TS616

_

_

fb

fb

R

R

R

G

G

+

+

CG

CG

R

The TS616 operates with power supplies from

12V down to 5V. This can be achieved by either a

dual power sup plies of ±6V or ±2.5V or a single

power supply of 12V or 5V referenced to the

ground. In the case of asymmetrical supply, a new

biasing is necessary to assume a positive output

dynamic range between 0V and +V

Considering the values of V

OH and VOL, the ampli-

fier will provide an output dynamic from +0.5V to

10.6V on 25Ω load for a 12V supply and from

0.45V to 3.8V on 10Ω load for a 5V supply.

100µF

100µF

OUT

OUT

supply rails.

CC

10Ω

10Ω

SINGLE POWER SUPPLY

22/27

The amplifier must be biased with a mid-supply

(nominally +V

/2), in order to maintain the DC

CC

component of the signa l at this val ue. Several options are possible to provide this bias supply, such

as a virtual ground using an o perational amplifier

or a two-resistance di vider (whi ch is the cheapest

solution). A high resistance value is required to

limit the current cons umption. O n the other hand,

the current must be high enough to bias the

non-inverting input of t he am plifier. If we consider

TS616

this bias current (30µA max.) as the 1% of the current through the resist ance divider to keep a stable mid-supply, two resistances of 2.2kΩ can be

used in the case of a 12V power supply and two

resistances of 820Ω can be u sed in the case of a

5V power supply.

The input provides a high pass filter with a break

frequency below 10Hz which is necessary to remove the original 0 volt DC component of the input

signal, and to fix it at +V

CC

/2.

CHANNEL SEPARATION - CROSSTALK

The following figure shows the crosstalk from an

amplifier to a second amplifier. This phenomenon,

accentuated at high frequencies, is unavoidable

and intrinsic to the circuit.

Nevertheless, the PCB layout also has an effect

on the crosstalk level. Capacitive coupling between signal wires, distance between critical signal nodes and power supply bypassing are the

most significant fact o rs.

Figure 65: Crosstalk vs. Frequency

AV=+4, Rfb=620Ω, VCC=±6V, Vout=2Vp

-50

-60

-70

-80

-90

-100

CrossTal k (dB)

-110

-120

-130

10k 100k 1M 10M

Frequency (Hz)

CHOICE OF THE FEEDBACK CIRCUIT

Table 1: Closed-Loop Gain - Feedback Compo-

nents

V

CC

±6

±2.5

(V)

Gain

+1 750

+2 680

+4 620

+8 510

-1 680

-2 680

-4 620

-8 510

+1 1.1k

+2 1k

+4 910

+8 680

-1 1k

-2 1k

-4 910

-8 680

Rfb (Ω)

INVERTING AMPLIFIER BIASING

In this case a resistance R is necessary to achieve

good input biasing, see Figure 66.

This resistance is calculated by assuming the negative and positive input bias current. The aim is to

compensate for the offset bias current which could

affect the input offset voltage and the output DC

component. Assuming Ib-, Ib+, R

volt output, the resistance R comes: R = R

in, Rfb and a zero

in // Rfb .

Figure 66: Compensation of the Input Bias

Current

fb

fb

R

R

Ib-

Ib-

Rin

Rin

Ib+

Ib+

_

_

+

+

TS616

TS616

Vcc+

Vcc+

Vcc-

Vcc-

Output

Output

Load

Load

R

R

23/27

TS616

ACTIVE FI LT ER I N G

Figure 67 : Low-Pass Active Filtering. Sallen-Key

C1

C1

R

R

1 R2

1 R2

IN

IN

The resistors R

fb and RG give the gain of the f ilter

+

+

C2

C2

TS616

TS616

_

_

R

R

fb

fb

910Ω

RG

RG

910Ω

OUT

OUT

25Ω

25Ω

as a classical non-inverting am plification configuration :

R

AVg1

fb

--------- -+==

R

g

Assume the following expression i s the response

of the system:

preferable to use very stabl e resisto rs and c apacitances values.

In the case of R1=R2:

R

2C2C

------------------------------------=

ζ

2C1C

fb

--------- -–

1

R

g

2

INCREASING THE LINE LEVEL BY USING AN

ACTIVE IMPEDANCE MATCHING

With passive matching, the output signal amplitude of the driver must be twice the amplitude on

the load. To go beyond this limitation, active

matching impedance can be used. W ith this t echnique, it is possible to keep good impedance

matching with an amplitude on the load higher

than half of the output driver amplitude. This c oncept is shown in Figure 68 for a differential line.

Figure 68: TS616 as a differential line driver with

an active impedance matching

Vout

T

j

ω

------------------Vin

j

j

ω

ω

---------------------------------------------==

12

------ -

ζ

ω

g

j

ω

c

j

ω()

------------- -++

2

ω

c

2

the cut-off frequency is not gai n-dependent a nd it

becomes:

1

------------------------------------- -=

ω

c

R1R2C1C2

The damping factor becomes:

1

-- -

=

ζ

ω

()

cC1R1C1R2C2R1C1R1

2

g–++

The higher the gain, the more sensitive the damping factor is. When the gain is higher than 1 it is

100n

Vcc+

1k

Vi

100n

100n

10µ

1k

GND

Vi Vo

1/2 R1

1/2 R1

+

_

+

_

Vcc/2

Vcc+

Rs1

GND

R2

R3

R5

R4

Vcc+

GND

Vo°

Vo°

Rs2

µ

1

10n

Vo

1:n

Hybrid

&

RL

Transformer

100Ω

24/27

TS616

Component Calculation

Let us consider the equivalent circuit for a single-ended configuration as shown in Figure 69.

Figure 69: Single ended equivalent circuit

+

+

+

Vi

Vi

½ R1

½ R1

+

_

_

_

_

R2

R2

R3

R3

Vo°

Vo°

Rs1

Rs1

-1

-1

-1

-1

Vo

Vo

½ RL

½ RL

Let us consider the unloaded system . Assumi ng

the currents through R1, R2 and R3

are respect ively:

2Vi

Vi Vo°–

()

---------

---------------------------and

R1

° equals Vo without load, the gain in this

as Vo

R2

Vi Vo+

()

------------------------,

R3

case becomes :

2R2

----------R1

R2

–

1

------- R3

R2

------- -++

R3

G

Vo noload

()

--------------------------------Vi

1

------------------------------------==

2R2

----------R1

R2

------- -–

R3

R2

------- -++

R3

Rs1Iout

----------------------- e q 3

1

R2

------- -–

R3

,–=

()

Vi 1

Vo

------------------------------------------------

1

By identification of both equations (eq2) and

(eq3), the synthesized impedance is, with

Rs1=Rs2=Rs:

Ro

Rs

----------------- e q 4

,=

()

R2

1

------- -–

R3

Figure 70: Equivalent schematic. Ro is the

synthesized impedance .

Iout

1/2RL

° required for a passive imped-

Vi.Gi

Unlike the level Vo

ance, Vo

us write Vo

° will be smaller than 2Vo in our case. Let

°=kVo with k the m at ching f actor vary -

Ro

ing between 1 and 2. Assum ing that the current

through R3 is negligible, (eq4) becomes the following :

Ro

kVoRL

----------------------------- -=

RL 2R s1+

The gain, for the loaded system will be (eq1):

2R2

----------R1

R2

1

------- -–

R3

R2

------- -++

R3

,==

()

GL

Vo withload

()

-------------------------------------Vi

1

1

-- -

------------------------------------ e q 1

2

As shown in Figure70, this system is an ideal generator with a synthesized impedance as the internal impedance of the system. From this, the output voltage becomes:

Vo ViG

()

RoIout

–= eq2

()

,

()

with Ro the synthesized impedance and Iout the

output current. On the other hand Vo can be expressed as:

After choosing the k factor, Rs will equal to

1/2RL(k-1).

A good impedance matching assume s:

1

Ro

-- -RL eq5

,=

()

2

(eq4) and (eq5) give :

R2

------- -1

R3

2Rs

----------- e q 6

,–=

()

RL

By fixing an arbitrary value of R2, (eq6) becomes :

R3

R2

-------------------- -=

2Rs

1

-----------–

RL

Finally, the values of R2 and R3 allow us to extract

R1 from (eq1), and it becomes:

25/27

TS616

R1

----------------------------------------------------------- e q 7

21

2R2

R2

------- -–

R3

GL 1–

,=

()

R2

------- -–

R3

with GL the required gain.

Table 2 : Components Calculation for Impedance

Matching Implementa tion

GL (gain for the

loaded system)

R1 2R2/[2(1-R2/R3)GL-1-R2/R3]

R2 (=R4) Abritra ry fixed

R3 (=R5) R2/(1-Rs/0.5RL)

Rs 0.5RL(k-1)

Load view ed by

each driv er

GL is fixed for the application requirements

GL=Vo/Vi=0.5(1+2R2/R1+R2/R3)/(1-R2/R3)

kRL/2

26/27

PACKAGE MECHANICAL DATA

8 PINS - PLASTIC MICROPACKAGE (SO Exposed-Pad)

TS616

Dim.

Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 1.350 1.750 0.053 0.069

A1 0.000 0.250 0.001 0.010

A2 1.100 1.650 0.043 0.065

B 0.330 0.510 0.013 0.020

C 0.190 0.250 0.007 0.010

D 4.800 5.000 0.189 0.197

D1 3.10 0.122

E 3.800 4.000 0.150 0.157

E1 2.41 0.095

e 1.270 0.050

H 5.800 6.200 0.228 0.244

h 0.250 0.500 0.010 0.020

L 0.400 1.270 0.016 0.050

k0d 8d0d 8d

ddd 0.100 0.004

Information furnished is bel ieved to be accurate and reliable. However, STMicroe lectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from

its use. No li cense is granted by i mp lica tion or otherwise under a n y patent or patent rig hts of STMicroelectronics. Spec ific at ions

mentioned in this publication ar e subject to change without notice. This publication supersedes and replaces all information

previously supplied. S TMicroelectronics products are not authorized for use as critica l components in life suppo rt devices or

systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

© 2002 STM icroelectronics - Printed in Italy - All Ri g h ts Reserv ed

STMicr o el ectronics G ROU P OF COMPANI E S

Australi a - Brazil - C hi na - Finlan d - F rance - Germ any - Hong Kon g - I ndi a - Italy - Japan - Malaysia - Malta - Morocco

Singapo re - Spain - Sweden - Swi t zerland - United Kingdom

© http://www.st.com

27/27

Loading...

Loading...