TDA9105

DEFLECTIONPROCESSOR FOR MULTISYNC MONITORS

PRELIMINARY DATA

HORIZONTAL

.

DUALPLLCONCEPT

.

150kHz MAXIMUMFREQUENCY

.

SELF-ADAPTATIVE

.

X-RAYPROTECTION INPUT

.

DC ADJUSTABLEDUTY-CYCLE

.

1stPLLLOCK /UNLOCKINFORMATION

.

WIDE RANGE DC CONTROLLED H-POSITION

.

ON/OFF SWITCH (FOR PWR MANAGEMENT)

.

TWOH-DRIVEPOLARITIES

.

MOIRE OUTPUT

VERTICAL

.

VERTICALRAMP GENERATOR

.

50 TO165Hz AGC LOOP

.

DCCONTR OLLED V-AMP,V-POS,S-AMP &C-C OR

.

ON/OFF SWITCH

EWPCC

.

VERTICAL PARABOLA GENERATOR WITH

DC CONTROLLED KEYSTONE & AMPLITUDE

.

AUTOTRACKING WITH V-POS& V-AMP

GEOMETRY

.

WAVE FORM GENERATOR FOR PARALELLOGRAM& SIDE PIN BALANCECONTROL

.

AUTOTRACKING WITH V-POS& V-AMP

DYNAMICFOCUS

.

VERTICALPARABOLAOUTPUTFOR VERTICALDYNAMIC FOCUS

.

AUTOTRACKING WITH V-POS& V-AMP

GENERAL

.

ACCEPT POSITIVE OR NEGATIVE HORIZONTAL& VERTICAL SYNC POLARITIES

.

SEPARATE H & V TTLINPUT

.

COMPOSITEBLANKINGOUTPUT

DESCRIPTION

The TDA9105 is a monolithic integrated circuit

assembled in a 42 pins shrink dual in line plastic

package.

This IC controls all the functions related to the

horizontaland vertical deflectionin multimodesor

multisyncmonitors.

This IC, combined with TDA9205 (RGB preamp),

STV942x(OSDprocessor),ST727x(microcontroller) and TDA817x(vertical booster), allowsto realize very simple and high quality multimodes or

multisyncmonitors.

SHRINK42

(Plastic Package)

ORDER CODE : TDA9105

PIN CONNECTIONS

V-FOCUS

H-LOCKOUT

PLL2C

H-DUTY

H-FLY

H-GND

H-REF

FC2

FC1

C0

R0

PLL1F

H-LOCKCAP

PLL1INHIB

H-POS

XRAY-IN

H-SYNC

V

GND

H-OUTEM

H-OUTCOL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

CC

19

20

21

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

SPINBAL

KEYBAL

GEOMOUT

EWAMP

KEYST

EWOUT

V-FLY

VDCIN

V-SYNC

V-POS

VDCOUT

V-AMP

V-OUT

C-CORR

VS-AMP

V-CAP

V-REF

V-AGCCAP

V-GND

MOIRE

BLK-OUT

9105-01.EPS

June 1996

This is advance informationon anewproduct now in development or undergoingevaluation. Details are subject to change without notice.

1/32

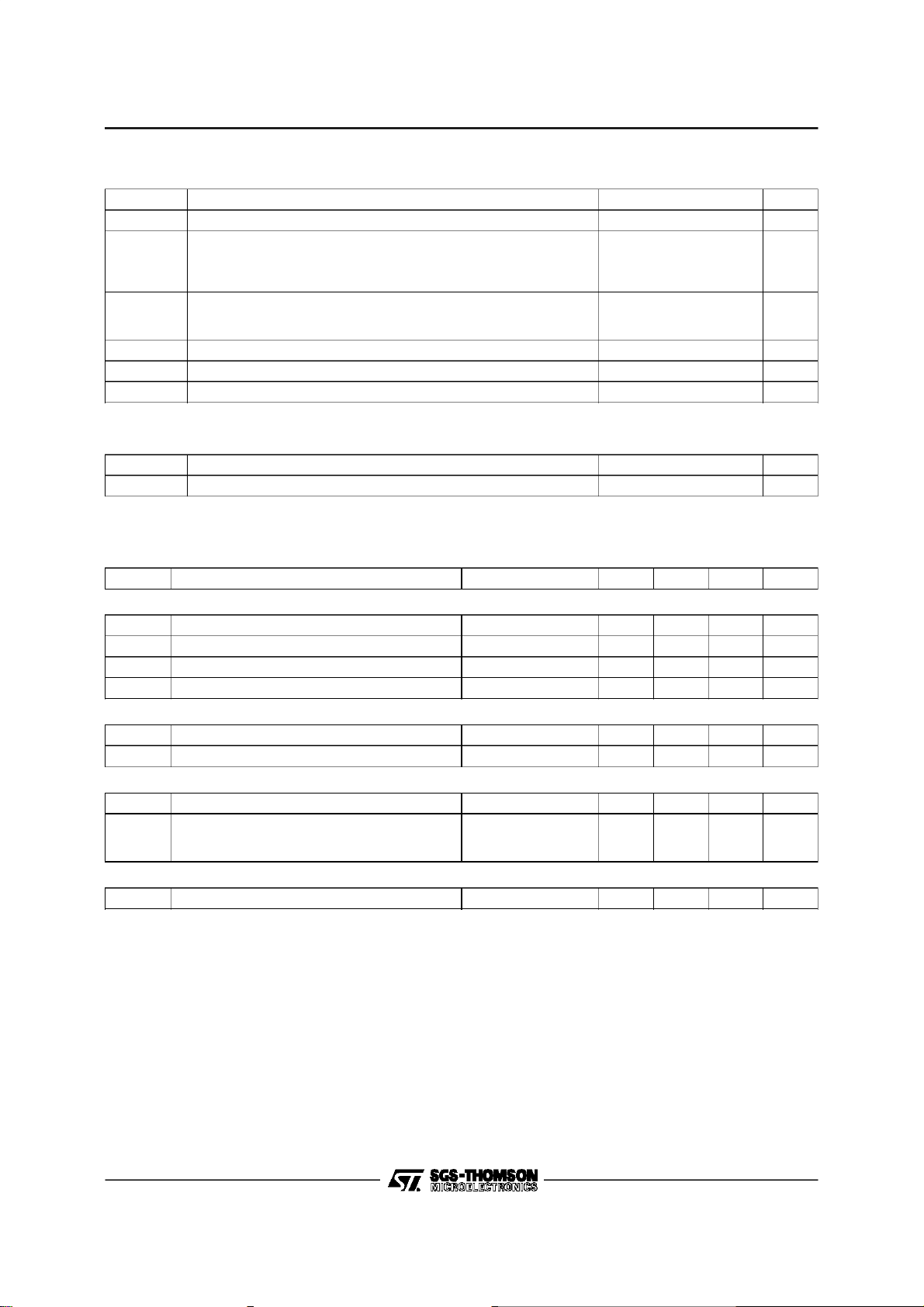

TDA9105

PINDESCRIPTION

Pin Name Function

1 V-FOCUS Vertical Dynamic Focus Output

2 H-LOCKOUT First PLL Lock/UnlockOutput

3 PLL2C Second PLL Loop Filter

4 H-DUTY DC ControlofHorizontalDrive Output PulseDuty-cycle.If thisPinisgrounded, the Horizontal

5 H-FLY Horizontal Flyback Input (positive polarity)

6 H-GND Horizontal Section Ground

7 H-REF Horizontal Section Reference Voltage, must be filtered

8 FC2 VCO Low Threshold Filtering Capacitor

9 FC1 VCO High ThresholdFiltering Capacitor

10 C0 Horizontal OscillatorCapacitor

11 R0 Horizontal OscillatorResistor

12 PLL1F First PLL Loop Filter

13 H-LOCKCAP First PLL Lock/UnlockTime Constant Capacitor. When Frequency ischanging, a Blanking

14 PLL1INHIB TTL-Compatible Inputfor PLL1 Output Current Inhibition

15 H-POS DC Control for HorizontalCentering

16 XRAY-IN X-RAY protectionInput (withinternal latchfunction)

17 H-SYNC TTL compatible Horizontal Sync Input

18 V

CC

19 GND Ground

20 H-OUTEM Horizontal Drive Output (emiter of internal transistor)

21 H-OUTCOL Horizontal Drive Output (open collector of internal transistor)

22 BLKOUT Blanking Output, activated during frequency changes, when X-RAYInput istriggered,when

23 MOIRE Moire Output

24 V-GND Vertical Section SignalGround

25 V-AGCCAP Memory Capacitor forAutomatic Gain Control Loop in Vertical Ramp Generator

26 V-REF Vertical Section ReferenceVoltage

27 V-CAP Vertical Sawtooth GeneratorCapacitor

28 VS-AMP DC Control of VerticalS-Shape Amplitude

29 C-CORR DC Control of VerticalC-Correction

30 V-OUT Vertical Ramp Output (with frequency independantamplitude and S-Correction)

31 V-AMP DC Control of VerticalAmplitude Adjustment

32 VDCOUT Vertical Position ReferenceVoltage Output

33 V-POS DC Control of VerticalPosition Adjustment

34 V-SYNC TTL-Compatible VerticalSync Input

35 VDCIN Geometric CorrectionReference Voltage Input

36 V-FLY Vertical Flyback Input (positive polarity)

37 EWOUT East /WestPincushion Correction Parabola Output

38 KEYST DC Control of KeystoneCorrection

39 EWAMP DC Control East/West PincushionCorrection Amplitude

40 GEOMOUT Side PinBalance & Parallelogram Correction Parabola Output

41 KEYBAL DC Control of ParallelogramCorrection

42 SPINBAL DC Control ofSide Pin Correction Amplitude

and VerticalOutputs are inhibited.By connecting a Capacitor onthis Pin aSoft-start function

may berealized on H-drive Output.

Pulse isgenerated on Pin23, the duration of this Pulse is proportionnel to the Capacitoron

Pin 13.

Supply Voltage(12V Typ.)

VS istoolow, orwhenDevice isin stand-bymode (throughH-DUTY Pin2)and duringH-FLY,

V-FLY, V-SYNC, VSawth retrace.

9105-01.TBL

2/32

BLOCK DIAGRAM

TDA9105

H-OUTEM

H-OUTCOL

H-DUTY

XRAY-IN

H-LOCKOUT

PLL2C

H-FLY

FC1

FC2

R0

C0

PLL1F

H-POS

MOIRE

23

GND18V

19

CC

V-FOCUS

1

KEYST

38

EWOUT

37

EWAMP

39

KEYBAL

41

GEOMOUT

SPINBAL

40

42

MOIRE

VDCIN

V-Sync

H-Sync

20

2

X

35

H

21

4

16

2

3

5

9

8

11

10

12

15

BUFFER

OUTPUT

PULSE

SHAPER

PHASE

SHIFTER

COMP

PHASE

VCO

COMP

PHASE

FREQUENCY

SAFETY

PROCESSOR

VS

VIDEO UNLOCK

LOCK

IDENT

UNLOCK

V-MID

V-REF

BLK

GEN

H-FLY

RAMP

VERT OSC

GENERATOR

S

CORR

V-SYNC

22

36

32

33

30

31

25

27

29

28

BLK-OUT

V-FLY

VDCOUT

V-PO S

V-OUT

V-AMP

VAGCCAP

VCAP

C-CORR

VS-AMP

V-REF

PULSE

SHAPER

POL

DETECT

PLL1

INHIB

PULSE

SHAPER

POL

DETECT

7

H-REF

6

H-GND

17

H-SYNC

14

13

PLL1INHIB

H-LOCKCAP

26

V-REF

24

V-GND

34

V-SYNC

TDA9105

9105-02.EPS

3/32

TDA9105

QUICK REFERENCE DATA

Parameter Value Unit

Horizontal Frequency 15 to 150 kHz

Autosynch Frequency (forGiven R0, C0) 1 to 3.7 FH

± Hor Sync Polarity Input YES

Compatibility with Composite Sync on H-SYNC Input YES (see note 1)

Lock/Unlock Identification on 1

DC Control forH-Position YES

X-RAY Protection YES

Hor DUTY Adjust YES

Stand-by Function YES

Two Polarities H-Drive Outputs YES

SupplyVoltage Monitoring YES

PLL1 Inhibition Input YES

Composite Blanking Output YES

Horizontal Moire Output YES

Vertical Frequency 35 to 200 Hz

Vertical Autosync (for 150nF) 50 to 165 Hz

Vertical S-Correction YES

Vertical C-Correction YES

Vertical Amplitude Adjustment YES

Vertical Position Adjustment YES

East/West Parabola Output YES

PCC (Pin CushionCorrection) Amplitude Adjustment YES

Keystone Adjustment YES

Dynamic Horizontal Phase Control Output YES

Side Pin Balance Amplitude Adjustment YES

Parallelogram Adjustment YES

Tracking of Geometric Corrections with V-AMP and V-POS YES

Reference Voltage YES (see note 2)

Mode Detection NO

Vertical Dynamic Focus YES

Notes : 1. Provided PLL inhibition input is used, see application diagram on page 27.

2. One for Horizontal section and one for Vertical section.

st

PLL YES

9105-02.TBL

4/32

TDA9105

ABSOLUTEMAXIMUM RATINGS

Symbol Parameter Value Unit

V

CC

V

IN

VESD ESD Succeptibility

T

stg

T

T

oper

THERMALDATA

Symbol Parameter Value Unit

R

th (j-a)

HORIZONTAL SECTION

OperatingConditions

Symbol Parameter Test Conditions Min. Typ. Max. Unit

VCO

R0min Oscillator Resistor Min Value (Pin 11) 6 kΩ

C0min Oscillator Capacitor Min Value (Pin 10) 390 pF

Fmax Maximum Oscillator Frequency 150 kHz

HsVR Horizontal Sync InputVoltage (Pin 17) 0 5.5 V

INPUT SECTION

MinD Minimum Input Pulses Duration (Pin 17) 0.7 µS

Mduty Maximum Input Signal Duty Cycle (Pin 17) 25 %

OUTPUT SECTION

I5m Maximum Input Peak Current (Pin 5) 5 mA

HOI1

HOI2

DC CONTROL VOLTAGES

DCadj DC Voltageon DC Controls (Pins 4-15) V

Supply Voltage (Pin18) 13.5 V

Max Voltageon Pins 4, 15, 28, 29, 31, 33, 38, 39,41, 42

Pin 5

Pins 17, 34

Pin 16

Human Body Model, 100pFDischarge through 1.5kΩ

EIAJ Norm, 200pF Dischargethrough 0Ω

8

1.8

6

12

2

300

Storage Temperature -40, +150 °C

Max OperatingJunction Temperature 150 °C

j

Operating Temperature 0, +70 °C

Junction-Ambient Thermal Resistance Max. 65 °C/W

Horizontal Drive Output Max Current

Pin 20

Pin 21

Sourced current

Sink current

=8V 2 6 V

REF-H

20

20

V

kV

V

9105-03.TBL

9105-04.TBL

mA

mA

9105-05.TBL

5/32

TDA9105

HORIZONTAL SECTION (continued)

ElectricalCharacteristics (V

= 12V,T

CC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

SUPPLY AND REFERENCE VOLTAGES

V

V

REF-H

I

REF-H

V

I

REF-V

Supply Voltage (Pin18) 10.8 12 13.2 V

CC

Supply Current (Pin18) See Figure 1 40 60 mA

I

CC

Reference Voltage forHorizontal Section (Pin 7) I = 2mA 7.4 8 8.6 V

Max SourcedCurrent on V

Reference Voltage forVertical Section (Pin 26) I = 2mA 7.4 8 8.6 V

REF-V

Max SourcedCurrent on V

(Pin 7) 5 mA

REF-H

(Pin 26) 5 mA

REF-V

INPUT SECTION/PLL1

V

V

V

Horizontal Input Threshold Voltage (Pin 17) Low level voltage

INTH

VCO ControlVoltage (Pin 12) V

VCO

VCO Gain,dF/dV (Pin 12) R0 = 6.49kΩ, C0 = 680pF 17 kHz/V

COG

Hph Horizontal Phase Adjust (Pin 15) % of Horizontalperiod ±12.5 %

f0 Free Running Frequency (adjustable b y changing R0) R0 = 6.49kΩ, C0 = 680pF 25 27 29 kHz

CR PLL1 Capture Range

PLLinh PLL 1 Inhibition (Pin 14) PLL ON

(Typ. Threshold = 1.6V) PLL OFF

I

HLock0

V

HLock0

Max OutputCurrent on HLock Output I

Low Level Voltage on HLock Output V2with I2= 10mA 0.25 0.5 V

SECOND PLL AND HORIZONTAL OUTPUT SECTION

FBth Flyback Input Threshold Voltage(Pin 5) See Figure 14 0.65 0.75 V

Hjit Horizontal Jitter See Application Diagram

Horizontal Drive OutputDuty-cycle

(Pin 20 or 21) (see Note)

HDmin

HDmax

Minimum

Maximum

HDvd Horizontal Drive Low Level Output Voltage Pin 20 to GND,

HDem Horizontal Drive High Level Output Voltage

(output on Pin 20)

XRAYth X-RAYProtection Input Threshold Voltage(Pin 16) TBD 8 TBD V

ISblkO Maximum Output Current on Composite

Blanking Output

VSblkO Low-Level Voltage on Composite Blanking

Output (Blanking ON)

ISmoiO Maximum Output Current on Moire Output I

VSmoiO Low-Level Voltage on Moire Output V

Vphi2 Internal Clamping Voltage on 2nd PLL Loop

Filter Output (Pin3)

V

Threshold Voltage to Stop H-out, V-out and to

OFF

Activate BLKout (OFF Mode when V

(Pin 4)

VSCinh Supply Voltage toStop H-out, V-out when

< VSCinh (Pin18)

V

CC

Note : IfH-drive is taken on Pin20 (Pin 21 connectedto supply), H-D is the ratio of low level duration to horizontal period.

IfH-drive is taken on Pin21 (Pin 20 grounded), H-D isthe ratio of high level duration to horizontal period.

In both cases, H-D period drivinghorizontal scanning transistor off.

amb

Fh Min

Fh Max

4<VOFF

=25°C)

)

Highlevel voltage 2

= 8V 1.6 to 6.2 V

REF-H

R0 = 6.49kΩ, C0 = 680pF

See conditions on Fig. 1

f0

3.7 x f0

V

14

V

14

2

2

80 ppm

(Pins8-9)

=2V

V

4

=6V

V

4

V

4=VREF

- 100mV

32

53.5

57.5

34

56

60

58.5

62.5

1.1 1.7 V

V

21-V20,IOUT

Pin 21 to V

= 20mA

I

OUT

I

22

with I22= 10mA 0.25 0.5 V

V

22

23

with I23= 10mA 0.25 0.5 V

23

Vmin

Vmax

V

4

= 20mA

,

CC

9.5 10 V

1.6

3.2

TBD 7.5 V

0.8 V

0.8 V

10 mA

36

10 mA

10 mA

1V

kHz

kHz

V

%

%

%

V

V

9105-06.TBL

6/32

TDA9105

VERTICALSECTION

OperatingConditions

Symbol Parameter Min. Typ. Max. Unit

VSVR Vertical Sync Input Voltage (Pin 34) 0 5.5 V

VEWM Maximum EW OutputVoltage (Pin 37) 6.5 V

VDHPCM Maximum Dynamic Horizontal Phase Control OutputVoltage (Pin 40) 6.5 V

VDHPCm Minimum Dynamic Horizontal Phase Control Output Voltage (Pin 40) 0.9 V

VDFm Minimum Vertical Dynamic Focus Output Voltage (Pin 1) 0.9 V

Rload Minimum Load for less than 1% Vertical Amplitude Drift (Pin 25) 65 MΩ

9105-07.TBL

ElectricalCharacteristics (VCC=12V, T

amb

=25°C)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

BIASP

I

BIASN

VSth Vertical Sync Input Threshold Voltage(Pin 34) High-level

VSBI Vertical Sync InputBias Current

V

V

V

Bias Current (current sourced by PNP Base)

(Pins 28-29)

For V

=2V 2 µA

28-29

Bias Current (Pin31) (sinkedby NPN base) For V31= 6V 0.5 µA

2

Low-level

V

= 0.8V 1 µA

(Current Sourced by PNP Base)

Voltage at Ramp Bottom Point (Pin 27) 2/8 V

RB

Voltage atRampTop Point (with Sync)(Pin27) 5/8 V

RT

Voltage at Ramp Top Point (without Sync) (Pin

RTF

27)

34

VRT-0.1 V

0.8

V

V

REF-V

REF-V

VSW Minimum Vertical Sync Pulse Width (Pin 34) 5 µS

VSmDut Vertical Sync Input Maximum Duty-cycle

15 %

(Pin 34)

VSTD Vertical Sawtooth Discharge Time Duration

With 150nF cap 70 µS

(Pin 27)

VFRF Vertical Free Running Frequency V

= 2V, V29grounded,

28

Measured on Pin27

100 Hz

Cosc (Pin27) = 150nF

ASFR AUTO-SYNC Frequency (see Note 1) With C

RAFD Ramp Amplitude Drift Versus Frequency V

50Hz < f< 165Hz

Rlin Ramp Linearity onPin 30 V

Vpos Vertical Position Adjustment Voltage (Pin 32) V

V

V

I

VPOS

V

Max Currenton VerticalPosition Control

Output (Pin 32)

Vertical Output Voltage (Pin 30)

OR

(peak-to-peak voltage on Pin30)

V31=2V

V

V

V

OUTDC

DC Voltage on Vertical Output (Pin30) See Note 2 7/16 V

= 150nF 50 165 Hz

27

= 6V, C27= 150nF

31

grounded 0.5 %

28,V29

=2V

33

=4V

33

= 6V 3.65

33

100 ppm/Hz

3.2

3.5

3.8

±2mA

2

=4V

31

= 6V 3.75

31

3

4

3.3 V

V

V

2.2 V

V

V

REF-V

V0I Vertical Output Maximum Current (Pin 30) ±5mA

dVS Max VerticalS-Correction Amplitude

= 2Vinhibits S-CORR

V

28

= 6Vgives maximum S-CORR

V

28

Ccorr Max VerticalC-Correction Amplitude V

∆V/V

∆V/V

V

V

at T/4

30pp

at 3T/4 TBD-4+4

30pp

=2V

29

=4V

29

= 6V TBD

29

-5

0

+5

TBD %

%

TBD %

%

%

VFly Th Vertical Flyback Threshold (Pin 36) 1 TBD V

VFly Inh Inhibitionof VerticalFlyback Input (Pin 36) See Note 1 V

I

BIAS DCIN

Notes : 1. It is the frequency range for which theVERTICAL OSCILLATOR will automatically synchronize, using a single capacitor value on

Bias Current (Pin35) (sourced by PNP base) For V35=V

Pin 27 and with a constantramp amplitude.

2. Typically 3.5Vfor Vertical reference voltage typical value (8V).

32

- 0.5 V

REF

2 µA

9105-08.TBL

7/32

TDA9105

VERTICALSECTION (continued)

East/WestFunction

Symbol Parameter Test conditions Min. Typ. Max. Unit

EW

TDEW

EW

EW

KeyAdj Keystone AdjustmentCapability :

Keytrack Keystone versus V-POS control

Notes : 1. When Pin36 >V

DC Output Voltage (see Figure 2) V33=4V,V35=V32,V38= 4V 2.5 V

DC

DC Output Voltage Thermal Drift See Note 2 100 ppm/°C

DC

Parabola Amplitude V28= 2V, V29grounded,

para

Parabola Amplitude versus V-AMP

track

Control (tracking between V-AMP and

E/W)

A/B Ratio (seeFigure 2)

B/A Ratio

(tracking between V-POS and EW)

A/B Ratio

B/A Ratio

-0.5V, Vfly input is inhibitedand vertical blanking on composite blankingoutputis replaced byvertical sawtooth

discharge time.

2. These parameters are not tested on each unit. They are measured during our internal qualification procedure which includes

characterization on batches comming from corners of our processes and also temperature characterization.

REF

= 6V, V33= 4V,

V

31

V

35=V32,V38

V

39

V

39

= 2V, V29grounded

V

28

= 4V, V35=V32,

V

33

= 4V, V39=4V

V

38

V

31

V

31

V

31

= 2V, V29grounded,

V

28

= 6V, V33= 4V,

V

31

V

35=V32,V39

V

38

V

38

= 2V, V29grounded,

V

28

= 6V, V38= 4V,V39=6V

V

31

= 2V, V35=V

V

33

V33= 6V, V35=V

= 4V,

=6V

=2V

=2V

=4V

=6V

=4V

=6V

=2V

32

32

TBD 2.9

0

0.36

0.82

1.45

TBD

0.48

TBD

0.48

0.54

0.54

V

V

V

V

V

9105-09.TBL

Dynamic Horizontal PhaseControl Function

Symbol Parameter Test Conditions Min. Typ. Max. Unit

DHPC

TDDHPC

SPBpara Side Pin BalanceParabola

SPBtrack Side Pin balance Parabola

ParAdj Parallelogram Adjustment Capability

Partrack Parallelogram versus V-pos Control

DC Ouput Voltage (see Figure 3) V33= 4V,V35=V32,V41=4V 4 V

DC

DC Output Voltage Thermal Drift See Note 100 ppm/°C

DC

= 2V,V29grounded,

V

28

= 6V,V33= 4V,

Amplitude (see Figure3)

Amplitude versus V-amp Control

(tracking between V-ampand SPB )

A/B ratio (see Figure.3)

B/A ratio

(tracking between V-posand DHPC)

A/B ratio

B/A ratio

V

31

V

35=V32,V41

V

42

V

42

= 2V,V29grounded,

V

28

= 4V,V35=V32,

V

33

= 4V,V42=6V

V

41

V

31

V

31

V

31

= 2V,V29grounded,

V

28

= 6V,V33= 4V,

V

31

V

35=V32,V42

V

41

V

41

= 2V,V29grounded,

V

28

= 6V,V41= 4V, V42=6V

V

31

= 2V,V35=V32,

V

33

= 6V,V35=V

V

33

=4V

=6V

=2V

=2V

=4V

=6V

=6V

=6V

=2V

32

TBD +1.45

- 1.45 TBD

0.36

0.82

1.45

TBD

TBD

0.12

0.12

0.53

0.53

V

V

V

V

V

9105-10.TBL

8/32

TDA9105

VERTICALSECTION (continued)

VerticalDynamic Focus Function

Symbol Parameter Test Conditions Min. Typ. Max. Unit

VDF

TDVDF

VDFAMP Parabola Amplitude versus V-amp

VDFKEY Parabola Assymetry versus V-pos

Note : These parameters are not tested on each unit. They are measured during our internal qualification procedure which includes

characterization on batches commingfrom corners of our processes andalso temperature characterization.

DC Output Voltage (see Figure 4) V33= 4V,V35=V

DC

DC Output Voltage Thermal Drift See Note 100 ppm/C

DC

= 2V,V29grounded,

V

28

= 4V,V35=V32,

(tracking between V-ampand VDF)

(see Figure 4)

Control (tracking between V-pos

and VDF)

A/B ratio

B/A ratio

V

33

=2V

V

31

=4V

V

31

=6V

V

31

= 2V,V29grounded,

V

28

= 6V,

V

31

V

= 2V, V35=V32,

33

= 6V, V35=V

V

33

32

-0.84

-1.78

-3.14

0.42

32

0.48

6V

-0.72

-1.57

-2.85

0.52

0.58

-0.6

-1.36

-2.56

0.62

0.68

V

V

V

9105-11.TBL

9/32

TDA9105

Figure 1 : Testing Circuit

10kΩ

CC

V

23

19

10kΩ

1

38

10kΩ

37

41

39

Ω

10k

100nF

40

42

10kΩ

V

2.2µF

CC12V

CC

V

MOIRE

18

V-Sync

H-Sync

20

Ω

1k

CC

V

21

H

OUTPUT

BUFFER

2

X

35

SAFETY

416

CC

V

2

Ω

10k

22nF

47nF

53

47nF

PULSE

SHAPER

PHASE

SHIFTER

COMP

PHASE

PROCESSOR

VS

BLK

GEN

H-FLY

36 22

V-SYNC

10/32

6.49kΩ 0.1%

VIDEOUNLOCK

10 11 8 9

680pF 1%

µ

4.7

F

Ω

1.8k

10nF

15 12

1µF

VCO

COMP

PHASE

FREQUENCY

LOCK

IDENT

UNLOCK

V-MID

V-REF

RAMP

VERT OSC

GENERATOR

S

CORR

470nF

1%

27 25 31 30 33 32

1%

150nF

28

V-REF

POL

PULSE

SHAPER

7

6

F

µ

17

DETECT

PLL1

INHIB

14

13

262924

220nF

2.2

F

µ

2.2

PULSE

SHAPER

34

POL

DETECT

TDA9105

9105-03.EPS

TDA9105

Figure2 : E/WOutput

EW

A

EW

DC

PARA

Figure 4 : VerticalDynamic Focus Function

A

VDF

B

DC

Figure3 : DynamicHorizontal Phase Control

Output

V

=6V

42

V41=6V

B

A

SPB

9105-04.EPS

AMP

PARA

=2V

V

42

BVDF

DHPC

V33=2V

DC

9105-05.EPS

9105-06.EPS

11/32

TDA9105

TYPICAL VERTICALOUTPUTWAVEFORMS

Function

Control

Pin

Output

Pin

Control

Voltage

Specification Picture Image

Vertical Size 31 30

Vertical

Position

DC

33 32

Control

Vertical

DC

In/Out

35

37

40

Vertical

S

25 30

Linearity

2V

6V

2V

4V

6V

3.2V

3.5V

3.8V

2V

4V

This terminal is a Pin

1

controlling the centerposition

of geometric correction

signals. When connected to

Pin 32, ”Autotracking” occurs.

2V

∆V

12/32

Vertical

C

Linearity

29 30

6V

2V

6V

∆V

∆V

V

V

V

∆V

∆

∆V

PP

V

PP

PP

=4%

=5%

=5%

9105-13.TBL/ 9105-07.EPS TO 9105-13.EPS

V

PP

V

PP

V

PP

TYPICAL GEOMETRYOUTPUT WAVEFORMS

Function

Control

Pin

Output

Pin

Control

Voltage

=4V

V

39

2V

TDA9105

Specification Picture Image

4.95V

2.95V

Trapezoid

Control

Pin Cushion

Control

Parrallelogram

Control

Side Pin

Balance

Control

38 37

39 37

41

40

42 40

2.5V

6V

=4V

V

38

2V

2.95V

2.5V

2.5V

4.95V

0V

2.9V

6V

=4V

V

42

2V

6V

V

=4V

41

2V

4V

3V4V

3V4V

1.45V

1.45V

6V

Vertical

Dynamic

1

Focus

Note : The specification of Output voltage is indicated on 4VPPvertical sawtooth output condition.The output voltage depends on vertical

sawtooth output voltage.

6V

3V

13/32

9105-14.TBL/ 9105-14.EPS TO 9105-22.EPS

TDA9105

OPERATINGDESCRIPTION

GENERALCONSIDERATIONS

Power Supply

The typicalvalue of the powersupply voltage V

is 12V.Perfectoperationis obtainedif VCCismaintained in the limits : 10.8V → 13.2V.

In order to avoid erratic operation of the circuit

during thetransientphase of V

switchingoff,the valueof V

CC

outputs of thecircuitare inhibited if V

switchingon, or

CC

ismonitoredandthe

<7.6 typi-

CC

cally.

Inordertohaveaverygoodpowersupplyrejection,

the circuitis internallypoweredby severalinternal

voltage references (The unique typical value of

which is 8V). Two of these voltage referencesare

externallyaccessible, one for the verticalpart and

one for the horizontal part. These voltage references can be used for the DC control voltages

applied onthe concernedpinsby thewayof potentiometers or digital to analog converters(DAC’s).

Furthermoreit isnecessaryto filterthea.m.voltage

references by the use of external capacitor connected to ground, in order to minimize the noise

and consequentlythe ”jitter” on vertical and horizontal output signals.

DC Control Adjustments

The circuithas10adjustmentcapabilities: 2forthe

horizontal part, 2 for the E/Wcorrection, 4 for the

vertical part, 2 for the Dynamic Horizontal phase

control.

The corresponding inputs of the circuit has to be

driven with a DC voltage typically comprised between 2 and 6V for a value of the internal voltage

referenceof 8V.

CC

In order to have a good tracking with the voltage

reference value, it’s better to maintainthe control

voltagesbetween V

/4 and 3/4⋅ V

REF

REF

.

The input current of the DC control inputs is typicallyvery low (about a few µA).Dependingon the

internalstructure of the inputs, itcan be positiveor

negative(sink or source).

HORIZONTAL PART

Input section

The horizontal input is designed to be sensitiveto

TTLsignalstypically comprisedbetween 0and 5V.

Thetypicalthresholdof this inputis1.6V.Thisinput

stageuses an NPN differentialstage and the input

currentis very low.

Figure6 : InputStructure

H-SYNC 1.6V

Concerningthe duty cycle of the input signal, the

followingsignals may be appliedto the circuit.

Using internal integration,both signalsare recognizedon conditionthatZ/T≤ 25%.Synchronisation

occurs on the leading edge of the internal sync

signal. The minimum value of Z is 0.7µs.

Figure7

9105-24.EPS

Figure 5 : Exampleof PracticalDC Control

VoltageGeneration

V

REF

DCControl

PWM

DAC

Output

14/32

Voltage

PLL1

ThePLL1 is composedof aphase comparator, an

external filter and a VoltageControlled Oscillator

(VCO).

Thephasecomparatorisa”phasefrequency”type,

designedin CMOStechnology.This kind of phase

detector avoids locking on false frequencies. It is

followedby a ”charge pump”, composed of 2 current sourcessink and source(I =1mAtyp.)

9105-23.EPS

9105-25.EPS

OPERATINGDESCRIPTION (continued)

Figure 8 : Principle Diagram

13

LOCKDET

COMP1

E2

H-LOCKOUT

2

H-LOCKCAP

H-SYNC

17

INPUT

INTERFACE

The dynamic behaviour of the PLL is fixed by an

external filter which integrates the current of the

charge pump. A ”CRC” filter is generally used(see

Figure 9).

PLL1is inhibited byapplying a high level on Pin 14

(PLLinhib )whi chisa TTLcompatibl einput.Theinhibi tion results fr om the openingof a switc hlocated betweenthechargepumpandthefilter(see Figure8).

The VCOuses an externalRC network. It delivers

a linear sawtooth obtained by charge and discharge of the capacitor,bya currentproportionnal

to the current in the resistor. typical thresholds of

sawtoothare 1.6Vand 6.4V(see Figure10).

The control voltage of the VCO is typically comprised between 1.6V and 6V (see Figure 10). The

theoreticalfrequencyrangeofthis VCOisintheratio

1 → 3.75, but due to spread and thermal drift of

externalcomponentsand thecircuititself,the effec-

Figure 10 : Details of VCO

High

Low

CHARGE

PUMP

PLL1INHIB

INHIBITION

H-POS

PHASE

ADJUST

14

PLL

15

PLL1F R0 C0

12 11 10

VCO

OSC

3.2V

tivefrequencyrange has tobe smaller (e.g.30kHz

→ 85kHz).In theabsenceofsynchronisationsignal

thecontrolvoltageisequalto1.6Vtyp.andtheVCO

oscillates on its lowestfrequency(free frequency).

Thesynchrofrequencyhastobealwayshigherthan

thefreefrequencyanda marginhas tobe taken.As

an example for a synchro range from 30kHz to

85kHz,the suggestedfree frequencyis 27kHz.

Figure9

PLL1F

12

TDA9105

9105-26.EPS

9105-27.EPS

Loop

12

Filter

(1.6V < V < 6V)

12

11

R0

I

0

2

I

0

4I

0

2

C0

10

6.4V

1.6V

6.4V

1.6V

0 0.75T T

RS

FLIPFLOP

9105-28.EPS

15/32

TDA9105

OPERATINGDESCRIPTION (continued)

The PLL1 ensures the coincidence between the

leading edge of the synchro signal and a phase

reference obtained by comparison between the

sawtooth of the VCO and an internal DC voltage

adjustablebetween 2.4V and 4V (byPin 15). So a

±45°phase adjustmentis possible(seeFigure 11).

Figure11 : PLL1 Timing Diagram

H Osc

Sawtooth

Phase REF1

H Synchro

Phase REF1 isobtainedby comparisonbetween thesawtoothand

a DCvoltage adjustable between 2.4V and 4V. The PLL1 ensures

the exact coincidence between the signals phase REF and

HSYNS.A ± T/8phase adjustment is possible.

0.75T

The twoVCO threshold canbe filteredby connecting capacitoron Pins8-9.

The TDA9103 also includes a LOCK/UNLOCK

identification block which senses in real-time

0.25T

6.4V

2.4V<Vb<4V

Vb

1.6V

whetherthePLLis lockedon the incominghorizontal sync signal or not. The resulting informationis

availableon HLOCKOUToutput (Pin 2). The block

diagram of the LOCK/UNLOCK function is describedin Figure 12.

TheNOR1 gateis receivingthe phasecomparator

output pulses (which alsodrive the chargepump).

Whenthe PLL is locked,on point A there is a very

small negative pulse (100ns) at each horizontal

cycle, so after R-C filter, there is a high level on

Pin13 whichforce HLOCKOUTto high level(providedthat HLOCKOUTis pulled up to V

CC

).

When the PLL is unlocked, the 100ns negative

pulseonA becomesmuchlargerandconsequently

the average level on Pin13 willdecrease.When it

reaches 6.5V, point B goes to low level forcing

HLOCKOUToutput to ”0”.

Thestatusof Pin13 isapproximatelythe following :

- Near 0Vwhen there is no H-SYNC,

- Between0 and4V withH-SYNCfrequencydifferent from VCO,

- Between 4 and8Vwhen H-SYNC frequency

9105-29.EPS

= VCOfrequency butnot in phase,

- Near to8Vwhen PLL is locked.

It is important to notice thatPin 13is notanoutput

pinand mustonly beused forfilteringpurpose(see

Figure12).

Figure 12 : LOCK/UNLOCKBlock Diagram

From

Phase

Comparator

NOR1

A

20kΩ

220nF

H-Lock CAP

13

6.5V

2

B

HLOCKOUT

9105-30.EPS

16/32

TDA9105

OPERATINGDESCRIPTION (continued)

PLL2 The PLL2 ensures a constant position of the

Figure 13 : PLL2 TimingDiagram

H Osc

Sawtooth

0.75T

0.25T

6.4V

4V

1.6V

shaped flyback signalin comparison with the sawtoothof theVCO (seeFigure 13).

The phase comparator of PLL2 is followed by a

chargepump witha ±0.5mA(typ.) outputcurrent.

TheflybackinputiscomposedofanNPNtransistor.

This input has tobe currentdriven.

Themaximumrecommanded inputcurrentis 2mA

(seeFigures 14 and 15).

Flyback

Internally

Shaped

Flyback

H Drive

Ts

Duty Cycle

The duty cycle of H-driveis adjustable between 30% and 50%.

Figure 15 : Dual PLL Block Diagram

Horizontal

Input

17

C Lockdet

INPUT

INTERFACE

Adjust

Rapcyc

43

RAP

CYC

VBVA

HLOCKOUT

13 14 12 11 10

2

LOCKDET

High

COMP1

LowE2

Cap

PHi2

CHARGE

PUMP

High

Low

Figure14 : Flyback Input Electrical Diagram

400Ω

5

HFLY

20kΩ

9105-31.EPS

CHARGE

PUMP

COMP2

PLL1INHIB

INHIBITION

Horizontal

PHASE

ADJUST

4V

EN

PLL

Adjust

15

R0 C0Filter

VCO

3.2V

GND 0V

OSC

FLYBACK

Q1

Flyback

5

9105-32.EPS

PWM

LOGI

PWM

BUFFER

21

20

SortCOLL

SortEM

17/32

9105-33.AI

TDA9105

OPERATINGDESCRIPTION (continued)

Output Section

The H-drive signal is transmitted to the output

through a shaping block ensuring a duty cycle

adjustable from 30% to 50%. In order to ensure a

reliable operation of the scanningpower part, the

output is inhibitedin the followingcircumstances:

-V

too low,

CC

- Xray protectionactivated,

- During thehorizontal flyback,

- Outputvoluntarily inhibited throughPin 4.

The outputstage iscomposedofa DarlingtonNPN

bipolartransistor.Boththecollectorand theemitter

are accessible(see Figure 16).

TheoutputDarlingtonis inoff-statewhenthepower

scanning transistoris alsoin off-state.

The maximum output current is 20mA, and the

correspondingvoltagedropofthe outputdarlington

is 1.1Vtypically.

It is evident that the power scanning transistor

cannot be directly driven by the integratedcircuit.

An interfacehasto bedesignedbetweenthe circuit

and the power transistorwhich can be ofbipolaror

MOS type.

X-RAY PROTECTION : the activation of the X-ray

protectionis obtained by applicationof ahigh level

on the X-ray input (>8V). Consequences of X-ray

protectionare :

- Inhibition of H drive output,

- Activationof compositeblanking output.

The reset of this protection is obtained by V

CC

switchoff (see Figure 17).

Figure16 : Output stagesimplifieddiagram,

showingthe two possibilitiesof

connection

V

21

CC

20

V

CC

21

H-DRIVE

H-DRIVE

Outputs inhibition

The applicationof a voltagelower than1V (typ.) on

Pin 4(duty cycle adjust) inhibitsthe horizontaland

vertical outputs. Thisis not memorised.

Figure 17 : Safety FunctionsBlock Diagram

Checking

V

CC

V

CC

REF

XRAY Protection

1V

0.7V

S

R

Inhibition

LOGIC

BLOCK

Q

XRAY

V

CC off

H-Duty cycle

Flyback

V-fly

Vsync

V sawtooth

retracetime

H-fly

20

9105-34.EPS

H OUTPUT

INHIBITION

V OUTPUT

INHIBITION

COMPOSITE

BLANKING

to 2ND PLL

9105-35.EPS

18/32

OPERATINGDESCRIPTION (continued)

Moire Function

Figure 18 : Moire Function Block Diagram

TDA9105

H-SYNC

V-SYNC

Figure 19 : Moire Output Waveform

EVEN FRAME

H

V

MOIRE

ODD FRAME

H

Monosta ble

Ck

D

Ck

D

Rst

Q

Q

Q

Q

23

9105-36.EPS

V

MOIRE

Geometric Corrections

The principle isrepresentedin Figure20.

Starting from the verticalramp, aparabolashaped

is generatedfor E/Wcorrection,dynamichorizontal

phase control correction, and verticaldynamicFocus correction.

The core of the parabola generator is an analog

multiplier. The output currentof whichis equalto :

2

.

is a vertical DC

Where V

∆I=k(V

is the vertical ramp, typically com-

RAMP

RAMP-VDCIN)

prised between 2 and 5V, V

DCIN

input adjustablein the range 3.2V → 3.8V in order

to generate a dissymmetric parabola if required

(keystoneadjustment).

In order to keep good screengeometryforany end

user preferencesadjustment we implemented the

possibilityto have”geometry tracking”. To enable

the ”tracking” function, the V

nectedto V

It is possible to inhibitV

fixedDC voltageon theV

DCIN

.

POS

DCIN

DCOUT

trackingby applying a

must be con-

Pin.

This DC voltage in that case must be taken from

the verticalreference and adjustedto 3.5Vwith an

externalbridge resistor.

Due to large output stages voltage range (E/W,

BALANCE, FOCUS), the combination of tracking

function with maximum vertical amplitudemax. or

min.vertical positionand maximumgainonthe DC

controlinputsmay leads to theoutputstagessaturation. This must be avoided by limitingthe output

voltageby apropriateDC controlvoltages.

19/32

9105-37.EPS

TDA9105

OPERATINGDESCRIPTION (continued)

Geometric Corrections(continued)

Figure 20 : GeometricCorrectionsPrinciple

ANALOG MULTIPLIER

VERTICALRAMP

2

VERT.DYN. FOCUS OUT

VDCIN

VDCIN

VDCIN

ForE/WpartandDynamicHorizontalphasecontrol

part, a sawtooth shaped differentialcurrent in the

followingformisgenerated:∆I’= k’(V

RAMP-VDCIN

Then ∆Iand∆I’are added together and converted

into voltage.

These two parabola are respectively available on

Pin 37 andPin40 bythe way of an emitter follower

which has to be biased by an external resistor

(10kΩ). They can be DC coupled with external

circuitry.

EW V

= 2.5V+ K1’(V

OUT

+K

RAMP-VDCIN

1(VRAMP-VDCIN

2

)

K1isadjustableby EW amp control (Pin 39)

’ is adjustableby KEYST control (Pin 38)

K

1

EW AMP

EW OUT

KEYSTONE

SIDEPIN AMP

SIDE PIN BAL. OUT

KEY BALANCE

Dyn. Hor.

PhaseControl

).

K2is adjustableby SPBamp control (Pin 42)

’is adjustableby KEYBALcontrol (Pin 41)

K

2

V

OUT

=4V+K2’(V

+K

2(VRAMP-VDCIN

RAMP-VDCIN

For vertical dynamic focus part, only a constant

amplitudeparabolais generated in the form :

=6V - 0.75x (V

V

OUT

AMP-VDCIN

Theoutputconnectionisthesame asthe twoother

corrections(Pins 37-40).

)

It is important to note that the parasitic parabola

during the discharge of the vertical oscillator capacitoris suppressed.

)2.

9105-38.EPS

)

2

)

20/32

OPERATINGDESCRIPTION (continued)

VERTICALPART

Figure 21 : VerticalPart Block Diagram

DISCH.

V_SYNC

34

SYNCHRO OSCILLATOR

POLARITY

TDA9105

TRANSCONDUCTANCE

AMPLIFIERCHARGE CURRENT

REF

27

OSC

CAP

SAMPLING

25

SAMP.

CAP

S CORRECTION

28

VS_AMP

29

COR_C

PARABOLA

GENERATOR

38

EW_CENT

41 42

SPB_CENT

SPB_AMP

The verticalpart generatesa fixed amplitude ramp

which can be affected by a S and C correction

shape.Then,the amplitude ofthisrampis adjusted

to drivean externalpower stage.

The internalreference voltageused forthe vertical

part isavailablebetween Pin 26 andPin24. Itcan

be usedasvoltagereferenceforany DCadjusment

C CORRECTION

30

31

VERT_OUT

39

EW_AMP

37

EW_OUT

40

SPB_OUT

1

V_FOCUS

Vlow

Sawth.

Disch.

VERT_AMP

to keep a high accuracy to each adjustment. Its

typicalvalue is :

V26=V

REF

= 8V.

The charge of the external capacitor on Pin 27

) generates a fixedamplitude ramp between

(V

CAP

the internal voltages, V

(VH=5/8 ⋅ V

REF

).

L(VL

=V

REF

/4) and V

9105-39.EPS

H

21/32

TDA9105

OPERATINGDESCRIPTION (continued)

VERTICALPART (continued)

Function

When the synchronisationpulse is not present, an

internal current source sets the free running frequency.For an external capacitor,C

the typicalfree running frequencyis 100Hz.

Typical free running frequency can be calculated

by :

f0(Hz)=1.5 ⋅ 10−5⋅

1

C

OSC

A negative or positive TTL level pulse applied on

Pin 34 (VSYNC) can synchronise the ramp in the

frequencyrange [fmin,fmax].This frequencyrange

depends on the external capacitor connected on

Pin 27. A capacitor in the range [150nF, 220nF] is

recommanded for application in the following

range: 50Hz to 120Hz.

Typical maximumandminimumfrequency,at 25°C

and without any correction (S correction or C correction), can becalculated by :

=2.5 ⋅ f0and f

f

max

min

=0.33 ⋅ f

0

If S or C corrections are applied,these values are

slighty affected.

If an externalsynchronisationpulse is applied, the

internal oscillator is automaticaly caught but the

amplitude is no more constant. An internalcorrection is activated to adjust it in less than half a

second: the highest voltage of theramp onPin27

is sampledon thesamplingcapacitorconnectedon

Pin 25 (VAGCCAP) at each clock pulse and a

transconductance amplifier generates the charge

current of the capacitor. The ramp amplitude becomes again constant.

It is recommandedto usea AGCcapacitorwithlow

leakagecurrent.A valuelower than 100nA ismandatory.

Pin 36, Vfly is the vertical flyback input used to

generate the composite blanking signal. If Vfly is

not used, (V

- 0.5), at minimum, must be con-

REF

nected to thisinput.

DC Control Adjustments

Then, S and C correction shapes can be addedto

this ramp. This frequency independent S and C

corrections are generated internally; their ampli-

(nF)

OSC

= 150nF,

tude are DC adjustable on Pin 28 (V

SAMP

) and

Pin 29 (COR-C).

S correctionis non effectivefor V

/4 and maximumfor V

V

REF

SAMP

SAMP

= 3/4 ⋅ V

lower than

.

REF

C correctionis non effectivefor COR-C grounded

and maximum for :

COR-C = V

/4 or COR-C = 3/4 ⋅ V

REF

REF

.

Endly,the amplitudeof thisSandC correctedramp

can be adjustedby the voltage applied on Pin 31

). The adjustedramp is available on Pin 30

(V

AMP

) to drive an external power stage. The gain

(V

OUT

of thisstageistypically±30% whenvoltage applied

on Pin31 is in the rangeV

/4 to3/4 ⋅ V

REF

REF

.The

DC value of this ramp is kept constant in the

frequency range , for any correction applied onit.

Its typicalvalue is : V

DCOUT=VMID

ADC voltage is availableon Pin 32 (V

= 7/16 ⋅ V

DCOUT

driven bythe voltageapplied on Pin33 (V

For a voltage control range between V

3/4 ⋅ V

V

DCOUT

So,theV

of V

, thevoltageavailableon Pin 32is :

REF

= 7/16 ⋅ V

DCOUT

. It increases the accuracywhen tempera-

OUT

±300mV.

REF

voltageis correlated withDC value

REF

REF

). Itis

POS

/4 and

.

)

ture varies.

Basic Equations

In firstapproximation,theamplitudeof therampon

Pin 30 (V

V

OUT-VMID

with V

V

V

On Pin32 (V

lated by : V

is the voltageapplied on Pin33.

V

POS

)is:

OUT

=(V

CAP-VMID

= 7/16 ⋅ V

MID

isthe middlevalueof therampon Pin27

MID

CAP=V27

, ramp withfixed amplitude.

DCOUT

DCOUT=VMID

) [1 + 0.16 ⋅ (V

; typically 3.5V

REF

AMP-VREF

), thevoltage (in volts)is calcu-

+0.16 ⋅ (V

POS-VREF

/2)]

/2).

The current available on Pin27

(when V

I

OSC

C

SAMP=VREF

=3/8 ⋅ V

: capacitorconnectedon Pin 27

OSC

REF

⋅ C

/4) is :

OSC

⋅ f

f synchronisationfrequency

The recommanded capacitor value on Pin 25

(V

) is470nF.Its ensuresa goodstability ofthe

AGC

internal closedloop.

22/32

INTERNALSCHEMATICS

Figure22

TDA9105

Figure26

Href

5

Figure23

Figure24

Pins 1-37-40

N MOS

1mA max

2-22-23V

CC

Pins

10mAmax.

Href

Figure27

9105-40.EPS

9105-41.EPS

Figure28

9105-44.EPS

V

CC

7

9105-45.EPS

Figure25

4

P MOS

8

3

9105-42.EPS

9105-46.EPS

Figure29

9

9105-43.EPS

9105-47.EPS

23/32

TDA9105

INTERNALSCHEMATICS (continued)

Figure30

10

Figure31

11

Figure34

P MOS

14

9105-48.EPS

9105-52.EPS

Figure35

Figure32

12

Figure33

N MOS P MOS P MOS

13

N MOS

9105-49.EPS

Figure36

9105-50.EPS

9105-51.EPS

15

9105-53.EPS

16

9105-54.EPS

24/32

INTERNALSCHEMATICS (continued)

Figure37

TDA9105

Figure39

Figure38

Figure41

P MOS

17

21

20mAmax.

20

Figure40

9105-55.EPS

9105-56.EPS

25

P MOS

N

P

N

P

9105-57.EPS

V

CC

26

9105-58.EPS

27

V

REF

V

REF

V

CC

V

REF

N

P

N MOS

9105-59.EPS

25/32

TDA9105

INTERNALSCHEMATICS (continued)

Figure42

V

REF

28

Figure43

Figure46

Figure47

9105-60.EPS

32

V

CC

9105-64.EPS

V

REF

29

Figure44

30

Figure45

V

33

REF

N MOS

9105-61.EPS

V

CC

9105-65.EPS

Figure48

V

REF

34

9105-62.EPS

9105-66.EPS

Figure49

V

REF

26/32

31

9105-63.EPS

35

9105-67.EPS

INTERNALSCHEMATICS (continued)

Figure50

V

REF

36

P MOS

Figure51

Pins

38-39

41-42

TDA9105

V

REF

9105-68.EPS

9105-69.EPS

27/32

TDA9105

APPLICATION DIAGRAMS

Figure 52 : DemonstrationBoard

R75

SCOR

CCOR

KEYST

PINCSH

KEYBAL

HDF

+12V

VSIZE

VSHIFT

SBPAMP

HSHIFT

27kΩ

R28 3.9kΩ

R25 3.9kΩ

R22 3.9kΩ

R19 3.9kΩ

R13 3.9kΩ

R16 3.9kΩ

R10 3.9kΩ

R7 3.9kΩ

R4 3.9kΩ

R1 3.9kΩ

HFLY

HOUT

REF

R30 10kΩ

R29 120kΩ

R27 10kΩ

R26 120kΩ

R24 10kΩ

R23 120kΩ

R21 10kΩ

R20 120kΩ

R15 10kΩ

R14 120kΩ

R18 10kΩ

R17 120kΩ

R12 10kΩ

R11 120kΩ

R9 10kΩ

R8 120kΩ

R6 10kΩ

R5 120kΩ

R3 10kΩ

R2 120kΩ

R73 10k

Ω

R74 10kΩ

TP13

1µF1µF

++

C35 C39

REF V

H

R83 1kΩ R93 R94

R84

47kΩ

J3b

J2b

J1b

HSIZE

12341234 567

0/5V to 2/6V INTERFACE

1234

+12V

15kΩ 330kΩ

R55

270kΩ

R53

1kΩ

R52

27kΩ

IC1

R87

10kΩ

C54 15nF

R91

1

J24

E/W

R59

2.2Ω 1W

C44

220pF

R57

270kΩ

BC557

Q3 Q4

BC557

Ω

R92

1k

C38 1µF

42

41

40

12345

C1

TP12

22nF

R89

4.7kΩ

+12V

R88

10kΩ

5.6kΩ

1

J25

CON1

DYN

FOCUS

1

1

J21

-12V

Q9

TIP122

39kΩ

R56

R54

470Ω

R51

6.2kΩ

E/W POWER STAGE

R81

REF

V

+

C37 1µF

+

37

38

39

678

C45

220pF

REF

H

C30

C34

1µF

+

C36

1µF

+

offon

S1

TP11

C32

100nF

+

C13

470µF

D1

1N4004

+12V

D5

1N4148

43.2kΩ

33.2kΩ

R82

1%

1%

36

34

35

9

47nF

C50

+

47µF

C51

C29

100nF

SW1

J23

TP15

35V

C12

100µF

+

3

6

2

7

R8515kΩ

R86 4.7kΩ

R70 12kΩ

+

C43 1µF

32

33

T

D

A

10

1112131415

R32

680pF 5%

C2

47nF

TP14

C52

R71

10kΩ

1HFLY

J18

5

1

C10

100nF

R37

+

C42 1µF

910

6.49kΩ 1%

C3

R90 1Ω

2

V YOKE

R41

IC2

4

31

3

R39

1.5Ω

TDA8172

5.6kΩ

C7

10nF

123

J22

R47b

220Ω

1/2W

R401Ω1/2W

Ω

R38 5.6k

VERTICAL

DEFLECTION

REF

V

C4

TP1

27

STAGE

C27

150nF

R47a

C28

47µF

+

C5

26

25

C15

220nF

C31

100nF

+

C14

470µF

-12V

C11

470pF

R36 12kΩ

+

C41 1µF

+

C40 1µF

28

29

30

33Ω 3W

47Ω 3W

+12V

100nF

470nF

HDRIVE

T1

G 5576-00

+

C20

63V

100µF

Q10

R35

L1

10µH

+

1µF

C53

23

24

Q2

STD5N20

R44 10Ω

BC547

1kΩ

HORIZONTAL

DRIVER

STAGE

C19

1nF

R46

560Ω

R45

22kΩ

Q1

BC557

5

1617181920

R31 1.8kΩ

+

C48 1nF

R80 2.7kΩ

4.7µF

C6

220nF

D4

1N4148

R33

10kΩ

TP3

+12V

XRAY INJ2HSYNC

TP2

21 22

C9

100nF

+

C8

100µF

TP5 TP4

1

J3

TP7

1

VSYNC

BLK

J19

J5

TP6

9105-70.EPS

28/32

APPLICATION DIAGRAMS

Figure 53 : Control Board

TDA9105

+5V

Jc4

1

Cc4

Ω

1

Jc26

CON1

10µF

HSIZE

Pc13 4.7kΩ

Pc12 47kΩ

SCOR

Pc11 47kΩ

Pc10 47k

Pc9 47kΩ

Pc8 47kΩ

Pc7 47kΩ

CCOR

VSIZE

VSHIFT

KEYST

PINCSH

Icc1B

14528

+12V

Pc2 47kΩ Cc2

Q

RC

47pF

CX

Pc6 47kΩ

KEYBALHFLY

Pc5 47k

Ω

Pc4 47kΩ

Pc3 47kΩ

C

R

+12V

+12V

Cc4

10µF

Cc5

TT

X

C

100nF

Pc1 47kΩ

Cc1

47pF

Q

T

T

Icc1A

14528

R

Q

Q

SBPAMP

Jc2 Jc3

1234

HSHIFT

HDF

Jc1

1234 1234567

HOUT

9105-71.EPS

29/32

TDA9105

APPLICATION DIAGRAMS

Figure 54 : PCB Layout

30/32

9105-72.TIF

APPLICATION DIAGRAMS

Figure 55 : ComponentsLayout

TDA9105

31/32

9105-73.EPS

TDA9105

PACKAGE MECHANICALDATA

42 PINS- PLASTICSHRINK DIP

A2

A1

E

E1

LA

42

1

Dimensions

BeB1

D

22

21

c

SDIP42

Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

e1

e2

E

.015

0,38

Gage Plane

e3

e2

A 5.08 0.200

A1 0.51 0.020

A2 3.05 3.81 4.57 0.120 0.150 0.180

B 0.36 0.46 0.56 0.0142 0.0181 0.0220

B1 0.76 1.02 1.14 0.030 0.040 0.045

c 0.23 0.25 0.38 0.0090 0.0098 0.0150

D 37.85 38.10 38.35 1.490 1.5 1.510

E 15.24 16.00 0.60 0.629

E1 12.70 13.72 14.48 0.50 0.540 0.570

e 1.778 0.070

e1 15.24 0.60

e2 18.54 0.730

e3 1.52 0.060

L 2.54 3.30 3.56 0.10 0.130 0.140

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility

for the consequences of use of such information nor for anyinfringement of patents or otherrights ofthird parties which may result

from its use. Nolicence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.

Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all

information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components inlife

support devices or systems without express written approval of SGS-THOMSON Microelectronics.

PMSDIP42.EPS

SDIP42.TBL

32/32

1996 SGS-THOMSON Microelectronics - All RightsReserved

Purchase of I

2

I

C Patent. Rights to use these components in a I2C system, is granted provided that the system conformsto

2

C Components ofSGS-THOMSON Microelectronics,conveys alicense under the Philips

2

the I

C Standard Specifications as defined by Philips.

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil -Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia- Malta - Morocco

The Netherlands - Singapore - Spain- Sweden - Switzerland- Taiwan - Thailand - UnitedKingdom -U.S.A.

Loading...

Loading...