TDA7430

DIGITALLYCONTROLLEDAUDIO PROCESSOR WITH

SURROUNDSOUND MATRIX AND VOICECANCELLER

1 STEREO(4 STEREO)INPUT + 1 MIXER INPUT

INPUT ATTENUATION CONTROL IN 0.5dB

STEP

VOICECANCELLERIS AVAILABLE

TREBLEMIDDLE AND BASS CONTROL

THREE SURROUND MODES ARE AVAIL-

ABLE:

- MUSIC:4 SELECTABLERESPONSES

- MOVIE AND SIMULATED:

256SELECTABLE RESPONSES

2 SPEAKER AND 2 RECORD ATTENUATORS:

- 2 INDEPENDENTSPEAKERSAND 2

INDEPENDENTRECORD CONTROL

IN 1dBSTEPFOR BALANCEFACILITY

- AVAILABILITYOFLOUDSPEAKER

EQUALIZATIONFIXEDBY EXTERNAL

COMPONENTS

- INDEPENDENTMUTE FUNCTION

ALL FUNCTIONS PROGRAMMABLE VIA SERIAL BUS

DESCRIPTION

The TDA7430/7431are volume tone (bass middle

and treble) balance (Left/Right) processors with

TDA7431

SDIP42 TQFP44

ORDERING NUMBERS: TDA7430 (TQFP44)

TDA7431 (SDIP42)

voice canceller for quality audio applications in

car radioand Hi-Fisystems.

They reproduce surround sound by using programmable phase shifters and a signal matrix.

Control of all thefunctions is accomplishedby serial bus.

The AC signal setting is obtained by resistor networks and switches combined with operational

amplifiers.

Thanks to the usedBIPOLAR/CMOSTechnology,

Low Distortion, Low Noise and DC stepping are

obtained.

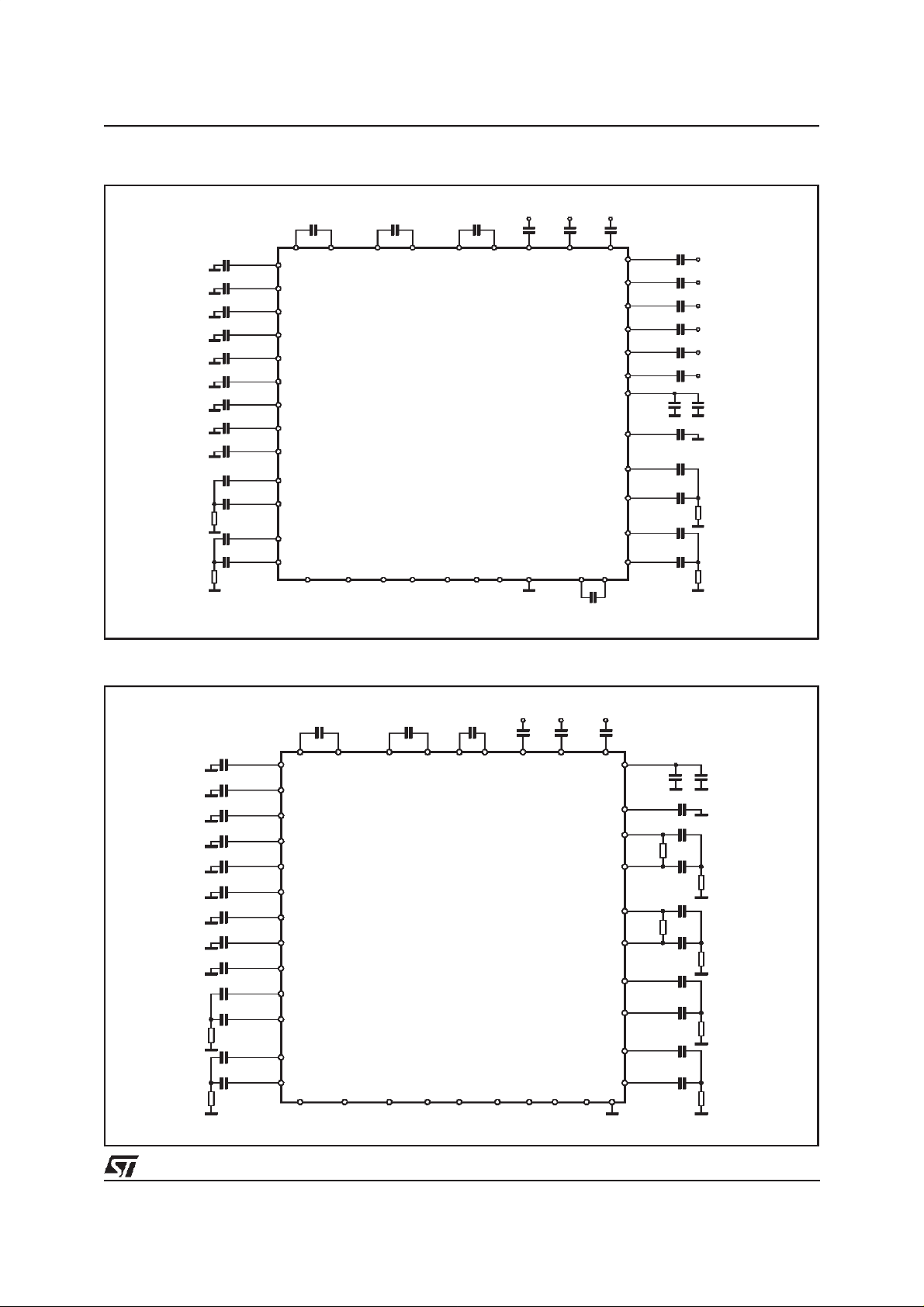

PIN CONNECTIONS

PS4

1

PS3

2

PS2

3

PS1

4

LP

5

LP1

6

HP1

7

HP2

VOUTREF

VAR_L

BASSO_L

VAR_R

BASSO_R

BASS_LO

BASS_LI

BASS_RO

BASS_RI

MIDDLE_LO

MIDDLE_LI

MIDDLE_RO

MIDDLE_RI

September 1999

8

9

10

11

12

13

14

15

16

17

18

19

20

21

D95AU219B

42

V

S

41

CREF

40

NBRO

39

NBRIN

38 LPVC

R_IN37

MIX

36

L_IN

35

NBLIN

34

NBLO

33

RECOUT_L

32

RECOUT_R

31

L_OUT

30

R_OUT

29

DIG_GND28

SCL

27

SDA

26

ADDR

25

AGND

24

TREBLE_L

23

TREBLE_R

22

LP1

HP1

HP2.

REAROUT

REARIN

VAR_L

BASSO_L

VAR_R

BASSO_R

BASS_LO

BASS_LI

LP

PS1

PS2

PS3

VSPS4

CREF

R_IN4

44 43 42 41 3940 38 37 36 35 34

1

2

3

4

5

6

7

8

9

10

MIDDLE_LI

MIDDLE_LO

MIDDLE_RO

171118 19 20 21 22

TREBLE_L

TREBLE_R

MIDDLE_RI

12 13 14 15 16

BASS_RI

BASS_RO

R_IN3

AGND

R_IN2

SDA

LPVC

SCL

33

32

31

30

29

28

27

26

25

24

23

D95AU220B

R_IN1

MIX

L_IN1

L_IN2

L_IN3

L_IN4

RECOUT_L

RECOUT_R

L_OUT

R_OUT

DIG_GND

1/21

TDA7430 - TDA7431

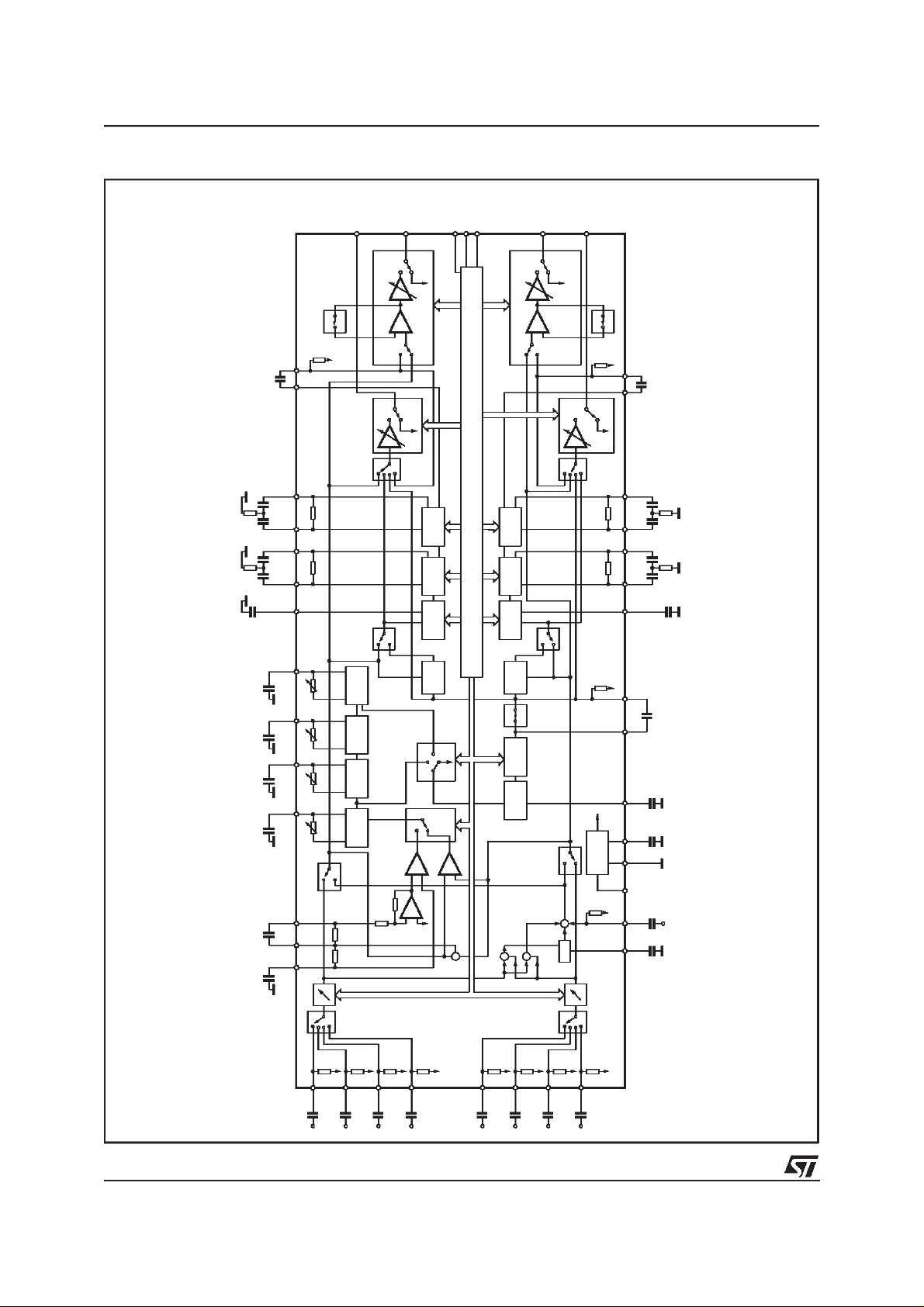

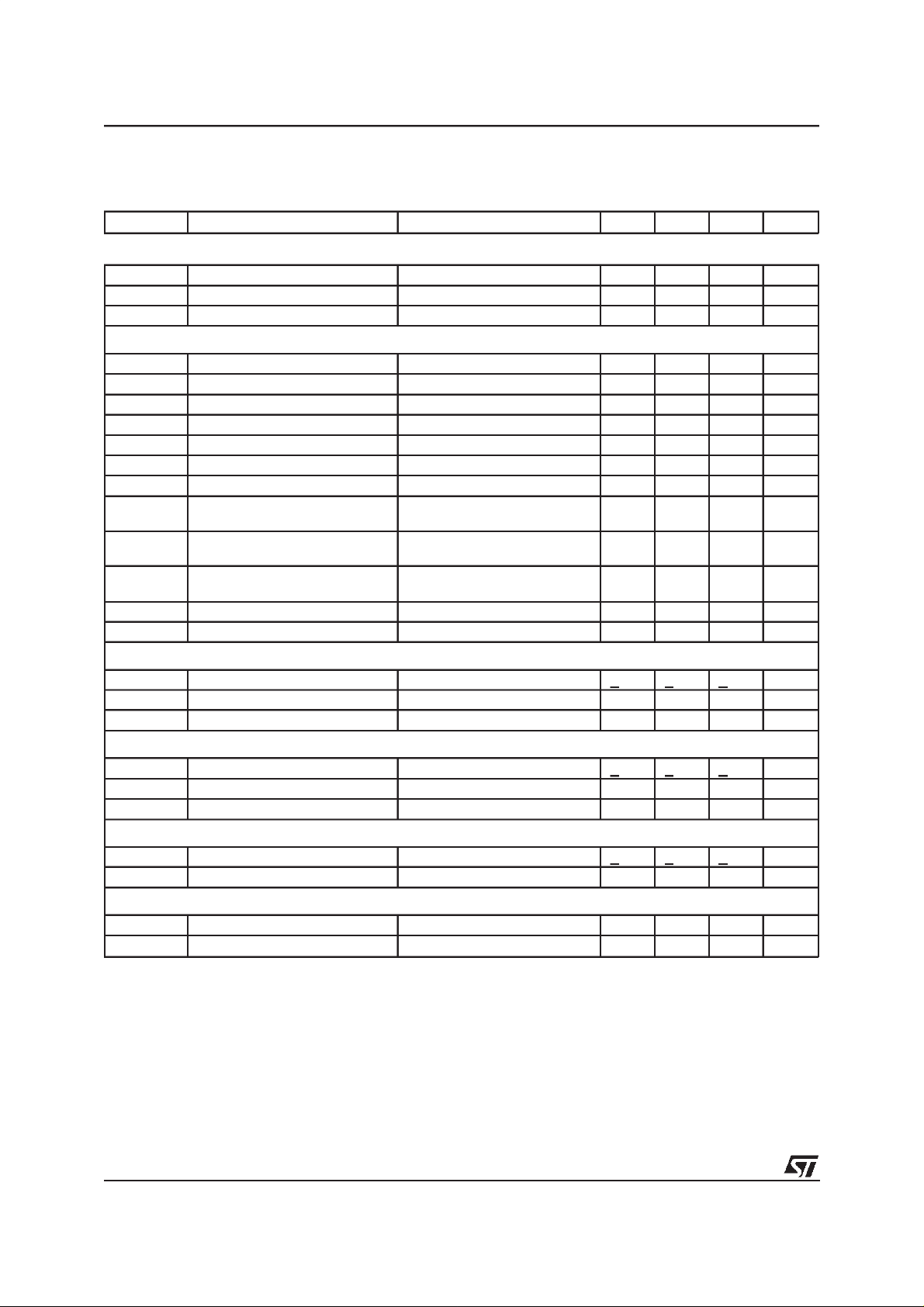

BLOCK DIAGRAM (TDA7430)

RECOUT-L

27

SPKR

79dB CONTROL

SCL

SDA

L-OUT

25

ATT

MUTE

DIG GND

222123

SPKR

R-OUT

RECOUT-R

24

26

ATT

MUTE

79dB CONTROL

D95AU221B

5.6K

2.7K

100nF

100nF

22nF

18nF

5.6nF

22nF

22nF

4.7nF

100nF

5.6nF 680nF

2.2µF

BASSO-L VAR-L

BASS-LO

10 7 6

BASS-LI

MIDDLE-LO

MIDDLE-LI

15 14 11

19

TREBLE-L

PS4

PS3

PS2

PS1

1 2 3 43 42 41 40

LP1 HP1 HP2

31.5dB control

30K

FIX

RB

RM

RPS4

RPS3

RPS2

RPS1

RHP1

RLP1

PS4

PS3

PS2

PS1

79dB CONTROL

OFF

400Hz

400Hz

4KHz

90Hz

REC

SURR

R5

-

+

FIX

VAR

ATT

MUTE

3BAND

C BUS DECODER + LATCHES

2

BASS

MIDDLE

TREBLE

AMP

MIXING

MOVIE/SIM

OFF

MUSIC

MOVIE/

I

L-R

-

+

+

REAR

SURR

MUSIC

SIM

-

+

R6

-

+

+

TREBLE MIDDLE BASS

AMP

MIXING

EFFECT

CONTROL

LPF

9KHz

-

+

30K

MUTE

SURR

RM RB

50K

Vref

SUPPLY

100K

31.5dB control

8912183234

2.2µF

BASSO-R VAR-R

79dB CONTROL

BASS-RO

BASS-RI

100nF 100nF

MIDDLE-RO

18nF 22nF

MIDDLE-RI

17 16 13

5.6nF

REARIN

2.2µF

REAROUT

45

1.2nF

LP

22µF

CREF

AGND

S

V

39 20 38 44

MIX-IN

1µF100nF

LPVC MIX TREBLE-R

5.6K

2.7K

FIX

VAR

ATT

REC

3BAND

FIX

REAR

SURR

OFF

ON

VOICE

+LPF

-

2/21

50K

50K

50K

L-IN3

50K

28

L-IN4

0.47µF

31

30

29

L-IN1

L-IN2

0.47µF

0.47µF

0.47µF

50K

33

35

R-IN2

R-IN1

0.47µF

0.47µF

37

36

R-IN4

R-IN3

0.47µF

0.47µF

50K

50K

50K

THE SWITCHES POSITION MATCHES THE RESET CONDITION

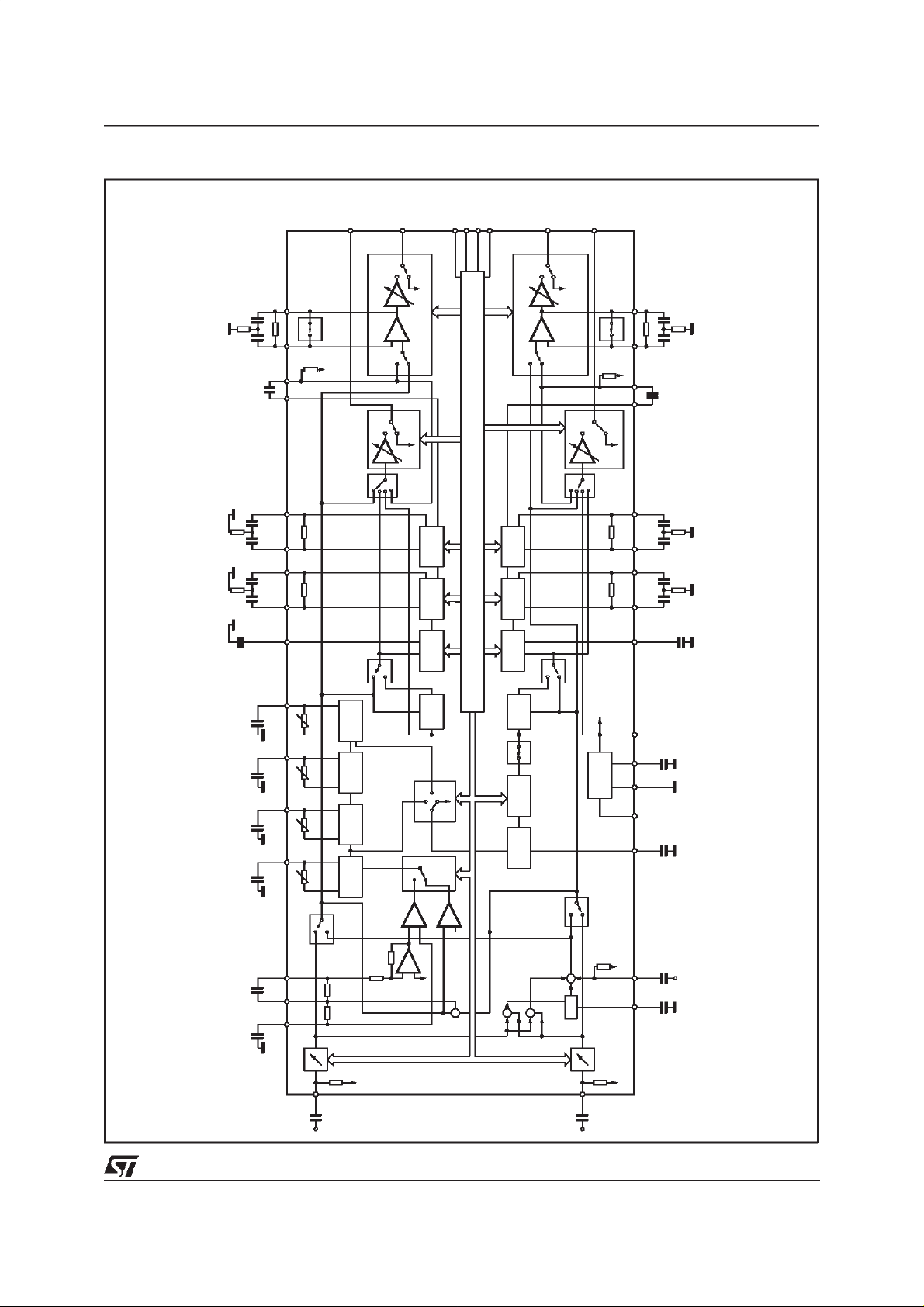

BLOCK DIAGRAM (TDA7431)

NBLO

RECOUT-L

32

ATT

SPKR

79dB CONTROL

30

L-OUT

MUTE

SCL

SDA

272628

DIG GND

25

ADDR

SPKR

TDA7430 - TDA7431

R-OUT

RECOUT-R

29

31

ATT

MUTE

79dB CONTROL

D95AU222C

NBRO

40391213162293638

5.6K

2.7K

NB1

100nF

100nF

22nF

18nF

5.6nF

22nF

22nF

4.7nF

100nF

NB-LA NB-LB

2.2µF

NB2

NBLIN

VAR-L

BASSO-L

BASS-LO

BASS-LI

MIDDLE-LO

MIDDLE-LI

TREBLE-L

PS4

PS3

PS2

PS1

30K

MUTE

79dB CONTROL

RM RB

21 20 17

42 24 415

NB3

NBRIN

VAR-R

BASSO-R

TREBLE-R

VOUTREF

CREF

AGND

S

V

LP

NB-RA NB-RB

2.2µF

BASS-RO

BASS-RI

100nF 100nF

MIDDLE-RO

18nF 22nF

MIDDLE-RI

22µF

1.2nF

NB4

5.6K

2.7K

5.6nF

-

+

30K

79dB CONTROL

FIX

14 11 10 34 33

RB

RM

19 18 15

23

OFF

PS4

RPS4

400Hz

PS3

RPS3

400Hz

PS2

4KHz

RPS2

PS1

90Hz

RPS1

REC

SURR

FIX

VAR

ATT

MUTE

3BAND

C BUS DECODER+ LATCHES

2

BASS

MIDDLE

TREBLE

AMP

MIXING

MOVIE/SIM

MUSIC

MOVIE/

OFF

L-R

-

I

+

REAR

SURR

MUSIC

SIM

-

+

FIX

FIX

TREBLE MIDDLE BASS

AMP

MIXING

EFFECT

CONTROL

LPF

9KHz

+

VAR

SURR

-

3BAND

OFF

REC

ATT

REAR

SURR

Vref

SUPPLY

5.6nF 680nF

LP1 HP1 HP2

678 4 3 2 1

31.5dB control

ON

R6

-

+

R5

RHP1

RLP1

50K

35

L-in

0.47µF

+

+

VOICE

100K

+LPF

-

control

31.5dB

50K

37

R-in

0.47µF

MIX-IN

1µF100nF

LPVC MIX

THE SWITCHES POSITION MATCHES THE RESET CONDITION

3/21

TDA7430 - TDA7431

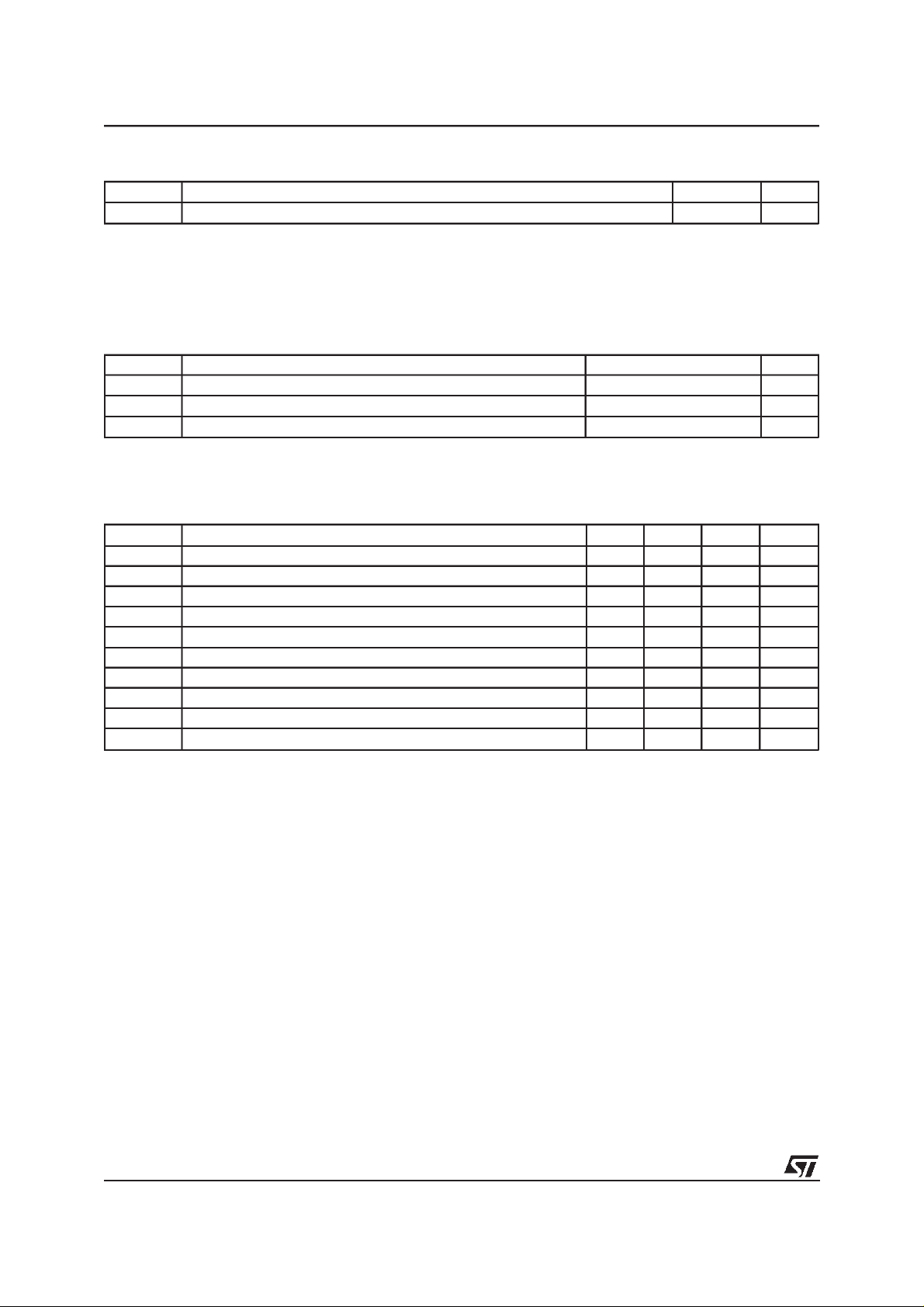

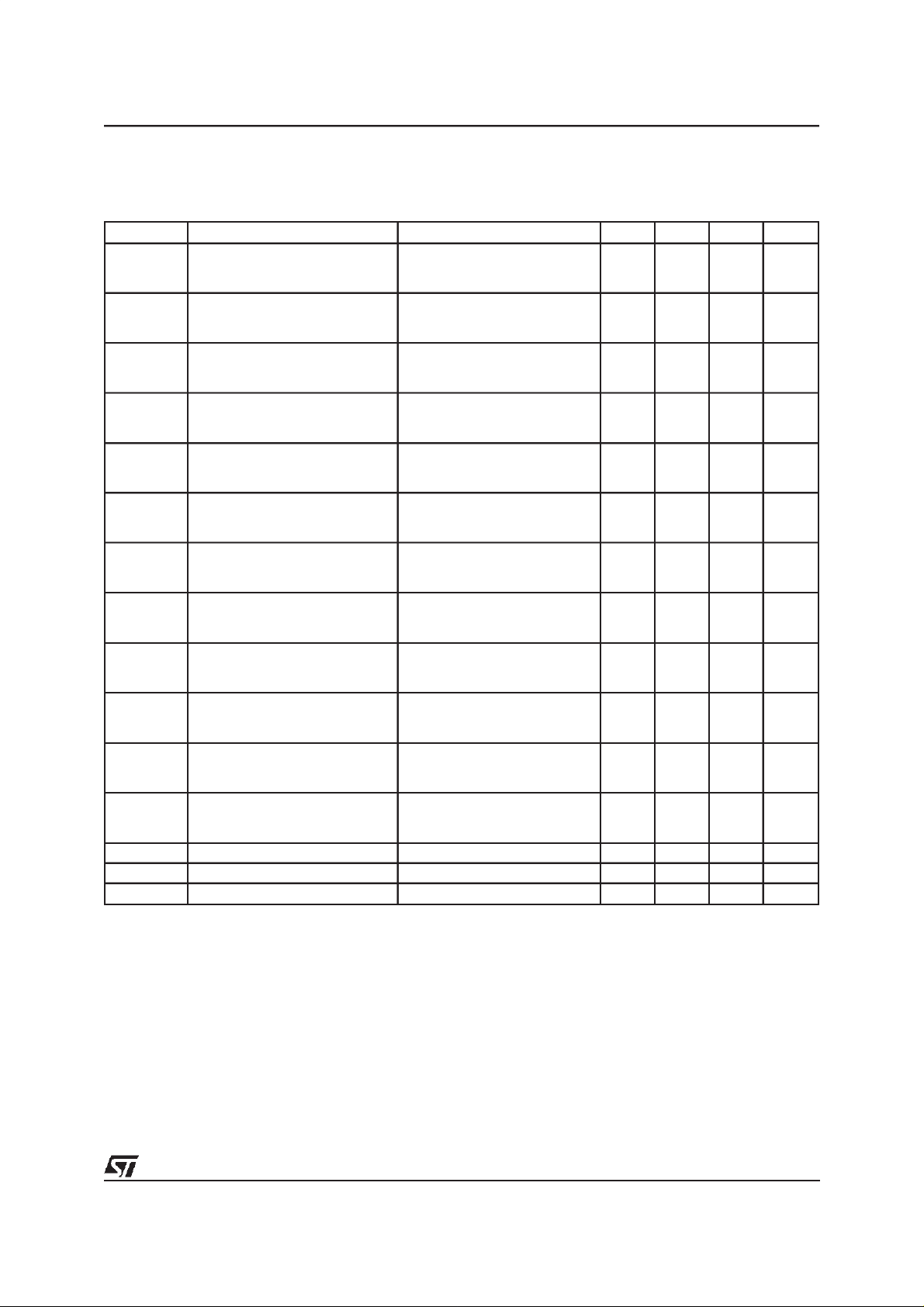

THERMAL DATA

Symbol Description Value Unit

R

thj-pins

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

T

amb

T

QUICK REFERENCE DATA

Symbol Parameter Min. Typ. Max. Unit

V

V

THD Total Harmonic DistortionV = 1Vrms f = 1KHz 0.01 0.1 %

S/N Signal to Noise Ratio V

S

Thermal Resistance Junction-pins Max. 85 °C/W

Operating SupplyVoltage 11 V

S

Operating Ambient Temperature -10 to85

Storage Temperature Range -55 to +150 °C

stg

Supply Voltage 7 9 10.2 V

S

CL

Max. input signal handling 2 Vrms

= 1Vrms (mode = OFF) 106 dB

out

Channel Separation f = 1KHz 90 dB

C

Treble Control (2db step) -14 +14 dB

Middle Control (2db step) -14 +14 dB

Bass Control (2dB step) -14 +14 dB

Balance Control 1dB step (L

) -79 0 dB

CH,RCH

Mute Attenuation 100 dB

C

°

4/21

TEST CIRCUIT (TDA7430)

TDA7430 - TDA7431

2.7K

2.7K

22nF

22nF

4.7nF

100nF

1.2nF

5.6nF

5.6nF

5.6nF

100nF

22nF

18nF

18nF

MIDDLE-LO

22nF

MIDDLE-RO

TREBLE-R

TREBLE-L

LPVC

MIDDLE-LI

MIDDLE-RI

D95AU225B

2.2µF

876

9

PS4

40

PS3

41

PS2

42

PS1

43

LP

44

LP1

1

18

19

34

14

15

16

17

27 26 25 24 23 22 21 20

RECOUT-L RECOUT-R L-OUT R-OUT

2.2µF

REAROUT

VAR-L

BASSO-LVAR-RBASSO-R

TDA7430

2.2µF

0.47µF

REARIN

R-IN4

45

DIG-GND SCL SDA AGND

37 36 35

0.47µF

R-IN3

HP2

0.47µF

R-IN2

38

32

HP1

680nF

32

33

31

30

29

28

39

10

11

12

13

R-IN1

L-IN1

L-IN2

L-IN3

L-IN4

V

S

CREF

BASS-LO

BASS-LI

BASS-RO

BASS-RI

0.47µF

0.47µF

0.47µF

0.47µF

0.47µF

22µF

220nF

100nF

100nF

100nF

100nF

100nF10µF

5.6K

5.6K

1µF

MIX

TEST CIRCUIT (TDA7431)

22nF

PS4

22nF

PS3

4.7nF

100nF

1.2nF

5.6nF

5.6nF

5.6nF

100nF

2.7K

2.7K

22nF

18nF

22nF

18nF

PS2

PS1

LP

LP1

TREBLE-R

TREBLE-L

LPVC

MIDDLE-LO

MIDDLE-LI

MIDDLE-RO

MIDDLE-RI

D95AU224B

2.2µF

13

12 11 10 8 7 37 36 35

2.2µF

VAR-L

HP2BASSO-LVAR-RBASSO-R

2

3

4

5

6

22

TDA7431

23

38

18

19

20

21

9

32 31 30 29 28 27 26 25 24

VOUTREF RECOUT-L RECOUT-R L-OUT R-OUT

680nF

0.47µF

HP1

R-IN

1µF

MIX

0.47µF

L-IN

DIG-GND SCL SDA ADDR AGND

V

S

421

100nF10µF

41

40

39

34

33

NBRO

NBRIN

NBLIN

NBLO

15K

15K

220nF

220nF

7.5K

220nF

220nF

7.5K

22µF

CREF

100nF

14

BASS-LO

100nF

15

BASS-LI

BASS-RO

16

5.6K

100nF

100nF

17

BASS-RI

5.6K

5/21

TDA7430 - TDA7431

ELECTRICALCHARACTERISTICS (referto the test circuitT

V

= 1Vrms;RG= 600Ω, allcontrolsflat (G = 0dB), EffectCtrl = -6dB, MODE = OFF; f = 1KHz

in

=25°C, VS= 9V,RL= 10KΩ,

amb

unless otherwisespecified)

Symbol Parameter Test Condition Min. Typ. Max. Unit

SUPPLY

V

S

I

S

SVR Ripple Rejection L

Supply Voltage 7 9 10.2 V

Supply Current 10 18 26 mA

CH /RCHout, Mode = OFF 60 80 dB

INPUTSTAGE

R

IN

V

CL

C

RANGE

A

VMIN

A

VMAX

A

STEP

V

DC

A

VO1

A

VO2

A

VO3

R

LPV

R

MIX

Input Resistance 35 50 65 KΩ

Clipping Level THD = 0.3% 2 2.5 Vrms

Control Range 31.5 dB

Min. Attenuation -1 0 1 dB

Max. Attenuation 31 31.5 32 dB

Step Resolution 0.5 1 dB

DC Steps adjacent att.step -3 0 3 mV

Voice CancelerOutput 1 LIN=RIN,RIN= ON,

V

= 0V FIX, 0dB attenuation

mix

Voice CancelerOutput 2 LIN=RIN=0VV

mix

=1V

rms

FIX,

567dB

-1 0 1 dB

0dB attenuation

Voice CancelerOutput 3 LIN=-RIN,V

= 0V FIX,

mix

567dB

0dB attenuation

Low Pass Filter Resistance 22.4 32 41.6 KΩ

Input Impedance 70 100 130 KΩ

BASSCONTROL

Gb ControlRange Max. Boost/cut +11.5 +14.0 +16.0 dB

B

STEP

R

B

Step Resolution 1 2 3 dB

Internal Feedback Resistance 32 44 56 K

MIDDLE CONTROL

Gm Control Range Max. Boost/cut +11.5 +14.0 +16.0 dB

M

STEP

R

M

Step Resolution 1 2 3 dB

Internal Feedback Resistance 17.5 25 32.5 K

TREBLECONTROL

Gt Control Range Max. Boost/cut +13.0 +14.0 +15.0 dB

T

STEP

Step Resolution 1 2 3 dB

EFFECTCONTROL

C

RANGE

S

STEP

Control Range -21 -6 dB

Step Resolution 0.5 1 1.5 dB

Ω

Ω

6/21

TDA7430 - TDA7431

ELECTRICALCHARACTERISTICS (continued)

SURROUNDSOUNDMATRIX

TEST CONDITION (Phase Resistor SelectionD0=0, D1=1,D2=0.D3=1, D4=0,D5=1, D6=0,D7=1

Symbol Parameter Test Condition Min. Typ. Max. Unit

G

D

OFF

GOFF

In-phase Gain (OFF) Mode OFF, Input signal of

LR In-phase Gain Difference

(OFF)

G

MOV

D

GMOV

In-phase Gain (Movie) Movie mode, Effect Ctrl = -6dB

LR In-phase Gain Difference

(Movie)

G

MUS

D

GMUS

In-phase Gain (Music) Musicmode, Effect Ctrl = -6dB

LR In-phase Gain Difference

(Music)

L

MON1

L

MON2

L

MON3

R

MON1

R

MON2

R

MON3

R

LP1

R

HPI

R

LPF

Simulated L Output 1 SimulatedMode,EffectCtrl= -6dB

Simulated L Output 2 SimulatedMode,EffectCtrl= -6dB

Simulated L Output 3 SimulatedMode, EffectCtrl= -6dB

Simulated R Output 1 SimulatedMode,EffectCtrl= -6dB

Simulated R Output 2 SimulatedMode,EffectCtrl= -6dB

Simulated R Output 3 SimulatedMode,EffectCtrl= -6dB

Low Pass Filter Resistance 7 10 13 KΩ

High Pass Filter Resistance 42 60 78 KΩ

LP PinImpedance 7 10 13 K

1kHz, 1.4 V

L

L

→

in

out

p-p,Rin

→ R

out

Mode OFF, Input signal of

1kHz, 1.4 V

Rin→ R

Input signalof 1kHz, 1.4 V

Rin→ R

p-p

out,Lin

out,Lin

→ L

→ L

out

p-p

out

Movie mode, Effect Ctrl = -6dB

Input signalof 1kHz, 1.4 V

R

(R

in

→

out

)–(L

→

in

Input signalof 1kHz, 1.4 V

R

(R

in

→

out

), (L

→

in

p-p

L

)

out

p-p

L

)

out

Music mode, Effect Ctrl = -6dB

Input signalof 1kHz, 1.4 V

(Rin→ R

)-(Lin→ L

out

out

p-p

)

Input signalof 250Hz,

1.4 V

p-p,Rin

and Lin→ L

out

Input signalof 1kHz,

1.4 V

p-p,Rin

and Lin→ L

out

Input signalof 3.6kHz,

1.4 V

p-p,Rin

and L

L

→

in

out

Input signalof 250Hz,

1.4 V

p-p,Rin

and Lin→R

out

Input signalof 1kHz,

1.4 V

p-p,Rin

and Lin→R

out

Input signalof 3.6kHz,

1.4 V

p-p,Rin

and Lin→ R

out

-1 0 1 dB

-1 0 1 dB

8dB

0dB

7dB

0dB

4.5 dB

–4.0 dB

7.0 dB

– 4.5 dB

3.8 dB

–20 dB

Ω

7/21

TDA7430 - TDA7431

ELECTRICALCHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

SURROUNDSOUNDMATRIX PHASE

R

PS10

R

PS11

R

PS12

R

PS13

R

PS20

R

PS21

R

PS22

R

PS23

R

PS30

R

PS31

R

PS32

R

PS33

R

PS40

R

PS41

R

PS42

R

PS43

SPEAKER & RECORDATTENUATORS

C

range

S

STEP

E

A

V

DC

A

MUTE

R

VEA

AUDIOOUTPUTS

N

O(OFF)

N

O(MOV)

N

O(MUS)

N

O(MON)

d Distorsion Av = 0 ;V

S

C

V

OCL

R

OUT

V

OUT

BUS INPUTS

V

IL

V

IH

I

IN

V

O

Phase Shifter1: D1 = 0,D0 = 0 8.3 11.8 15.2 KΩ

Phase Shifter1: D1 = 0,D0 = 1 10 14.1 18.3 KΩ

Phase Shifter1: D1 = 1,D0 = 0 12.6 17.9 23.3 KΩ

Phase Shifter1: D1 = 1,D0 = 1 26.4 37.3 48.85 KΩ

Phase Shifter2: D3 = 0,D2 = 0 4 5.6 7.2 K

Phase Shifter2: D3 = 0,D2 = 1 4.8 6.8 8.7 KΩ

Phase Shifter2: D3 = 1,D2 = 0 6 8.4 10.9 KΩ

Phase Shifter2: D3 = 1,D2 = 1 12.9 18.3 23.7 KΩ

Phase Shifter3: D5 = 0,D4 = 0 8.5 12.1 15.6 KΩ

Phase Shifter3: D5 = 0,D4 = 1 10.2 14.5 18.7 K

Phase Shifter3: D5 = 1,D4 = 0 12.7 18.1 23.3 K

Phase Shifter3: D5 = 1,D4 = 1 27.4 39.1 50.75 KΩ

Phase Shifter4: D7 = 0,D6 = 0 8.5 12.1 15.6 KΩ

Phase Shifter4: D7 = 0,D6 = 1 10.2 14.5 18.7 KΩ

Phase Shifter4: D7 = 1,D6 = 0 12.7 18.1 23.3 K

Phase Shifter4: D7 = 1,D6 = 1 27.4 39.1 50.75 K

Control Range 79 dB

Step Resolution -0.5 1 1.5 dB

Attenuation set error Av = 0 to -20dB -1.5 0 1.5 dB

Av = -20 to -79dB -3 0 2 dB

DC Steps adjacent att.steps -3 0 3 mV

Output Mute Condition +70 100 dB

Input Impedance 21 30 39 K

Output Noise(OFF) Output Mute,Flat

B

= 20Hz to 20KHz

W

Output Noise(Movie) Mode=Movie ,

B

= 20Hz to 20KHz

W

Output Noise(Music) Mode = Music ,

B

= 20Hz to 20KHz,

W

Output Noise(Simulated) Mode = Simulated,

B

= 20Hz to 20KHz

W

= 1Vrms 0.01 0.1 %

in

4

5

30 µVrms

30 mVrms

30 µVrms

Channel Separation 70 90 dB

Clipping Level d = 0.3% 2 2.5 Vrms

Output Resistance 10 40 70 Ω

DC Voltage Level 3.8 V

Input LowVoltage 1V

Input HighVoltage 3 V

Input Current -5 +5

Output VoltageSDA

IO= 1.6mA 0.4 V

Acknowledge

Ω

Ω

Ω

Ω

Ω

Ω

Vrms

µ

µVrms

A

µ

8/21

TDA7430 - TDA7431

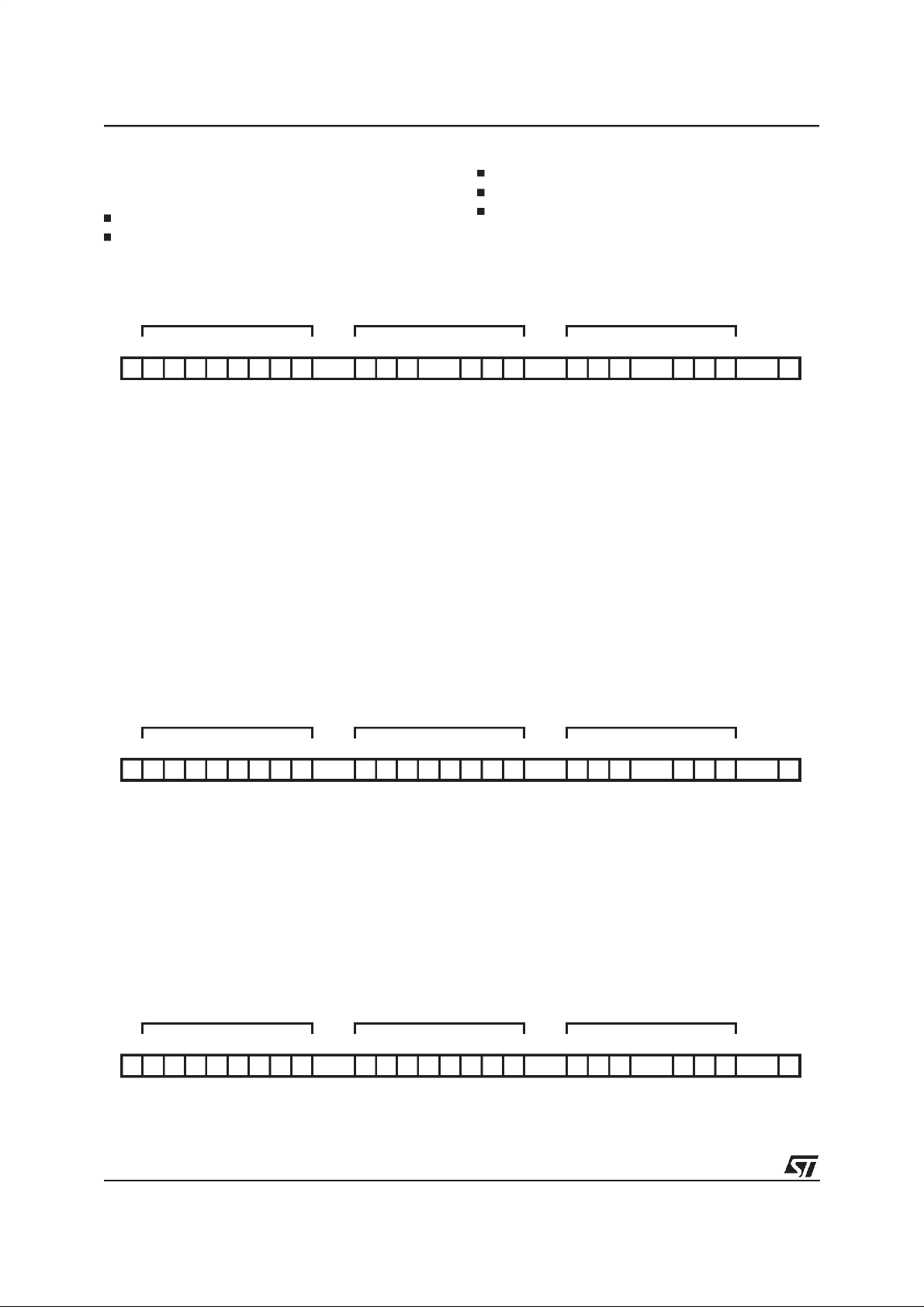

I2C BUSINTERFACE

Data transmission from microprocessor to the

TDA7430/TDA7431 and viceversa takes place

through the 2 wires I

2

C BUS interface, consisting

of the two linesSDA and SCL (pull-up resistorsto

positivesupply voltagemust be connected).

Data Validity

As shown in fig. 3, the data on the SDA line must

be stable during the high period of theclock. The

HIGH and LOW state of the data line can only

change when the clock signal on the SCL line is

LOW.

Start andStop Conditions

As shown in fig.4 a start condition is a HIGH to

LOW transition of the SDA line while SCL is

HIGH. The stop condition is a LOW to HIGHtransition of theSDA line while SCL is HIGH.

Byte Format

Every byte transferredon the SDA line must con-

tain 8 bits. Each byte must be followed by an ac-

2

Figure 3: Data Validityon theI

CBUS

knowledgebit. The MSB is transferredfirst.

Acknowledge

The master (µP) puts a resistive HIGH level onthe

SDA line during the acknowledge clock pulse (see

fig. 5). The peripheral (audioprocessor) that acknowledges has to pull-down (LOW) the SDA line

duringthisclockpulse.

The audioprocessor which has been addressed

has to generate an acknowledge after the reception of each byte, otherwise the SDA line remains

at the HIGH level during the ninth clock pulse

time. In this case the master transmitter can generate the STOP information in order to abort the

transfer.

Transmission without Acknowledge

Avoiding to detect the acknowledge of the audio-

processor,the µP canuse a simplertransmission:

simply it waits one clock without checking the

slaveacknowledging,and sendsthe new data.

This approach of course is less protected from

misworking.

Figure 4: Timing Diagram of I

2

Figure 5: Acknowledgeon the I

CBUS

2

CBUS

9/21

TDA7430 - TDA7431

SOFTWARESPECIFICATION

InterfaceProtocol

The interfaceprotocol comprises:

A startcondition(S)

/TDA7431address

A subaddressbytes

A sequenceof data(N byte+ achnowledge)

A stopcondition (P)

A chip address byte, containing the TDA7430

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S100000A0ACK ACK DATA ACK P

D95AU226A

SUBADDRESS DATA 1 to DATA n

B DATA

ACK = Achnowledge

S = Start

P = Stop

A = Address

B = AutoIncrement

EXAMPLES

No IncrementalBus

The TDA7430 /TDA7431 receives a start condi-

tion, the correct chip address, a subaddresswith

the MSB = 0 (no incremental bus), N-datas (all

these datas concern the subaddress selected), a

stop condition.

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S100000A0ACK ACK DATA ACK P

D95AU306

IncrementalBus

The TDA7430 /TDA7431 receive s a start condition, the correct chip address, a subaddresswith

the MSB = 1 (incrementalbus): now it is in a loop

condition with an autoincreaseof the subaddress

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S100000A0ACK ACK DATA ACK P

D95AU307

SUBADDRESS DATA

0D3

X X X D2 D1 D0

whereas SUBADDRESS from ”1XXX1010” to

”1XXX1111”of DATAare ignored.

The DATA 1 concern thesubaddress sent, and

the DATA 2 concern the subaddress sent plus

one in the loopetc, and at the end it receiversthe

stop condition.

SUBADDRESS DATA 1 to DATA n

1D3

X X X D2 D1 D0

10/21

TDA7430 - TDA7431

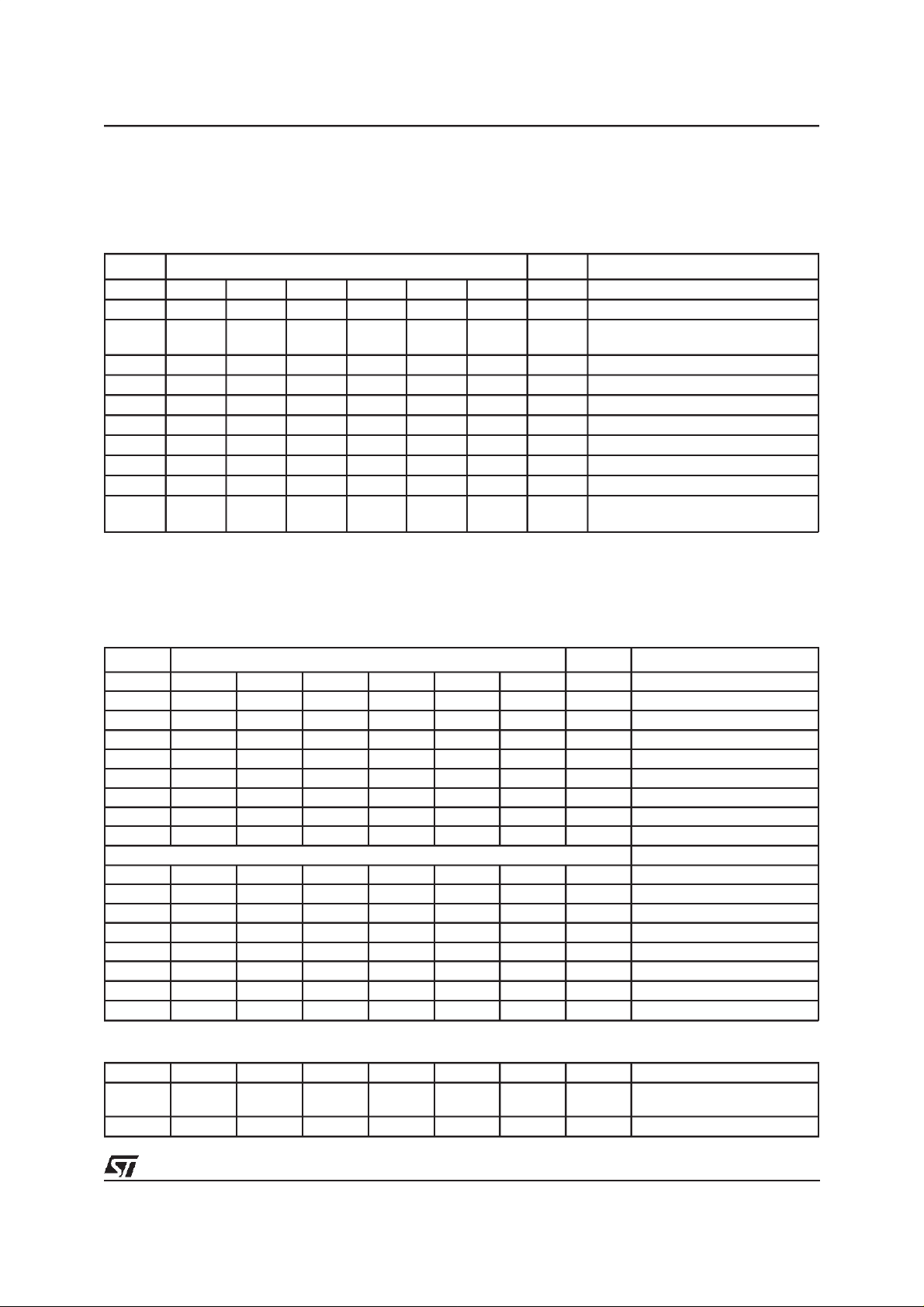

DATA BYTES

Address = 80(HEX):ADDR open;82 (HEX):need to connectsupply

FUNCTIONSELECTION:

The firstbyte (subaddress)

MSB LSB SUBADDRESS

D7 D6 D5 D4 D3 D2 D1 D0

B X X X 0 0 0 0 INPUT ATTENUATION

B X X X 0 0 0 1 SURROUND & OUT & EFFECT

B X X X 0 0 1 0 PHASE RESISTOR

B X X X 0 0 1 1 BASS & NATURAL BASE

B X X X 0 1 0 0 MIDDLE & TREBLE

B X X X 0 1 0 1 SPEAKER ATTENUATION ”L”

B X X X 0 1 1 0 SPEAKER ATTENUATION ”R”

B X X X 0 1 1 1 RECORD ATTENUATION ”L”

B X X X 1 0 0 0 RECORD ATTENUATION”R”

B X X X 1 0 0 1 INPUT MULTIPLEXER, VOICE

B = 1 incrementalbus; active

B = 0 no incremental bus;

X = indifferent 0,1

CONTROL

CANCELLER & REC OUT

INPUT ATTENUATION SELECTION

MSB LSB INPUT ATTENUATION

D7 D6 D5 D4 D3 D2 D1 D0 0.5 dB STEPS

000 0

0 0 1 -0.5

010 -1

0 1 1 -1.5

100 -2

1 0 1 -2.5

110 -3

1 1 1 -3.5

4 dB STEPS

000 0

001 -4

010 -8

011 -12

100 -16

101 -20

110 -24

111 -28

INPUT ATTENUATION= 0 ∼ -31.5dB

D7 D6 D5 D4 D3 D2 D1 D0 REAR SWITCH

0 REARIN, REAROUT PIN

1 NO REARIN,REAROUT PIN

ACTIVE

11/21

TDA7430 - TDA7431

SURROUNDSELECTION

MSB LSB

D7 D6 D5 D4 D3 D2 D1 D0 SURROUND MODE

0 0 SIMULATED

0 1 MUSIC

1 0 OFF

1 1 MOVIE

OUT

0 VAR

1 FIX

EFFECT CONTROL

0000 -6

0001 -7

0010 -8

0011 -9

0100 -10

0101 -11

0110 -12

0111 -13

1000 -14

1001 -15

1010 -16

1011 -17

1100 -18

1101 -19

1110 -20

1111 -21

PHASE RESISTOR SELECTION

MSB LSB

D7 D6 D5 D4 D3 D2 D1 D0 PHASE SHIFT 1 (KΩ)

00 12

01 14

10 18

11 37

00 6

01 7

10 8

11 18

00 12

01 14

10 18

11 39

00 12

01 14

10 18

11 39

SURROUND PHASE

RESISTOR

PHASE SHIFT 2 (KΩ)

PHASE SHIFT 3 (KΩ)

PHASE SHIFT 4 (KΩ)

12/21

TDA7430 - TDA7431

BASS SELECTION

MSB LSB BASS

D7 D6 D5 D4 D3 D2 D1 D0 2 dB STEPS

0000 -14

0001 -12

0010 -10

0011 -8

0100 -6

0101 -4

0110 -2

0111 0

1111 0

1110 2

1101 4

1100 6

1011 8

1010 10

1001 12

1000 14

NATURAL BASE

0

1

NBRIN, NBRO, NBLIN,

NBLO PINACTIVE

NO NBRIN, NBRO,NBLIN,

NBLO PIN

SPEAKER/RECORDATT. R & L SELECTION

MSB LSB SPEAKER/RECORD ATT

D7 D6 D5 D4 D3 D2 D1 D0 1 dB STEPS

000 0

001 -1

010 -2

011 -3

100 -4

101 -5

110 -6

111 -7

8 dB STEPS

0000 0

0001 -8

0010 -16

0011 -24

0100 -32

0101 -40

0110 -48

0111 -56

1000 -64

1001 -72

MUTE

101X

11XX

X = INDIFFERENT0,1

∼

SPEAKER/RECORDATTENUATION= 0dB

-79dB

13/21

TDA7430 - TDA7431

MIDDLE& TREBLE SELECTION

MSB LSB MIDDLE

D7 D6 D5 D4 D3 D2 D1 D0 2 dB STEPS

0000 -14

0001 -12

0010 -10

0011 -8

0100 -6

0101 -4

0110 -2

0111 0

1111 0

1110 2

1101 4

1100 6

1011 8

1010 10

1001 12

1000 14

TREBLE

2 dB STEPS

0000 -14

0001 -12

0010 -10

0011 -8

0100 -6

0101 -4

0110 -2

0111 0

1111 0

1110 2

1101 4

1100 6

1011 8

1010 10

1001 12

1000 14

14/21

TDA7430 - TDA7431

VOICE CANCELLER/INPUT/RECOUT L & R SELECTION

MSB LSB

D7 D6 D5 D4 D3 D2 D1 D0 VOICE CANCELLER

0 OFF

1ON

INPUT MULTIPLEXER

0 0 IN2

0 1 IN3

1 0 IN4

1 1 IN1

REC OUT ”L”

0 0 VER 1 (3BAND)

0 1 VER 2 (SURR)

1 0 VER 3 (REAR)

1 1 FIX

REC OUT ”R”

0 0 VER 1 (3BAND)

0 1 VER 2 (SURR)

1 0 VER 3 (REAR)

11 FIX

POWER ON RESET

BASS &MIDDLE 2dB

TREBLE 0dB

SURROUND & OUT CONTROL+ EFFECT CONTROL OFF + FIX + MAX ATTENUATION

SPEAKER/RECORD ATTENUATION L &R MUTE

INPUT ATTENUATION + REARN SWITCH MAX ATTENUATION + ON

NATURAL BASE OFF

VOICE CANCELER OFF

INPUT IN1

PIN: L-OUT,R-OUT, RECOUT-L, RECOUT-R

V

S

20µA

100Ω

GND

D94AU204

15/21

TDA7430 - TDA7431

PIN: HP1

LP1

HP2

V

S

GND

10K

60K

D94AU198

PIN: L-IN,R-IN, L-IN2,R-IN2, L-IN3, R-IN3,

L-IN4, R-IN4,

V

S

PIN: HP2

V

S

HP1

GND

D94AU199

PIN: VER-L, VER-R,

V

S

20µA

5.5K

60K

5.5K

PIN: CREF

V

GND

S

GND

V

REF

20K

20K

50K

42K

20µA

D94AU200

20µA

D95AU336

GND

PIN: LP1

HP1

GND

Vref

30K

V

S

20µA

SW

D95AU227

20µA

10K

D94AU211

16/21

TDA7430 - TDA7431

PIN: SCL,SDA

PIN: ADDR

GND

V

S

20µA

D94AU205

PIN: PS1,PS2,PS3, PS4LP

V

S

GND

PIN: REARIN

V

S

20µA

D95AU308

GND GND

PIN: MIX

20µA

20µA

SW

50K

D95AU228A

GND

Vref

50K

D95AU229

PIN: REAROUT,BASSO-L,BASSO-R

V

V

S

20µA

S

20µA

GND

Vref

100K

D94AU123

GND

D95AU230

17/21

TDA7430 - TDA7431

PIN: BASS-LI,BASS-R I,MID DLE- LI,MIDDLE-RI,

V

S

20µA

45K

GND

BASS-LO

BASS-RO,MIDDLE-LO,MIDDLE-RO

or

25K

: Bass

: MIDDLE

D95AU231A

PIN: TREBLE-L,TREBLE-R

V

S

20µA

PIN: BASS-LO,BASS-RO,MIDDLE-LO,MIDDLE-RO,

V

S

20µA

(*)

GND

BASS-LI,BASS-RI,MIDDLE-LI,MIDDLE-RI

(*) 45K:

Bass

25K : MIDDLE

D95AU232

PIN: VOUT REF

V

S

20µA

GND

D95AU309

PIN: NBLIN,NBRIN

V

S

D95AU234

25K

GND

10K

D95AU233A

GND

PIN: NBLO,NBRO

V

S

20µA

VREF

SWGND

GND

D95AU235A

18/21

SDIP42 PACKAGE MECHANICAL DATA

TDA7430 - TDA7431

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 5.08 0.20

A1 0.51 0.020

A2 3.05 3.81 4.57 0.120 0.150 0.180

B 0.38 0.46 0.56 0.0149 0.0181 0.0220

B1 0.89 1.02 1.14 0.035 0.040 0.045

c 0.23 0.25 0.38 0.0090 0.0098 0.0150

D 36.58 36.83 37.08 1.440 1.450 1.460

E 15.24 16.00 0.60 0.629

E1 12.70 13.72 14.48 0.50 0.540 0.570

e 1.778 0.070

e1 15.24

e2 18.54

0.60

0.730

e3 1.52 0.060

L 2.54 3.30 3.56 0.10 0.130 0.140

OUTLINE AND

MECHANICAL DATA

SDIP42 (0.600”)

E

E1

A2

A1

LA

BeB1

D

42

1

22

21

c

SDIP42

e1

e2

E

.015

0,38

Gage Plane

e3

e2

19/21

TDA7430 - TDA7431

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 1.60 0.063

A1 0.05 0.15 0.002

0.006

A2 1.35 1.40 1.45 0.053 0.055 0.057

B 0.30 0.37 0.45 0.012 0.014 0.018

C 0.09 0.20 0.004

0.008

D 12.00 0.472

D1 10.00 0.394

D3 8.00 0.315

e 0.80 0.031

E 12.00 0.472

E1 10.00 0.394

E3 8.00 0.315

L 0.45 0.60 0.75 0.018 0.024 0.030

L1 1.00 0.039

K 0°(min.), 3.5°(typ.), 7°(max.)

OUTLINE AND

MECHANICAL DATA

TQFP44 (10 x 10)

D

D1

A1

2333

34

B

44

1

e

11

TQFP4410

22

E

E1

12

L

0.10mm

.004

Seating Plane

B

K

A

A2

C

20/21

TDA7430 - TDA7431

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products

are not authorizedfor use as critical components in life support devices orsystems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

1999 STMicroelectronics –Printed in Italy– AllRights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil- China- Finland - France - Germany- Hong Kong - India - Italy - Japan - Malaysia- Malta- Morocco -

Singapore - Spain -Sweden- Switzerland - UnitedKingdom - U.S.A.

http://www.st.com

21/21

Loading...

Loading...