®

TDA7407

ADVANCED CAR SIGNAL PROCESSOR

FULLY INTEGRATED SIGNAL PROCESSOR

OPTIMIZED FOR CAR RADIO APPLICATIONS

FULLY PROGRAMMABLE BY I2C BUS

INCLUDES AUDIOPROCESSOR, STEREO -

DECODER WITH NOISE BLANKER AND

MULTIPATH DETECTOR

SOFTMUTE FUNCTION

PROGRAMMABLE ROLL-OFF COMPENSA-

TION

NO EXTERNAL COMPONE NTS

DESCRIPTION

The TDA7407 is the newcomer of the CSP family

introduced by TDA7460/61. It uses the same innovative concepts and design technologies allowing fully software programmability through I

bus and overall cost optimisation for the system

designer.

The device includes a three band audioprocessor

with configurable inputs and absence of external

BLOCK DIAGRAM

2

TQFP44

ORDERING NUMBER:

components for filter settings, a last generation

stereodecoder with multipath detector and a so-

C

phisticated stereoblend and noise cancellation

circuitry.

Strength points of the CSP approach are flexibility

and overall cost/room saving in the application,

combined with high performances.

TDA7407

June 2001

1/30

TDA7407

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

S

T

amb

T

stg

SUPPLY

Symbol Parameter Test Condition Min. Typ. Max. Unit

V

S

I

S

SVRR Ripple Rejection @ 1KHz Audioprocessor (all filters flat) 50 60 dB

ESD

All pins are protected against ESD according to the MIL883 standard.

PIN CONNECTION

Operating Supply Voltage 10.5 V

Operating Ambient Temperature Range -40 to 85 °C

Operating Storage Temperature Range -55 to 150 °C

Supply Voltage 7.5 9 10 V

Supply Current VS = 9V 30 35 40 mA

Stereodecoder + Audioprocessor 45 55 dB

THERMAL DATA

CDR

CDROUT

CDGND

CDLOUT

CDL

N.C.

PHONE-

PHONE+

AFS

AM

N.C.

TAPE L

CREF

N.C.

LEVEL

REF

V

ACINRF

ACINLF

ACINRR

171118 19 20 21 22

N.C.

MPIN

MPOUT

MUXL

ACINLR

MUXR

TAPE R

44 43 42 41 3940 38 37 36 35 34

1

2

3

4

5

6

7

8

9

10

12 13 14 15 16

MPX

N.C.

N.C.

ACOUTL

ACOUTR

33

32

31

30

29

28

27

26

25

24

23

PINCON-TDA7407

QUAL

SMUTE

N.C.

OUT LF

OUT RF

OUT LR

OUT RR

N.C.

V

S

GND

N.C.

SDA

SCL

Symbol Parameter Value Unit

R

th-j pins

Thermal Resistance Junction-pins Max 85 °C/W

2/30

TDA740 7

PIN DESCRIPTION

N. Name Function Type

1 CDR CD Right Channel Input I

2 CDROUT CD Output Right Channel O

3 CDGND CD Input Common Ground I

4 CDLOUT CD Output Left Channel O

5 CDL CD Input Left Channel I

6nc 7 PH - Differential Phone Input - I

8 PH + Differential Phone Input + I

9 AFS AFS Drive I

10 AM AM Input I

11 nc 12 MPX FM Stereodecoder Input I

13 nc 14 LEVEL Level Input Stereodecoder I

15 MPIN Multipath Input I

16 MPOUT Multipath Output O

17 nc 18 MUXL Multiplexer Output Left Channel O

19 MUXR Multiplexer Output Right Channel O

20 nc 21 QUAL Stereodecoder Quality Output O

22 SMUTE Soft Mute Drive I

23 SCL I

24 SDA I

25 nc 26 GND Supply Ground S

27 VS Supply Voltage S

28 nc 29 OUTRR Right Rear Speaker Output O

30 OUTLR Left Rear Speaker Output O

31 OUTRF Right Front Spaeaker Output O

32 OUTLF Left Front Speaker Output O

33 nc 34 ACOUTR Pre-speaker AC Output Right Channel O

35 ACOUTL Pre-speaker AC Output Left Channel O

36 nc 37 ACINLR Pre-speaker Input Left Rear Channel I

38 ACINRR Pre-speaker Input Right Rear Channel I

39 ACINRF Pre-speaker Input Right Front Channel I

40 ACINLF Pre-speaker Input Left Front Channel I

41 VREF Reference Voltage Output O

42 CREF Reference Capacitor Pin S

43 TAPEL Tape Input Left I

44 TAPER Tape Input Right I

Pin type legenda: I = Input O = Output I/O = Input/Output S = Supply nc = not connected

2

C Clock Line I

2

C Data Line I/O

3/30

TDA7407

AUDIO PROCESSOR PART

Input Multiplexer

Quasi-differential CD and cassette stereo input

AM mono input

Phone differential input

Multiplexer signal after In-Gain available at

separate pins

Volume control

1dB attenuator

Max. gain 15dB

Max. attenuation 79dB

Bass Control

2nd order frequency response

Center frequency programmable in 4(5) steps

DC gain programmable

±15 x 1dB steps

ELECTRICAL CHARACTERISTICS (V

S

= 9V; T

unless otherwise specified).

Mid Control

2nd order frequency response

Center frequency programmable in 4 steps

Q-factor programmable in 2 steps

±15 x 1dB steps

Treble Control

2nd order frequency response

Center frequency programmable in 4 steps

±15 x 1dB steps

Speaker Control

4 independent speaker controls in 1dB steps

max gain 15dB

max. attenuation 79dB

Mute Functions

Direct mute

Digitally controlled softmute with 4 programmable

mute time.

amb

= 25°C; RL = 10KΩ; all gains = 0dB; f = 1KHz;

Symbol Parameter Test Condition Min. Typ. Max. Unit

INPUT SELECTOR

G

G

G

R

in

V

CL

S

IN

IN MIN

IN MAX

STEP

V

DC

Input Resistance all inputs except Phone 70 100 130 K

Clipping Level 2.2 2.6 V

Input Separation 80 100 dB

Min. Input Gain -1 0 1 dB

Max. Input Gain 13 15 17 dB

Step Resolution 0.5 1 1.5 dB

DC Steps Adjacent Gain Step -5 0.5 5 mV

G

MIN

to G

MAX

-10 5 10 mV

DIFFERENTIAL CD STEREO INPUT

R

in

CMRR Common Mode Rejection Ratio V

e

N

Input Resistance Differential 70 100 130 K

Common Mode 70 100 130 K

Output Noise @ Speaker

Outputs

= 1

CM

V

= 1

CM

20Hz to 20KHz flat; all stages

0dB

@ 1KHz 45 70 dB

VRMS

@ 10KHz 45 60 dB

VRMS

615

DIFFERENTIAL PHONE INPUT

R

in

CMRR Common Mode Rejection Ratio V

Input Resistance Differential 40 56 K

= 1

CM

V

= 1

CM

@ 1KHz 40 70 dB

VRMS

@ 10KHz 40 60 dB

VRMS

VOLUME CONTROL

G

A

A

MAX

MAX

STEP

E

A

Max Gain 13 15 17 dB

Max Attenuation 70 79 dB

Step Resolution 0.5 1 1.5 dB

Attenuation Set Error G = -20 to 20dB -1.25 0 1.25 dB

G = -60 to 20dB -4 0 3 dB

Ω

RMS

Ω

Ω

V

µ

Ω

4/30

TDA740 7

ELECTRICAL CHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

E

T

V

DC

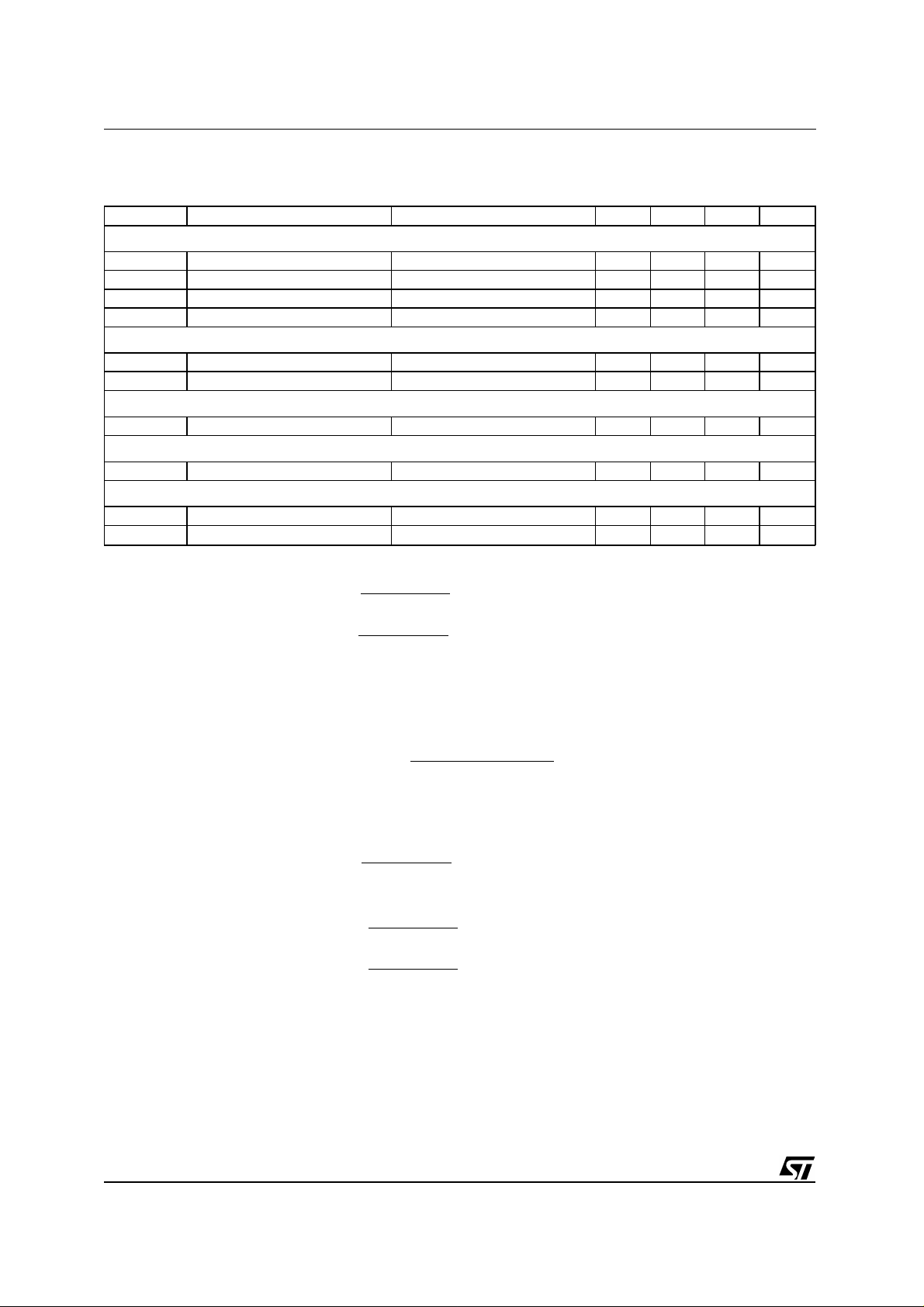

SOFT MUTE/AFS

A

MUTE

T

D

V

TH low

V

TH high

R

PD

BASS CONTROL

C

RANGE

A

STEP

f

C

Q

BASS

DC

GAIN

MID CONTROL

C

RANGE

A

STEP

f

C

Q

MID

TREBLE CONTROL

C

RANGE

A

STEP

f

C

1) The SM pin is active low (Mute = 0)

2) See note in Programming Part

Tracking Error 2dB

DC Steps Adjacent Attenuation Steps 0.1 3 mV

From 0dB to G

MIN

0.5 5 mV

Mute Attenuation 80 100 dB

Delay Time T1 0.48 ms

T2 0.96 ms

T3 40.4 ms

T4 324 ms

Low Threshold for SM-/AFS- Pin

1

1V

High Threshold for SM-/AFS-Pin 2.5 V

Internal Pull-up Resistor 45 K

Control Range

13

±

15

±

17 dB

±

Step Resolution 0.5 1 1.5 dB

Center Frequency f

Quality Factor Q

C1

f

C2

f

C3

f

C4

1

Q

2

Q

3

Q

4

54 60 66 Hz

63 70 77 Hz

72 80 88 Hz

90 100

(150)

(2)

110 Hz

0.9 1 1.1

1.11.251.4

1.3 1.5 1.7

1.8 2 2.2

Bass-Dc-Gain DC = off -1 0 1 dB

DC = on 3.5 4.4 5.5 dB

Control Range

13

±

15

±

17 dB

±

Step Resolution 0.5 1 1.5 dB

Center Frequency f

Quality Factor Q

Control Range

C1

f

C2

f

C3

f

C4

1

Q

2

450 500 550 Hz

0.9 1 1.1 kHz

1.35 1.5 1.65 kHz

1.8 2 2.2 kHz

0.9 1 1.1

1.8 2 2.2

13

±

15

±

17 dB

±

Step Resolution 0.5 1 1.5 dB

Center Frequency f

C1

f

C2

f

C3

f

C4

8 10 12 KHz

10 12.5 15 KHz

12 15 18 KHz

14 17.5 21 KHz

Ω

5/30

TDA7407

ELECTRICAL CHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

SPEAKER AT T ENUATORS

R

IN

G

MAX

A

MAX

A

STEP

A

MUTE

E

E

V

DC

AUDIO OUTPUTS

V

CLIP

R

L

C

L

R

OUT

V

DC

GENERAL

e

NO

S/N Signal to Noise Ratio all gain = 0dB flat; VO = 2V

d Distortion VIN = 1V

S

C

E

T

BUS INPUT S

V

IL

V

IH

I

IN

V

O

Input Impedance 35 50 65 K

Max Gain 13 15 17 dB

Max Attenuation -70 -79 dB

Step Resolution 0.5 1 1.5 dB

Output Mute Attenuation 80 90 dB

Attenuation Set Error

2dB

±

DC Steps Adjacent Attenuation Steps 0.1 5 mV

Clipping Level d = 0.3% 2.2 2.6 V

Output Load Resistance 2 K

Output Load Capacitance 10 nF

Output Impedance 30 120

DC Voltage Level 4.3 4.5 4.7 V

Output Noise BW = 20 Hz to 20 KHz

315

output muted

BW = 20 Hz to 20 KHz

6.5 15

all gain = 0dB

102 110 dB

96 100 dB

bass treble at 12dB;

a-weighted; V

= 1V

V

IN

= 2.6V

O

; all stages 0dB 0.002 0.1 %

RMS

; Bass & Treble = 12dB 0.05 0.1 %

RMS

RMS

RMS

Channel separation Left/Right 80 100 dB

Total Tracking Error AV = 0 to -20dB -1 0 1 dB

= -20 to -60dB -2 0 2 dB

A

V

Input Low Voltage 0.8 V

Input High Voltage 2.5 V

Input Current VIN = 0.4V -5 5

Output Voltage SDA

IO = 1.6mA 0.4 V

Acknowledge

Ω

RMS

Ω

Ω

V

µ

V

µ

A

µ

6/30

Stereodecoder Part

TDA7407

ELECTRICAL CHARACTERISTICS (V

MPX

= 500mV(75KHz deviation), fm= 1KHz, Gv = 6dB, T

V

S

= 9V; deemphasis time constant = 50µs,

amb

= 27°C; unless otherwise specified).

Symbol Parameter Test Condition Min. Typ. Max. Unit

V

in

R

in

G

MIN

G

MAX

G

STEP

SVRR Supply Voltage Ripple

MPX Input Level Gv = 3.5dB 0.5 1.25 V

Input Resistance 70 100 130 K

Min. Input Gain 1.5 3.5 4.5 dB

Max. Input Gain 8.5 11 12.5 dB

Step Resolution 1.75 2.5 3.25 dB

= 100mV; f = 1KHz 35 60 dB

V

ripple

Rejection

α

Max. channel Separation 30 50 dB

THD Total Harmonic Distortion 0.02 0.3 %

S+N

N

Signal plus Noise to Noise

Ratio

A-weighted, S = 2V

rms

80 91 dB

MONO/STEREO-SWITCH

V

PTHST1

V

PTHST0

V

PTHMO1

V

PTHMO0

Pilot Threshold Voltage for Stereo, PTH = 1 10 15 25 mV

Pilot Threshold Voltage for Stereo, PTH = 0 15 25 35 mV

Pilot Threshold Voltage for Mono, PTH = 1 7 12 17 mV

Pilot Threshold Voltage for Mono, PTH = 1 10 19 25 mV

PLL

f/f Capture Range 0.5 %

∆

RMS

Ω

DEEMPHASIS and HIGHCUT

τ

τ

τ

τ

HC50

HC75

HC50

HC75

Deemphasis Time Constant Bit 7, Subadr, 10 = 0,

V

>> V

LEVEL

HCH

Deemphasis Time Constant Bit 7, Subadr, 10 = 1,

V

>> V

LEVEL

HCH

Highcut Time Constant Bit 7, Subadr, 10 = 0,

V

>> V

LEVEL

HCL

Highcut Time Constant Bit 7, Subadr, 10 = 1,

V

>> V

LEVEL

HCL

25 50 75

50 75 100

100 150 200

150 225 300

STEREOBLEND-and HIGHCUT-CONT ROL

REF5V Internal Reference Voltage 4.7 5 5.3 V

TC

REF5V

L

Gmin

L

Gmax

L

Gstep

VSBL

VSBL

VSBL

VHCH

VHCH

VHCH

VHCL

VHCL

VHCL

Temperature Coefficient 3300 ppm

Min. LEVEL Gain -1 0 1 dB

Max. LEVEL Gain 8 10 12 dB

LEVEL Gain Step Resolution 0.3 0.67 1 dB

Min. Voltage for Mono 25 29 33 %REF5V

min

Min. Voltage for Mono 54 58 62 %REF5V

max

Step Resolution 2.2 4.2 6.2 %REF5V

step

Min. Voltage for NO Highcut 38 42 46 %REF5V

min

Min. Voltage for NO Highcut 62 66 70 %REF5V

max

Step Resolution 5 8.4 12 %REF5V

step

Min. Voltage for FULL Highcut 12 17 22 %VHCH

min

Max. Voltage for FULL Highcut 28 33 38 %VHCH

max

Step Resolution 2.2 4.2 6.2 %VHCH

step

s

µ

s

µ

s

µ

s

µ

7/30

TDA7407

ELECTRICAL CHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

Carrier and harmonic suppression at the output

19 Pilot Signal f = 19KHz 40 50 dB

α

38 Subcarrier f = 38KHz 75 dB

α

57 Subcarrier f = 57KHz 62 dB

α

α76

Intermodulation (Note 1)

2f

α

3f

α

Traffic Ratio (Note 2)

57 Signal f = 57KHz 70 dB

α

SCA - Subsidiary Communications Authoorization (Note 3)

67 Signal f = 67KHz 75 dB

α

ACI - Adjacent Channel Interference (Note 4)

114 Signal f = 114KHz 95 dB

α

190 Signal f = 190KHz 84 dB

α

Notes to the characteristics:

1. Intermodulation Suppression: α2 =

α3 =

measured with: 91% pilot signal; fm = 10kHz or 13kHz.

Subcarrier f = 76KHz 90 dB

= 10KHz, f

mod

= 13KHz, f

mod

= 1KHz 65 dB

spur

= 1KHz 75 dB

spur

V

O(signal)(at1KHz

V

O(spurious)(at

V

O(signal)(at1KHz

V

O(spurious)(at

)

; fs = (2 x 10KHz) − 19KHz

1KHz

)

)

; fs = (3 x 13KHz) − 38KHz

1KHz

)

2. Traffic Radio (V.F.) Suppression: measured with: 91% stereo signal; 9% pilot signal; fm=1kHz; 5% subcarrier (f = 57kHz,

fm = 23Hz AM, m = 60%)

α57 (V.W>F.

) =

V

O

(

spurious

O

at

)(

1KHz

(

+

23KHz

⁄

−

)

)

V

signal)(at1KHz

3. SCA ( Subsidiary Communications Authorization ) measured with: 81% mono signal; 9% pilot signal; fm = 1kHz; 10%SCA - subcarrier

( fs = 67kHz, unmodulated ).

V

O

at1KHz

(

)(

α67

signal

=

V

O

(

spurious

)(

9KHz

at

)

F

;

= (2 x 38KHz) −67KHz

S

)

4. ACI ( Adjacent Channel Interference ): α114 =

α190 =

O(signal)(at1KHz

V

O(spurious)(at

V

O(signal)(at1KHz

V

O(spurious)(at

)

; FS = 110KHz − (3 x 38KHz

4KHz

)

)

; FS = 186KHz − (5 x 38KHz

4KHz

)

)

)

V

measured with: 90% mono signal; 9% pilot signal; fm =1kHz; 1% spurious signal ( fs = 110kHz or 186kHz, unmodulated).

8/30

NOISE BLANKER PART

TDA7407

internal 2nd order 140kHz high pass filter

programmable trigger threshold

trigger threshold dependent on high frequency

noise with programmable gain

additional circuits for deviation and field-

very low offset current during hold time due to

opamps wMOS inputs

four selectable pulse suppression times

programmable noise rectifier charge/discharge

current

strength dependent trigger adjustment

ELECTRICAL CHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

V

TR

V

TRNOISE

Trigger Threshold

Noise Controlled Trigger

Threshold

V

RECT

V

RECT DEV

Rectifier Voltage V

deviation dependent

rectifier Voltage

V

RECT FS

Fieldstrength Controlled

Rectifier Voltage

T

V

RECTADJ

S

Suppression Pulse

Duration

5)

Noise Rectifier

discharge adjustment

SR

PEAK

(c) = by design/characterization functionally guaranteed through dedicated test mode structure

Noise Rectifier Charge Signal PEAK in

0) 1)

meas. with V

= 0.9V NBT = 111 (c) 30 (c) mV

PEAK

NBT = 110 (c) 35 (c) mV

NBT = 101 (c) 40 (c) mV

NBT = 100 (c) 45 (c) mV

NBT = 011 (c) 50 (c) mV

NBT = 010 (c) 55 (c) mV

NBT = 001 (c) 60 (c) mV

NBT = 000 (c) 65 (c) mV

2)

meas. with V

= 1.5V NCT = 00 (c) 260 (c) mV

PEAK

NCT = 01 (c) 220 (c) mV

NCT = 10 (c) 180 (c) mV

NCT = 11 (c) 140 (c) mV

= 0mV NRD

MPX

= 50mV; f = 150KHz 1.5 1.7 2.1 V

V

MPX

= 200mV; f = 150KHz 2.2 2.5 2.9 V

V

MPX

3)

means. with

V

= 800mV

MPX

(75KHz dev.)

6)

= 00 0.5 0.9 1.3 V

OVD = 11 0.5 0.9(off) 1.3 V

OVD = 10 0.9 1.2 1.5 V

OVD = 01 1.7 2.0 2.3 V

OVD = 00 2.5 2.8 3.1 V

4)

means. with

V

= 0mV

MPX

V

<< V

LEVEL

SBL

(fully mono)

Signal HOLDN

in Testmode

FSC = 11 0.5 0.9(off) 1.3 V

FSC = 10 0.9 1.4 1.5 V

FSC = 01 1.7 1.9 2.3 V

FSC = 00 2.1 2.4 3.1 V

BLT = 00 TBD 38 TBD

BLT = 10 TBD 32 TBD

BLT = 01 TBD 25.5 TBD

BLT = 00 TBD 22 TBD

Signal PEAK in

6)

Testmode

Testmode

NRD = 00

NRD = 01

NRD = 10

NRD = 11

PCH = 0

PCH = 1

6)

(c) 0.3 (c) V/ms

6)

(c) 0.8 (c) V/ms

6)

(c) 1.3 (c) V/ms

6)

(c) 2.0 (c) V/ms

7)

(c) 10 (c) mV/µs

7)

(c) 20 (c) mV/µs

OP

OP

OP

OP

OP

OP

OP

OP

OP

OP

OP

OP

OP

OP

OP

OP

s

µ

s

µ

s

µ

s

µ

9/30

TDA7407

ELECTRICAL CHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

V

ADJMP

Noise Rectifier adjustment

through Multipath

8)

Signal PEAK in

Testmode

0) All Thresholds are measured using a pulse with TR =2µs, T

1) NBT represents the Noiseblanker Byte bits D

2) NAT represents the Noiseblanker Byte bit pair D

3) OVD represents the Noiseblanker Byte bit pair D

4) FSC represents the Fieldstrength Byte bit pair D

5) BLT represents the Speaker RR Byte bit pair D

6) NRD represents the Configuration-Byte bit pair D

7) PCH represents the Stereodecoder-Byte bit D

8) MPNB represents the HighC ut-Byte bit D

V

IN

, D0 for the noise blanker trigger threshold

2

, D3 for the noise controlled triggeradjustment

4

, D6 for the over deviation detector

7

, D0 for the fieldstrength control

1

, D6 for the blanktime adjustment

7

1

, D0 for the noise rectifier discharge-adj ustment

5

for the noise rectifier charge-current adjustment

7

and the Fieldstrength-Byte D7 for the noise rectifier multipath adjustment

V

OP

MPNB = 00

MPNB = 01

MPNB = 10

MPNB = 11

HIGH

= 2µs and TF = 10µs. The repetition rate must not increase the PEAK voltage.

8)

(c) 0.3 (c) V/ms

8)

(c) 0.5 (c) V/ms

8)

(c) 0.7 (c) V/ms

8)

(c) 0.9 (c) V/ms

DC

D97AU636

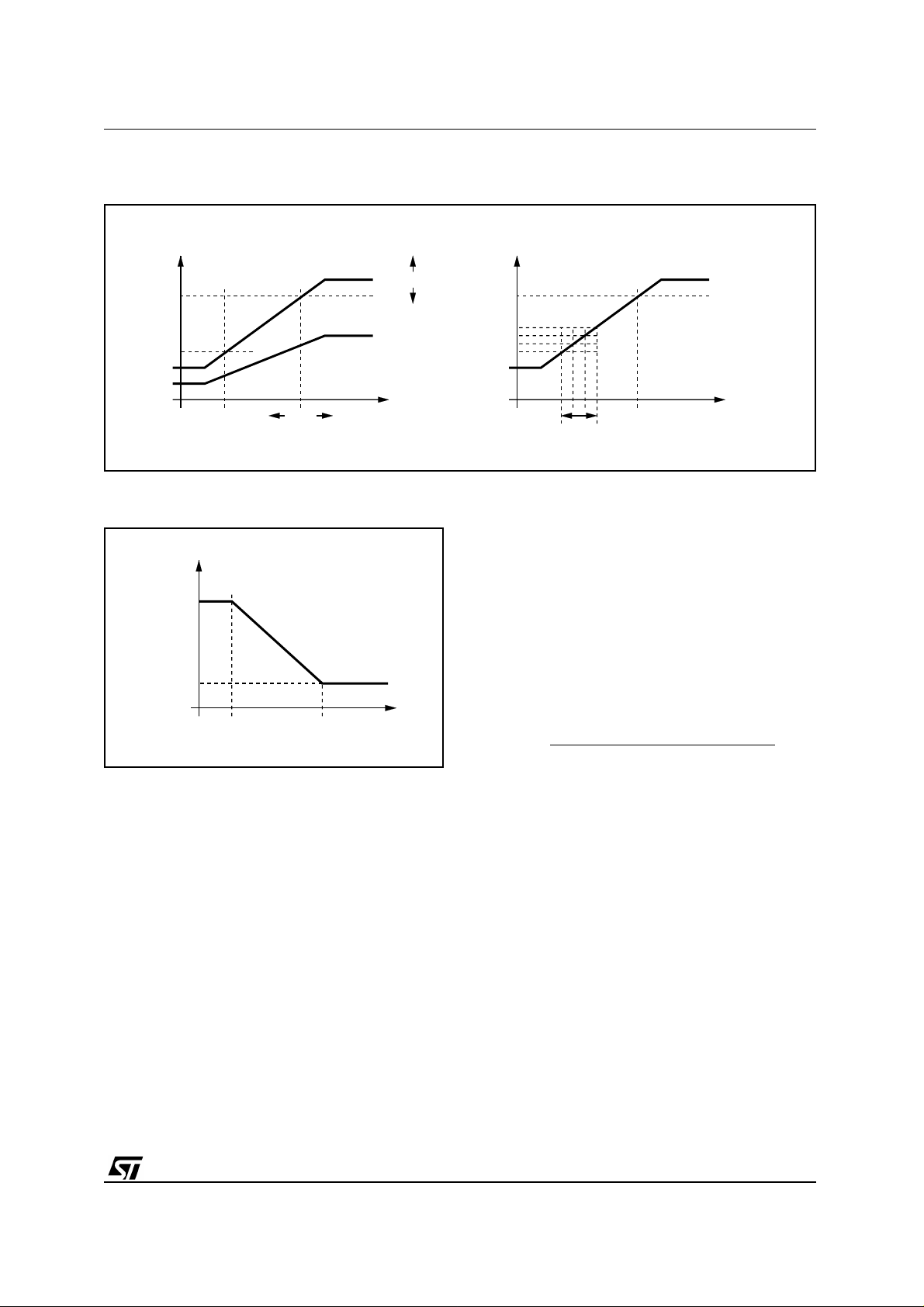

Figure 1. Trigger Threshold vs.V

VTH

MIN. TRIG. THRESHOLD

65mV

8 STEPS

30mV

0.9V

D97AU648

T

R

PEAK

NOISE CONTROLLED

TRIG. THRESHOLD

1.5V

T

HIGH

V

PEAK(V)

260mV(00)

220mV(01)

180mV(10)

140mV(11)

T

F

Time

Figure 2. Deviation Controlled Trigger Adjust-

ment

V

PEAK

(V

)

OP

00

2.8

2.0

1.2

0.9

D97AU649

20

32.5 45 75

01

10

DETECTOR OFF (11)

DEVIATION(KHz)

10/30

Figure 3. Fieldstrength Controlled Trigger Adjustment

V

PEAK

MONO STEREO

»3V

NOISE

ATC_SB OFF (11)

2.4V(00)

1.9V(01)

1.4V(10)

TDA7407

0.9V

Multipath Detector

Internal 19kHz band pass filter

noisy signal good signal

D97AU650

two pin solution fully independent usable for

external programming

selectable internal influence on Stereoblend

E'

Programmable band pass and rectifier gain

ELECTRICAL CHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

f

CMP

G

G

RECTMP

I

CHMP

I

DISMP

BPMP

Center Frequency of MultipathBandpass

Bandpass Gain bits D2, D1 configuration byte = 00 6 dB

Rectifier Gain bits D7, D6 configuration byte = 00 7.6 dB

Rectifier Charge Current bit D5 configuration byte = 0 0.5

Rectifier Discharge Current 0.5 1 1.5 mA

stereodecoder locked on Pilottono 19 KHz

bits D2, D1 configuration byte = 10 12 dB

bits D2, D1 configuration byte = 01 16 dB

bits D2, D1 configuration byte = 11 18 dB

, D6 configuration byte = 01 4.6 dB

bits D

7

bits D7, D6 configuration byte = 10 0 dB

bits D7, D6 configuration byte = 11 off dB

bit D5 configuration byte = 1 1.0

A

µ

A

µ

Quality Detector

Symbol Parameter Test Condition Min. Typ. Max. Unit

A Multipath Influence Factor Addr. 12 / Bit 5+6 00

01

10

11

B Noise Influence Factor Addr. 16 / Bit 1+2 00

01

10

11

0.7

0.85

1.00

1.15

15

12

9

6

dB

dB

dB

dB

dB

dB

dB

dB

11/30

TDA7407

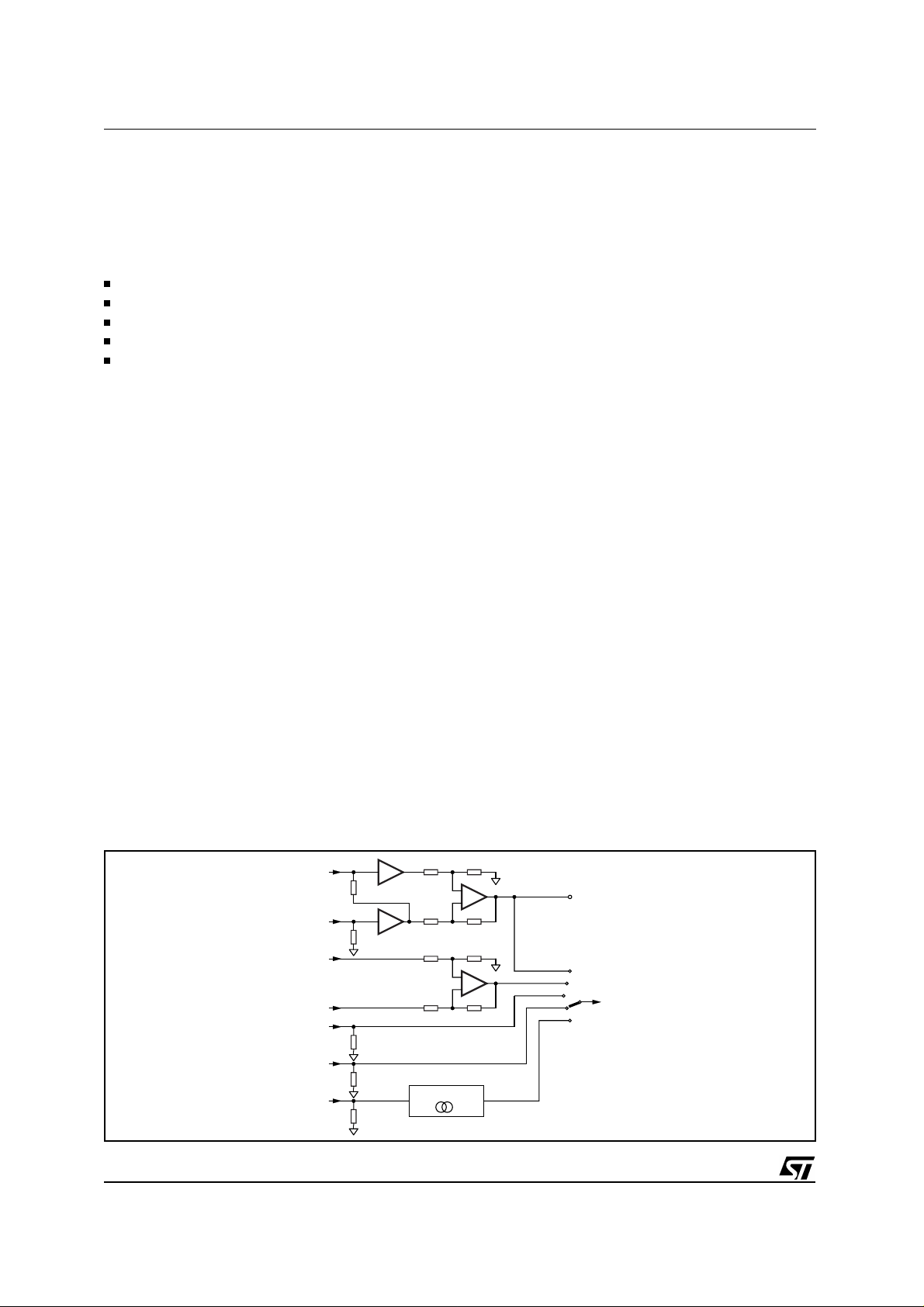

DESCRIPTION OF THE AUDIOPROCESSOR

PART

Input Multiplexer

CD quasi differential

Cassette stereo

Phone differential

AM mono

Stereodecoder input.

Input stages

Most of the input stages have remained the same

as in preceeding ST audioprocessors with exception of the CD inputs (see figure 4).

In the meantime there are some CD players in

the market having a significant high source impedance which affects strongly the commonmode rejection of the normal differential input

stage. The additional buffer of the CD input

avoids this drawback and offers the full commonmode rejection even with those CD players.

The output of the Cd stage is permanently available of the Cd out-pins

AutoZero

In order to reduce the number of pins ther e is no

AC coupling between the In-Gain and the following stage, so that any offset generated by or before the In-Gain stage would be transferred or

even amplified to the output.

To avoid that ef fect a special offset cancellation

stage called AutoZero is implemented.

This stage is located before the volume-block to

eliminate all offsets generated by the Stereodecoder, the Input Stage and the In-Gain (Please

notice that externally generated offsets, e.g. generated through the leakage current of the coupling capacitors, are not cancelled).

The auto-zeroing is started every t ime the DATABYTE 0 is selected and takes a time of max.

0.3ms. To avoid audible clicks the audioprocessor is muted before the volume stage during this

time.

AutoZero Remain

In some cases, for example if the µP is executing

a refresh cycle of the I

2

C bus programming, it is

not useful to start a new AutoZero action because

no new source is selected and an undesired mute

would appear at the outputs. For such applications the TDA7407 could be switched in the "Auto

Zero Remain mode" (Bit 6 of the subaddress

byte). If this bit is set to high, the DATABYTE 0

could be loaded without invoking the AutoZero

and the old adjustment value remains.

Multiplexer Output

The output signal of the Input Multiplexer is available at separate pins (please see the Blockdiagram). This signal represents the input signal amplifier by the In Gain stage and is also going into

the Mixer stage.

Softmute

The digitally controlled softmute stage allows

muting/demuting the signal with a I

grammable slope. The mute process can either

be activated by the softmute pin or by the I

2

C bus pro-

2

bus. The slope is realized in a special S shaped

curve to mute slow in the critical regions (see fig-

C

Figure 4. Input stages

12/30

CD+

PHONE+

PHONE-

CASSETTE

AM

MPX

15K 15K

100K

100K

100K

1

1

+

-

15K 15K

15K 15K

+

-

15K 15K

STEREODECODER

CD OUT

IN GAIN

D98AU854A

100K

CD-

100K

TDA740 7

Figure 5. Soft m ute Timing

1

EXT.

MUTE

+SIGNAL

REF

-SIGNAL

1

2

I

C BUS

OUT

Note: Please notice that a start ed Mute act i on is alway s ter minated

and could not be interrupted by a change of the mute signal.

D97AU634

Time

ure 5).

For timing purposes the Bit 3 of the I

2

C bus output register is set to 1 from the start of muting until the end of demuting.

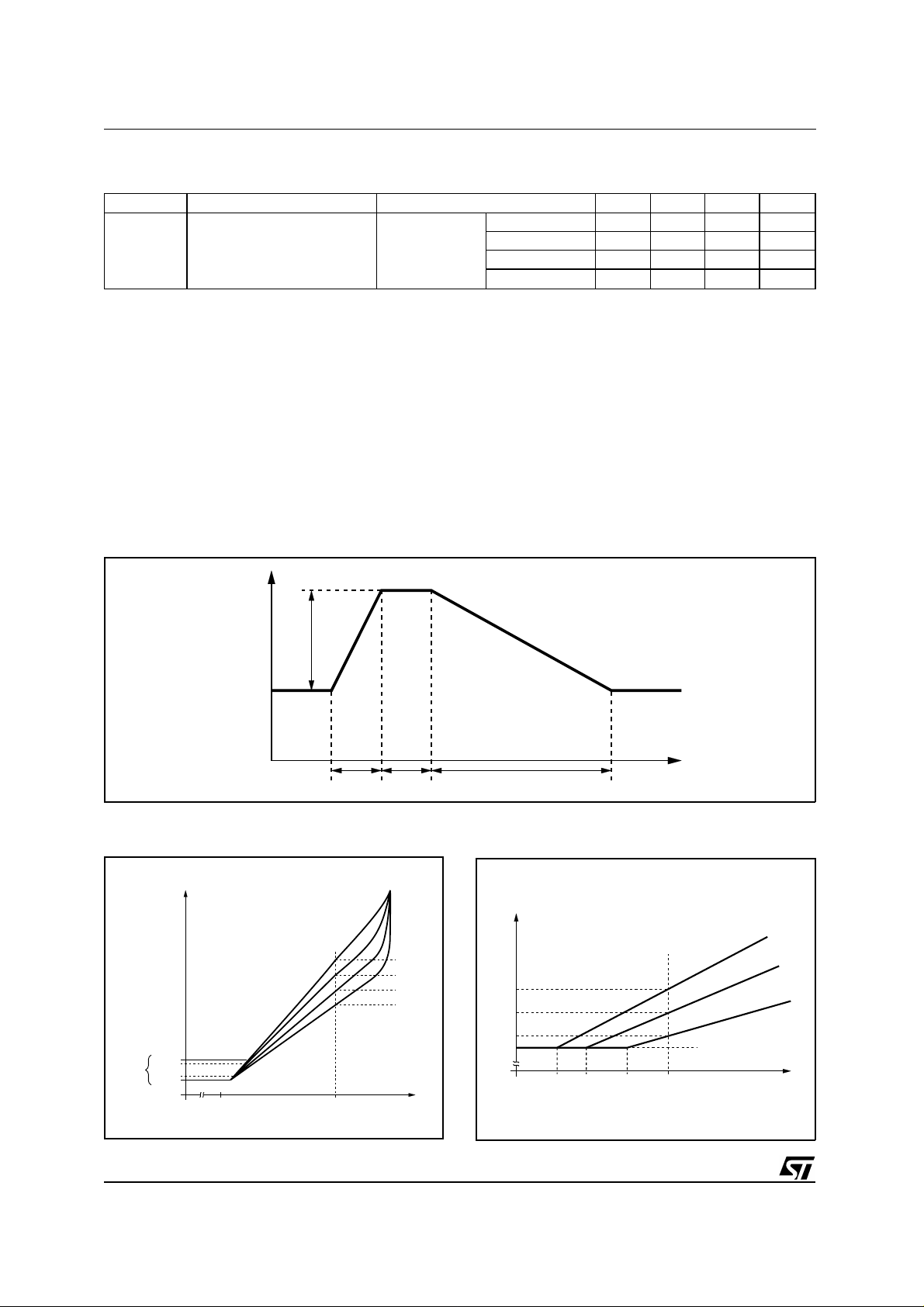

BASS

There are four parameters programmable in the

bass stage: (see figs 6, 7, 8, 9):

Attenuation

Figure 6 shows the attenuation as a function of

frequency at a center frequency at a center frequency of 80Hz.

Center Frequency

Figure 7 shows the four possible center frequencies 60,70,80 and 100Hz.

Quality Factors

Figure 8 shows the four possible quality factors 1,

1.25, 1.5 and 2.

frequency at a center frequency of 1kHz.

Center Frequency

Figure 11 shows the four possible center frequencies 500Hz, 1kHz, 1.5kHz and 2kHz.

Quality Fac tor

Figure 12 shows the two possible quality f actors

1 and 2 at a center frequency of 1kHz.

TREBLE

There are two parameters programmable in the

treble stage (see figs 13, 14):

Attenuation

Figure 13 shows the attenuation as a f unction of

frequency at a center frequency of 17.5KHz.

Center Frequency

Figure 14 shows the four possible Center Frequency (10, 12.5, 15 and 17.5kHz).

AC Coupling

In some applications additional signal manipulations are desired, for example surround-sound or

more-band-equalizing.

For this purpose a AC-Coupling is placed before

the Speaker-attenuators, which can be activated

or internally shorted by Bit7 in the Bass/TrebleConfiguration byte. In short condition the inputsignal of the speaker-attenuator is available at

AC Outputs and the AC Input could be used as

additional stereo inputs. The input impedance of

the AC Inputs is always 50KΩ.

Speaker Attenuator

The speaker attenuators have exactely the same

Figure 6. Bass Control @ fc = 80Hz, Q = 1

15.0

DC Mode

In this mode the DC gain is incre ased by 5.1dB. In ad dition the progr ammed center frequency a nd quality

factor is decreased by 25% which can be used to

reach alternative center frequencies or quality factors.

MID

There are 3 parameters programmable in the mid

stage (see figs. 10, 11 & 12)

Attenuation

Figure 10 shows the attenuation as a function of

10.0

5.0

0.0

-5.0

-10.0

-15.0

10.0 100.0 1.0K 10.0K

13/30

TDA7407

Figure 7. Bass Center @ Gain = 14dB, Q = 1

15.0

12.5

10.0

7.5

5.0

2.5

0.0

10.0 100.0 1.0K 10.0K

Figure 9. Bass normal and DC Mode @ Gain =

14dB, fc = 80Hz

15.0

12.5

10.0

Figure 8. Bass Quality factors @ Gain = 14dB,

fc = 80Hz

15.0

12.5

10.0

7.5

5.0

2.5

0.0

10.0 100.0 1.0K 10.0K

Figure 10. Mid Control @ fc=1kHz, Q=1

15.0

10.0

7.5

5.0

2.5

0.0

10.0 100.0 1.0K 10.0K

Note: In general the center frequency, Q and DC-mode can be set

independently. The exception from this rule is the mode (5/xx1111xx)

where the center frequency is set to 150Hz instead of 100Hz.

Figure 11. Mid Center Frequency @

Gain=14d B, Q1

15.0

12.5

10.0

7.5

5.0

5.0

0.0

-5.0

-10.0

-15.0

10.0 100.0 1.0K 10.0K

Figure 12. Mid Q-factor @ fc=1kHz, Gain=14dB

15.0

12.5

10.0

7.5

5.0

2.5

0.0

10.0 100.0 1.0K 10.0K

14/30

2.5

0.0

10.0 100.0 1.0K 10.0K

TDA7407

Figure 13. Treble Control @ fc = 17.5KHz

15.0

10.0

5.0

0.0

-5.0

-10.0

-15.0

10.0 100.0 1.0K 10.0K

structure and range like the Volume stage.

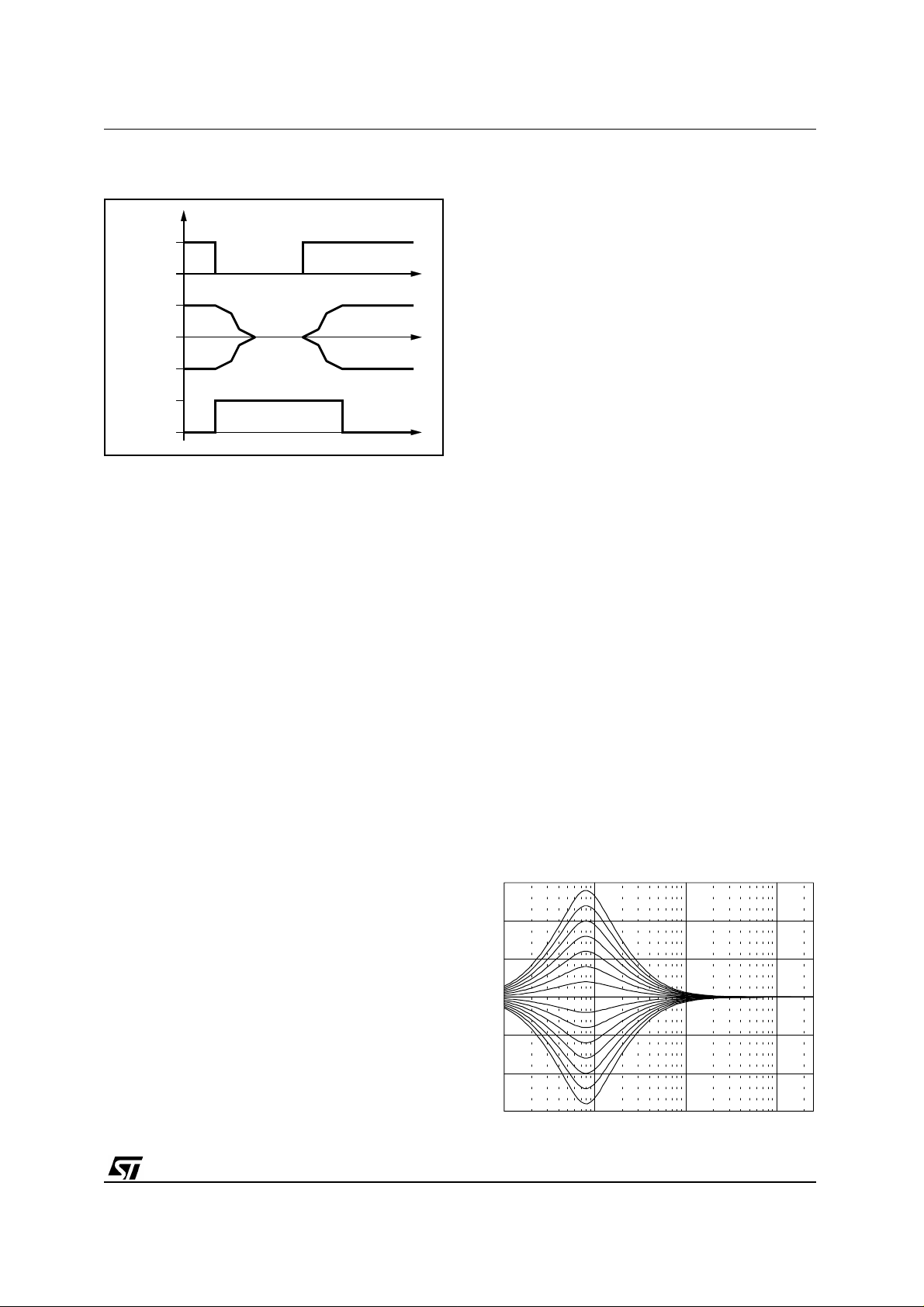

FUNCTIONAL DESCRIPTION OF STEREODECODER

The stereodecoder part of the TDA7407 (see Fig.

15) contains all functions necessary to demodulate the MPX signal like pilot tone dependent

MONO/STEREO switching as well as

"stereoblend" and "highcut" functions.

Stereodecoder Mute

The TDA7407 has a fast and easy to control RDS

mute function which is a combination of the audioprocessor’s softmute and the high-ohmic mute of

the stereodecoder. If the stereodecoder is selected

and a softmute command is sent (or activated

Figure 14. Treble Center Frequencies

@ Gain = 14dB

15.0

12.5

10.0

7.5

5.0

2.5

0.0

10.0 100.0 1.0K 10.0K

throug h the SM pin) t he stereode coder will be s et

automatically to the high-ohmic mute condition after the audio sign al has be en softmut ed.

Hence a checking of alternate frequencies could

be performed. To release the system from the

mute condition simply the unmute command must

be sent: the stereodecoder is unmuted immediately and the audioprocessor is softly unmuted.

Fig. 16 shows the output signal V

as well as the

O

internal stereodecoder mute signal. This influence of Softmute on t he stereodecoder mute can

be switched off by setting bit 3 of the Softmute

byte to "0". A stereodecoder mute command (bit

0, stereodecoder byte set to "1") will set the

stereodecoder in any case independently to the

high-ohmic mute state.

Figure 15. Block Diagram of the Stereodecoder

15/30

TDA7407

Figure 16. Signals During Stereodecoder’s

Softmute

SOFTMUTE

COMMAND

t

STD MUTE

t

V

O

D97AU638

t

If any other source than t he stereodecoder is selected the decoder remains muted and the MPX

pin is connected to Vref to avoid any discharge of

the coupling capacitor through leakage currents.

Ingain + Infilter

The Ingain stage allows to adjust the MPX signal to

a magni tude o f ab out 1V rms in t ern ally whic h is th e

recommended value. The 4th order input filter has

a corner frequency of 80KHz and is used to attenuate sp ik es and nose and acts a s an anti allasing filter for the follo w ing s w itch ca pa ci tor fil te rs .

Demodulator

In the demodulator block the left and the right

channel are separated from the MPX signal. In

this stage also the 19 kHz pilot tone is cancelled.

For reaching a high channel separation the

TDA7407 offers an I

2

C bus programmable roll-off

adjustment which is able to compensate the lowpass behaviour of the tuner section. If the tuner

attenuation at 38kHz is in a range from 4.2% to

31.0% the TDA7407 needs no external network

in front of the MPX pin. Within this range an adjustment to obtain at least 40dB channel separation is possible.

The bits for t his adjustment are located together

with the fieldstrength adjustment in one byte. This

gives the possibility to perform an optimization

step during the production of the carradio where

the channel separation and the fieldstrength control are trimmed.

The setup of the Stereoblend characteristics

which is programmable in a wide range is described in 2.8.

Figure 17. Internal Ster e obl en d C ha r ac ter is tic s

Deemphasis and Highcut.

The lowpass filter for the deemphasis allows to

choose between a time constant of 50µs and

7

75µs (bit D

, Stereodecoder byte).

The highcut control range will be in both cases

τ

HC

= 2 ⋅ τ

. Inside the highcut control range

Deemp

(between VHCH and VHCL) the LEVEL signal

is converted into a 5 bit word whic h controls the

lowpass time constant between τ

. There by the resolution will remain always

τ

Deemp

Deemp

...3⋅

5 bits independently of the absolute voltage

range between the VHCH and VHCL values.

The highcut function can be switched off by I

2

bus (bit D7, Fieldstrength byte set to "0").

The setup of the highcut characteristics is de-

scribed in 2.9.

PLL and Pilot Tone Detector

The PLL has the task to lock on the 19kHz pilotone during a stereo t ransmission to allow a correct demodulation. The included detector enables

the demodulation if t he pilot tone r eaches the se-

PTHST

lected pilot tone threshold V

. Two different

thresholds are available. The detector output (signal STEREO, see block diagram) can be checked

by reading the status byte of the TDA7407 via I

2

bus.

Fieldstrength Control

The fieldstrength input is used to control the high

cut and the stereoblend function. In addition the

signal can be also used to control the noiseblanker thresholds and as input for the multipath

detector. These additional functions are described in sections 3.3 and 4.

C

C

16/30

Figure 18. Relation Betwe en Int e r na l a nd External LEVEL V olta ge a nd S e tup of Stereoblend

TDA7407

INTERNAL

VOLTAGES

REF 5V

VSBL

SETUP OF VST

LEVEL

VSTVMO

Figure 19. Highcu t C h a racter i s t ics

LOWPASS

TIME CONSTANT

3•τ

Deemp

τ

Deemp

D97AU640

LEVEL INTERN

t

FIELDSTRENGHT VOLTAGE

FIELDSTRENGHTVHCHVHCL

INTERNAL

VOLTAGES

REF 5V

VSBL

58%

50%

42%

33%

D97AU639

SETUP OF VMO

VMO

LEVEL INTERN

VST

FIELDSTRENGHT VOLTAGE

t

modulator compatible analog signal which is used

to control the channel separation between 0dB

and the maximum separation. Internally this control range has a fixed upper limit which is the internal reference voltage REF5V. The lower limit

can be programmed between 29.2% and 58%, of

REF5V in 4.167% steps (see figs. 14, 15).

To adjust the external LEVEL voltage to the internal range two values must be defined: the LEVEL

gain L

and VSBL (see fig. 15). To adjust the

G

voltage where the full channel separation is

reached (VST) the LEVEL gain L

has to be de-

G

fined. The following equation can be used to estimate the gain:

=

L

G

Field strength

REF5V

voltage [STEREO]

LEVEL Input and Gain

To suppress undesired high frequency modulation on the highcut and stereoblend function the

LEVEL signal is lowpass filtered firstly.

The filter is a combination of a 1s t order RC lowpass at 53kHz (working as anti-aliasing filter) and

a 1st-order switched capacitor lowpass at 2.2kHz.

The second stage is a programmable gain stage

to adapt the LEVEL signal internally to different IF

device (see Testmode section 5 LEVELINTERN).

The gain is widely programmable in 16 steps

from 0dB to 10dB (step = 0.67dB). These 4 bits

are located together with the Roll-Off bits in the

"Stereodecoder Adjustment" byte to simplify a

possible adaptation during the production of the

carradio.

Stereoblend Control

The stereoblend control block converts the internal LEVEL voltage (LEVEL INTERN) into an de-

The gain can be programmed through 4 bits in

the "Stereodecoder-Adjustment" byte.

The MONO voltage VMO (0dB channel separation) can be choosen selecting VSBL

All necessary internal reference voltages like

REF5V are derived from a bandgap circuit.

Therefore they have a temperature coefficient

near zero. This is useful if t he fieldstrength signal

is also temperature compensated.

But most IF devices apply a LEVEL voltage with a

TC of 3300ppm. The TDA7407 offers this TC for

the reference voltages, too. The TC is selectable

7

with bit D

of the "stereodecoder adjustment"

byte.

Highcut Control

The highcut control setup is similar to the

stereoblend control setup : the starting point

VHCH can be set with 2 bits to be 42, 50, 58 or

66% of REF5V whereas the range can be set to

be 17, 22, 28 or 33% of VHCH (see fig. 19).

17/30

TDA7407

FUNCTIONAL DESCRIPTION OF THE NOISEBLANKER

In the automotive environment the MPX signal is

disturbed by spikes produced by the ignit ion and

for example the wiper motor. The aim of the

noiseblanker part is to cancel the audible influence of the spikes.

Therefore the output of t he stereodecoder is held

at the actual voltage for a t ime between 22 and

38µs (programmable).

The block diagram of t he noiseblanker is given in

fig.20.

In a first s tage the spikes must be detected but to

avoid a wrong triggering on high frequency

(white) noise a complex trigger control is implemented. Behind the triggerstage a pulse former

generates the "blanking" pulse. To avoid any

crosstalk to the signalpath the noiseblanker is

supplied by his own biasing circuit.

Trigger Path

The incoming MPX signal is highpass filtered,

amplified and rectified. This second order highpass-filter has a corner frequency of 140kHz.

The rectified signal, RECT, is lowpass filtered to

generate a signal called PEAK. Also noise with a

frequency 140kHz increases the PEAK voltage.

The resulting voltage can be adjusted by use of

the noise rectifier discharge current.

The PEAK voltage is fed to a threshold generator,

which adds to the PEAK voltage a DC dependent threshold VTH. Both signals, RECT and

PEAK+VTH are fed to a comparator which triggers a re-triggerable monoflop. The monoflop’s

output activates the sample-and-hold circuits in

the signalpath for selected duration.

Automatic N oise Controlled Thresh old Adjustment (ATC)

There are mainly two independent possibilities for

programming the trigger threshold:

0

a the low threshold in 8 steps (bits D

to D2 of

the noiseblanker byte)

b the noise adjusted threshold in 4 steps

3

(bits D

and D4 of the noiseblanker byte,

see fig. 17).

The low threshold is active in combination with a

good MPX signal without any noise; the PEAK

voltage is less than 1V. The sensitivity in this operation is high.

If the MPX signal is noisy the PEAK voltage increases due to the higher noise, which is also

rectified. With increasing of the PEAK voltage the

trigger threshold increases, too. This particular

gain is programmable in 4 steps.

AUTOMATIC TH RESHOLD CONTROL MECHANISM

Automatic Threshold Control by the

Stereoblend Voltage

Besides the noise controlled threshold adjustment there is an additional possibility for influencing the trigger threshold. It is depending on the

stereoblend control.

The point where the MPX signal starts to become

noisy is fixed by the RF part. Theref ore also the

starting point of the normal noise-controlled trigger adjustment is fixed (fig. 14). In some cases

the behaviour of the noiseblanker can be improved by increasing the threshold even in a re-

Figure 20. Block Diagra m o f t he No iseblan ker

18/30

MPX

MPX CONTROL

RECTIFIER

LOWPASS

D98AU856

RECT

+

-

VTH

+

PEAK

+

MONOFLOP HOLDN

THRESHOLD

GENERATOR

ADDITIONAL

THRESHOLD

CONTROL

Figure 21. Block Diagra m o f t he Mul ti path Detect or

TDA7407

gion of higher fieldstr ength. Sometimes a wrong

triggering occures for the MPX signal often shows

distortion in this range which can be avoided

even if using a low threshold.

Because of the overlap of this range and the

range of the stereo/mono transition it can be controlled by stereoblend. This threshold increase is

programmable in 3 steps or switched off with bits

0

and D1 of the fieldstrength control byte.

D

Over Deviation Detector

If the system is t uned to stations with a high deviation the noiseblanker can trigger on the higher

frequencies of the modulation. To avoid this

wrong behaviour, which causes noise in the output signal, the noiseblanker offers a deviation dependent threshold adjustment.

By rectifying the MPX signal a further signal representing the actual deviation is obtained. It is

used to increase the PEAK voltage. Offset and

gain of this circuit are programmable in 3 steps

6

with the bits D

and D7 of the stereodecoder byte

(the first step turns off the detector, see fig. 18).

FUNCTIONAL DESCRIPTION OF THE MULTIPATH DETECTOR

Using the internal multipath det ector the audible

effects of a multipath condition can be minimized.

A multipath condition is detected by rectifying the

19kHz spectrum in the fieldstrength signal.

An external capacitor is used to define the attack

and decay times (see block diagram fig. 21). the

MPOUT pin is used as detector output connected

to a capacitor of about 47nF and additionally the

MPIN pin is selected to be the fieldstrength input.

Using the configuration an external adaptation to

the user’s requirement is given in fig.21.

To keep the old value of the Multipath Detector

during an AF-jump, the external capacitor can be

disconnected by the MP-Hold switch. This s witch

can be controlled directly by the AFS-Pin.

Selecting the "internal influence" in the configuration byte, the channel separation is automatically

reduced during a multipath condition according to

the voltage appearing at the MP_OUT pin. A

possible application is shown in fig. 21.

Programming

To obtain a good multipath performance an adaptation is necessary. Therefore tha gain of the

19kHz bandpass is programmable in four steps

as well as the rectifier gain. The attack and decay

times can be set by the external capacitor value.

QUALITY DETECTOR

The TDA7407 offers a quality detector output

which gives a voltage representing the FM reception conditions. To calculate this voltage the MPX

noise and the multipath detector output are

summed according to the following formula:

Quality = 1.6 (V

-0.8V)+ a (REF 5 V - V

noise

MPOUT

The noise signal is the PEAK signal without additional influences. The factor "a" can be programmed from 0.7 to 1.15. the output is a low impedance output able to drive external circuitry as

well as simply fed to an A/D converter for RDS

applications.

)

19/30

TDA7407

AF Search Control

The TDA7407 is supplied with several functionality to support AF-checks using the stereodecoder.

As mentioned already before the highohmic-mute

feature avoids any clicks during the jump condition. It is possible a the same time to evaluate the

noise- and multipath-content of the alternate frequency by using the Quality detector output.

Therefore the multipath-detector is switched automatically to a small time-constant.

One additional pin (AFS) is implemented in order

to separate the audioprocessor-mute and

stereodecoder AF-functions. In Figure 22 the

blockdiagram and control-functions of the com-

Figure 22. Mute Control Logic

plete AFS-functionality is shown (please note that

the pins AFS and SM ar e ac tive low as well as all

control-bits indicated by an overbar).

TEST MODE

During the test mode, whic h can be activated by

0

setting bit D

of the testing byte and bit D5 of the

subaddress byte to "1", several internal signals

are available at the CASSR pin.

During this mode the input resistor of 100kOhm is

disconnected from the pin. The internal signals

available are shown in the software specification.

20/30

TDA7407

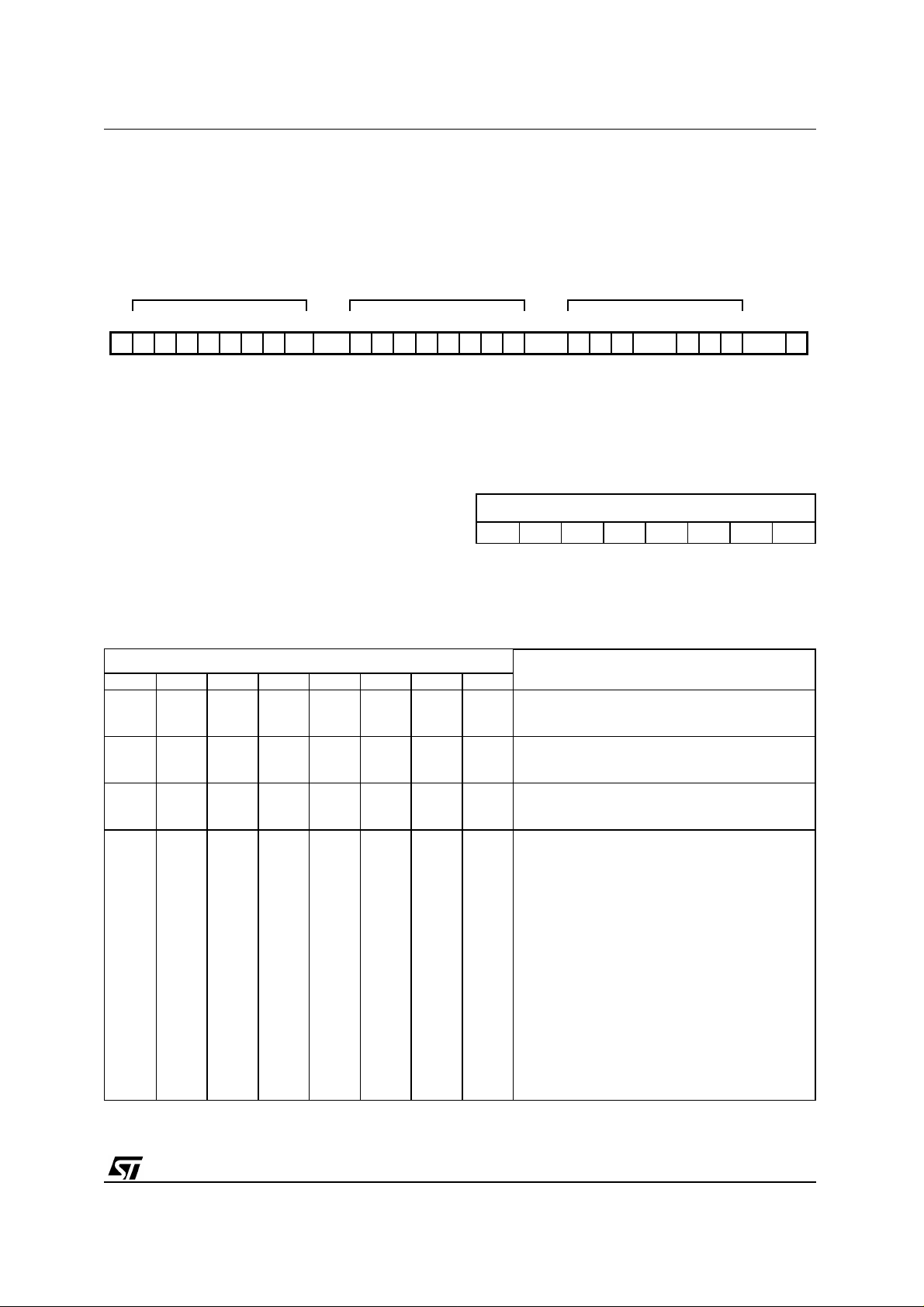

I2C BUS INTERFACE DESCRIPTION

Interface Protocol

The interface protocol comprises:

-a start condition (S)

/ write transmission)

-a subaddress byte

-a sequence of data (N-bytes + acknowledge)

-a stop condition (P)

-a chip address byte (the LSB bit determines read

CHIP ADDRESS

MSB

S 1 0 0 0 1 1 0 R/W ACK ACK ACK P

D97AU627

LSB MSB LSB MSB LSB

S = Start

ACK = Acknowledge

AZ = AutoZero-Remain

SUBADDRESS DATA 1 to DATA n

AZ T

XI

A3 A2 A1 A0 DATA

Auto increment

If bit I in the subaddress byte is set to "1", the

autoincrement of the subaddress is enabled.

T = Testing

I = Autoincrement

P = Stop

MAX CLOCK SPEED 500kbits/s

The transmitted data is auto matically updated after each ACK. Transmission can be repeated

without new chip address.

TRANSMITTED DATA (send mode)

MSB LSB

XXXXSTSMXX

SM = 1 Soft mute activated

ST = 1 Stereo mode

X = Not Used

SUBADDRESS (receive mode)

MSB LSB FUNCTION

I3 I2 I1 I0 A3 A2 A1 A0

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

AutoZero Remain

off

on

Testmode

off

on

Auto Increment Mode

off

on

Input Multiplexer

0

Volume

1

Treble

0

Bass

1

Speaker attenuator LF

0

Speaker attenuator RF

1

Speaker attenuator LR

0

Speaker attenuator RR

1

SoftMute / Bass Prog.

0

Stereodecoder

1

Noiseblanker

0

High Cut Control

1

Fieldstrength & Quality

0

Configuration

1

EEPROM

0

Testing

1

New Quality/Control

0

Middle Filter

1

21/30

TDA7407

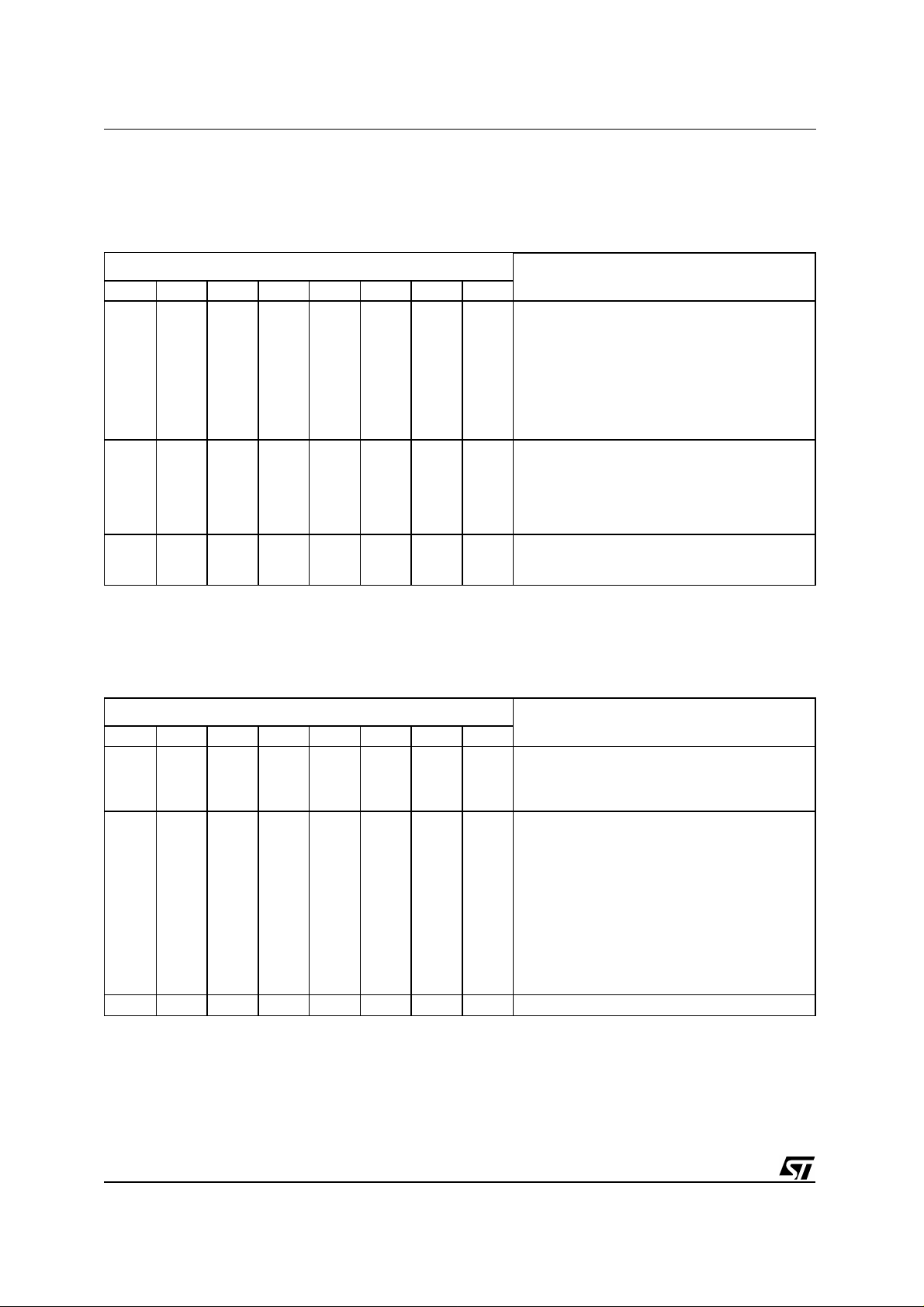

DATA BYTE SPECIFICATION

After power on reset all register are set to 11111110

Input Selector (subaddress 0H)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Source Selector

CD

0

0

0

0

1

1

1

1

0

0

:

1

1

0

1

0

0

:

1

1

0

0

:

1

1

0

1

:

0

1

0

0

1

1

0

0

1

1

0

Cassette

1

Phone

0

AM

1

Stereo Decoder

0

AC Inputs Front

1

Mute

0

AC inputs Rear

1

In-Gain

15dB

14dB

:

1 dB

0 dB

Coupl. Front Speaker

external

internal

Volume and Speaker Attenuation (subaddress 1H, 4H, 5H, 6H, 7H)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

1

:

1

1

1

:

1

0

0

0

:

0

0

:

0

0

X11XXXXXMute

0

:

0

0

0

:

0

0

0

0

:

0

0

:

1

1

0

:

0

0

0

:

0

0

0

0

:

0

0

:

0

0

1

:

1

1

0

:

0

0

0

0

:

0

1

:

0

0

1

:

0

0

1

:

0

0

0

0

:

1

0

:

1

1

1

:

0

0

1

:

0

0

0

0

:

1

0

:

1

1

1

:

0

0

1

:

0

0

0

0

:

1

0

:

1

1

1

:

not used configurations

1

0

+15dB

1

:

:

+1dB

1

0dB

0

0dB

0

-1dB

1

:

:

-15dB

1

-16dB

0

:

:

-78dB

0

-79dB

1

22/30

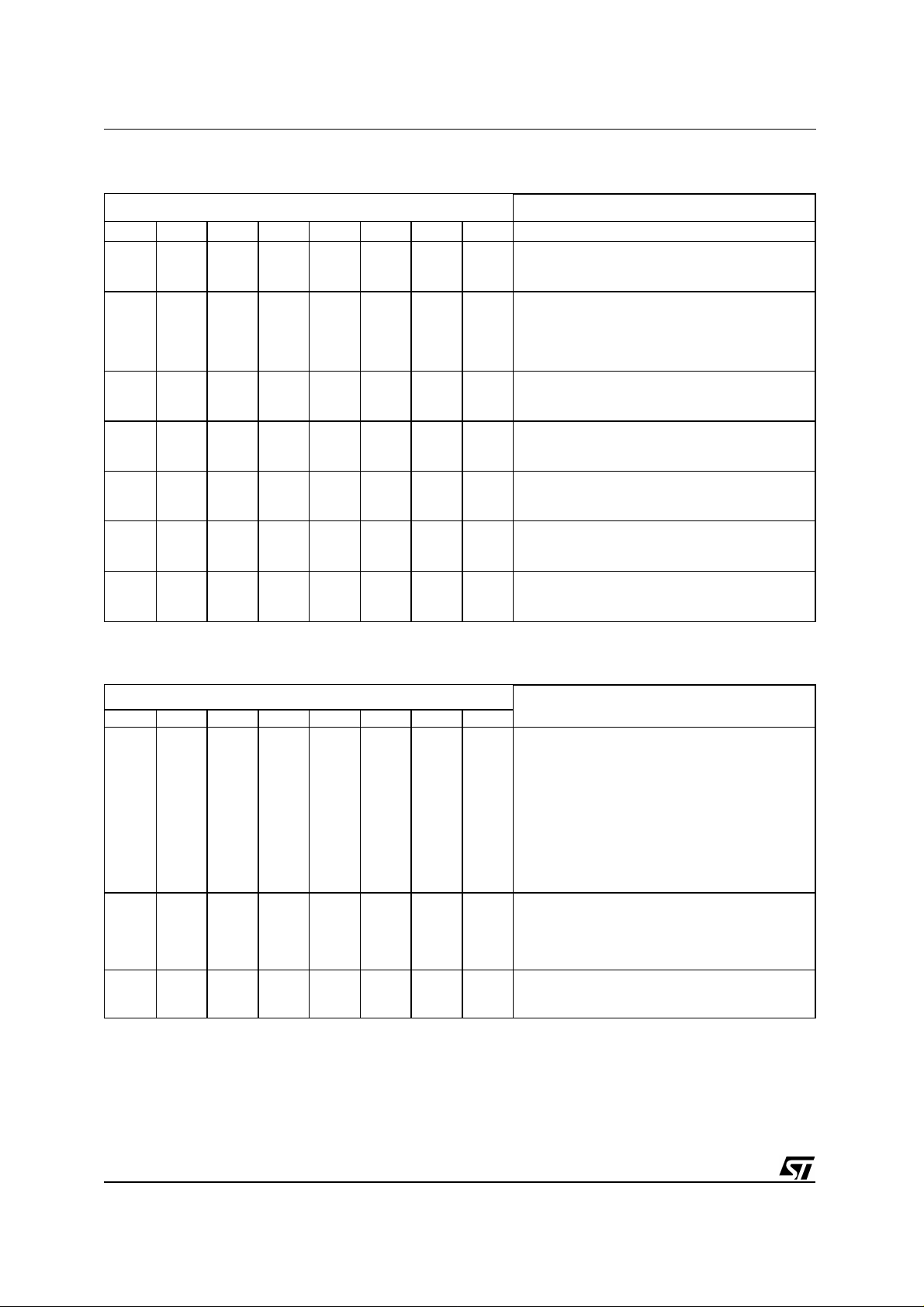

Treble Fil ter (subaddress 2H)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Treble Steps

-15dB

0

0

:

0

0

1

1

:

1

1

0

0

1

1

0

1

0

1

0

1

0

0

:

1

1

1

1

:

0

0

0

0

:

1

1

1

1

:

0

0

0

0

:

1

1

1

1

:

0

0

0

-14dB

1

:

:

-1dB

0

0dB

1

0dB

1

+1dB

0

:

:

+14dB

1

+15dB

0

Treble Center Frequency

10.0KHz

12.5KHz

15.0KHz

17.5KHz

Coupl. Rear Speaker

external (AC)

internal

TDA7407

Bass Filter (subaddress 3H)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Bass Steps

-15dB

0

0

:

0

0

1

1

:

1

1

0

0

1

1

0

1

0

1

0

1

0

0

:

1

1

1

1

:

0

0

0

0

:

1

1

1

1

:

0

0

0

0

:

1

1

1

1

:

0

0

0

-14dB

1

:

:

-1dB

0

0dB

1

0dB

1

+1dB

0

:

:

+14dB

1

+15dB

0

Bass Q-Factor

1.0

1.25

1.50

2.0

Bass DC Mode

off

on

23/30

TDA7407

Soft Mute and Bass Programming (subaddress 8H)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Mute

0

Enable Soft Mute

1

Disable Soft Mute

Mutetime = 0.48ms

Mutetime = 0.96ms

Mutetime = 40.4ms

Mutetime = 324ms

Stereodecoder Soft Mute Influence = on

Stereodecoder Soft Mute Influence = off

Bass Center Frequency

Center Frequency = 60 Hz

Center Frequency = 70 Hz

Center Frequency = 80 Hz

Center Frequency = 100Hz

Center Frequency = 150Hz

Noise Blanker Time

38µs

25.5µs

32µs

22µs

0

0

1

1

1

0

0

1

1

1 Only for Bass Q-Factor = 2.0

0

1

0

1

0

0

1

1

0

1

0

1

0

1

1

0

1

0

1

Stereodecoder (subaddress 9H)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

0

STD Unmuted

1

STD Muted

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

In Gain 11dB

In Gain 8.5dB

In Gain 6dB

In Gain 3.5dB

Stereodecoder = on

Stereodecoder = off

Forced Mono

Mono/Stereo switch automatically

Noiseblanker PEAK charge current low

Noiseblanker PEAK charge current high

Pilot Threshold HIGH

Pilot Threshold LOW

Deemphasis 50µs

Deemphasis 75µs

24/30

Noiseblanker (subaddress AH)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Low Threshold 65mV

0

0

0

0

1

1

1

1

0

0

1

1

0

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

1

1

0

0

1

1

0

Low Threshold 60mV

1

Low Threshold 55mV

0

Low Threshold 50mV

1

Low Threshold 45mV

0

Low Threshold 40mV

1

Low Threshold 35mV

0

Low Threshold 30mV

1

Noise Controlled Threshold 320mV

Noise Controlled Threshold 260mV

Noise Controlled Threshold 200mV

Noise Controlled Threshold 140mV

Noise blanker OFF

Noise blanker ON

Over deviation Adjust 2.8V

Over deviation Adjust 2.0V

Over deviation Adjust 1.2V

Over deviation Detector OFF

TDA7407

High Cut (subaddress BH)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

0

High Cut OFF

1

High Cut ON

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Max. High Cut 2dB

Max. High Cut 5dB

Max. High Cut 7dB

Max. High Cut 10dB

VHCH at 42% REF 5V

VHCH at 50% REF 5V

VHCH at 58% REF 5V

VHCH at 66% REF 5V

VHCL at 16.7% VHCH

VHCL at 22.2% VHCH

VHCL at 27.8% VHCH

VHCL at 33.3% VHCH

Strong Multipath influence on PEAK 18K

OFF

ON (18K Discharge if V

MPOUT

<2.5V)

25/30

TDA7407

Fieldstrength Control (subaddress CH)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

VSBL at 29% REF 5V

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

0

0

1

1

0

VSBL at 33% REF 5V

1

VSBL at 38% REF 5V

0

VSBL at 42% REF 5V

1

VSBL at 46% REF 5V

0

VSBL at 50% REF 5V

1

VSBL at 54% REF 5V

0

VSBL at 58% REF 5V

1

Noiseblanker Field strength Adj 2.3V

Noiseblanker Field strength Adj 1.8V

Noiseblanker Field strength Adj 1.3V

Noiseblanker Field strength Adj OFF

Quality Detector Coefficient a = 0.7

Quality Detector Coefficient a = 0.85

Quality Detector Coefficient a = 1.0

Quality Detector Coefficient a = 1.15

Multipath off influence on PEAK discharge

-1V/ms (at MPout = 2.5V

Configuration (subaddress DH)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Noise Rectifier Discharge Resistor

0

0

0

1

1

0

1

0

1

0

1

0

1

0

0

1

1

0

1

0

1

0

0

1

1

R = infinite

1

R = 56k

Ω

R = 33k

0

1

Ω

R =18k

Ω

Multipath Detector Bandpass Gain

6dB

12dB

16dB

18dB

Multipath Detector internal influence

ON

OFF

Multipath Detector Charge Current 0.5µA

Multipath Detector Charge Current 1µA

Multipath Detector Reflection Gain

Gain = 7.6dB

Gain = 4.6dB

Gain = 0dB

disabled

26/30

Stereodecoder Adjustment (subaddress EH)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Roll Off Compensation

not allowed

0

0

0

:

0

:

0

1

1

1

:

1

:

1

0

0

0

:

1

0

0

0

:

1

0

0

1

:

1

0

1

0

:

1

0

0

0

:

1

:

1

0

0

0

:

1

:

1

0

0

1

:

0

:

1

0

0

1

:

0

:

1

0

1

0

:

0

:

1

0

1

0

:

0

:

1

7.2%

9.4%

:

13.7%

:

20.2%

not allowed

19.6%

21.5%

:

25.3%

:

31.0%

Level Gain

0dB

0.66dB

1.33dB

:

10dB

TDA740 7

Testing (subaddress FH)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Stereodecoder test signals

0

OFF

1

Test signals enabled if bit D5 of the subaddress

(test mode bit) is set to "1", too

0

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

1

0

1

Note : This byte is used for testing or evaluation purposes only and must not be set to other values than the default "11111110" in the application!

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

External Clock

Internal Clock

Testsignals at CASS_R

VHCCH

Level intern

Pilot magnitude

VCOCON; VCO Control Voltage

Pilot threshold

HOLDN

NB threshold

F228

VHCCL

VSBL

not used

not used

PEAK

not used

REF5V

not used

VCO

OFF

ON

Audioprocessor test mode

enabled if bit D5 of the subaddress

(test mode bit) is set to "1"

OFF

27/30

TDA7407

New Quality / Control (subaddress 10H)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Reference Generation

0

Internal Reference-Divider

1

External Reference Force

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Quality Noise-Gain

15dB

12dB

9dB

6dB

SC-Clock-Mode

Fast Mode

Normal Mode

Auto-Zero

Off

On

Smoothing Filter

On

Off

Enable AF-Pin

Enable Pin

Disable Pin

AF-Pin ST-Decoder-Mute-Influence

On

Off

Mid Filter (subaddress 11H)

MSB LSB FUNCTION

D7 D6 D5 D4 D3 D2 D1 D0

Attenuation

-15dB

0

0

:

0

0

1

1

:

1

1

0

0

1

1

0

1

0

1

0

1

0

0

:

1

1

1

1

:

0

0

0

1

:

1

1

1

1

:

0

0

0

1

:

1

1

1

1

:

0

0

0

-14dB

1

:

:

-1dB

0

0dB

1

0dB

1

+1dB

0

:

:

+14dB

1

+15dB

0

Middle Center-frequency

500Hz

1.0kHz

1.5kHz

2.0kHz

Mid Q Factor

1.0

2.0

28/30

TDA7407

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 1.60 0.063

A1 0.05 0.15 0.002 0.006

A2 1.35 1.40 1.45 0.053 0.055 0 .057

B 0.30 0.37 0.45 0.012 0.014 0.018

C 0.09 0.20 0.004 0.008

D 12.00 0.472

D1 10.00 0.394

D3 8.00 0.315

e 0.80 0.031

E 12.00 0.472

E1 10.00 0.394

E3 8.00 0.315

L 0.45 0.60 0.75 0.018 0.024 0.030

L1 1.00 0.039

K 0°(min.), 3.5˚(typ.), 7°(max.)

OUTLINE AND

MECHANICAL DATA

TQFP44 (10 x 10)

D

D1

A1

2333

34

B

44

1

e

22

E

E1

12

11

0.10mm

.004

Seating Plane

B

A

A2

C

L

K

TQFP4410

29/30

TDA7407

Information furnished is believ ed t o be accurate and rel i abl e. However, STM icroel ectronics assumes no responsibility f or the consequences

of use of such informati on nor for any infringement of patents or other ri ghts of third parties which may result from its use. No license is

granted by im plica tion or otherw ise under any patent or pa tent right s of STMicr oelectronic s. Speci fication mentioned in this publication are

subject to c hange without notice. Thi s publication supersedes and replac es all information prev i ously supplied. STMic roel ectronics produc ts

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2001 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

30/30

Loading...

Loading...