DIGITALLY CONTROLLED AUDIO PROCESSOR

WITH SURROUND SOUND MATRIX

1 STEREOINPUT

VOLUMECONTROLIN 1.25dB STEP

TREBLEAND BASSCONTROL

THREE SURROUND MODES ARE AVAIL-

ABLE:

– MOVIE,MUSIC AND SIMULATED

FOURSPEAKER ATTENUATORS:

– 4INDEPENDENT SPEAKERSCONTROL

IN 1.25dBSTEPSFOR BALANCEFACILITY

– INDEPENDENTMUTE FUNCTION

ALL FUNCTIONS PROGRAMMABLE VIA SE-

RIAL BUS

DESCRIPTION

The TDA7345 is a volume tone (bass and treble)

balance (Left/Right) processor for quality audio

applicationsin car radio and Hi-Fi systems.

It reproduces surround sound by using phase

shifters and a signal matrix. Control of all the

functionsis accomplishedby serial bus.

The AC signal setting is obtained by resistor net-

TDA7345

SO28

ORDERING NUMBER:

works and switches combined with operational

amplifiers.

Thanks to the usedBIPOLAR/CMOSTechnology,

Low Distortion, Low Noise and DC stepping are

obtained.

TDA7345D

PIN CONNECTION

CREF

PS2

PS1

LP1

HP1 REAR IN

HP2

L-in

BASS-LA

BASS-LB

TREBLE-L

REC_OUT_L

REC_OUT_R

Lout

Rout

1

2

3

4

5

6

7

8

9

10

11

12

13

14

D94AU191A

28

27

26

25

24

22

21

20

19

18

17

16

15

Vs

PS3

PS4

LP

REAR OUT23

R-in

BASS-RA

BASS-RB

TREBLE-R

DIG GND

SDA

SCL

AGND

November 1999

1/18

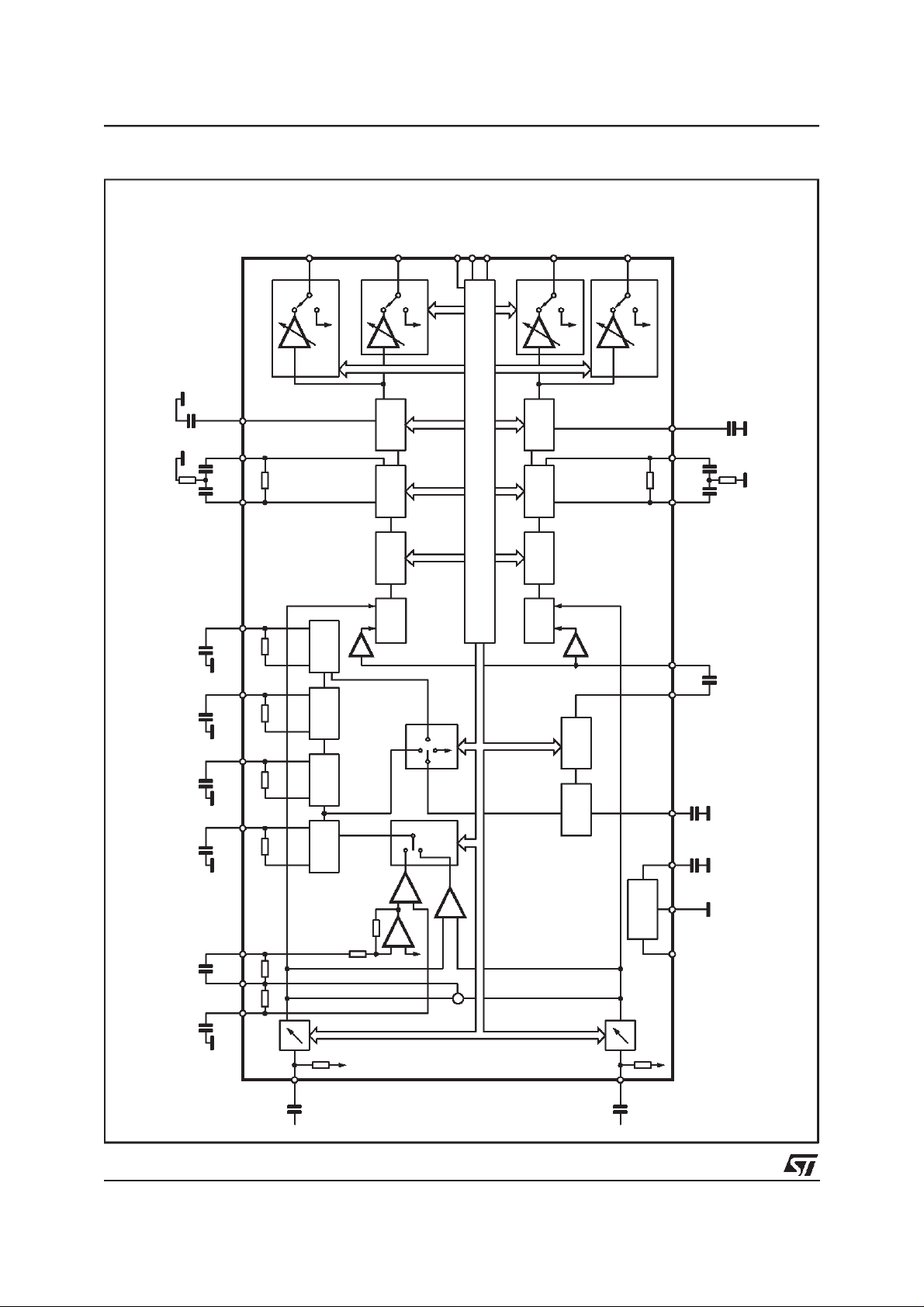

TDA7345

BLOCK DIAGRAM

5.6nF

100nF

5.6K

100nF

TREBLE(L)

BASS-LB

8910

BASS-LA

SPKR

RB

11

ATT

REC_OUT_L

MUTE

ATT

SPKR

LOUT

13

TREBLE

BASS

VOL

MUTE

SCL

SDA

161718

DIG GND

C BUSDECODER + LATCHES

2

I

ATT

SPKR

ROUT

14

VOL BASS TREBLE

MUTE

ATT

SPKR

REC_ OUT_R

12

MUTE

RB

D94AU192A

TREBLE(R)

21 20 19

5.6nF

BASS-RB

100nF 100nF

5.6K

22nF

22nF

100nF

100nF

5.6nF 680nF

PS4

PS3

PS2

PS1

LP1 HP1 HP2

AMP

MIXING

PS4

RPS4

RPS3

RPS2

RPS1

RHP1

RLP1

4 5 6 3 2 27 26

0.47µF

400Hz

-

MUSIC

SIM

-

+

+

MOVIE/SIM

OFF

MUSIC

MOVIE/

-

L-R

+

+

PS3

400Hz

PS2

4KHz

PHASE SHIFTER

PS1

90Hz

R6

R5

50K

7

L-in

AMP

MIXING

EFFECT

CONTROL

LPF

9KHz

REAR IN

24

REAR OUT

1.2nF

LP BASS-RA

C5

22µF

AGND CREF

SUPPLY

S

V

28 15 1 25 23

50K

22

R-in

0.47µF

2/18

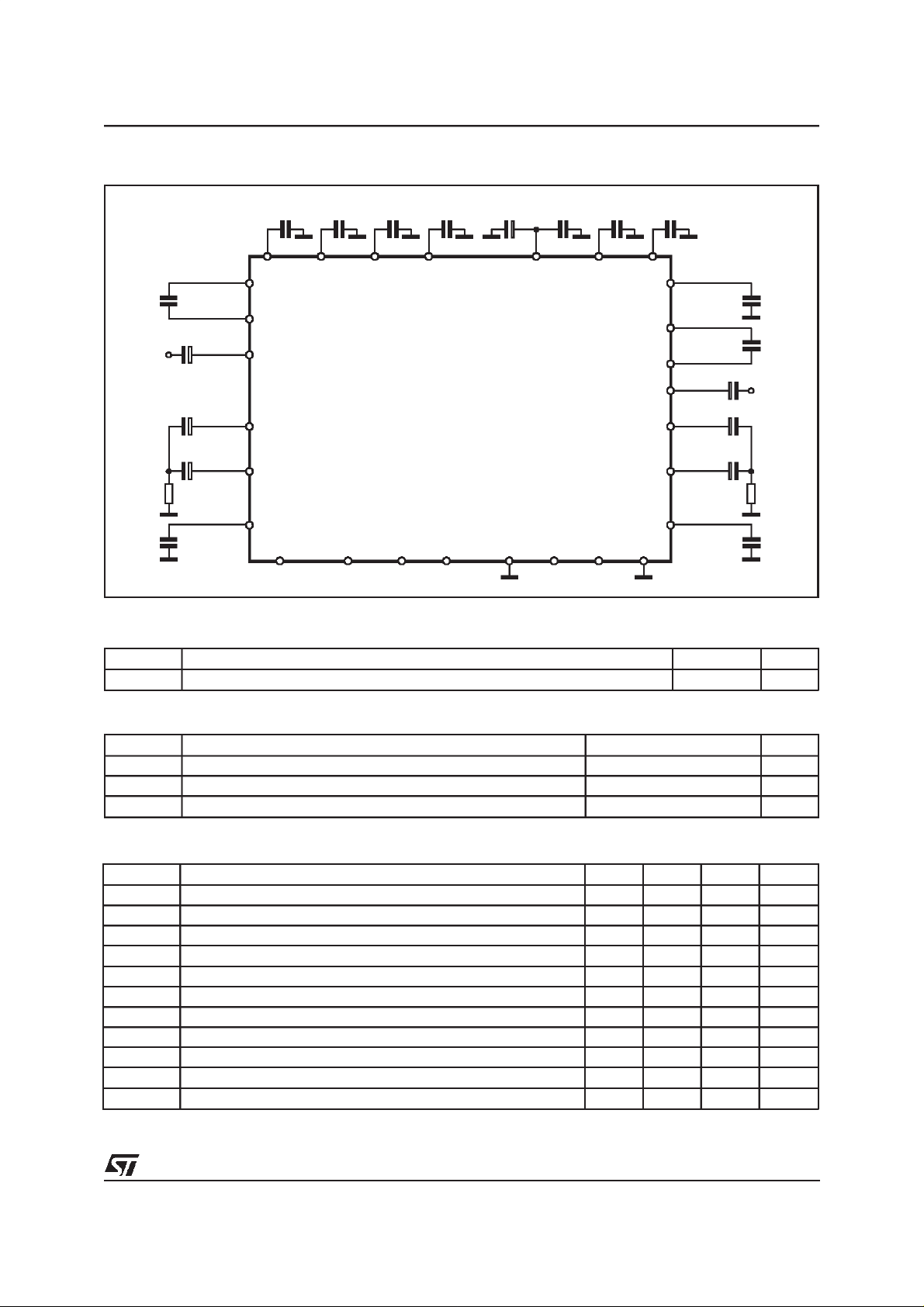

TEST CIRCUIT

TDA7345

680nF

C16

0.47µF

C17

C20 100nF

BASS-LA

C21 100nF

BASS-LB

R2

5.6K

TREBLE-L

5.6nF

C22

D94AU193A

THERMAL DATA

5.6nF C15 100nF C14 22µF C3 100nF C2100nF C13 10µFC1

LP1 PS1 PS2 CREF V

HP1

5

6

HP2

L-in

7

TDA7345

8

9

10

11

REC OUT L

12

REC OUTR

13 14 15 1716 18

LOUT ROUT AGND SCL SDA DIG GND

22nF C4

S

PS3

22nF C5

PS4

2627128234

25

24

23

22

21

20

19

LP

1.2nF

C6

REAR IN

2.2µF

REAR OUT

0.47µFC7

R-in

C10 100nF

BASS-RA

C11 100nF

BASS-RB

TREBLE-R

5.6nF

C12

R1

5.6K

Symbol Description Value Unit

R

thj-pins

Thermal Resistance Junction-pins Max. 85

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

T

amb

T

Operating Supply Voltage 11 V

S

Operating Ambient Temperature -10 to 85 °C

Storage Temperature Range -55 to +150 °C

stg

QUICK REFERENCE DATA

Symbol Parameter Min. Typ. Max. Unit

V

V

CL

THD Total Harmonic Distortion V = 1Vrms f = 1KHz 0.02 0.1 %

S/N Signal to Noise Ratio V

S

Supply Voltage 7 9 10.5 V

S

Max. input signal handling 2 Vrms

out = 1Vrms (made = OFF) 106 dB

Channel Separation f= 1KHz 70 dB

C

Volume Control 1.25dB step -78.75 0 dB

Treble Control (2db step) -14 +14 dB

Bass Control (2db step) -14 +14 dB

Balance Control 1.25dB step REC-OUT L & R -38.75 0 dB

Balance Control 1.25dB step (L

OUT,ROUT

) -78.75 0 dB

Mute Attenuation 90 dB

C/W

°

3/18

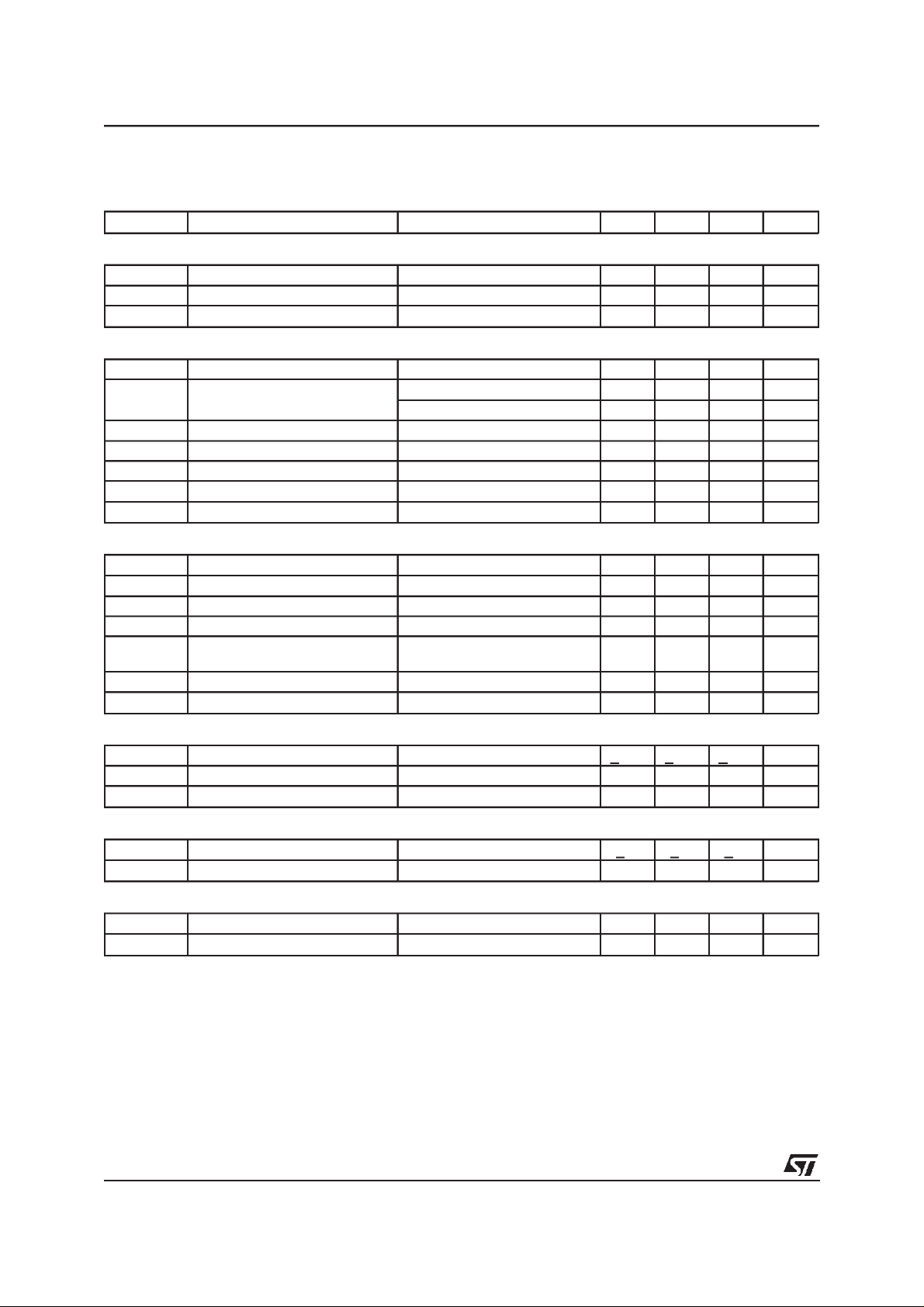

TDA7345

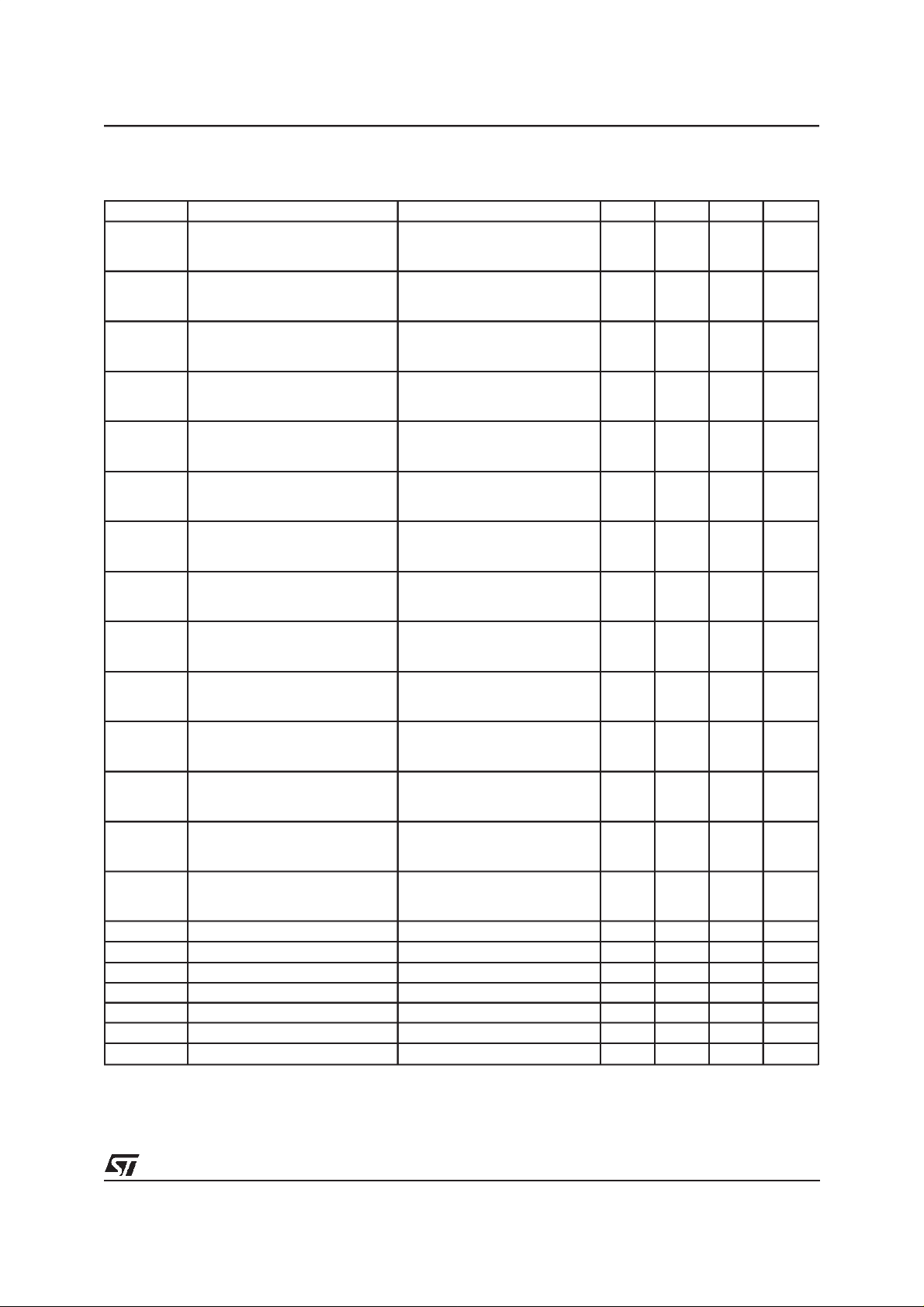

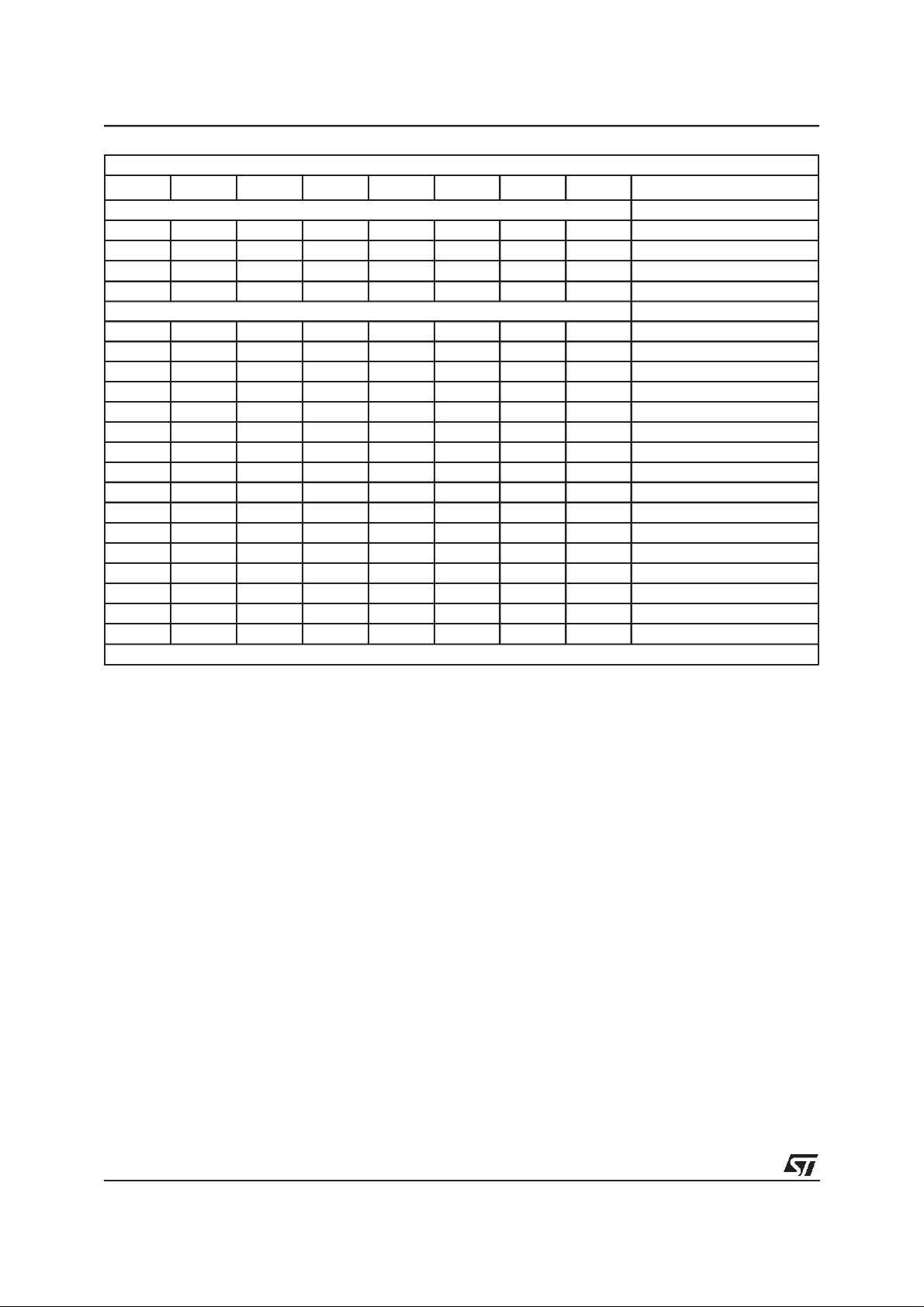

ELECTRICALCHARACTERISTICS

R

= 600Ω, all controls flat (G = 0),Effect Ctrl = -6dB, MODE= OFF; f = 1KHz

G

(refer to the testcircuit T

=25°C, VS= 9V, RL= 10KΩ,

amb

unless otherwisespecified)

Symbol Parameter Test Condition Min. Typ. Max. Unit

SUPPLY

V

S

I

S

SVR Ripple Rejection L

Supply Voltage 7 9 10.5 V

Supply Current 20 25 35 mA

CH /RCH out, Mode = OFF 60 80 dB

INPUT STAGE

C

RANGE

A

A

A

V

R

II

V

CL

VMIN

VMAX

STEP

DC

Input Resistance 35 50 65 KΩ

Clipping Level THD = 0.3%; Lin or Rin 2 2.5 Vrms

THD = 0.3%; Rin + Lin (2) 3.0 Vrms

Control Range 19.68 dB

Min. Attenuation -1 0 1 dB

Max. Attenuation 18.68 19.68 20.68 dB

Step Resolution 0.11 0.31 0.51 dB

DC Steps adjacent att. step -3 0 3 mV

VOLUMECONTROL

C

RANGE

A

VMIN

A

VMAX

A

STEP

E

A

E

T

V

DC

Control Range 70 75 dB

Min. Attenuation -1 0 1 dB

Max. Attenuation 70 75 dB

Step Resolution Av = 0to -40dB 0.5 1.25 1.75 dB

Attenuation Set Error Av = 0to -20dB

Av = -20to -60dB

-1.5

-3

0 1.5

2

Tracking Error 2dB

DC Steps adjacent attenuation steps -3 0 3 mV

BASS CONTROL (1)

dB

dB

Gb Control Range Max. Boost/cut +11.5 +14.0 +16.0 dB

B

STEP

R

B

Step Resolution 1 2 3 dB

Internal Feedback Resistance 32 44 56 KΩ

TREBLECONTROL (1)

Gt Control Range Max. Boost/cut +13 +14 +15 dB

T

STEP

Step Resolution 1 2 3 dB

EFFECTCONTROL

4/18

C

RANGE

S

STEP

Control Range -21 -6 dB

Step Resolution 0.5 1 1.5 dB

TDA7345

ELECTRICALCHARACTERISTICS

(continued)

SURROUNDSOUND MATRIX

Symbol Parameter Test Condition Min. Typ. Max. Unit

In-phase Gain (OFF) Mode OFF,Input signalof

LR In-phase Gain Difference

D

G

GOFF

OFF

(OFF)

G

MOV1

G

MOV2

D

GMOV

In-phase Gain (Movie 1) Moviemode, Effect Ctrl = -6dB

In-phase Gain (Movie 2) Moviemode, Effect Ctrl = -6dB

LR In-phase Gain Diffrence

(Movie)

G

MUS1

G

MUS2

D

GMUS

In-phase Gain (Music 1) Music mode, Effect Ctrl = -6dB

In-phase Gain (Music 2) Music mode, Effect Ctrl = -6dB

LR In-phase Gain Difference

(Music)

L

MON1

L

MON2

L

MON3

R

MON1

R

MON2

R

MON3

R

LP1

R

PS1

R

PS2

R

PS3

R

PS2

R

HPI

R

LPF

Simulated L Output 1 SimulatedMode,EffectCtrl= -6dB

Simulated L Output 2 SimulatedMode,EffectCtrl= -6dB

Simulated L Output 3 SimulatedMode, EffectCtrl= -6dB

Simulated R Output 1 SimulatedMode,EffectCtrl= -6dB

Simulated R Output 2 SimulatedMode,EffectCtrl= -6dB

Simulated R Output 3 SimulatedMode,EffectCtrl= -6dB

Low Pass FilterResistance 7.5 10 12.5 K

Phase Shifter1 Resistance 13.5 17.95 22.5 k

Phase Shifter2 Resistance 0.30 0.40 0.50 KΩ

Phase Shifter3 Resistance 13.6 18.08 22.6 KΩ

Phase Shifter4 Resistance 13.6 18.08 22.6 KΩ

High Pass Filter Resistance 45 60 75 KΩ

LP PinImpedance 7.5 10 12.5 K

1kHz, 1.4 V

Lin→ L

out

p-p,Rin

→ R

out

Mode OFF,Input signalof

1kHz, 1.4 V

(Rin→ R

Input signal of 1kHz, 1.4 V

Rin→ R

Input signal of 1kHz, 1.4 V

R

→

in

out

out,Lin

R

out,Lin

p-p

), (Lin→ L

→ L

out

L

→

out

out

)

p-p

p-p

Movie mode, Effect Ctrl = -6dB

Input signal of 1kHz, 1.4 V

(Rin→ R

)–(Lin→ L

out

Input signal of 1kHz, 1.4 V

(Rin→ R

)–(Lin→ L

out

Input signal of 1kHz, 1.4 V

Rin→ R

out,Lin

→ L

out

out

out

p-p

)

p-p

)

p-p

Music mode, Effect Ctrl = -6dB

Input signal of 1kHz, 1.4 V

R

(R

in

→

out

)–(L

→

in

p-p

L

)

out

Input signal of 250Hz,

1.4 V

p-p,Rin

and L

L

→

in

out

Input signal of 1kHz,

1.4 V

p-p,Rin

and Lin→ L

out

Input signal of 3.6kHz,

1.4 V

p-p,Rin

and Lin→ L

out

Input signal of 250Hz,

1.4 V

p-p,Rin

and Lin→R

out

Input signal of 1kHz,

1.4 V

p-p,Rin

and L

R

→

in

out

Input signal of 3.6kHz,

1.4 V

p-p,Rin

and Lin→ R

out

-1.5 0 1.5 dB

-1.5 0 1.5 dB

7dB

8dB

0dB

6dB

7.5 dB

0dB

4.5 dB

– 4.0 dB

7.0 dB

– 4.5 dB

3.8 dB

–20 dB

Ω

Ω

Ω

5/18

TDA7345

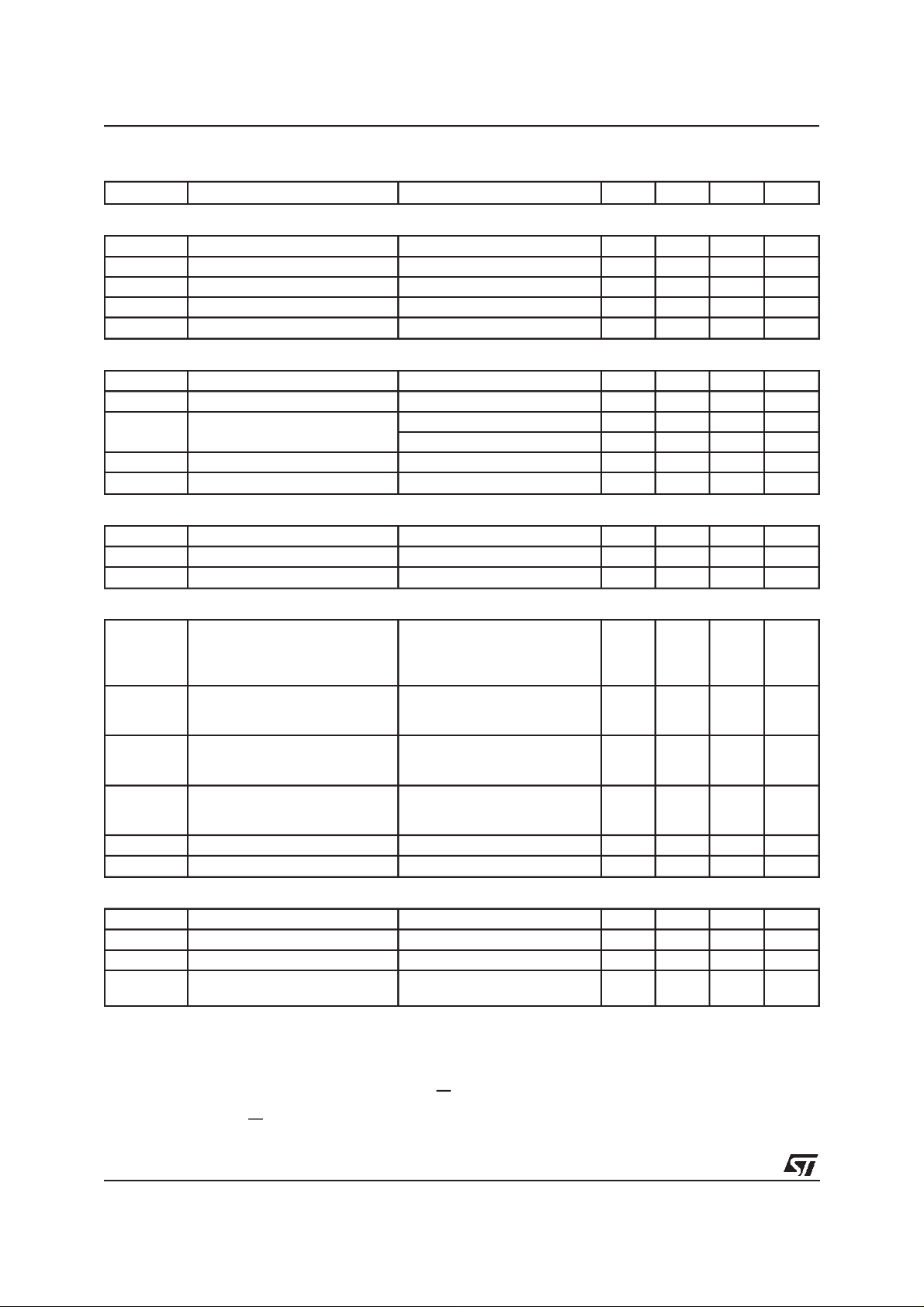

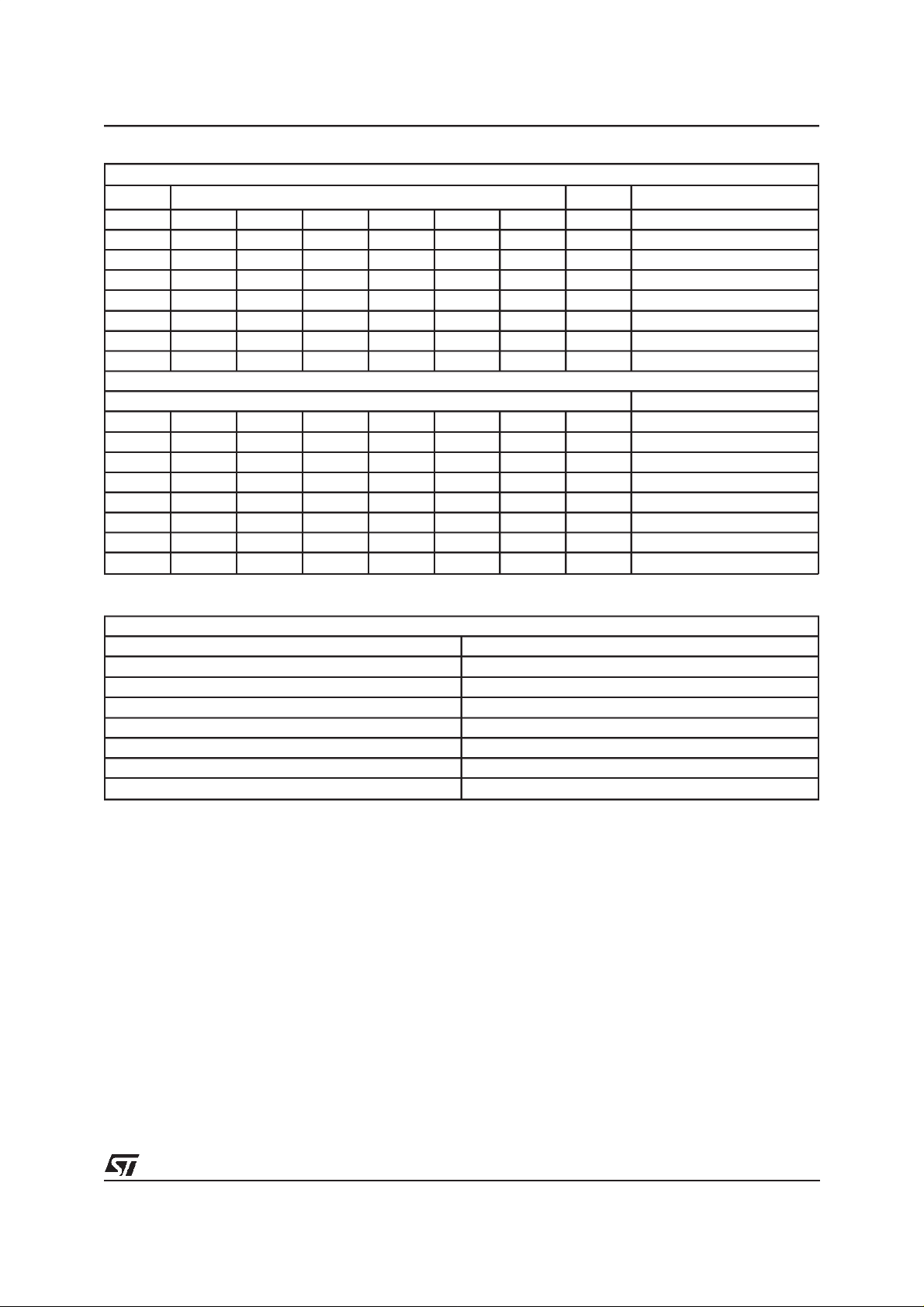

ELECTRICALCHARACTERISTICS(continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

SPEAKERATTENUATORS (REC_OUT_L, REC_OUT_R)

C

S

A

range

STEP

E

MUTE

V

DC

A

Control Range 35 37.5 40 dB

Step Resolution 0.5 1.25 1.75 dB

Attenuation set error -1.5 1.5 dB

Output Mute Attenuation 80 90 dB

DC Steps adjacent att. steps -3 0 3 mV

SPEAKERATTENUATORS (LOUT,ROUT)

C

S

A

range

STEP

E

V

DC

MUTE

A

Control Range 70 75 dB

Step Resolution Av = 0 to -40dB 0.5 1.25 1.75 dB

Attenuation set error Av = 0 to 20dB -1.5 0 1.5 dB

Av = -20 to -60dB -3 0 2 dB

DC Steps adjacent att. steps -3 0 3 mV

Output Mute Attenuation 80 90 dB

AUDIO OUTPUTS (LOUT,ROUT, REC_OUT_L, REC_OUT_R)

V

OCL

R

OUT

V

OUT

Clipping Level d =0.3% 2 2.5 Vrms

Output resistance 100 200 300 Ω

DC Voltage Level 4.2 4.5 4.8 V

GENERAL

N

O(OFF)

N

O(MOV)

N

O(MUS)

N

O(MON)

d Distorsion Av = 0 ; V

S

C

Output Noise(OFF) BW= 20Hzto 20KHz

Output LOUT, ROUT,

Output: REC-OUT-L,

REC-OUT-R

Output Noise(Movie) Mode =Movie ,

B

= 20Hzto 20KHz

W

R

out

and L

measurement

out

Output Noise(Music) Mode = Music ,

B

= 20Hzto 20KHz,

W

R

out

and L

measurement

out

Output Noise(Simulated) Mode = Simulated,

B

= 20Hzto 20KHz

W

R

out

and L

measurement

out

in = 1Vrms 0.02 0.1 %

Channel Separation 60 70 dB

BUS INPUTS

8

8

1515µVrms

Vrms

µ

30 µVrms

30 µVrms

30

Vrms

µ

V

IL

V

IH

I

IN

V

O

Input Low Voltage 1V

Input High Voltage 3 V

Input Current -5 +5 µA

Output VoltageSDA

IO= 1.6mA 0.4 0.8 V

Acknowledge

Note:

(1) Bass and Treble response: The center frequency and the resonance quality can be choosen by

the external circuitry. A standard first order bass response can be realized by a standard feedback network.

V

(2) The peack voltage of the two input signals must be less then

V

(Lin + Rin)

peak

•

S

<

A

Vin

2

S

:

2

6/18

TDA7345

2

C BUSINTERFACE

I

Data transmission from microprocessor to the

TDA7345 and viceversa takes place through the

2 wires I

2

C BUS interface, consisting of the two

lines SDA and SCL (pull-up resistors to positive

supply voltage must be connected).

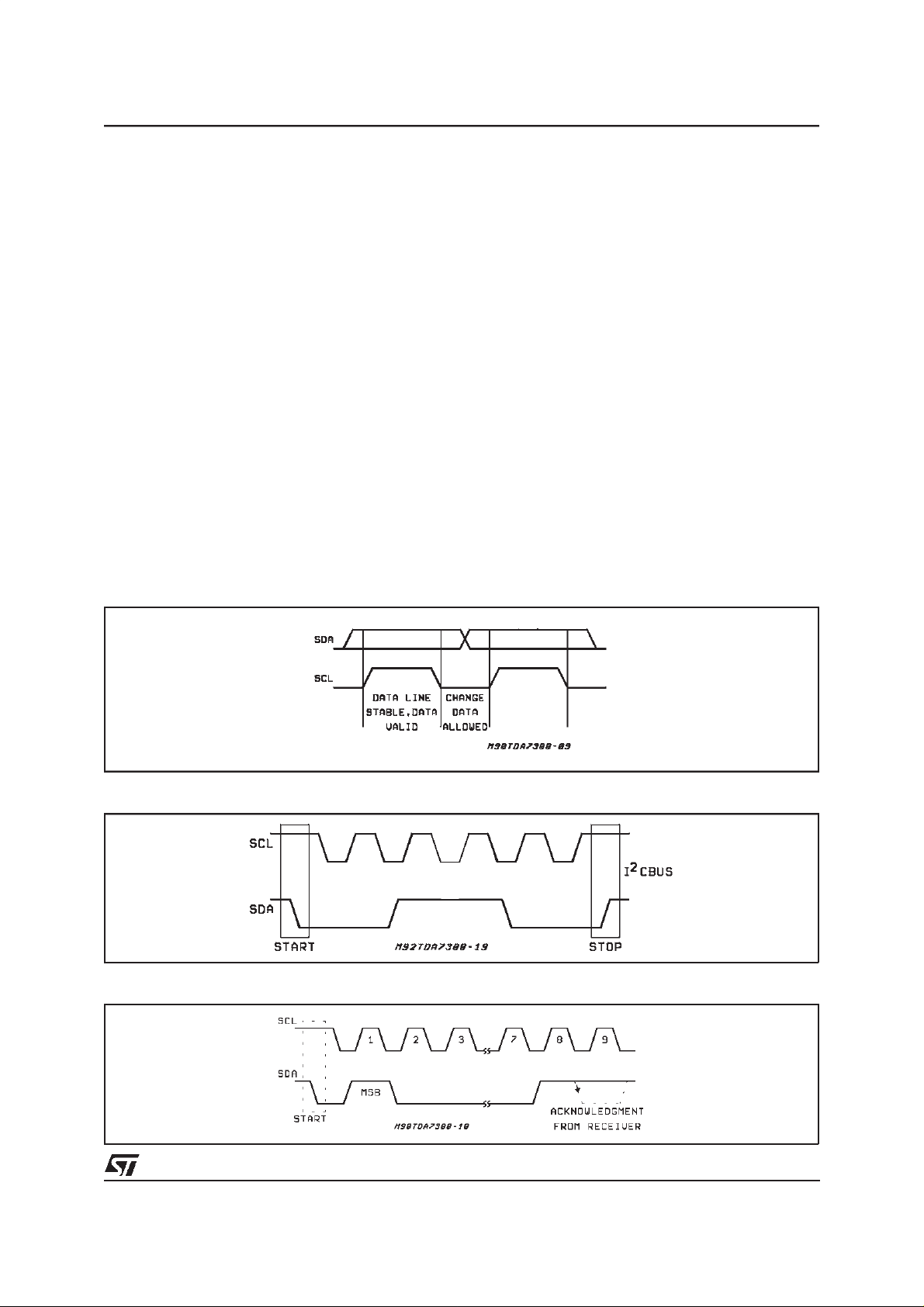

Data Validity

As shown in fig. 3, the data on the SDA line must

be stable during the high period of theclock. The

HIGH and LOW state of the data line can only

change when the clock signal on the SCL line is

LOW.

Start and StopConditions

As shown in fig.4 a start condition is a HIGH to

LOW transition of the SDA line while SCL is

HIGH. The stop condition is a LOW to HIGH transition of the SDA line while SCLis HIGH.

Byte Format

Every byte transferred on the SDA line must con-

tain 8 bits. Each byte must be followed by an ac-

Figure 3:

Data Validityon theI

2

CBUS

knowledgebit. The MSBis transferredfirst.

Acknowledge

The master (µP)puts a resistiveHIGHlevel on the

SDA line during the acknowledgeclock pulse (see

fig. 5). The peripheral (audioprocessor) that acknowledges has to pull-down (LOW) the SDA line

during the acknowledge clock pulse, so that the

SDAlineisstableLOWduringthis clockpulse.

The audioprocessor which has been addressed

has to generate an acknowledge after the reception of each byte, otherwise the SDA line remains

at the HIGH level during the ninth clock pulse

time. In this case the master transmitter can generate the STOP information in order to abort the

transfer.

Transmission withoutAcknowledge

Avoiding to detect the acknowledge of the audio-

processor,the µP can use a simplertransmission:

simply it waits one clock without checking the

slaveacknowledging,and sends the new data.

This approach of course is less protected from

misworkingand decreasesthe noise immunity.

Figure 4:

TimingDiagram of I

2

Figure 5: Acknowledgeon the I

CBUS

2

CBUS

7/18

TDA7345

SOFTWARESPECIFICATION

InterfaceProtocol

The interfaceprotocol comprises:

A startcondition (s)

A chip address byte, containing the TDA7345

address (the 8th bit of the byte must be 0).

The TDA7345 must always acknowledge at

TDA7345 ADDRESS

MSB LSB MSB LSB MSB LSB

S10000010ACK DATA ACK DATA ACK S

D94AU194

the endof eachtransmittedbyte.

A subaddress(function) bytes (identifiedby the

MSB = 0)

A sequence of dates and subaddresses (N

bytes + achnowledge. The dates are identified

by MSB = 1, subaddressesby MSB = 0)

A stopcondition (P)

Data Transferred (N-bytes + Acknowledge)

ACK = Achnowledge

S = Start

P = Stop

INTERFACEFEATURES

- Due to the fact that the MSB is used to select

if the byte transmitted is a subaddress (function) or a data (value), between a start and

stop condition, is possible to receive, how

manysubaddressesand datas as wanted.

chip address, a subaddresswith the LSB = 0 (no

incremental bus), N-datas (all these datas concern the subaddress selected), a new subaddress,N-data, a stop condition.

So it can receive in a single transmission how

many subaddress are necessary, and for each

subaddresshow manydata are necessary.

- The subaddress (function) is fixed until a new

subaddress is transmitted, so the TDA7345

can receive how many data as wantedfor the

selected subaddress (without the need for a

new startcondition)

- If TDA7345 receives a subaddress with the

LSB = 1 the incremental bus is selected, so it

enters in a loop condition that means that

every acknowledge will increase automatically the subaddress (function) and it receives the data related to the new subaddress.

2) INCREMENTAL BUS

TDA7345 receives a start condition, the correct

chip address a subaddress with the LSB = 1 (incremental bus): now it is in a loop condition with

an autoincreaseof thesubaddress.

The first data that it receives doesn’t concern the

subaddress sended but the next one, the second

one concerns the subaddresssended plus two in

the loop etc, and at the end it receives the stop

condition.

In the pictures there are some examples:

EXAMPLES

S = start

ACK= acknowledge

1) NO INCREMENTAL BUS

TDA7345 receives a start condition, the correct

B = 1 incrementalbus, B = 0 no incrementalbus

P = stop

1) one subaddress,with n dataconcerningthat subaddress(no incrementalbus)

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S10000010ACK A2 ACK DATA ACK P

D94AU195

8/18

SUBADDRESS DATA 1 ... DATA n

0A0A1 A3XX 0 1

TDA7345

2) one subaddress,(with incrementalbus) , with n data (data1that concerns subaddress+1, data 2

that concernssubaddress+ 2 etc.)

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S10000010ACK A2 ACK DATA ACK P

D94AU196

SUBADDRESS DATA 1 ... DATA n

0A0A1 A3XX 1 1

3) moresubaddress withmore data

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S10000010ACK A2 ACK DATA

D94AU197

SUBADDRESS DATA 1 ... DATA n

0A0A1 A3XX 0 1

SUBADDRESS DATA 1 ... DATA n

MSB LSB MSB LSB

ACK A2 ACK DATA ACK 1

0A0A1 A3XX 0 1

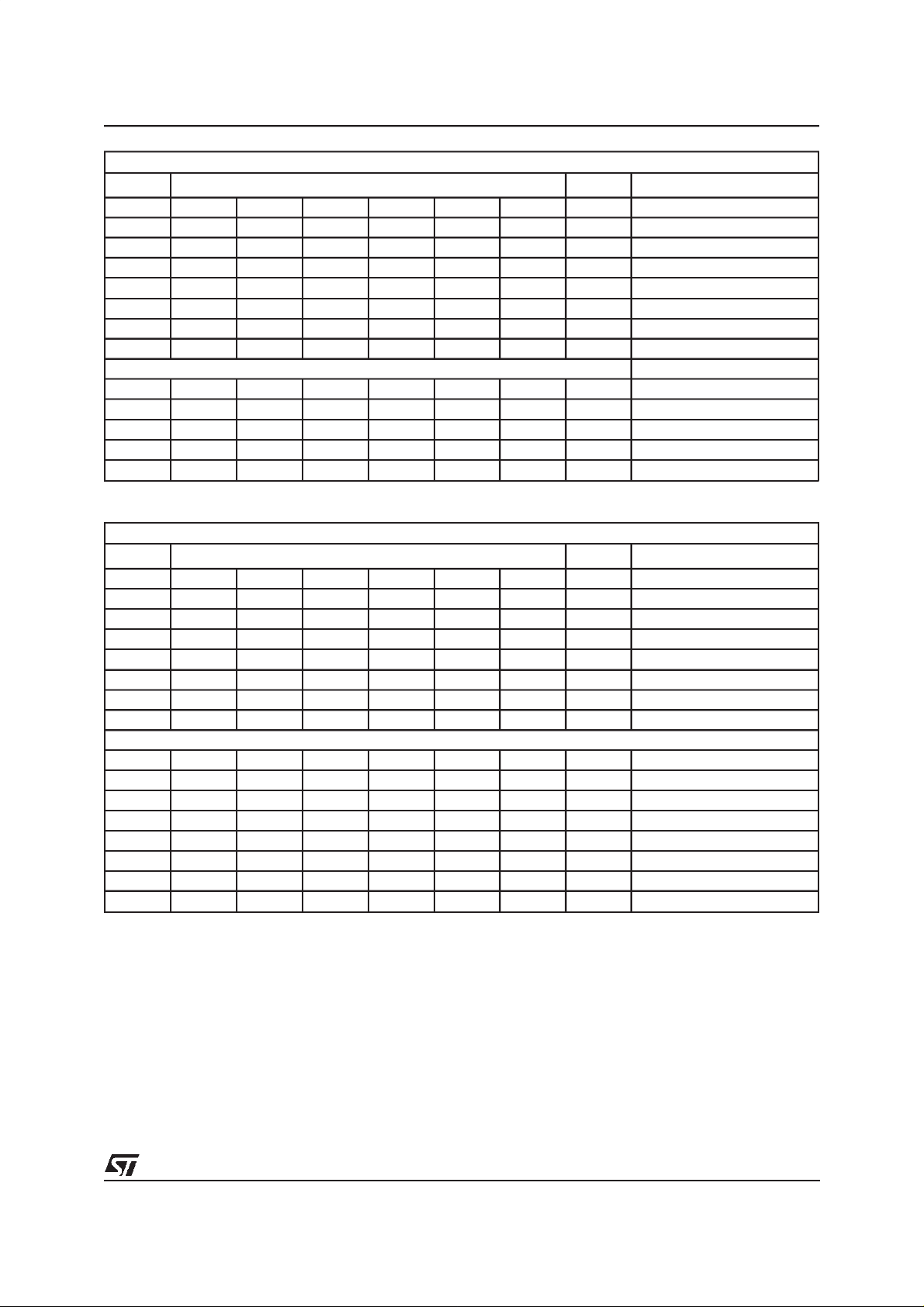

DATA BYTES

FUNCTIONSELECTION

FIRST BYTE(subaddress)

The first byte select the function,it is identifiedby theMSB = 0

MSB LSB SUBADDRESS

A0 A1 A2 A3 B

0000XXXBVOLUME ATTENUATION &

LOUDNESS

0100XXXBSURROUND & OUT &

EFFECT CONTROL

0010XXXBBASS

0110XXXBTREBLE

0001XXXBREC-OUT-R

0101XXXBREC-OUT-L

0011XXXBR

01110XXBL

OUT

OUT

01111XXBINPUT STAGE CONTROL

B = 1 yesincremental bus;

B = 0 no incremental bus;

X = indifferent 0,1

9/18

TDA7345

VALUE SELECTION

The secondbyte select the value,it is identifiedby the MSB = 1

VOLUME ATTENUATION

MSB LSB 1.25 dB STEPS

1 000 0

1 0 0 1 -1.25

1 0 1 0 -2.50

1 0 1 1 -3.75

1 1 0 0 -5.00

1 1 0 1 -6.25

1 1 1 0 -7.50

1 1 1 1 -8.75

10 dB STEPS

1 000 0

1 001 -10

1 010 -20

1 011 -30

1 100 -40

1 101 -50

1 110 -60

1 111 -70

ATT SPEAKER L AND R

MSB LSB 1.25 dB STEPS

1 000 0

1 0 0 1 -1.25

1 0 1 0 -2.50

1 0 1 1 -3.75

1 1 0 0 -5.00

1 1 0 1 -6.25

1 1 1 0 -7.50

1 1 1 1 -8.75

10 dB STEPS

1 000 0

1 001 -10

1 010 -20

1 011 -30

1 100 -40

1 101 -50

1 110 -60

1 111 -70

MUTE

10 OFF

11 ON

10/18

TDA7345

ATT REC-OUT L AND R

MSB LSB 1.25 dB STEPS

1XX 000 0

1 X X 0 0 1 -1.25

1 X X 0 1 0 -2.50

1 X X 0 1 1 -3.75

1 X X 1 0 0 -5.00

1 X X 1 0 1 -6.25

1 X X 1 1 0 -7.50

1 X X 1 1 1 -8.75

10 dB STEPS

1XX00 0

1 X X 0 1 -10

1 X X 1 0 -20

1 X X 1 1 -30

1XX11111 MUTE

TREBLE/ BASS

MSB LSB 2 dB STEPS

1XXX0111 14

1XXX0110 12

1XXX0101 10

1XXX0100 8

1XXX0011 6

1XXX0010 4

1XXX0001 2

1XXX0000 0

1XXX1000 0

1XXX1001 -2

1XXX1010 -4

1XXX1011 -6

1XXX1100 -8

1XXX1101 -10

1XXX1110 -12

1XXX1111 -14

11/18

TDA7345

SURROUND & OUT & EFFECT CONTROL

MSB LSB SELECTION

SELECTION SURROUND

1 0 0 SIMULATED

1 0 1 MUSIC

1 1 0 MOVIE

1 1 1 OFF

SELECTION EFFECT CONTROL

10000 -6

10001 -7

10010 -8

10011 -9

10100 -10

10101 -11

10110 -12

10111 -13

11000 -14

11001 -15

11010 -16

11011 -17

11100 -18

11101 -19

11110 -20

11111 -21

For exampleto selectthemusic mode, out fix, effectcontrol=-9dB:

10011101

12/18

TDA7345

INPUT CONTROL RANGE (0 TO -19.68dB)

MSB LSB 0.3125 dB STEPS

1X 000 0

1 Xx 0 0 1 -0.3125

1 X 0 1 0 -0.625

1 X 0 1 1 -0.9375

1 X 1 0 0 -1.25

1 X 1 0 1 -1.5625

1 X 1 1 0 -1.875

1 X 1 1 1 -2.1875

2.5 dB STEPS

1X000 0

1 X 0 0 1 -2.5

1 X 0 1 0 -5.0

1 X 0 1 1 -7.5

1X100 -10

1 X 1 0 1 -12.5

1X110 -15

1 X 1 1 1 -17.5

POWER ON RESET

VOLUME ATTENUATION MAX ATTENUATION,

TREBLE -14dB

BASS -14dB

SURROUND + EFFECT CONTROL OFF + MAX ATTENUATION

ATT SPEAKER R MUTE

ATT SPEAKER L MUTE

ATT REC-OUT L MUTE

ATT REC-OUT R MUTE

13/18

TDA7345

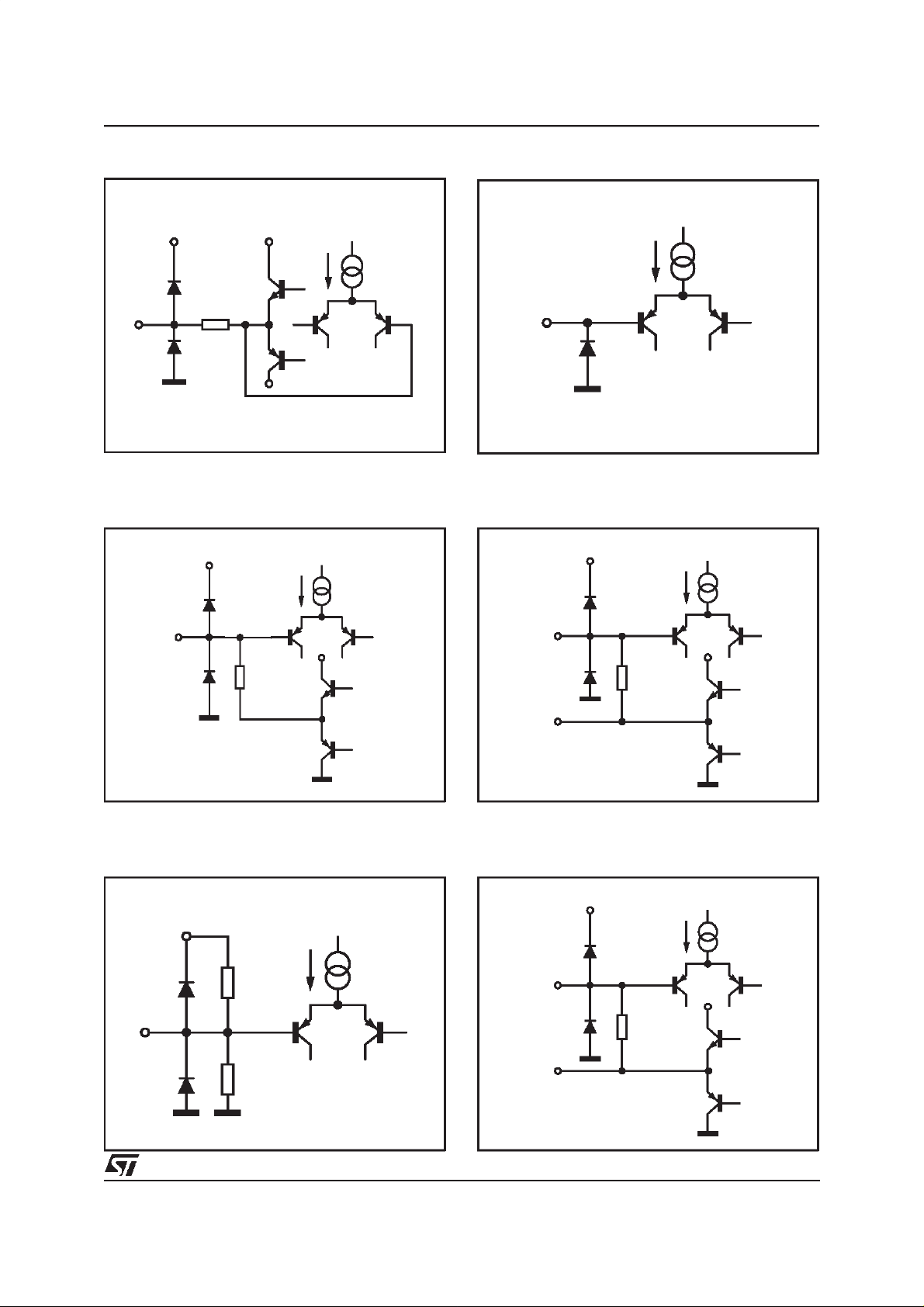

PIN:

PIN:

HP1

L

in,Rin

LP1

HP2

PIN:

HP2

V

GND

S

V

20µA

5.5K

60K

5.5K

D94AU199

S

V

S

10K

60K

GND

D94AU198

V

S

HP1

PIN:

BASS- LA, BASS - RA

20µA

20µA

50K

GND

V

REF

PIN: BASS- LB,BASS- RB

V

S

BASS-LA

BASS-RA

D94AU200

48KGND

20µA

D94AU202

BASS-LB

GND

BASS-RB

PIN: TREBLE- L, TREBLE- R

V

S

25K

48K

D94AU201

20µA

D94AU203

14/18

TDA7345

PIN:

PIN:

L

LP

OUT

,

V

, REC-OUT-1REC-OUT-R

R

OUT

S

20µA

PIN:

SCL,SDA

20µA

100Ω

D94AU204

PIN:

PS3, PS2

V

V

S

20µA

S

D94AU205

20µA

PIN:

C

REF

V

S

GND

D94AU206

10K

50K

50K

20µA

D94AU208

PIN:

PS2

PS3A

PS4A

PS2A

D94AU207

V

S

D94AU209

18.08K

20µA

398Ω

15/18

TDA7345

PIN:

PIN:

PS1

PS1A

D94AU210

REAR OUT

V

S

PIN:

LP1

V

S

20µA

V

S

20µA

17.95K

10K

HP1

D94AU211

PIN:

REAR IN

V

S

20µA

D94AU214

20µA

20K

20K

D94AU215

16/18

TDA7345

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.1 0.3 0.004 0.012

b 0.35 0.49 0.014 0.019

b1 0.23 0.32 0.009 0.013

C 0.5 0.020

c1 45° (typ.)

D 17.7 18.1 0.697 0.713

E 10 10.65 0.394 0.419

e 1.27 0.050

e3 16.51 0.65

F 7.4 7.6 0.291 0.299

L 0.4 1.27 0.016 0.050

S8°(max.)

mm inch

OUTLINE AND

MECHANICAL DATA

SO28

17/18

TDA7345

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change withoutnotice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registeredtrademark of STMicroelectronics

1999 STMicroelectronics – Printed in Italy– AllRights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

18/18

Loading...

Loading...