DIGITAL CONTROLLED STEREO AUDIO PROCESSOR

INPUTMULTIPLEXER:

- 3 STEREO INPUTS

- SELECTABLEINPUT GAIN FOR OPTIMAL

ADAPTIONTO DIFFERENTSOURCES

LOUDNESSFUNCTION

VOLUMECONTROL IN 1.25dBSTEPS

TREBLEAND BASS CONTROL

FOURSPEAKERATTENUATORS:

- 4 INDEPENDENTSPEAKERSCONTROL

IN 1.25dB STEPS FOR BALANCEAND

FADERFACILITIES

- INDEPENDENTMUTE FUNCTION

ALL FUNCTIONS PROGRAMMABLE VIA SE-

2

RIAL I

DESCRIPTION

The TDA7313N is a vo l ume, tone (bass and treble)

balance (Left/Ri ght) and fader (front/rear) processor

for quality audio applications in car radio and Hi-Fi

systems.

Selectableinput gainand external loudnessfunction

C BUS

TDA7313N

WITH LOUDNESS

DIP28 SO28

ORDERING NUMBERS:

TDA7313N TDA7313ND

are provided. Control is accomplished by serial

2

C busmic r oproces s orinterface.

I

TheACsignalsettingisobtainedbyresistornetwo rks

andswitchescombinedwithoperationalamplifiers.

Thanks to the used BIPOLAR/C MOS Tecnol ogy ,

LowDistortion, LowNoiseandLow DC steppingare

obtained.

PIN CONNECTION (Topview)

November 1999

1/14

TDA7313N

TEST CIRCUIT

THERMAL DATA

Symbol Description SO28 DIP28 Unit

R

thj-pins

Thermal Resistance Junction-pins max 85 65 °C/W

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

T

amb

T

stg

Operating Supply Voltage 10.2 V

S

Operating Ambient Temperature -40 to 85 °C

Storage Temperature Range -55 to +150

QUICK REFERENCE DATA

Symbol Parameter Min. Typ. Max. Unit

V

V

CL

THD Total Harmonic DistortionV = 1Vrms f = 1KHz 0.01 0.1 %

S/N Signal to Noise Ratio 106 dB

S

Supply Voltage 6 9 10 V

S

Max. input signal handling 2 Vrms

Channel Separation f = 1KHz 103 dB

C

Volume Control 1.25dB step -78.75 0 dB

Bass and TrebleControl 2db step -14 +14 dB

Fader and Balance Control 1.25dB step -38.75 0 dB

Input Gain 3.75dB step 0 11.25 dB

Mute Attenuation 100 dB

C

°

2/14

BLOCK DIAGRAM

TDA7313N

BUS

C17

5.6K R2

C11

2.7nF

100nF

100nF

100nF

TREBLE(L)

C15

BIN(L)

BOUT(L)

C14

LOUD(L)

SPKR

4

18

19

12

ATT

FRONT

OUT LEFT

25

RB

MUTE

ATT

SPKR

TREBLE

BASS

VOL

REAR

OUT LEFT

23

+ LOUD

MUTE

SCL

SDA

282726

SERIAL BUS DECODER + LATCHES

DIGGND

SPKR

RIGHT

OUT

24

ATT

BASS TREBLE

VOL

+ LOUD

FRONT

MUTE

ATT

SPKR

RIGHT

REAR

OUT

22

RB

MUTE

D98AU888

TREBLE(R)

5

BOUT(R) BIN(R)

21 20

LOUD(R)

8

C13

100nF

C12

100nF

C16

2.7nF

5.6K R1

C10

100nF

C9 2.2µF

17 16

OUT(L) IN(L)

INPUT

+ GAIN

SELECTOR

3x

2.2µF

L1 15L1L2 14L2L3 13

C1

C2

LEFT

INPUTS

C3

L3

R3 9R3R2 10R2R1 11

C4

C5

RIGHT

INPUTS

C6

R1

3x

2.2µF

76

OUT(R) IN(R)

SUPPLY

AGND CREF

231

V

C8 2.2µF

22µFC7

S

3/14

TDA7313N

ELECTRICALCHARACTERISTICS (refer tothe test circuit T

R

= 600Ω, all controlsflat(G = 0), f = 1KHz unless otherwise specified)

G

=25°C, VS= 9V,RL= 10KΩ,

amb

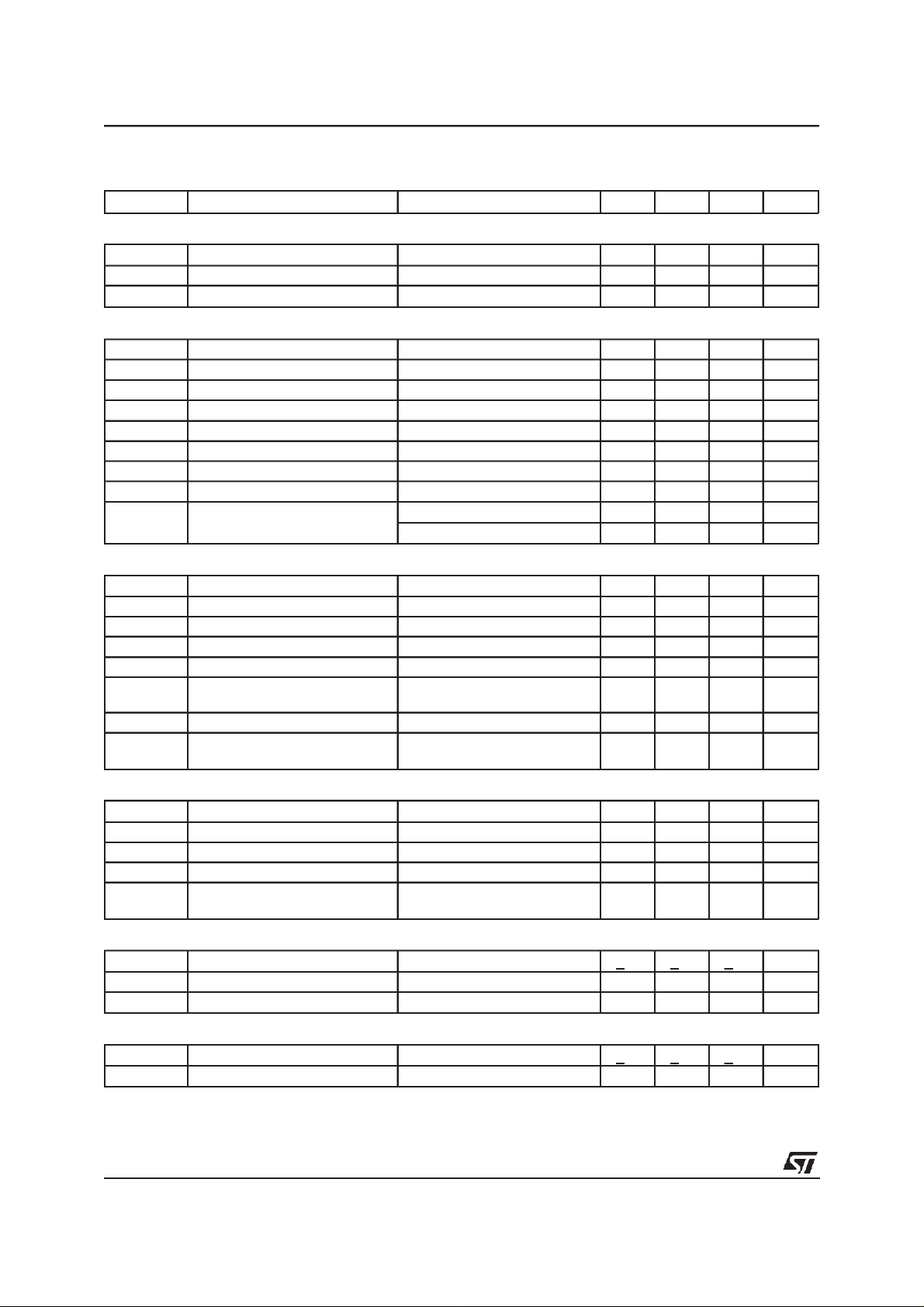

Symbol Parameter Test Condition Min. Typ. Max. Unit

SUPPLY

V

S

I

S

SVR Ripple Rejection 60 80 dB

Supply Voltage 6 9 10 V

Supply Current 8 11 mA

INPUT SELECTORS

G

G

G

V

R

II

V

CL

S

IN

R

L

INmin

INmax

STEP

e

IN

DC

Input Resistance Input 1, 2, 3 35 50 70 KΩ

Clipping Level 2 2.5 Vrms

Input Separation (2) 80 100 dB

Output Load resistance pin 7, 17 2 KΩ

Min. Input Gain -1 0 1 dB

Max. Input Gain 11.25 dB

Step Resolution 3.75 dB

Input Noise G = 11.25dB 2

DC Steps adjacent gain steps 4 20 mV

G = 18.75 to Mute 4 mV

VOLUMECONTROL

R

IV

C

RANGE

A

VMIN

A

VMAX

A

STEP

E

A

E

T

V

DC

Input Resistance 20 33 50 kΩ

Control Range 70 75 80 dB

Min. Attenuation -1 0 1 dB

Max. Attenuation 70 75 80 dB

Step Resolution 0.5 1.25 1.75 dB

Attenuation Set Error Av = 0 to -20dB

Av = -20 to -60dB

-1.25

-3

0 1.25

2

Tracking Error 2dB

DC Steps adjacent attenuation steps

From 0dB to Av max

0

0.5

3

7.5

SPEAKERATTENUATORS

µ

dB

dB

mV

mV

V

C

S

A

range

STEP

E

MUTE

V

DC

A

Control Range 35 37.5 40 dB

Step Resolution 0.5 1.25 1.75 dB

Attenuation set error 1.5 dB

Output Mute Attenuation 80 100 dB

DC Steps adjacent att. steps

from 0 to mute

0

1

BASS CONTROL(1)

Gb Control Range Max. Boost/cut +12 +14 +16 dB

B

STEP

R

B

Step Resolution 1 2 3 dB

Internal Feedback Resistance 34 44 58 KΩ

TREBLECONTROL(1)

Gt Control Range Max. Boost/cut +13 +14 +15 dB

Step Resolution 1 2 3 dB

4/14

T

STEP

10

3

mV

mV

TDA7313N

ELECTRICALCHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

AUDIO OUTPUTS

V

OCL

R

L

C

L

R

OUT

V

OUT

Clipping Level d = 0.3% 2 2.5 Vrms

Output Load Resistance 2 KΩ

Output Load Capacitance 10 nF

Output resistance 30 75 120 Ω

DC Voltage Level 4.2 4.5 4.8 V

GENERAL

e

NO

S/N Signal to Noise Ratio all gains = 0dB; V

d Distortion A

Sc Channel Separation left/right 80 103 dB

Output Noise BW = 20-20KHz, flat

output muted

all gains = 0dB

A curve all gains = 0dB 3 µV

O

=0,VIN= 1Vrms

V

A

= -20dB VIN= 1Vrms

Total Tracking error A

V

= 0 to -20dB

V

V

= 0.3Vrms

IN

-20 to -60 dB

2.5

515

µ

µV

= 1Vrms 106 dB

0.01

0.09

0.04

0

0

0.1

0.3

1

2

%

%

%

dB

dB

V

BUS INPUTS

V

IL

V

IH

I

IN

V

O

Notes:

(1) Bass and Trebleresponse seeattached diagram(fig.16). The center frequencyand quality ofthe resonance behaviour can be choosen by

the external circuitry. A standard first order bass response can be realized by a standard feedback network

(2) The selected input is groundedthru the 2.2µF capacitor.

Input Low Voltage 1V

Input High Voltage 3 V

Input Current -5 +5 µA

Output Voltage SDA

IO= 1.6mA 0.4 V

Acknowledge

Figure 1: Loudnessvs. VolumeAttenuation

Figure2: Loudnessvs. Frequency(C

100nF) vs. Volume Attenuation

LOUD

=

5/14

TDA7313N

Figure 3: Loudnessvs. ExternalCapacitors

Figure 5: Signalto Noise Ratio vs. Volume

Setting

Figure4: Noisevs.Volume/GainSettings

Figure6: Distortion& Noisevs. Frequency

Figure 7: Distortion& Noise vs. Frequency

6/14

Figure8: Distortionvs. Load Resistance

TDA7313N

Figure 9: ChannelSeparation(L → R) vs.

Frequency

Figure 11: SupplyVoltageRejection vs.

Frequency

Figure10: InputSeparation(L1→L2, L3, L4) vs.

Frequency

Figure12: OutputClipping Level vs. Supply

Voltage

Figure14: SupplyCurrent vs. TemperatureFigure 13: QuiescentCurrent vs. SupplyVoltage

7/14

TDA7313N

Figure 15: BassResistancevs. Temperature

I2C BUSINTERFACE

Data transmission from microprocessor to the

TDA7313N and viceversa takes place thru the 2

wires I

2

C BUS interface, consisting of the two

lines SDA and SCL (pull-up resistors to positive

supply voltage must be connected).

Data Validity

As shown in fig. 17, the data on the SDA line

must be stable during thehigh period of the clock.

The HIGH and LOW state of the data line can

only change when the clock signal on the SCL

line is LOW.

Start and Stop Conditions

As shown in fig.18 a start condition is a HIGH to

LOW transition of the SDA line while SCL is

HIGH. The stop condition is a LOW to HIGH transition of the SDA line while SCL is HIGH.

Byte Format

Every byte transferred on the SDA line must contain 8 bits. Each byte must be followed by an acknowledgebit. The MSB is transferredfirst.

Figure16: TypicalTone Response (with theext.

components indicated in the test

circuit)

Acknowledge

The master(µP) puts a resistive HIGH level on the

SDA line during the acknowledgeclock pulse (see

fig. 19). The peripheral (audioprocessor) that acknowledges has to pull-down (LOW) the SDA line

during the acknowledge clock pulse, so that the

SDAlineisstableLOWduringthis clockpulse.

The audioprocessor which has been addressed

has to generate an acknowledge after the reception of each byte, otherwise the SDAline remains

at the HIGH level during the ninth clock pulse

time. In this case the master transmitter can generate the STOP information in order to abort the

transfer.

Transmissionwithout Acknowledge

Avoiding to detect the acknowledge of the audioprocessor, the µP can use a simplier transmission: simply it waits one clock without checking

the slave acknowledging, and sends the new

data.

This approach of course is less protected from

misworkingand decreasesthe noise immunity.

Figure 17: Data Validityon the I

8/14

2

CBUS

Figure 18: TimingDiagramof I2CBUS

TDA7313N

Figure 19: Acknowledgeon the I

SOFTWARESPECIFICATION

Interface Protocol

The interface protocol comprises:

A start condition (s)

A chip address byte, containingthe TDA7313N

TDA7313N ADDRESS

MSB first byte LSB MSB LSB MSB LSB

S10001000

ACK = Acknowledge

S = Start

P = Stop

MAX CLOCK SPEED 100kbits/s

2

CBUS

ACK

address(the 8th bit ofthe bytemust be 0). The

TDA7313N must always acknowledge at the

end of each transmittedbyte.

A sequenceof data (N-bytes+ acknowledge)

A stopcondition (P)

DATA

Data Transferred (N-bytes + Acknowledge)

ACK

DATA

ACK

P

SOFTWARESPECIFICATION

Chip address

1

MSB

DATA BYTES

Ax = 1.25dB steps; Bx= 10dB steps; Cx= 2dB steps; Gx = 3.75dB steps

0001000

MSB LSB FUNCTION

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

1

B2

0

1

0

1

0

1

1

B1

B1

B1

B1

B1

G1

0

1

LSB

B0

B0

B0

B0

B0

G0

C3

C3

A2

A2

A2

A2

A2

S2

C2

C2

A1

A1

A1

A1

A1

S1

C1

C1

A0

A0

A0

A0

A0

S0

C0

C0

Volume control

Speaker ATT LR

Speaker ATT RR

Speaker ATT LF

Speaker ATT RF

Audio switch

Bass control

Treble control

9/14

TDA7313N

SOFTWARESPECIFICATION (continued)

DATA BYTES (detailed description)

Volume

MSB LSB FUNCTION

0 0 B2 B1 B0 A2 A1 A0 Volume 1.25dB steps

0

0

0

0

1

1

1

1

0 0 B2 B1 B0 A2 A1 A0 Volume 10dB steps

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

1

1

0

0

1

1

For example a volume of -45dBis given by:

00100100

0

1

0

1

0

1

0

1

0

-1.25

-2.5

-3.75

-5

-6.25

-7.5

-8.75

0

-10

-20

-30

-40

-50

-60

-70

Speaker Attenuators

MSB LSB FUNCTION

1

1

1

1

0

0

1

1

0

1

0

1

B1

B1

B1

B1

0

0

1

1

11111 Mute

B0

B0

B0

B0

0

1

0

1

A2

A2

A2

A2

0

0

0

0

1

1

1

1

A1

A1

A1

A1

0

0

1

1

0

0

1

1

A0

A0

A0

A0

0

1

0

1

0

1

0

1

Speaker LF

Speaker RF

Speaker LR

Speaker RR

For example attenuationof 25dBon speakerRF is given by:

10110100

0

-1.25

-2.5

-3.75

-5

-6.25

-7.5

-8.75

0

-10

-20

-30

10/14

TDA7313N

Audio Switch

MSB LSB FUNCTION

0 1 0 G1 G0 S2 S1 S0 AudioSwitch

0

0

1

0

1

0

0

1

1

0

1

0

1

1

0

1

0

1

For example to select the stereo 2 input with a gain of +7.5dBLOUDNESSON the 8bitstring is:

01001001

(*) Stereo 4 is connectedinternally,but not availableon pins.

Bass andTreble

Stereo 1

Stereo 2

Stereo 3

Stereo 4 (*)

LOUDNESS ON

LOUDNESS OFF

+11.25dB

+7.5dB

+3.75dB

0dB

0

0

1

1

1

1

0

1

C3

C3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

C2

C2

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

C3 = Sign

For example Bass at -10dB is obtainedby the following8 bit string:

01100010

C1

C1

0

0

1

1

0

0

1

1

1

1

0

0

1

1

0

0

C0

C0

Bass

Treble

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

-14

-12

-10

-8

-6

-4

-2

0

0

2

4

6

8

10

12

14

11/14

TDA7313N

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.1 0.3 0.004 0.012

b 0.35 0.49 0.014 0.019

b1 0.23 0.32 0.009 0.013

C 0.5 0.020

c1 45° (typ.)

D 17.7 18.1 0.697 0.713

E 10 10.65 0.394 0.419

e 1.27 0.050

e3 16.51 0.65

F 7.4 7.6 0.291 0.299

L 0.4 1.27 0.016 0.050

S8°(max.)

mm inch

OUTLINE AND

MECHANICAL DATA

SO28

12/14

TDA7313N

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

a1 0.63 0.025

b 0.45 0.018

b1 0.23 0.31 0.009

b2 1.27 0.050

D 37.34 1.470

E 15.2 16.68 0.598 0.657

e 2.54 0.100

e3 33.02 1.300

F 14.1 0.555

I 4.445 0.175

L 3.3 0.130

mm inch

0.012

OUTLINE AND

MECHANICAL DATA

DIP28

13/14

TDA7313N

Purchase of I2C Components of STMicroelectronics, conveys a license under the Philips I2C Patent

Rights to use these components in an I

2

C system, provided that the system conforms to the I2C

Standard Specificationsas definedby Philips.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change without notice. This publicationsupersedes and replaces all informationpreviously supplied. STMicroelectronics products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

1999 STMicroelectronics – Printed in Italy – AllRights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China- Finland - France - Germany - HongKong - India - Italy - Japan - Malaysia - Malta- Morocco -

14/14

Singapore - Spain - Sweden - Switzerland - UnitedKingdom - U.S.A.

http://www.st.com

Loading...

Loading...