SGS Thomson Microelectronics STV9432 Datasheet

STV9432

100MHz OSD FOR MONITOR

FEATURE

• 100MHz MAX. PIXEL CLOCK, AVAILABLE FOR

ANY LINE FREQUENCY BETWEEN 15 AND

140 kHz

• 12 x 18 CHARACTER ROM FONT INCLUDES:

- 240 MONOCOLOR CHARA CTE RS

- 16 MULTICOLOR CHARACTERS

• CHARACTER FLASHING

• UP TO 1K CHARACTERS TEXT DISPLAY

• ULTRA HIGH FREQUENCY PLL FOR JITTERFREE DISPLAY

• FLEXIBLE DISPLAY:

- ANY CHARACTER WIDTH AND HEIGHT

- ANYWHERE IN THE SCREEN

• SINGLE BYTE CHARACTER CODES AND

COLOR LOOK-UP TABLE FOR EASY PROGRAMMING AND FAST ACCESS

• CHARACTER FLIP OPERATIONS

• WIDE DISPLAY WINDOW ALLOWS PATTERN

GENERATION FOR FACTORY ADJUSTMENTS

2

•I

C BUS MCU INTERFACE

DESCRIPTION

2

Connected to a host MCU via a serial I

C Bus, the

STV9432TA is a multifunction slave peripheral

device integrating the ON-Screen-Display block.

The On-screen Display (OSD) includes a MASK

PROGRAMMABLE ROM that holds the CUSTOM

CHARACTER FONT, a 1Kbytes RAM that stores

the code strings of the different lines of t ext to be

displayed, and a set of registers to program character sizes and colors. A built-in digital PLL, operating at very high frequency, provides an accurate

display without visible jitter for a wide line frequency range from 15 to 140 kHz.

.

SDIP24 (Plastic Package)

ORDER CODE: STV9432

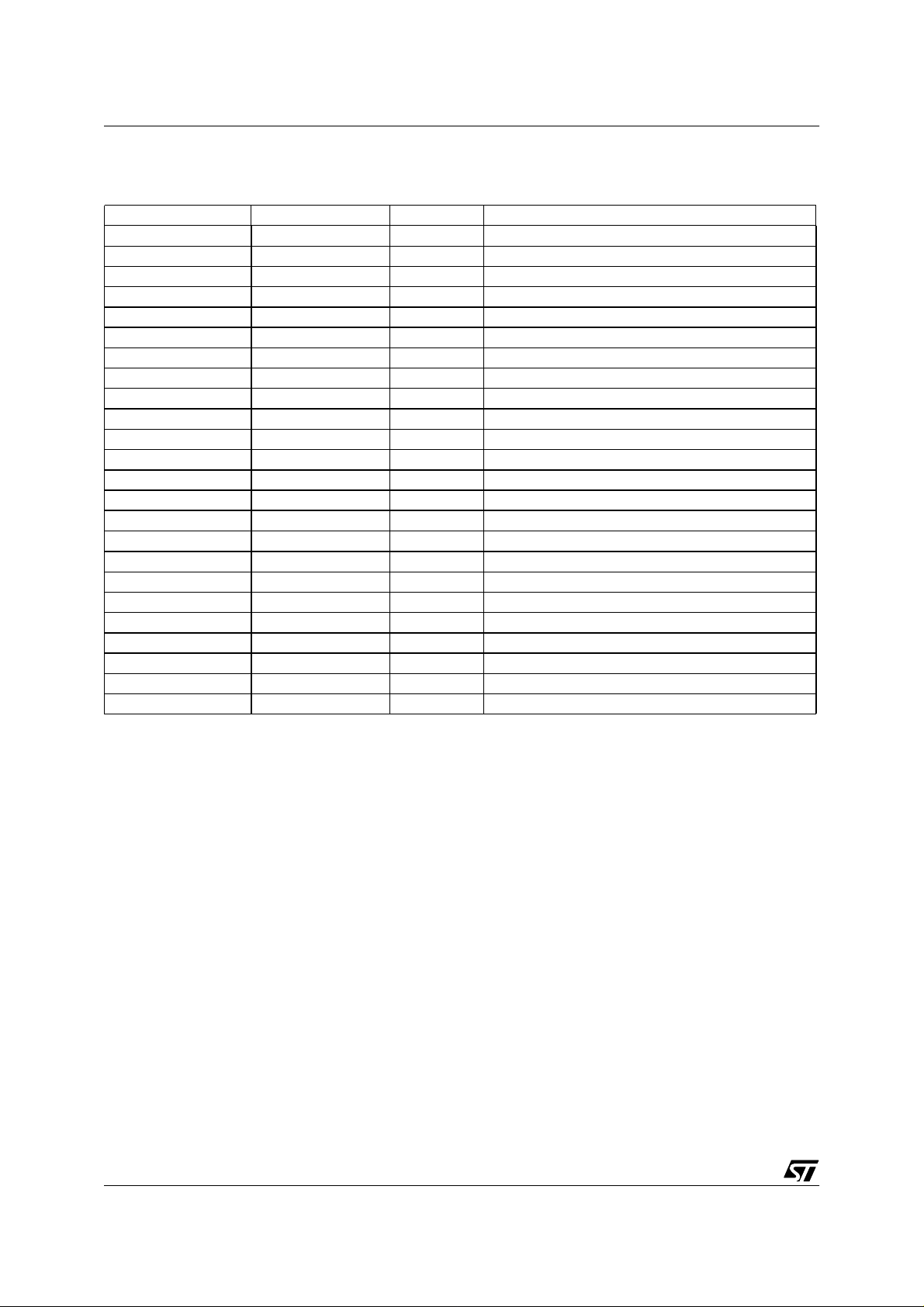

PIN CONNECTIONS

1

2

SDA

SCL

HS

VS

HFLY

N.C

DV

DV

XTI

XTO OV

3

4

5

6

7

8

9

DD

10

SS

11

12

24

23

22

21

20

19

18

17

16

15

14

13

TESTFILTER

ADCREFAGND

N.C

N.C

N.C

AV

DD

OV

DD

FBLK

BOUT

GOUT

ROUT

SS

Version 4.0

February 2000 1/16

This is preliminary information on a new product in development or undergoing evaluation. Details are subject to change without notice.

1

STV9432

1 - PIN DESCRIPTION

Pin Number Symbol Type Description

1 FILTER I/O PLL Filter

2 AGND Power Analog Ground

3 SDA I/O I

4 SCL I

5 HS Horizontal Sync Input

6 VS Vertical Sync Input

7 HFLY Horizontal Flyback Input

8 N.C. Not Connected

9 DV

10 DV

DD

SS

Power Digital +5V Power Supply

Power Digital Ground

11 XTI Crystal Oscillator Input

12 XTO O Crystal Oscillator Output

13 OV

SS

Power Ground for the RGB Outputs

14 ROUT O Red Output

15 GOUT O Green Output

16 BOUT O Blue Output

17 FBLK O Fast Blanking Output

18 OV

19 AV

DD

DD

Power +5V Supply for the RGB Outputs

Power Analog +5V Power Supply

20 N.C. Not Connected

21 N.C. Not Connected

22 N.C. Not Connected

23 ADCREF I/O ADC Reference Voltage Pin

24 TEST I/O Pin must be connected to ground

2

C Bus Serial Data

2

C Bus Serial Clock

2/18

2 - BLOCK DIAGRAM

24

TEST

HFLY

VS

HS

N.C

N.C

N.C

N.C

AV

DV

1

7

6

5

8

22

21

20

23

19

DD

9

DD

FILTER

ADCREF

OSCILLATOR

PLL

3.3V

VOLTAGE REGULATOR

POWER-ON RESET

CONTROLLER

1k BYTES R A M

DISPLAY

CHARACTER

FONT ROM

2

C BUS

I

INTERFACE

STV9432

STV9432

11

XTI

12

XTO

18

OV

DD

13

OV

SS

14

ROUT

15

GOUT

16

BOUT

17

FBLK

3

SDA

4

SCL

10

DV

SS

2

AGND

3 - ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

AV

, DVDD, OV

DD

V

IN

T

oper

T

stg

Supply Voltage -0.3, +6.0 V

DD

Input Voltage VSS - 0.3, VDD + 0.3 V

Operating Temperatu re 0, +70

Storage Temperature -40, +125

o

C

o

C

3/18

STV9432

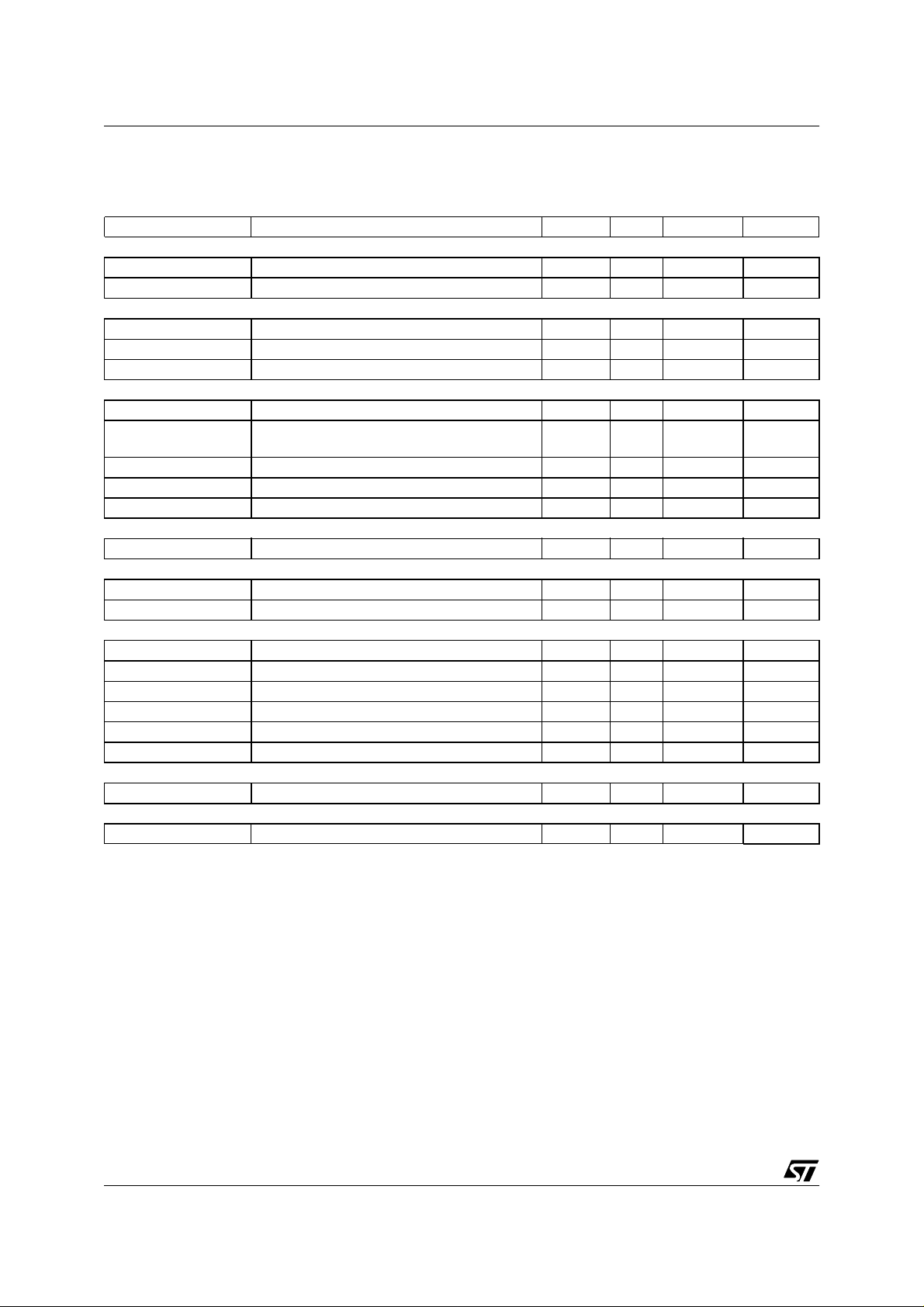

4 - ELECTRIC AL CHARACTERISTICS

(V

= 5V, VSS = 0V, GND = 0V, TA = 0 to 70o, unless otherwise specified)

DD

Symbol Parameter Min. Typ. Max. Unit

SUPPLY

AV

, DVDD, OV

DD

+ DIDD + OI

AI

DD

INPUTS (SCL, SDA)

V

IL

V

IH

I

IL

INPUTS (HS, VS, HFLY)

V

IL

V

IH

V

HYST

I

PU

HSIN Horizontal Synchro Input Range 15 140 kHz

OUTPUTS (SDA open drain)

V

OL

OUTPUTS (R, G, B, FBLK)

V

OL

V

OH

OSCILLATOR (XTI, XTO)

I

IL

I

IH

V

IL

V

IH

V

OL

V

OH

ADCREF

V

REF

POWER-ON RESE T

DV

DDTH

Supply Voltage 4.75 5 5.25 V

DD

Analog and Digital Supply Current - - 150 mA

DD

Input Low Voltage 0.8 V

Input High Voltage 2.4 V

Input Leakage Current -1 +1 µA

Input Low Voltage 0.8 V

Input High Voltage HS, VS

HFLY

2.4

3.6

V

Schmidt Trigger Hysteresis 0.4 V

Pull-up Source Current (V

= 0V) 100 µA

IN

Output Low Voltage (IOL = 3mA) 0 0.4 V

Output Low Voltage (IOL = 3mA) 0 0.4 V

Output High Voltage (IOH = 3mA) 0.8V

DD

VDDV

XTI Input Source Current (VIN = 0V) 3 15 µA

XTI Input Sink Current (VIN = VDD)3 15µA

XTI Input Low Voltage 1.4 V

XTI Input High Voltage 0.7V

DD

V

XTI Output Low Voltage (IOL = 3mA) 0 0.4 V

XTI Output High Voltage (IOH = 3mA) 0.8V

DD

VDDV

Output Voltage Reference 3.3 V

Supply Threshold Level 3.6 V

4/18

STV9432

5 - TIMINGS

Symbol Parameter Min. Typ. Max. Unit

OSCILLATOR

f

OSC

f

PXL

R, G, B, FBLK (C

t

R

t

F

t

SKEW

2

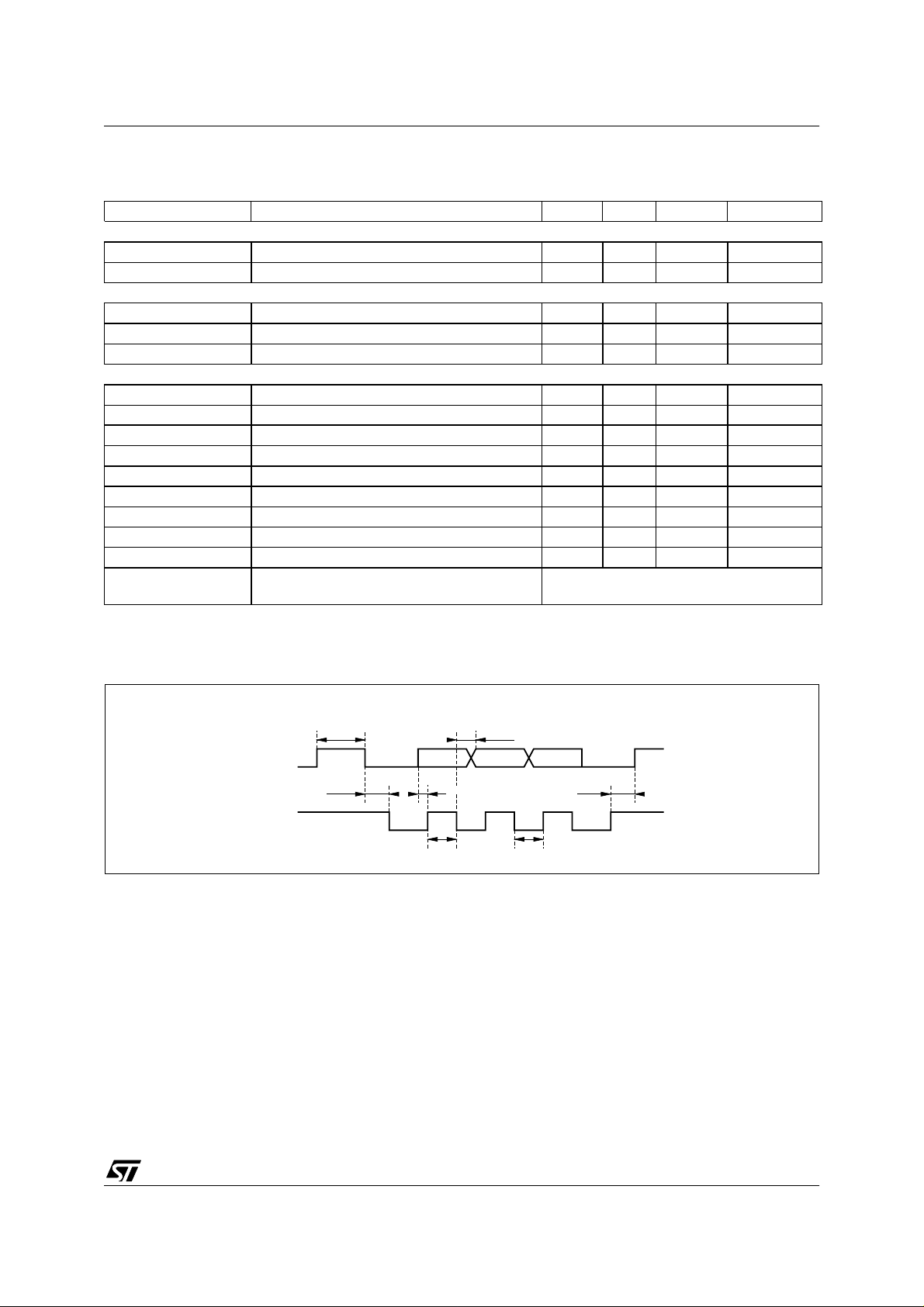

C INTERFACE: SDA AND SCL (see Figure 1)

I

f

SCL

t

BUF

t

HDS

t

SUP

t

LOW

t

HIGH

t

HDAT

t

SUDAT

t

F

t

R

Note : These parameters are not tested on each unit. They are measured during our internal qualification procedure which

includes characterization on batches comming from corners of our processes and also temperature characterization

Clock Frequency 8 MHz

Pixel Frequency 100 MHz

= 30pF)

LOAD

Rise Time (see Note 1) 5 ns

Fall Time (see Note 1) 5 ns

Skew between R, G, B, FBLK 5 ns

SCL Clock Frequency 0 400 kHz

Time the bus must be free between 2 access 500 ns

Hold Time for Start Condition 500 ns

Set up Time for Stop Condition 500 ns

The Low Period of Clock 400 ns

The High Period of Clock 400 ns

Hold Time Data 0 ns

Set up Time Data 500 ns

Fall Time of SDA 20 ns

Rise Time of both SCL and SDA

Depend on the pull-up resistor and the load

capacitance

Figure 1.

STOP START DATA

t

BUF

SDA

t

HDS

SCL

t

HIGH

t

SUDAT

t

HDAT

t

LOW

t

SUP

STOP

5/18

STV9432

6 - SERIAL INTERFACE

The 2-wires serial interface is an I2C interface. To be

connected to the I

address; the slave address of the STV9432 is BA (in

hexadecimal).

A6 A5 A4 A3 A2 A1 A0 RW

1011101

2

C bus, a devic e mu st o wn its slave

- The two bytes of the internal address where the

MCU wants to write data(s),

- The successive bytes of data(s).

All bytes are sent MSB bit first and the write data

transfer is ended with a stop.

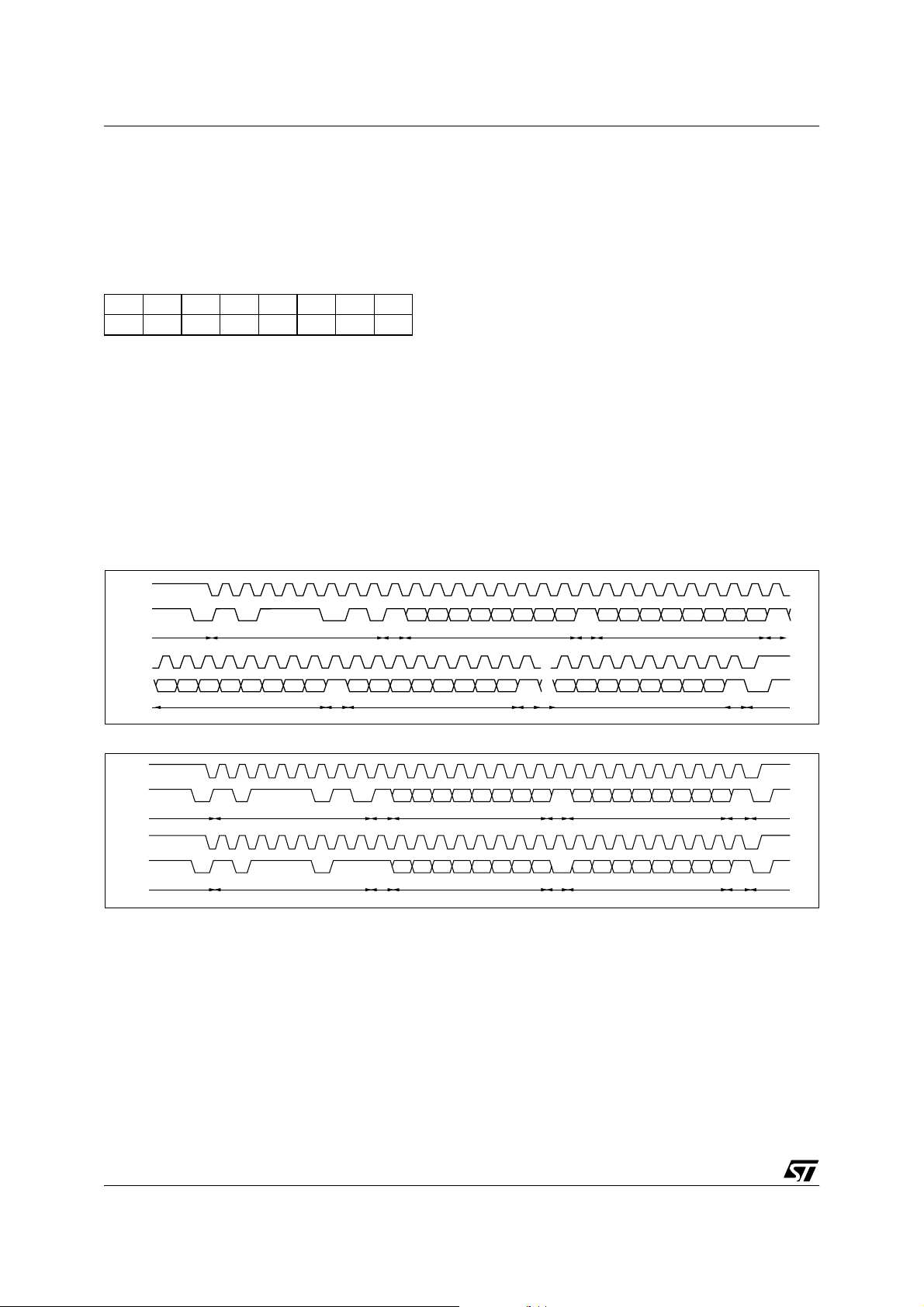

6.2 - DATA TRANSFER IN READ MODE

6.1 - DATA TRANSFER IN WRITE MODE

The host M CU c an write data in to the STV 943 2 registers or RAM.

To write data into the STVA9432TA after a start, the

MCU must send (Figure 2):

- First, the I

2

C address slave byte with a low level for

the R/W bit,

Figure 2. I2C Write Operation

SCL

SDA

SCL

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

SDA

Figure 3. I

SCL

SDA

Start

I2C Slave Address

2

C Read Operation

I2C Slave Address

R/W

A7 A6 A5 A4 A3 A2 A1 A0 - - A13 A12 A11 A10 A9 A8

ACK LSB Address ACK MSB Address ACKStart

ACK ACKData Byte 1 Data Byte 2 ACK Data Byte n Stop

R/W

A7 A6 A5 A4 A3 A2 A1

ACK

The host MCU can read data from the STV9432 registers, RAM or ROM.

To read data from the STV9432 (Figure 3), the MCU

must send 2 different I

includes the I

2

C slave address byte with R/W bit at

2

C sequences. The first one

low level and the 2 internal addr es s byte s.

The second one includes the I

2

C slave address byte

with R/W bit at high level and all the successive data

bytes read at successive addresses starting from the

initial address given by the first sequence.

A0

--

A13 A12

A10

A10A9A8

LSB Address ACK

MSB Address

ACK

Stop

6/18

SCL

SDA

Start

I2C Slave Address

D7 D6 D5 D4 D3 D2 D1 D0

R/W

*

ACK

Data Byte 1

D7 D6 D5 D4 D3 D2 D1 D0

ACK

Data Byte n

ACK

Stop

Loading...

Loading...