SGS Thomson Microelectronics STV9426, STV9425B, STV9425 Datasheet

MULTISYNCON-SCREEN DISPLAY FOR MONITOR

.

CMOSSINGLE CHIP OSD FOR MONITOR

.

BUILTIN1 KBYTERAM HOLDING:

- PAGES’DESCRIPTORS

- CHARACTER CODES

- USER DEFINABLECHARACTERS

.

128 ALPHANUMERIC CHARACTERS OR

GRAPHIC SYMBOLS IN INTERNAL ROM

(12x 18 DOTMATRIX)

.

UP TO 26 USERDEFINABLECHARACTERS

.

INTERNALHORIZONTALPLL(15TO 120kHz)

.

PROGRAMMABLE VERTICAL HEIGHT OF

CHARACTERWITHA SLICE INTERPOLATOR

TOMEETMULTI-SYNCHREQUIREMENTS

.

PROGRAMMABLE VERTICAL AND HORIZONTAL POSITIONING

.

FLEXIBLESCREENDESCRIPTION

.

CHARACTER BY CHARACTER COLOR SELECTION(UP TO 8 DIFFERENTCOLORS)

.

PROGRAMMABLE BACKGROUND (COLOR,

TRANSPARENT OR WITH SHADOWING)

.

50MHz MAXIMUMPIXEL CLOCK

.

2-WIRES ASYNCHRONOUS SERIAL MCU

INTERFACE (I

.

8 x 8 BITS PWMDAC OUTPUTS (STV9425)

4 x 8 BITS PWMDAC OUTPUTS (STV9425B)

.

SINGLEPOSITIVE5V SUPPLY

2

C PROTOCOL)

STV9425 - STV9425B

STV9426

8 x 8 bitsor 4 x 8 bits PWM DAC are available to

provideDC voltagecontrol toother peripherals.

TheSTV9425/25B/26providesthe useran easyto

useand cost effectivesolution to displayalphanumericor graphicinformation on monitor screen.

SHRINK24

(Plastic Package)

ORDER CODES :

STV9425 - STV9425B

DESCRIPTION

TheSTV9425/25B/26is anONSCREENDISPLAY

for monitor. It is built as a slave peripheral connected to a host MCU via a serial I

includesa displaymemory, controlsall the display

attributesand generatespixels fromthe data read

in its on chip memory. The line PLLand a special

slice interpolator allow to have a display aspect

which does not depend on the line and frame

frequencies. I

transparent internal access to prepare the next

pagesduring the displayof the current page.Togglefromonepage toanotherby programmingonly

one register.

December 1997

2

C interface allows MCU to make

2

C bus. It

DIP16

(Plastic Package)

ORDER CODE :

STV9426

1/15

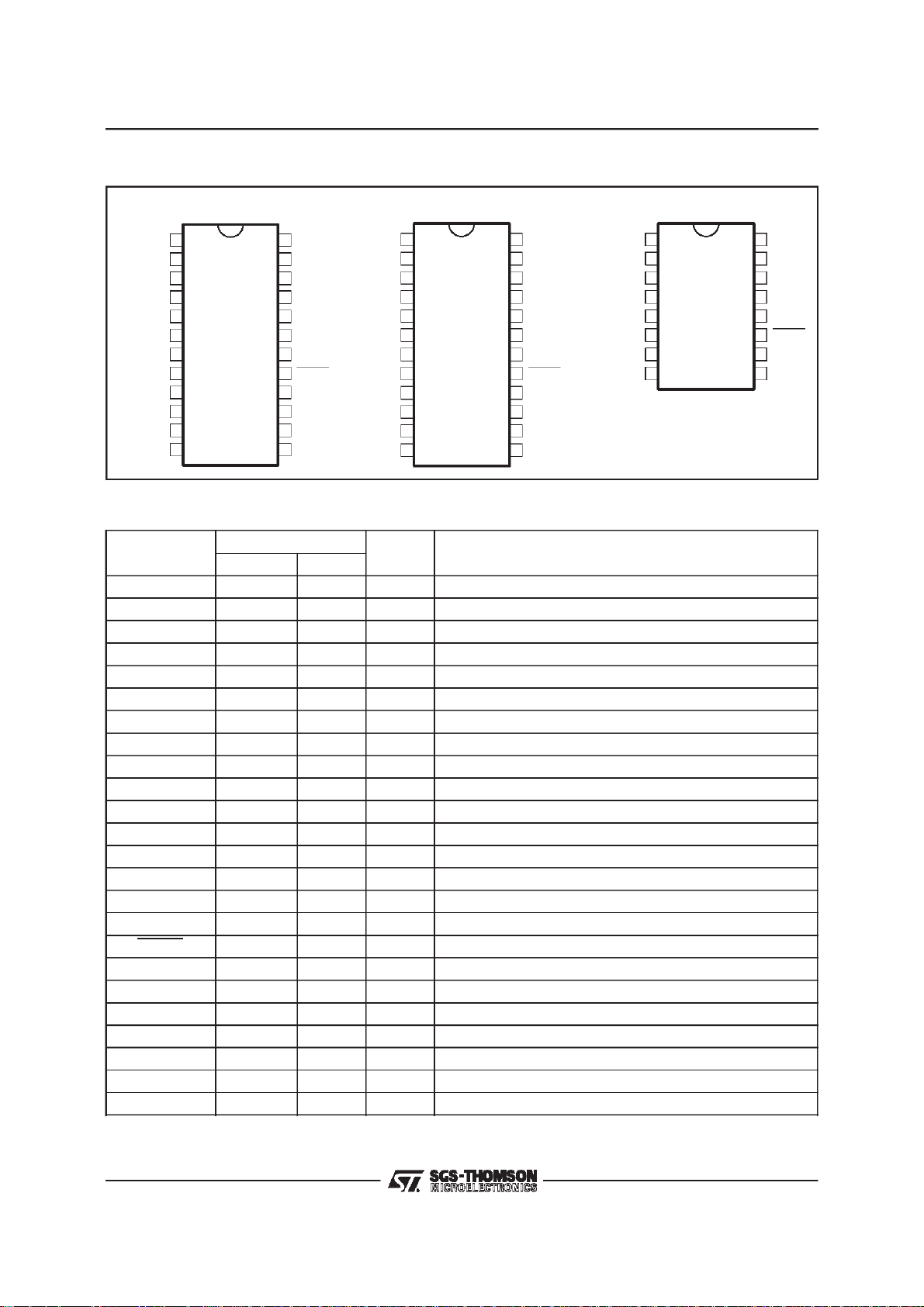

STV9425 - STV9425B - STV9426

PIN CONNECTIONS

PWM0

PWM1

FBLK

VSYNC

HSYNC

V

PXCK

CKOUT

XTAL OUT

XTAL IN

PWM2

SDIP24 (STV9425)

1

2

3

4

5

6

DD

7

8

9

10

11

12

RES E RVED

PWM7

24

PWM6

23

TEST

22

B

21

G

20

R

19

GND

18

RESET

17

SDA

16

SCL

15

PWM5

14

PWM4PWM3

13

XTALOUT

SDIP24 (STV9425B)

1

PWM1

FBLK

VSYNC

HSYNC

PXCK

CKOUT

XTALIN

PWM2

2

3

4

5

V

6

DD

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

RESERVED

PWM6

TEST

B

G

R

GND

RESET

SDA

SCL

PWM5

RESERVEDRES E RVED

V-SYNC

H-SYNC

CKOUT

XTAL OUT

XTAL IN

PIN DESCRIPTION

Symbol

PWM0 1 * - O DAC0 Output

PWM1 2 - O DAC1 Output

FBLK 3 1 O Fast Blanking Output

V-SYNC 4 2 I Vertical Sync Input

H-SYNC 5 3 I HorizontalSync Input

V

DD

PXCK 7 5 O Pixel FrequencyOutput

CKOUT 8 6 O Clock Output

XTAL OUT 9 7 O Crystal Output

XTAL IN 10 8 I Crystal or Clock Input

PWM2 11 - O DAC2 Output

PWM3 12 * - O DAC3 Output

PWM4 13 * - O DAC4 Output

PWM5 14 - O DAC5 Output

SCL 15 9 I Serial Clock

SDA 16 10 I/O Serial Input/Output Data

RESET 17 11 I Reset Input (Active Low)

GND 18 12 S Ground

R 19 13 O Red Output

G 20 14 O Green Output

B 21 15 O Blue Output

TEST 22 16 I Reserved (grounded in NormalOperation)

PWM6 23 - O DAC6 Output

PWM7 24 * - O DAC7 Output

* Reserved with STV9425B(not to be connected)

Pin Number

I/O Description

SDIP24 DIP16

6 4 S +5V Supply

DIP16 (STV9426)

FBLK

PXCK

1

2

3

V

4

DD

5

6

7

8

TEST

16

B

15

G

14

R

13

GND

12

RESET

11

SDA

10

SCL

9

9425-01.EPS /9425B-01.EPS/9426-01.EPS

9425-01.TBL

2/15

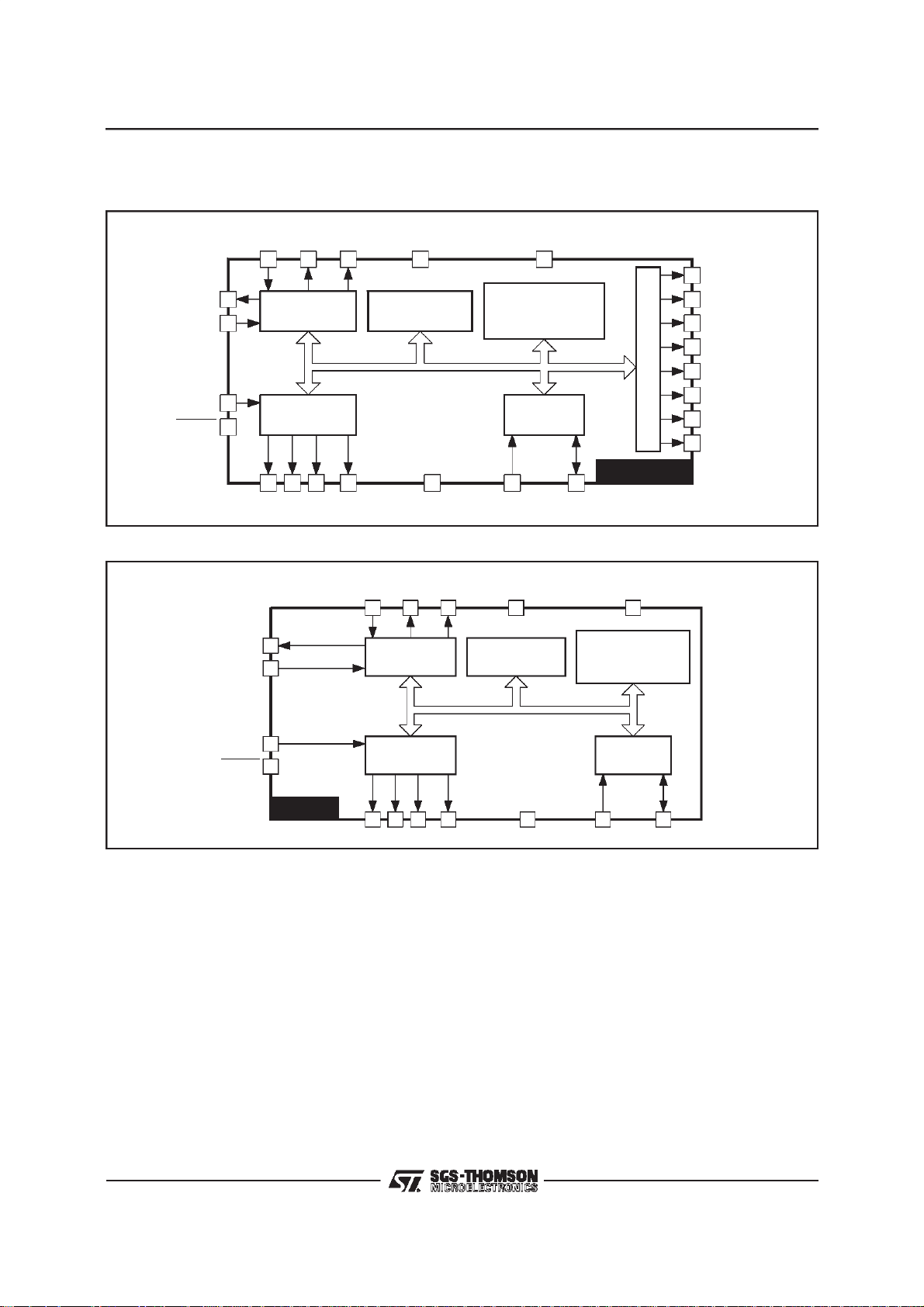

BLOCKDIAGRAMS

STV9425

STV9425 - STV9425B - STV9426

STV9426

CKOUT

HSYNC

VSYNC

RESET

XTALINXTAL

OUT PXCK TEST

V

DD

10 9 7 6 22

8

5

HORIZONTAL

DIGITAL PLL

4K ROM

(128 characters)

Address/Data

4

17

DISPLAY

CONTROLLER

19 20 21 3 18 15 16

R G B FBLK GND SCL SDA

XTALINXTAL

OUT PXCK TEST

78

CKOUT

HSYNC

6

3

HOR IZONTAL

DIGITALP LL

(128 characte rs)

1K RAM

Pa ge Descriptors +

User Defined Char.

2

I C BUS

INTERFACE

V

DD

45

4KRO M

PWM

STV9425/25B

*Reserved with STV9425B

16

1KRAM

Page Des criptors +

User Defined Char.

24

23

14

13

12

11

2

1

PWM7 *

PWM6

PWM5

PWM4 *

PWM3 *

PWM2

PWM1

PWM0 *

9425-02.EPS

VSYNC

RESET

2

11

STV9426

Addres s/Data

DISP LAY

CONTROLLER

1

R G B FBLK GND SCL

1213 14 15

INTERFACE

910

2

I C BUS

SDA

9426-02.EPS

3/15

STV9425 - STV9425B - STV9426

ABSOLUTEMAXIMUM RATINGS

Symbol Parameter Value Unit

V

DD

V

IN

T

oper

T

stg

ELECTRICAL CHARACTERISTICS

=5V,VSS=0V,TA= 0 to70°C, F

(V

DD

Symbol Parameter Min. Typ. Max. Unit

SUPPLY

V

DD

I

DD

INPUTS

SCL, SDA, TEST, RESET, V-SYNC and H-SYNC

V

IL

V

IH

I

IL

OUTPUTS

R, G,B, FBLK, SDA, CKOUT, PXCK and PWMi (i = 0 to 7)

V

OL

V

OH

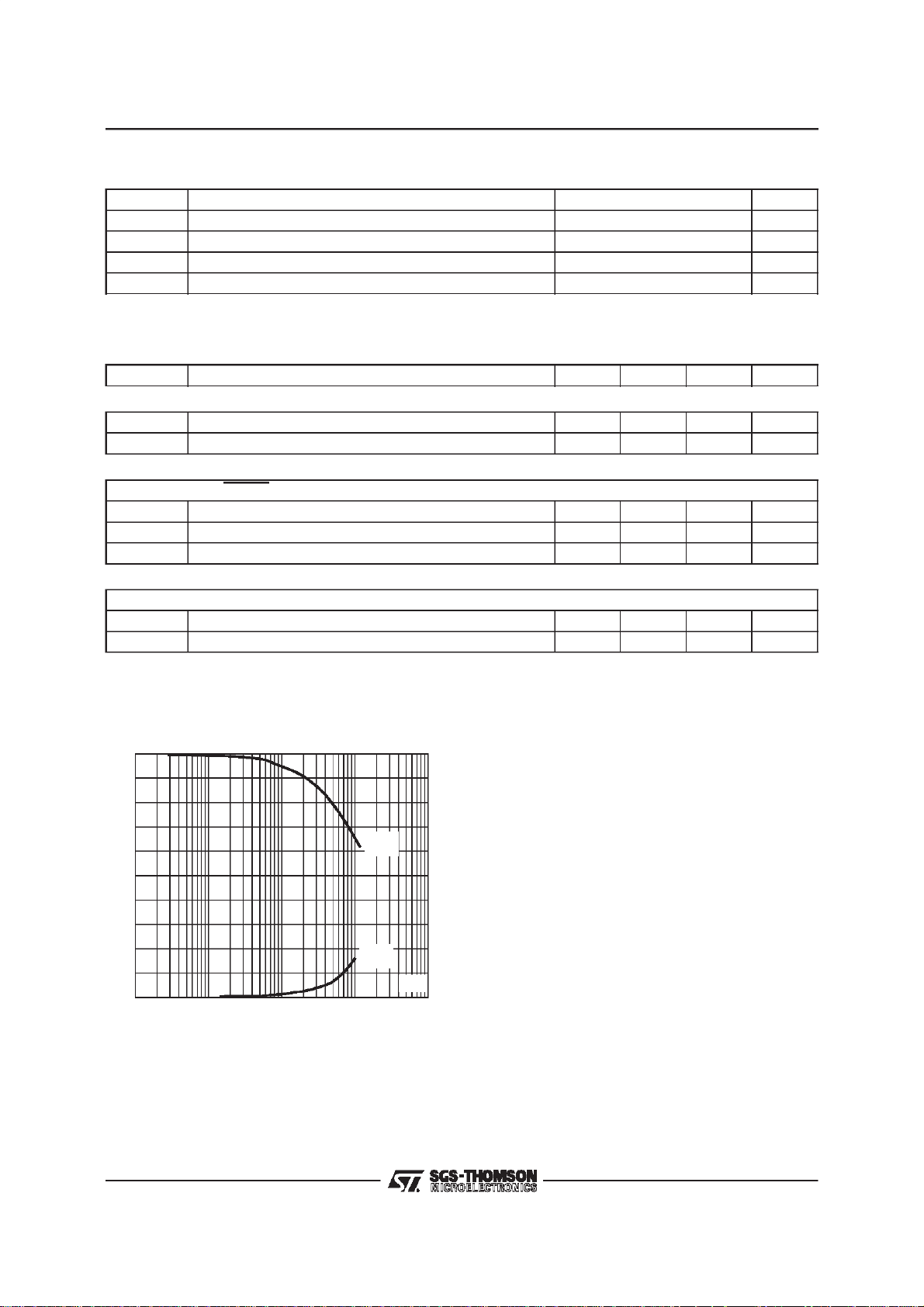

For R, G, B and FBLKoutputs, see Figure1.

Supply Voltage -0.3, +7.0 V

Input Voltage -0.3, +7.0 V

Operating AmbientTemperature 0, +70 °C

Storage Temperature -40, +125 °C

= 8 to15MHz, TEST= 0 V,unlessotherwise specified)

XTAL

Supply Voltage 4.75 5 5.25 V

Supply Current - 50 70 mA

Input Low Voltage 0.8 V

Input High Voltage 0.8V

DD

Input Leakage Current -20 +20

Output Low Voltage (IOL= 1.6mA) 0 0.4 V

Output High Voltage (IOL= -0.1mA) 0.8V

DD

V

DD

9425-02.TBL

V

A

µ

V

9425-03.TBL

Figure1 : TypicalR, G, B OutputsCharacteristics

V

(V)

,

V

OH

V

OL

I (A)

10

-4

10

-3

10

-2

10

-1

5

2.5

0

10

V

-5

OL OH

9425-17.EPS

4/15

STV9425 - STV9425B - STV9426

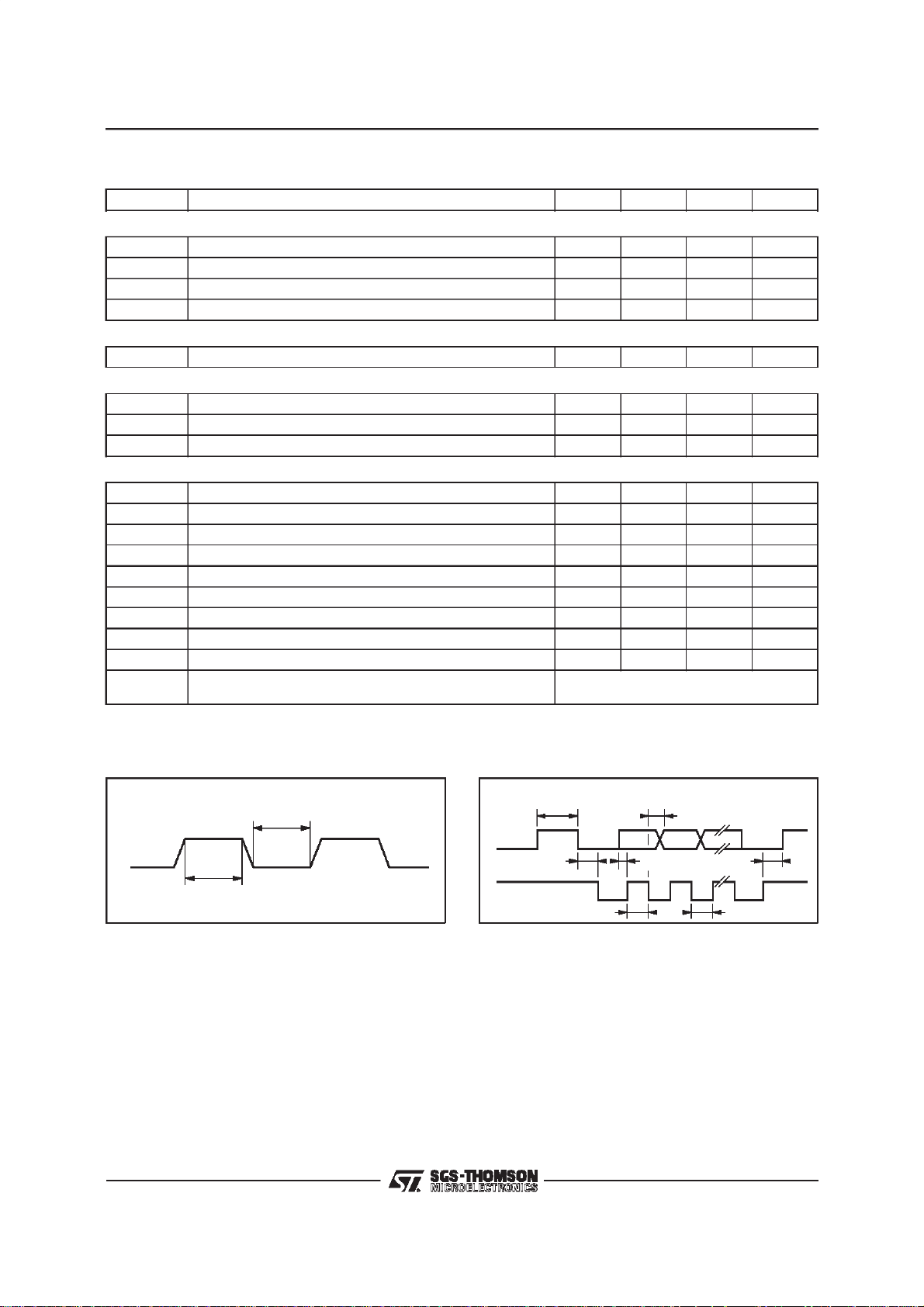

TIMINGS

Symbol Parameter Min. Typ. Max. Unit

OSCILATOR INPUT :XTI (see Figure 2)

T

WH

T

WL

F

XTAL

F

PXL

RESET

T

RES

R, G, B, FBLK (C

T

RISE

T

FALL

T

SKEW

I2C INTERFACE : SDA ANDSCL (see Figure 3)

F

SCL

T

BUF

T

HDS

T

SUP

T

LOW

T

HIGH

T

HDAT

T

SUDAT

T

F

T

R

Note 1 : These parameters are not tested on each unit. They are measured during our internal qualification procedure which includes

Clock High Level 20 ns

Clock Low Level 20 ns

Clock Frequency TBD 15 MHz

Pixel Frequency 50 MHz

Reset Low LevelPulse 4 µs

= 30pF)

LOAD

Rise Time (Note1) 5 ns

Fall Time (Note 1) 5 ns

Skew between R, G, B, FBLK (Note 1) 5 ns

SCL Clock Frequency 0 1 MHz

Time thebus must be free between 2 access 500 ns

Hold Timefor Start Condition 500 ns

Set upTime for StopCondition 500 ns

The Low Period of Clock 400 ns

The HighPeriod of Clock 400 ns

Hold TimeData 0 ns

Set upTime Data 375 ns

Fall Time of SDA 20 ns

Rise Time ofBoth SCL and SDA

characterization on batches comming from corners of our processes and also temperature characterization.

Depend onthe pull-up resistor

and the load capacitance

9425-04.TBL

Figure2

XTI

TWH

TWL

Figure3

9425-03.AI

STOP START DATA STOP

T

SDA

SCL

BUF

T

HDS

T

HIGH

T

SUDAT

T

HDAT

T

SUP

T

LOW

9425-04.AI

5/15