SGS Thomson Microelectronics STV1601A Datasheet

STV1601A

SERIALINTERFACE TRANSMISSION ENCODER

THISICCONTAINSALLTHECIRCUITSNEEDED

FOR CONVERSION FROM PARALLEL DATA,

ANDPARALLELCLOCK, INTO SERIALDATA.

APPLICATIONS ARE STRAIGHTFORWARD AS

ONLY A FEW EXTERNAL COMPONENTS ARE

NEEDED.

OTHERRELATEDIC’s INCLUDE:

.

STV1602A, A SERIAL TRANSMISSION DECODER (WITH A BUILT-IN CABLE EQUALIZER AND PARALLEL-TO-SERIAL

CONVERSION)

.

STV1389AQCOAXIALCABLE DRIVER

STRUCTURE

.

Hybrid IC

APPLICATIONS

SERIALDATA TRANSMISSION ENCODER

.

100 to 270Mb/s

APPLICATIONSEXAMPLES

.

Serial data transmission of digital television

signal525-625 lines

.

4:2:2 component 270Mb/s(10-BIT)

.

4*FSCPALcomposite 177Mb/s (10-BIT)

.

4*FSCNTSC composite 143Mb/s (10-BIT)

CODELIMITATION

The word composing the Sync word listed above

shallnot appearduring data words.

This limitationincludes 00 and FF in 8-bit use and

000 through 003 and 3FC through 3FF in 10-bit

use.

DESCRIPTION

TheSTV1601AisaHybridICencoderthatconverts

parallel data into serial data for a serial transmissionline.

PGA37

(Ceramic Package)

ORDER CODE : STV1601A

PIN CONNECTIONS

EE

V

VEED0Y

D0X

D1Y

D1X

D2Y

D2X

D3Y

FUNCTIONS

.

Parallel-to-serial conversion

.

Scrambler: Modulo - 2 division by

G(x) = (x

.

PLL for serial clockgeneration

.

PLLlock detection

.

Sync word required with the parallel data

stream

1st word FFH 3FFH

2nd word 00H 000H

3rd word 00H 000H

Syncwordconversion(8-bittiming referencesignal

isinternally converted to 10-bit).

November 1992

9+x4

+1)(x+1)

8 bit 10 bit

RSE

V

CC

PCX

PCY

GND

FV

TRP

TN1

27 26 25 24 23 22 21 20 19

28

29

30

31

32

33

34

35

36

37

123456789

SX

GND

SY

GND

D9X

D9Y

LST

D8X

18

17

16

15

14

13

12

11

10

D8Y

D3X

D4Y

D4X

D5Y

D5X

D6Y

D6X

D7Y

D7XNCPCK

1601A-01.EPS

1/17

STV1601A

PIN DESCRIPTION

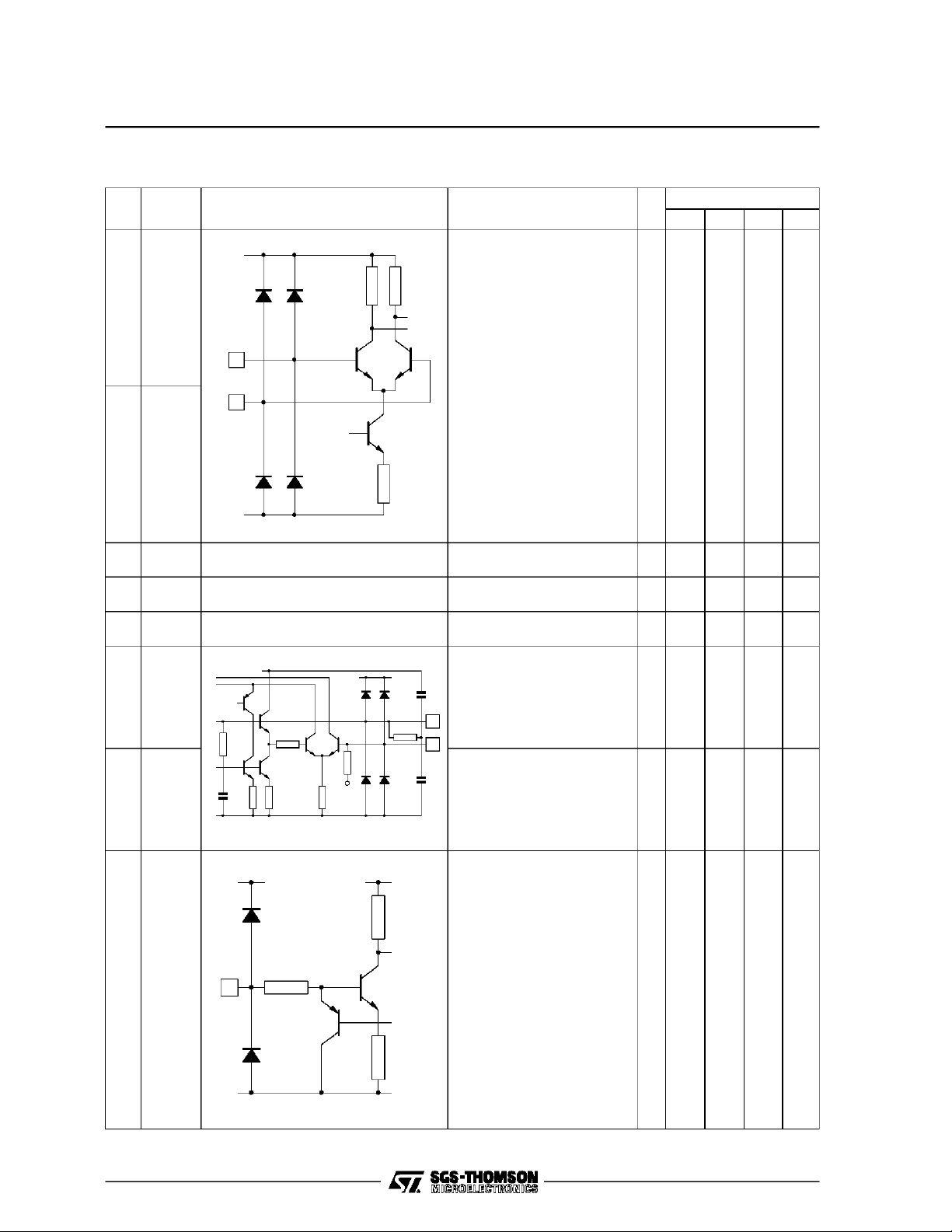

Pin

Symbol Equivalent circuit Description I/O

N

Standard

Min. Typ. Max. Unit

1 LST

36 PCK

GND

2kΩ

V

EE

GND

600Ω 600Ω

4kΩ

2kΩ

36

V

CC

PLL lock detection. Is High

while PLL locked. If

unlocked,becomes irregular.

At free running (TN1 H)

1

turnsLow

H

L

1601A-02.EPS

Clock output frequency

divided to 1/10 VCO output.

Used to check VCO free

running frequency

H

L

O

-1.0

-4.0VV

O

-0.8

-1.6

V

V

3SX

4SY

2/17

GND

240Ω

V

EE

V

CC

30Ω

100Ω 100Ω

30Ω

1601A-03.EPS

V

CC

Differential Serial Output

Inputparallel data is

34

converted to serial, then

O

from scrambled NRZ to

NRZI data

V

R3

2kΩ 2kΩ115Ω

V

EE

1601A-04.EPS

H

L

-1.6

-2.4

V

V

1601A-01.TBL

PIN DESCRIPTION(continued)

Pin

Symbol Equivalent circuit Description I/O

N

Parallel data and clock input

buffers power supply. When

this pin is connectedto +5V,

29 V

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

CC

D9X

D9Y

D8X

D8Y

D7X

D7Y

D6X

D6Y

D5X

D5Y

D4X

D4Y

D3X

D3Y

D2X

D2Y

D1X

D1Y

D0X

D0Y

29

6

7

V

R3

2kΩ

V

EE

parallel data clockturns to

TTL mode. When this pin is

connected to GND, parallel

data clock turns to ECL

1kΩ

mode.

Parallel input ports:

LSB : D0X or Y

MSB: D9Xor Y

Signal :DnX

Return : DnY

For ECL mode, V

0V

H

L

ForTTL mode, VCC shall be

+5V

H

L

1601A-05.EPS

CC

shalll be

STV1601A

Standard

Min. Typ. Max. Unit

-

-1.0

-1.6

2.0

0.8

V

V

V

V

28 RSE

2kΩ

10kΩ 10kΩ

70kΩ

GND

28

V

EE

VCO range selection

H : highrange 140 to 270MHz

L : low range 100 to 145MHz

H

L

1601A-06.EPS

I

-0.4

-4.0VV

1601A-02.TBL

3/17

STV1601A

PIN DESCRIPTION(continued)

Pin

Symbol Equivalent circuit Description I/O

N

V

CC

2kΩ 2kΩ

30 PCX

Standard

Min. Typ. Max. Unit

30

31

V

R3

31 PCY

V

EE

2, 5,

GND GND

32

26 V

27 V

EE

EE

GND

V

CC

33 FV

1kΩ

1kΩ

V

Ω

1k

1kΩ10k

9

Ω

34 TRP

1kΩ

2µF

V

EE

2kΩ

0.022µF

220Ω

0.1µF

Parallel clock (PCX) and its

return (PCY)

For ECL mode, V

H

CC

L

For TTLmode, V

CC

H

L

1601A-07.EPS

-5V power supply

I/O bufferPLL

-5V power supply

Logic part

VCO free runningfrequency

adjustment :

level gives the lowest

V

EE

frequency. Toadjust, set

34

TN1 high.

33

VCO input and phase

comparator outputshould be

connected to a parallel clock

frequency trapfilter to

minimize jitter

1601A-08.EPS

=0

= +5V

I

-1.0

2.0

-5.2 -5.0 -4.8 V

-5.2 -5.0 -4.8 V

I

-3.9 V

O

-3.2 V

-1.6

0.8

V

V

V

V

35 TN1

4/17

V

CC

GND

12kΩ

Test mode :

20kΩ

1

V

4k

Ω

V

High : VCO free running

condition (input disabled)

Low :Normal mode (input

enabled)

R3

EE

1601A-09.EPS

I

-1.0

-4.5VV

1601A-03.TBL

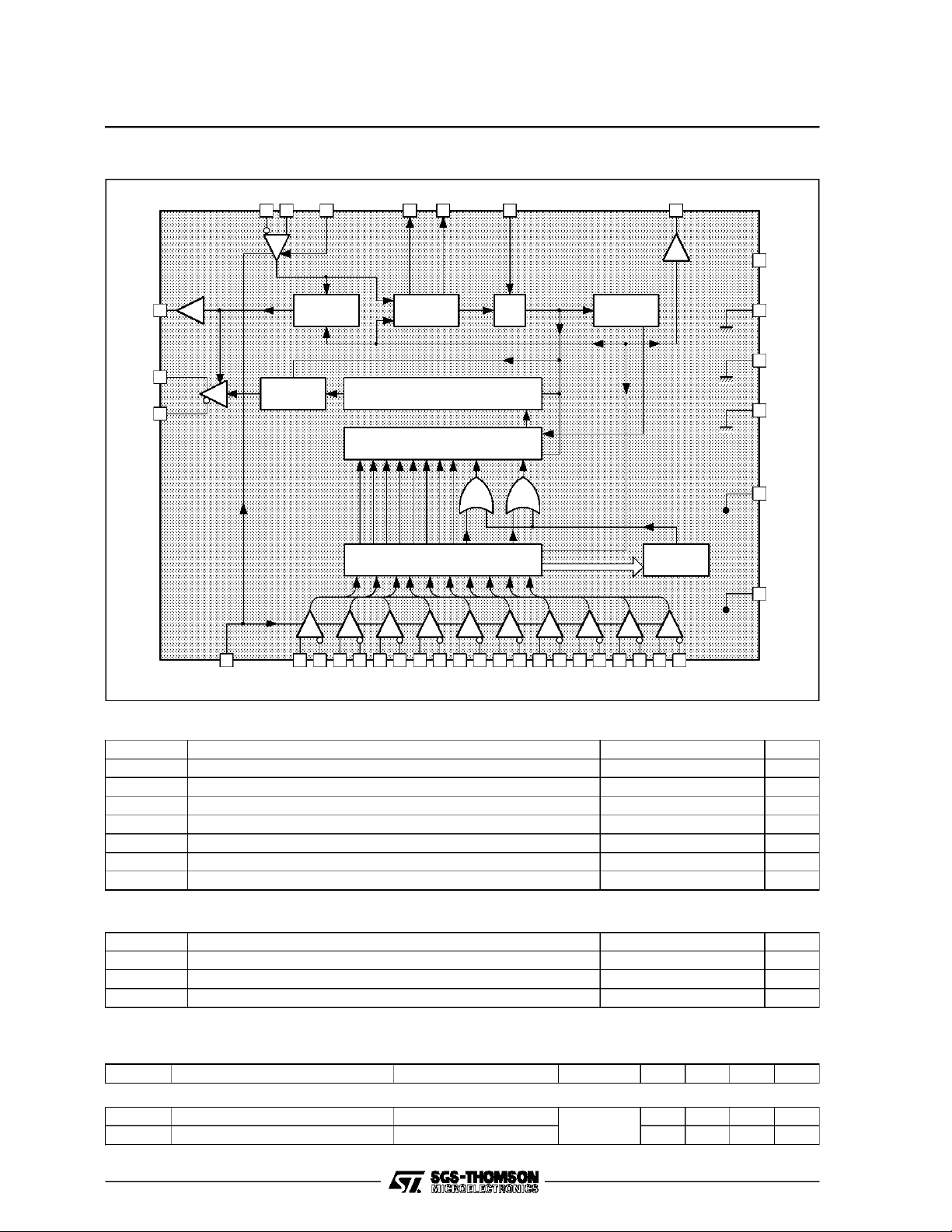

BLOCK DIAGRAM

STV1601A

PCY PCX TN1 FV TRP RSE PCK

353031 33 34 28 36

37 N.C.

LST

SX

SY

1

3

4

PLLLOCK

DETECTOR

NRZ ⊗

NRZI

PARALELL TO SERIAL CONVERTER

6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 2529

V

CC

D9X

D9Y

D8X

PHASE

DETECTOR

Parallel Clock

94

X +X + 1 SCRAMBLER

10-BITX3 WORD SHIFTREGISTER

D8Y

D7X

D7Y

D6X

D6Y

D5X

D5Y

VCO

D4X

D4Y

D3X

D3Y

Serial Clock

D2X

TIMING

GENERATOR

D2Y

D1X

Parallel Load

000hex

DETECTOR

D1Y

D0X

32

26

27

D0Y

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

I

T

V

V

V

OUT

oper

T

P

EE

CC

IN

stg

D

Supply Voltage -6 V

Supply Voltage +6 V

Input Voltage VEEto V

CC

Output Current -30 mA

Operating Temperature 0 to 65

Storage Temperature -50 to 125

Allowable Power Dissipation 2.0 W

2

GND

5

GND

GND

V

EE

V

EE

1601A-10.EPS

V

o

C

o

C

1601A-04.TBL

RECOMMENDED OPERATINGCONDITIONS

Symbol Parameter Value Unit

V

EE

V

CC

T

oper

* For TTL input. Voltages are given with respect toGND

Supply Voltage -4.8 to -5.2 V

Supply Voltage * 4.8 to 5.2 V

Operating Temperature 0 to 65

o

C

ELECTRICALCHARACTERISTICS (VEE=-5V, VCC= GND/+5V, TA=25oC unless otherwise speciied)

Symbol Parameter Test Conditions Test Circuit Min. Typ. Max. Unit

DC CHARACTERISTICS

I

I

Supply Current 1

EE

Supply Current 2 7 mA

CC

Figure 2

140 mA

5/17

1601A-05.TBL

1601A-06.TBL

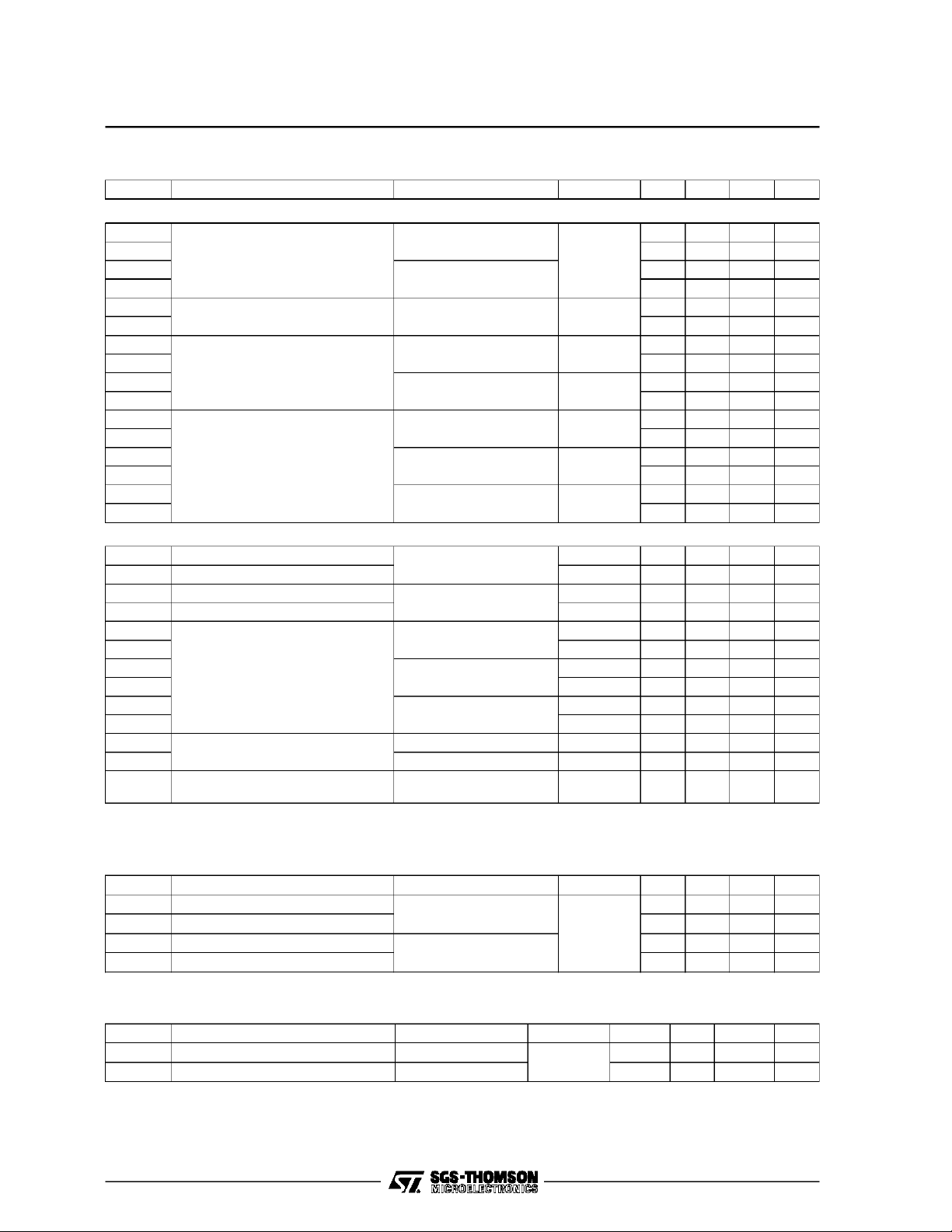

STV1601A

ELECTRICALCHARACTERISTICS (VEE=-5V, VCC= GND/+5V, TA=25oC unless otherwise speciied)

Symbol Parameter Test Conditions Test Circuit Min. Typ. Max. Unit

DC CHARACTERISTICS

V

IH

V

IL

V

V

V

V

V

V

V

V

V

V

V

V

Input Voltage

IH

IL

I

IH

Input Current PCX, PCY, DnX, DnY Figure3

I

IL

IH

IL

Input Voltage

IH

IL

OH

OL

OH

Output Voltage

OL

OH

OL

AC CHARACTERISTICS

f

MAX1

f

MIN1

f

MAX2

f

MIN2

f

f

f

f

f

f

f

OP1

f

OP2

VCO Max. Oscillation Frequency 1

VCO Min. Oscillation Frequency 1 14.0 MHz

VCO Max. Oscillation Frequency 2

VCO Min. Oscillation Frequency 2 10.0 MHz

HP1

LP1

HP2

PLL Pull in Range

LP2

HP3

LP3

PLL Generator Frequency

tjit Jitter

Tested through PCK : 1/10 of serial clock.

= GND

V

CC

PCX, PCY, DnX, DnY

VCC= +5V

PCX, PCY, DnX, DnY

RSE Figure 7

TN1 Figure 6

PCK

=1kΩ

R

P

LST

= -10µA, IOL= +10µA

I

OH

Figure 5

SX, SY

= 220Ω

R

P

RSE = ”H”

Figure 4 30.0 MHz

RSE = ”L”

f signal = 270MHz

Figure 1 27.7 MHz

RSE = ”H”

f signal = 177MHz

RSE = ”H”

f signal = 143MHz

RSE = ”H”

RSE = ”H” 14.0 27.0 MHz

RSE = ”L” 10.0 14.5 MHz

f signal = 270MHz

RSE = ”H”

Figure 8 ±0.25 nsec

-1.0 V

-1.6 V

2.0 V

0.8 V

5 µA

-1 +1 µA

-0.4 V

-4.0 V

-1 V

-4.5 V

-0.8 V

-1.6 V

-1.0 V

-4.0 V

-1.6 V

-2.4 V

15.0 MHz

25.5 MHz

18.8 MHz

16.5 MHz

15.0 MHz

13.0 MHz

1601A-07.TBL

SWITCHINGCHARACTERISTICS (VEE= -5V, VCC=GND/+5V, TA=25oC unless otherwise speciied)

Symbol Parameter Test Conditions Test Circuit Min. Typ. Max. Unit

t

Rise Time

r

Fall Time 1.4 nsec

t

f

t

Rise Time

r

t

Fall Time 0.7 nsec

f

PCK

=1kΩ

R

P

SX, SY

= 220Ω

R

P

Figure 10

0.8 nsec

0.7 nsec

TIMING RELATIONOF INPUTCLOCK AND DATA

Symbol Parameter Test Conditions Test Circuit Min. Typ. Max. Unit

t

6/17

Pulse Width PCX, PCY

w

t

Delay Time PCX - Dn -5 +5 nsec

d

Figure11

-5 + tc/2 tc/2 +5 + tc/2 nsec

1601A-08.TBL

1601A-09.TBL

Loading...

Loading...