SGS Thomson Microelectronics STV0056A Datasheet

SATELLITE SOUNDAND VIDEO PROCESSOR

SOUND

.

TWO INDEPENDENT SOUND DEMODULATORS

.

PLL DEMODULATION WITH 5-10MHz FREQUENCYSYNTHESIS

.

PROGRAMMABLE FM DEMODULATOR

BANDWIDTH ACCOMODATING FM DEVIATIONSFROM ±30kHzTILL±400kHz

.

PROGRAMMABLE 50/75µs, J17 OR NO DEEMPHASIS

.

WEGENERPANDASYSTEM

.

TWO AUXILIARY AUDIO INPUTS AND OUTPUTS

.

GAIN CONTROLLED AND MUTEABLE

AUDIOOUTPUTS

.

HIGH IMPEDANCE MODE AUDIO OUTPUTS

FORTWIN TUNERAPPLICATIONS

VIDEO

.

COMPOSITE VIDEO 6-bit 0 to 12.7dB GAIN

CONTROL

.

COMPOSITE VIDEO SELECTABLE INVERTER

.

TWO SELECTABLE VIDEO DE-EMPHASIS

NETWORKS

.

6 x 3 VIDEOMATRIX

.

BLACK LEVEL ADJUSTABLE OUTPUT FOR

ON-BOARDVIDEOCRYPTDECODER

.

HIGH IMPEDANCE MODE VIDEO OUTPUTS

FORTWIN TUNERAPPLICATIONS

MISCELLANEOUS

.

22kHz TONE GENERATION FOR LNB CONTROL

.

I2C BUS CONTROL

CHIP ADDRESSES = 06

.

LOW POWER STAND-BY MODE WITH ACTIVEAUDIO AND VIDEO MATRIXES

DESCRIPTION

TheSTV0056ABICMOS integratedcircuitrealizes

all thenecessary signal processing from the tuner

to the Audio/Video input and output connectors

regardlessthe satellite system.

HEX

OR46

HEX

(Plastic Package)

ORDER CODE : STV0056A

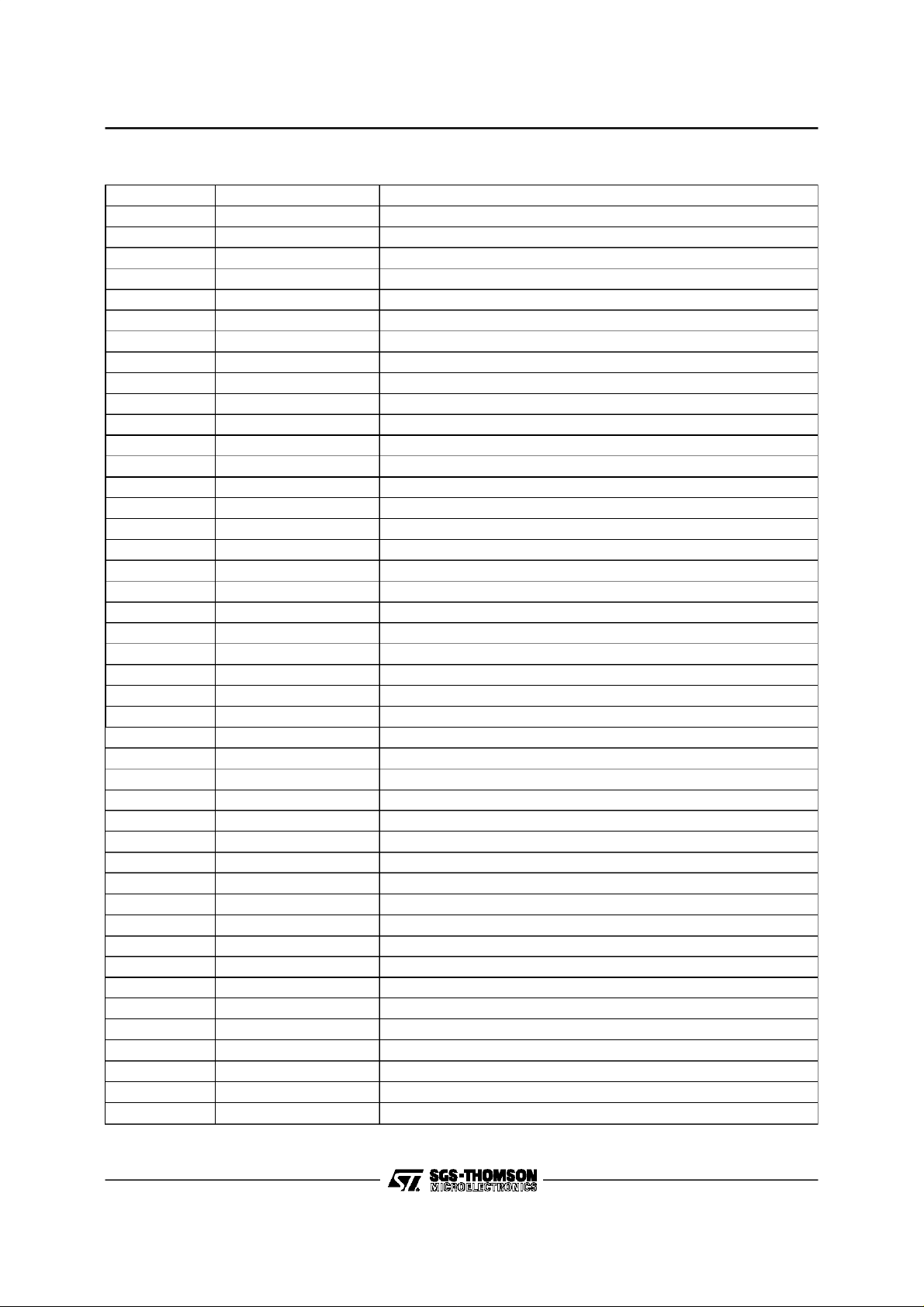

PIN CONNECTIONS

FC R

PK IN R

LEVEL R

S1 VID RTN

S3 VID RTN

VOL R

S3 VID OUT

S1 VID OUT

S2 VID OUT

VOL L

S2 VID RTN

S2 OUTL

CLAMP IN

S2 OUT R

UNCLDEEM

VIDEEM2/22kHz

V 12V

VIDEEM1

V GND

B-BAND IN

S2 RTN L

S2 RTN R

FM IN

S3 RTN L

S3 RTN R

AGC L

S3 OUTL

S3 OUT R

STV0056A

SHRINK56

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

ADVANCE DATA

A GND R

56

FC L

55

PK IN L

54

LEVEL L

53

PK OUT L

52

PK OUT R

51

I

50

REF

CPUMP R

49

48

U75 R

47

DET R

46

AMPLK R

45

A 12V

V

44

REF

43

A GND L

42

AGC R

41

AMPLK L

40

U75 L

DET L

39

CPUMP L

38

37

GND 5V

36

VDD5V

35

XTL

J17 L

34

33

J17 R

32

HA

31

SDA

30

SCL

I/O/22kHz

29

0056A-01.EPS

September 1996

This is advance informationon a new product now in development or undergoing evaluation. Detailsare subject to change without notice.

1/26

STV0056A

PIN ASSIGNMENT

Pin Number Name Function

1 FC R Audio Roll-off Right

2 PK IN R Noise Reduction Peak Detector Input Right

3 LEVEL R Noise Reduction Level Right

4 S1 VID RTN TV-Scart 1 Video Return

5 S3 VID RTN Decoder-Scart Video Return

6 VOL R Volume Controlled Audio Out Right

7 S3 VID OUT Decoder-Scart Video Output

8 S1 VID OUT TV-Scart 1 Video Output

9 S2 VID OUT VCR-Scart 2 Video Output

10 VOL L Volume Controlled Audio Out Left

11 S2 VID RTN VCR-Scart 2 VideoReturn

12 S2 OUT L Fixed Level Audio Output Left (to VCR)

13 CLAMP IN Sync-Tip ClampInput

14 S2 OUT R Fixed Level Audio Output Right (to VCR)

15 UNCL DEEM Unclamped Deemphasized Video Output

16 VIDEEM2/22kHz Video Deemphasis 2 or 22kHz Output

17 V 12V Video 12V Supply

18 VIDEEM1 Video Deemphasis 1

19 V GND Video Ground

20 B-BAND IN Base Band Input

21 S2 RTN L Auxiliary Audio ReturnLeft (from VCR)

22 S2 RTN R Auxiliary Audio Return Right (from VCR)

23 FM IN FM Demodulator Input

24 S3 RTN L Auxiliary Audio ReturnLeft (from decoder)

25 S3 RTN R Auxiliary Audio Return Right (from decoder)

26 AGC L AGC PeakDetector Capacitor Left

27 S3 OUT L Auxiliary Audio Output L (to decoder)

28 S3 OUT R Auxiliary Audio Output R (to decoder)

29 I/O/22kHz Digital Input/Output or 22kHz Output

30 SCL I

31 SDA I

32 HA Hardware Address

33 J17 R J17 Deemphasis Time Constant Right

34 J17 L J17 Deemphasis Time Constant Left

35 XTL 4/8MHz Quartz Crystal or Clock Input

36 V

5V Digital 5V Power Supply

DD

37 GND 5V Digital Power Ground

38 CPUMP L FM PLL Charge Pump Capacitor Left

39 DET L FM PLL Filter Left

40 U75 L Deemphasis Time Constant Left

41 AMPLK L Amplitude Detector CapacitorLeft

42 AGC R AGC Peak Detector Capacitor Right

43 A GND L Audio Ground

44 V

REF

2

C Bus Clock

2

C Bus Data

2.4V Reference

0056A-01.TBL

2/26

PIN ASSIGNMENT (continued)

Pin Number Name Function

45 A 12V Audio 12V Supply

46 AMPLK R Amplitude Detector Capacitor Left

47 DET R FM PLL Filter Right

48 U75 R Deemphasis Time Constant Right

49 CPUMP R FM PLL Charge Pump Capacitor Right

50 I

51 PK OUT R Noise Reduction Peak Detector Output Right

52 PK OUT L Noise Reduction Peak Detector Output Left

53 LEVEL L Noise ReductionLevel Left

54 PK IN L Noise Reduction Peak Detector Input

55 FC L Audio Roll-off Left

56 A GND R Audio Ground

REF

Current Reference Resistor

PIN DESCRIPTION

SOUND DETECTION

FMIN

This is the input to the two FM demodulators. It

feeds two AGC amplifiers with a bandwidth of at

least 5-10MHz. There is one amplifier for each

channelboth withthe same input. The AGCamplifiers havea 0dB to +40dBrange.

=5kΩ, Mininput = 2mVPPpersubcarrier.

Z

IN

Max input = 500mV

(max when all inputs are

PP

added together,when their phasescoincide).

AGC L, AGC R

AGC amplifiers peak detector capacitor connections. Theoutput current has an attack/decay ratio

of 1:32. That is the ramp up current is approximately 5µA and decay current is approximately

160µA. 11Vgives maximum gain. These pins are

also driven by a circuit monitoring the voltage on

AMPLK Land AMPLK R respectively.

AMPLKL, AMPLK R

The outputs of amplitude detectors LEFT and

RIGHT. Each requiresa capacitorand a resistorto

GND. The voltage across this is used to decide

whether thereis a signalbeing received by the FM

detector. The level detector output drives a bit in

the detectorI

2

C bus control block.

AMPLK L and AMPLK R drive also respectively

AGC Land AGC R. For instancewhen thevoltage

on AMPLKL is > (V

frompin AGCLto reducethe AGC gain.

V

REF

+1VBE) it sinkscurrent to

REF

DET L, DETR

Respectivelythe outputsofthe FMphasedetector

left and right.

This is for the connectionof an external loop filter

for the PLL. The output is a push-pull current

source.

CPUMP L, CPUMPR

The output from the frequency synthesizer is a

push-pullcurrentsourcewhichrequiresacapacitor

to groundto derive a voltagetopull the VCO to the

target frequency.The output is ±100µAto achieve

lockand±2µAduringlocktoprovidea trackingtime

constantof approximately10Hz.

V

REF

This is the audio processorvoltagereferenceused

through out the FM/audio section of the chip. As

such it is essential that it is well decoupled to

ground to reduce as far as possible the risk of

crosstalk and noise injection. This voltage is deriveddirectly from the bandgap reference of 2.4V.

The V

output can sink up to 500µA in normal

REF

operationand 100µAwhen in stand-by.

I

REF

Thisisa bufferedV

to produce an accurate current reference, within

the chip, for the biasing of amplifiers with current

outputs into filters.It is alsorequired for the Noise

reduction circuit to provide accurate roll-off frequencies. This pin should not be decoupledas it

would inject current noise. The target current is

50µA±2% thusa 47.5kΩ ±1% is required.

STV0056A

outputto an off-chipresistor

REF

0056A-01.TBL

3/26

STV0056A

PIN DESCRIPTION (continued)

A 12V

Double bonded main power pin for the audio/FM

section of the chip.The twobond connectionsare

to the ESD and to power the circuit and on chip

regulators/references.

A GND L

This ground pin is double bonded :

1) to channelLEFT : RF section& VCO,

2) to both AGC amplifiers, channel LEFT and

RIGHTaudio filter section.

A GND R

This ground pin is double bonded :

1) to the volume control, noise reduction system,

ESD + Mux + V

2) to channelright : RF section & VCO

BASEBANDAUDIO PROCESSING

PK OUT L, PK OUT R, PKOUT

The noise reduction control loop peak detector

output requires a capacitorto groundfrom this pin,

and a resistor to V

decaytimeconstant.Anonchip5kΩ ±25%resistor

and externalcapacitor give the attack time.

PK IN L, PK IN R or PK IN

Each ofthesepinsis an inputto acontrollooppeak

detector and is connected to the output of the

offchipcontrol loop bandpass filter.

LEVEL L, LEVELR

Respectivelythe audio left and right signalsof the

FM demodulatorsare output to levelL and level R

pins through an input follower buffer. The off-chip

filters driven by these pins must include AC coupling to the next stage (PK IN L and PKIN R pins

respectively).

FC L, FC R

The variable bandwidth transconductance amplifier hasa current output which is variable depending on the input signal amplitude asdefined bythe

control loop of the noise reduction. The output

current is then dumped into an off-chip capacitor

which togetherwith the accuratecurrentreference

define the min/max rolloff frequencies.Aresistorin

REF

pin to give some accurate

REF

serieswith acapacitoris connectedto groundfrom

these two pins.

J17 L, J17R

The externalJ17 de-emphasisnetworks for channels left and right. The amplifier for this filter is

voltageinput, current output. Output with±500mV

input willbe ±55µA.

To performJ17de-emphasiswiththe STV0042,an

externalcircuit is required.

U75 L, U75 R

External deemphasis networks for channels left

andright.Foreachchannelacapacitorand resistor

in parallel of 75µs time constant are connected

betweenhereandV

toprovide75µs de-empha-

REF

sis. Internallyselectable is an internalresistorthat

canbeprogrammedtobeadded inparallelthereby

convertingthe networkto approx 50µs de-emphasis (see control block map). The valueof the internal resistors is 54kΩ ±30 %. The amplifier for this

filter isvoltageinput, currentoutput ; with±500mV

input the output will be ±55µA.

VOL L, VOL R

The main audio output from the volume control

amplifierthe signal to get output signalsas highas

2V

(+12dB) on a DC bias of 4.8V. Control is

RMS

from +12dB to -26.75dB plus Mute with 1.25dB

steps.Thisamplifierhasshortcircuitprotectionand

is intendedto drivea SCARTconnectordirectlyvia

AC coupling and meets the standardSCARTdrive

requirements. These outputs feature high impedance modefor parallelconnection.

S2 OUT L, S2OUTR, S3 OUT L, S3 OUT R

These audio outputs are sourced directly from the

audio MUX, and as a result do not include any

volume controlfunction. They will output a 1V

RMS

signal biased at 4.8V. They are short circuit protected. These outputs feature high impedance

mode for parallel connection and meet SCART

driverequirement.

S2 RTNL, S2 RTN R, S3RTN L, S3 RTN R

These pins allow auxiliary audio signals to be connected to the audio processor and hence makes

use of the on-chip volume control. For additional

detailsplease referto theaudio switching table.

4/26

PIN DESCRIPTION (continued)

VIDEO PROCESSING

B-BAND IN

AC-coupledvideo input from a tuner.

Z

> 10kΩ ±25%. This drives an on-chip video

IN

amplifier. The other input of this amp is AC

grounded by being connected to an internal V

The video amplifier has selectable gain from 0dB

to 12.7dB in 63 steps and its output signal can be

selectednormal or inverted.

UNCL DEEM

Deemphasizedstill unclampedoutput. It isalso an

input of thevideo matrix.

VIDEEM1

Connected to an external de-emphasis network

(forinstance 625 linesPALde-emphasis).

VIDEEM2 / 22kHz

Connected to an external de-emphasis network

(forinstance525 lines NTSC orothervideode-emphasis). Alternativelya precise 22kHztonemaybe

output by I

2

C bus control.

CLAMP IN

This pin clamps the most negative extreme of the

input (the sync tips) to 2.7V

(orappropriatevolt-

DC

age). The video at the clamp input is only 1V

This clamped video which is de-emphasised, filtered andclamped (energy dispersal removed) is

normal, negative syncs, video. This signal drives

the VideoMatrix input called Normal Video.

It hasa weak (1.0µA ±15 %)stable current source

pullingthe inputtowards GND. Otherwisetheinput

impedanceis very high at DC to 1kHz Z

Video bandwidth through this is -1dB at 5.5MHz.

The CLAMPinput DC restore voltageis then used

as a means for getting the correct DC voltage on

the SCARToutputs.

S3 VIDRTN

This input can be driven for instance by the decoder.Thisinputhas aDC restoration clamp on its

input. The clampsink currentis 1µA±15% withthe

buffer Z

>1MΩ.

IN

S2 VIDRTN, S1 VIDRTN

Externalvideoinput1.0V

ACcoupled75Ω source

pp

impedance.This inputhas a DC restoration clamp

on its input. The clamp sink current is 1µA ±15%

with thebuffer Z

>1MΩ. Thissignalis an inputto

IN

the VideoMatrix.

S1 VID OUT, S2VID OUT

Video drivers for SCART 1 and SCART 2. An

external emitter follower buffer is required to drive

>2MΩ.

IN

REF

PP

a 150Ω load. The average DC voltageto be 1.5V

on the O/P. The signalis video2.0V

PP

with sync tip = 1.2V. These pins get signals from

the Video Matrix. The signal selected from the

Video Matrix for output on thispin is controlled by

a control register. This output also feature a high

.

impedancemode for parallelconnection.

S3 VID OUT

This outputcan drive for instancea decoder.Also

it is able to pass 10MHz ; Z

this pin will be 2V

. The black level of the ouput

PP

<75Ω. Video on

OUT

video signal can be adjustedthrough I

trol to easily interface with on-board Videocrypt

decoder. This output feature an high impedance

mode for parallelconnection.

V 12V

+ 12Vdoublebonded: ESD+guardrings andvideo

circuitpower.

V GND

Doubledbonded.CleanVIDIN GND. Strategically

placed video power ground connection to reduce

video currents gettinginto the rest of the circuit.

CONTROLBLOCK

GND 5V

.

The main power ground connection for the control

logic, registers, the I

2

C bus interface, synthesizer

& watchdogand XTLOSC.

V

5V

DD

Digital +5V power supply.

SCL

ThisistheI

2

C busclockline.Clock= DCto100kHz.

Requiresexternal pull up eg.10kΩ to 5V.

SDA

This is the I

2

C bus dataline.Requiresexternalpull

up eg. 10kΩ to 5V.

I/O / 22kHz

Generalpurpose input outputpin or 22kHz output.

XTL

This pinallowsforthe on-chiposcillator tobe either

used witha crystal to groundof 4MHzor 8MHz, or

to be driven by an external clock source. The

external source can be either 4MHz or 8MHz. A

programmablebitinthecontrolblockremovesa÷2

blockwhen the 4MHz optionis selected.

HA

Hardwareaddress with internal135µApull down.

Chip address is 06 when this pin is grouded and

chip address is 46 when connected to V

STV0056A

5.5MHzBW

2

C buscon-

.

DD

5/26

STV0056A

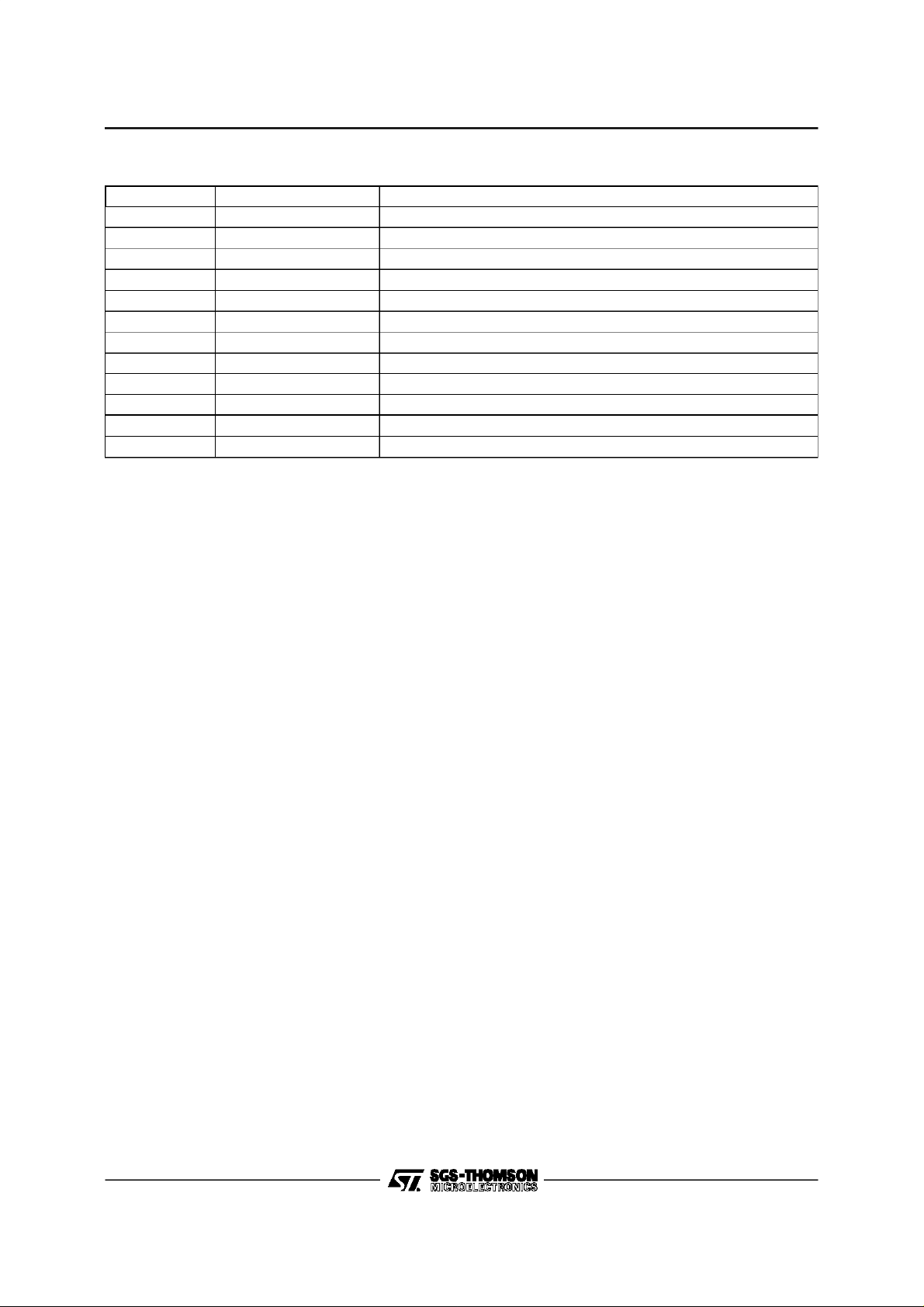

GENERALBLOCK DIAGRAM

From Tuner

Vide o

Proce ssing

From TV,

VCR/Decode r

FM

B-BAND

From Tuner

Demodulation

2 Cha nnels

Wegener

Panda +

Dee m phas is

22kHz to LNB

STV0056A

VIDEO PROCESSINGBLOCK DIAGRAM

LPF

2

6x3

Video

4

Matrix

3

2

To TV, VCR/De coder

Audio

Matrix

3

+

Volume

2

CBus

I

Interface

Active in Stand-by

0056A-02.EPS

6/26

I/O/22kHz

B-BAND IN

CLAMP IN

S3 VID RTN

S2 VID RTN

S1 VID RTN

29

20

CLAMP

13

CLAMP

5

CLAMP

11

CLAMP

4

STV0056A

NTSC

PAL

VIDEEM1VIDEEM2/22kHz

16 18 15

22kHz

TONE

± 1

G

Baseband

Normal

DecoderReturn

VCR Return

TV Return

BLACK LEVEL

ADJUST

To Decoder To VCR

UNCL DEEM

Deemphasized

2

89

7

S1 VID OUT

S2 VID OUTS3 VID OUT

To TV

0056A-03.EPS

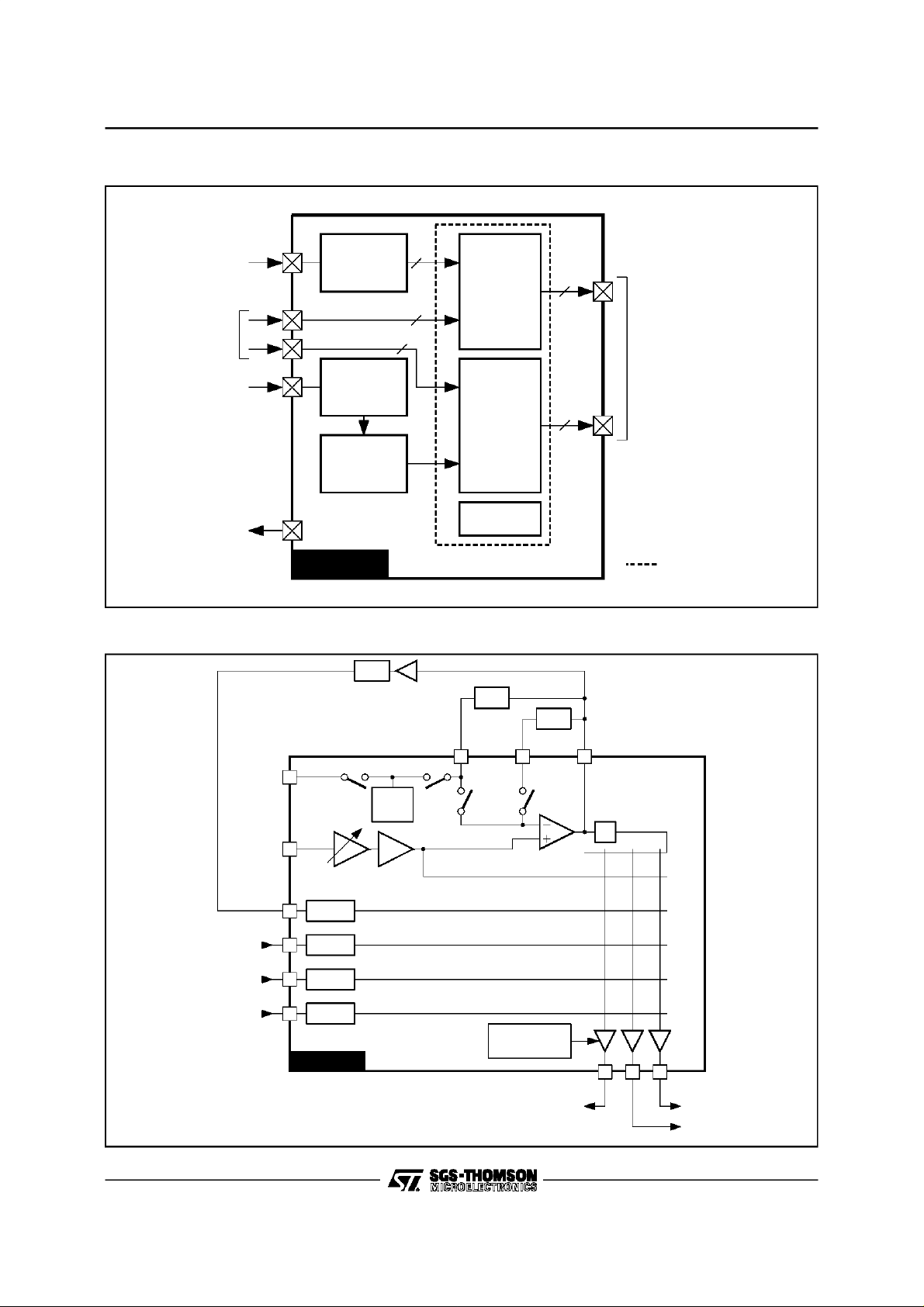

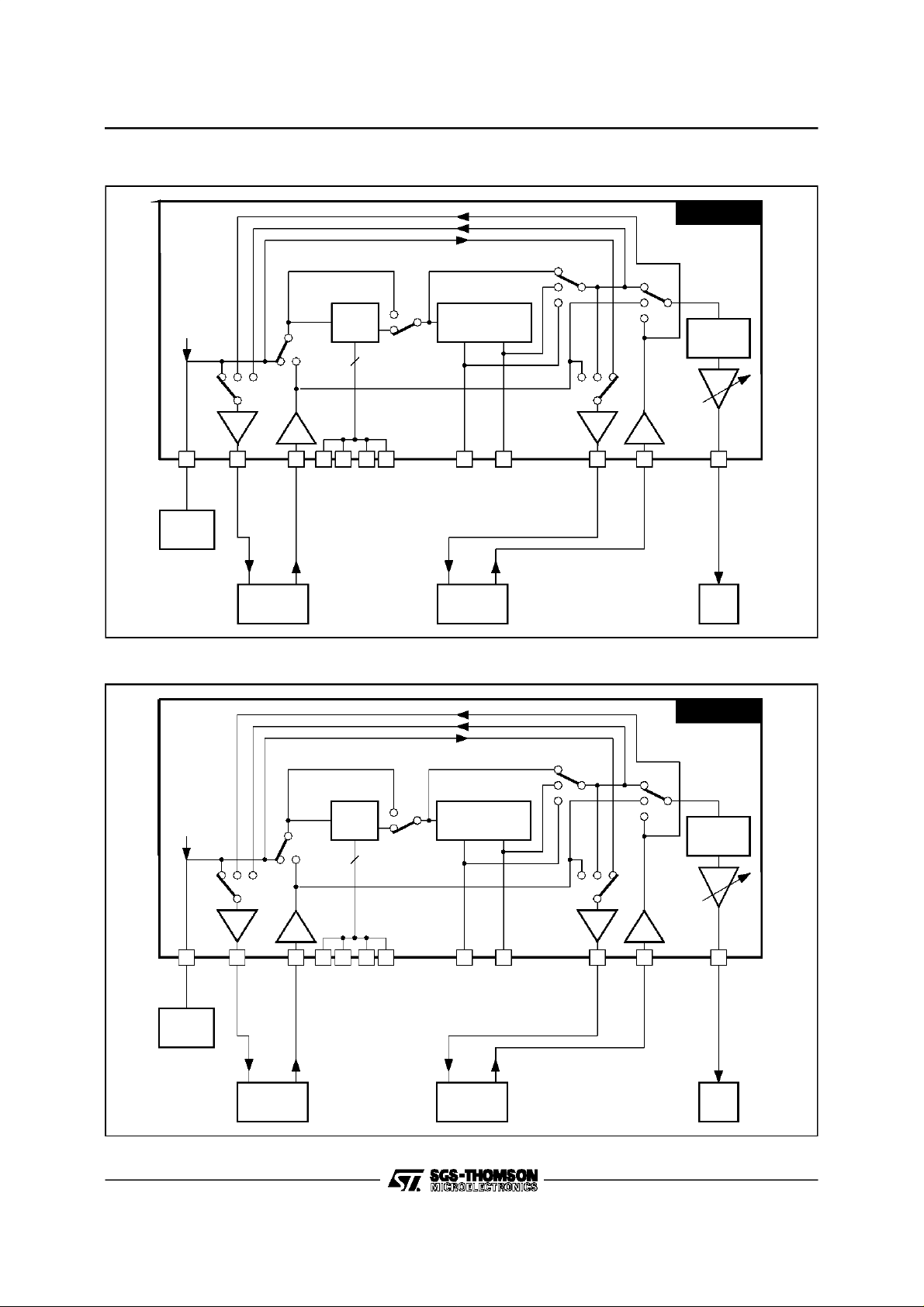

AUDIO PROCESSINGBLOCK DIAGRAM (CHANNELRIGHT)

AUDIO R

47

a

ANRS

K3

K4

abc

K6

28 25 51 2 3 1 14 22 6

b

a

-6dB -6dB

b

4

AUDIO

DEEMPHASIS

33 48

STV0056A

K2

a

ba

c

abc

6dB6dB

K1

b

c

K5

MONO

STEREO

STV0056A

DET R

PLL

FILTER

DecoderOut

FC R

PK IN R

S3 OUT R

Audio

DECODER VCR

S3 RTN R

Audio

DecoderReturn

LEVEL R

PK OUT R

J17 R

U75 R

AUDIO PROCESSING BLOCK DIAGRAM (CHANNEL LEFT)

AUDIO L

39

a

ANRS

K3

K4

abc

K6

27 24 52 54 53 55 12 21 10

b

a

-6dB -6dB

b

4

AUDIO

DEEMPHASIS

32 40

S2 OUT R

S2 RTN R

STV0056A

K2

a

ba

c

abc

6dB6dB

K1

b

c

K5

MONO

STEREO

VOL R

TV

0056A-04.EPS

DET L

PLL

FILTER

Audio

Decoder Out

FC L

PK IN L

S3 OUT L

DECODER VCR

S3 RTN L

Audio

Decoder Return

LEVEL L

PK OUT L

J17 L

U75 L

S2 OUT L

S2 RTN L

VOL L

TV

0056A-05.EPS

7/26

STV0056A

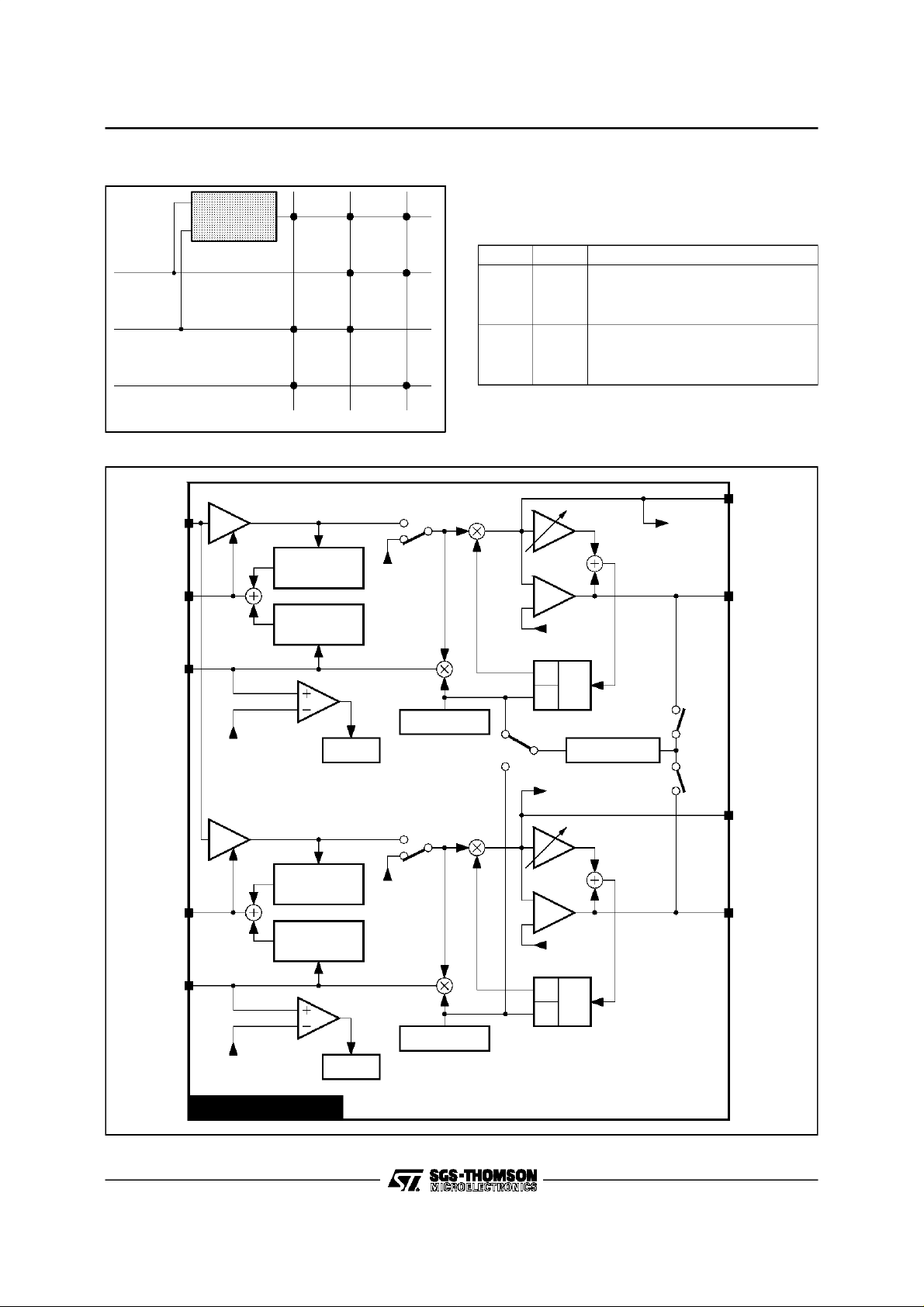

AUDIO SWITCHING

AUDIO

DEEMPHASIS

+ ANRS

AUDIOPLL

DECRTN

AUXIN K

K

1a

K

1b

1c 6b

VOL OUT AUX OUT

K

K

K

5b

5c

5a

FMDEMODULATION BLOCK DIAGRAM

FM IN

AGC R

AGC

LEVEL

DETECTOR1

LEVEL

DETECTOR2

Bias

K

6c

K

6a

K

DECOUT

SW1

K

4

0056A-06.EPS

Phase

Detect

:a→ANRSinput non-scrambledaudio

b → ANRS input descrambledaudio

K

a

b

b

c

a

b

b

c

K

2

1

2

1

2

3

a

No ANRS, No De-emphasis

a

No ANRS, 50µs

a

No ANRS, 75µs

a

No ANRS, J17

b

ANRS, No De-emphasis

b

ANRS, 50µs

b

ANRS, 75µs

b

ANRS, J17

DETR

AUDIOR

FM dev.

Select.

CPUMPR

V

REF

AMPLKR

AGC L

AMPLKL

V

AGC

V

REF

REF

Reg8 b4

LEVEL

DETECTOR1

LEVEL

DETECTOR2

Reg8 b0

Amp. Detect

WATCHDOG

SW3

Bias

Amp. Detect

WATCHDOG

Phase

Detect

90

VCO

0

SYNTHESIZER

AUDIOL

FM dev.

Select.

V

REF

90

VCO

0

SW2

SW4

DETL

CPUMPL

8/26

STV0042/STV0056A

0056A-07.EPS

Loading...

Loading...