SGS Thomson Microelectronics STW8NK80Z, STP8NK80ZFP, STP8NK80Z Datasheet

STP8NK80Z - STP8NK80ZFP

STW8NK80Z

N-CHANNEL 800V - 1.3Ω - 6.2A TO-220/TO-220FP/TO-247

Zener-Protected SuperMESH™Power MOSFET

TYPE V

STP8NK80Z

STP8NK80ZFP

STW8NK80Z

■ TYPICAL R

■ EXTREMELY HIGH dv/dt CAPABILITY

■ 100% AVALANCHE TESTED

■ GAT E CHARGE MINIMIZED

■ VERY LOW INTRINSIC CAPACITANCES

■ VER Y GO OD MANUFACTURING

800 V

800 V

800 V

(on) = 1.3 Ω

DS

DSS

R

DS(on)

< 1.5 Ω

< 1.5 Ω

< 1.5 Ω

I

D

6.2 A

6.2 A

6.2 A

Pw

140 W

30 W

140 W

REPEATIBILITY

DESCRIPTION

The SuperM ESH™ series is obtained through an

extreme optimization of S T’s well established stripbased PowerMESH™ layout. In addition to pushing

on-resistance significantly down, special careis taken to ensure a very good dv/dt capability for the

most demanding applications. Such series complements ST full range of high voltage MOSFETs including revolutionary MDm es h™ products.

3

2

TO-220

1

TO-220FP

3

2

1

TO-247

INTERNAL SCHEMATIC DIAGRAM

3

2

1

APPLICATIONS

■ HIGH CURRENT, HIGH SPEED SWITCHING

■ IDEAL FOR OFF-LINE POWER SUPPLIES,

ADAPTORS AND PFC

■ LI GHTING

ORDERING INFORMATION

SALES TYPE MARKING PACKAGE PACKAGING

STP8NK80Z P8NK80Z TO-220 TUBE

STP8NK80ZFP P8NK80ZFP TO-220FP TUBE

STW8NK80Z W8NK80Z TO-247 TUBE

1/11February 2003

STP8NK80Z - STP8NK80ZFP - STW8NK80Z

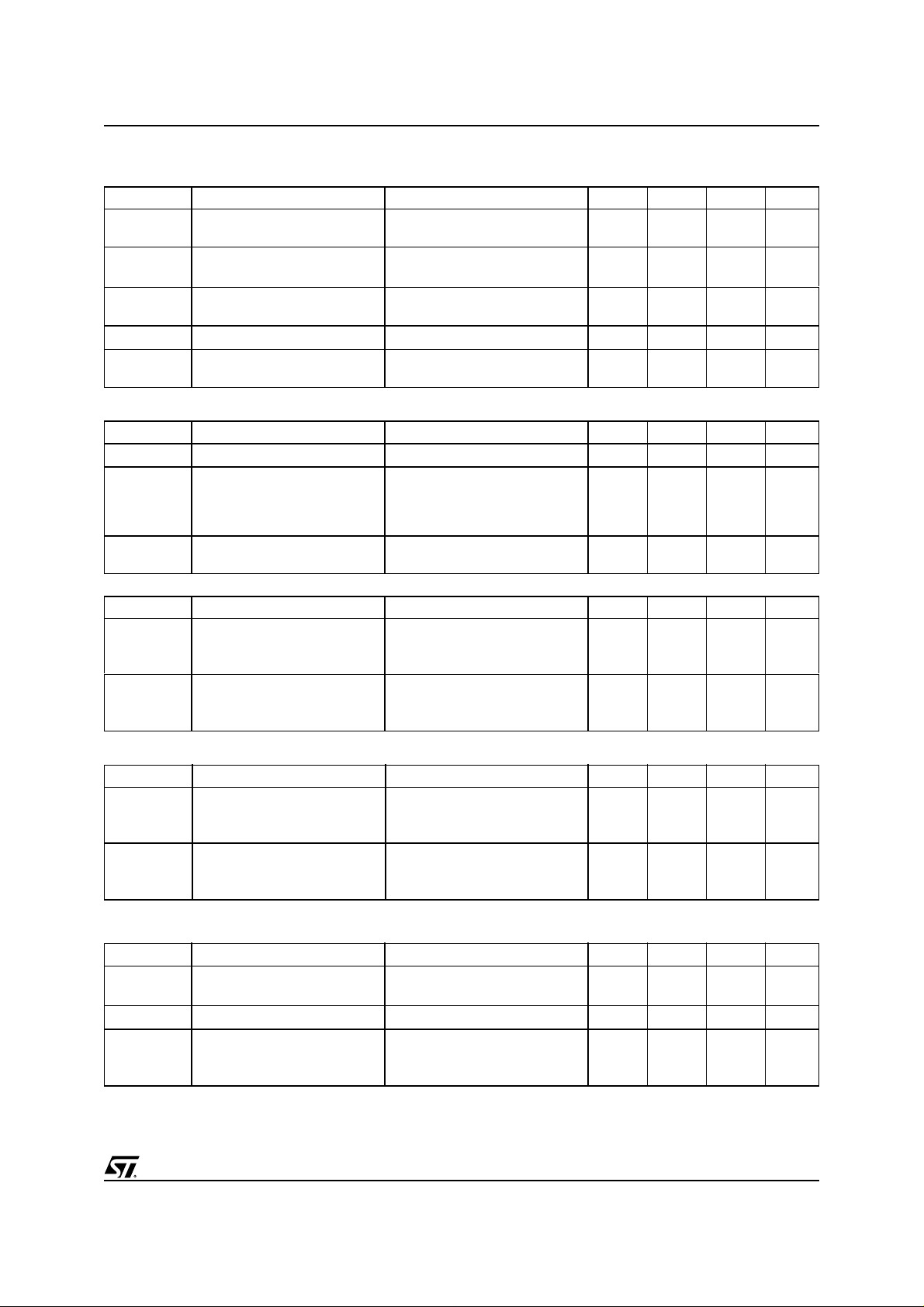

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

STP8NK80Z - STW8NK80Z STP8NK80ZFP

V

V

DGR

V

I

I

IDM()

P

TOT

V

ESD(G-S)

dv/dt (1) Peak Diode Recovery voltage slope 4.5 V/ns

V

T

T

() Pulse width limited by safe operating area

(1) I

SD

(*) Limited only by maximum temperature allowed

Drain-source Voltage (VGS=0)

DS

Drain-gate Voltage (RGS=20kΩ)

Gate- source Voltage ± 30 V

GS

Drain Current (continuous) at TC= 25°C

D

Drain Current (continuous) at TC= 100°C

D

6.2 6.2 (*) A

3.9 3.9 (*) A

800 V

800 V

Drain Current (pulsed) 24.8 24.8 (*) A

Total Dissipation at TC= 25°C

140 30 W

Derating Factor 1.12 0.24 W/°C

Gate source ESD(HBM-C=100pF, R=1.5 KΩ) 4000 V

Insulation Withstand Voltage (DC) - 2500 V

ISO

Operating Junction Temperature

j

Storage Temperature

stg

≤6.2A, di/dt ≤200 A/µs,VDD≤ V

(BR)DSS,Tj≤TJMAX.

-55to150 °C

THERMAL DATA

TO-220 TO-220FP TO-247

Rthj-case Thermal Resistance Junction-case Max 0.89 4.2 0.89 °C/W

Rthj-amb Thermal Resistance Junction-ambient Max 62.5 50

T

Maximum Lead Temperature For Soldering Purpose 300 °C

l

°C/W

AVALANCHE CHARACTERISTICS

Symbol Parameter Max Value Unit

I

AR

E

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

Single Pulse Avalanche Energy

AS

(starting T

= 25°C, ID=IAR,VDD=50V)

j

max)

j

6.2 A

300 mJ

GATE-SOURCE ZENER DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

BV

Gate-Source Breakdown Voltage

GSO

Igs=± 1 mA (Open Drain) 30 V

PROTECTION FEATURES OF GATE-TO-SOURCE ZENER DIODES

The built-in back-to-back Zener diodes have specifically been designed t o enhance not only the device’s

ESD capability, but also to make them s a fely absorb possible volt age trans ients tha t may occasionally be

applied from gate to source. In this respect the Zener voltage is appropriate to achieve an efficient and

cost-effective intervention to protect the device’ s integrity. These integ rated Zener diodes thus avoid the

usage of external components.

2/11

STP8NK80Z - STP8NK 80ZFP - STW8NK80Z

ELECTRICAL CHARACTERISTICS (T

=25°C UNLESS OTHERWISE SP ECIFIED)

CASE

ON/OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

ID=1mA,VGS= 0 800 V

Breakdown Voltage

I

DSS

I

GSS

V

GS(th)

R

DS(on)

Zero Gate Voltage

Drain Current (V

GS

=0)

Gate-body Leakage

Current (V

DS

=0)

Gate Threshold Voltage

Static Drain-source On

V

= Max Rating

DS

VDS= Max Rating, TC= 125 °C

V

= ± 20V ±10 µA

GS

V

DS=VGS,ID

= 100 µA

3 3.75 4.5 V

1

50

VGS=10V,ID= 3.1 A 1.3 1.5 Ω

Resistance

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

(1) Forward Transconductance VDS=15V,ID= 3.1 A 5.2 S

g

fs

C

oss eq.

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

(3) Equivalent Output

=25V,f=1MHz,VGS= 0 1320

V

DS

143

27

VGS=0,VDS= 640 V 58 pF

Capacitance

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(on)

Q

Q

Q

Turn-on Delay Time

t

r

g

gs

gd

Rise Time

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

VDD=400V,ID= 3.1 A

RG= 4.7Ω,VGS=10V

(Resistive Load see, Figure 3)

=640V,ID= 6.2 A,

V

DD

V

=10V

GS

17

30

46

8.5

25

µA

µA

pF

pF

pF

ns

ns

nC

nC

nC

SWITCHING OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(off)

Turn-off Delay Time

t

f

Fall Time

VDD= 400 V, ID= 3.1 A

R

=4.7ΩVGS=10V

G

48

28

(Resistive Load see, Figure 3)

t

r(Voff)

t

t

c

= 640V, ID= 6.2 A,

Off-voltage Rise Time

f

Fall Time

Cross-over Time

V

DD

RG=4.7Ω, VGS=10V

(Inductive Load see, Figure 5)

9

9

18

SOURCE DRAIN DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

VSD(1)

t

rr

Q

rr

I

RRM

Note: 1. Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %.

2. Pulse width limited by safe operating area.

3. C

Source-drain Current

(2)

Source-drain Current (pulsed)

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

is defined as a constant equivalent capacitance giving the same charging time as C

oss eq.

.

V

DSS

ISD= 6.2 A, VGS=0

I

SD

VDD=50V,Tj= 150°C

(see test circuit, Figure 5)

= 6.2 A, di/dt = 100 A/µs

460

2990

13

when VDSincreases from 0 to 80%

oss

6.2

24.8

1.6 V

ns

ns

ns

ns

ns

A

A

ns

nC

A

3/11

STP8NK80Z - STP8NK80ZFP - STW8NK80Z

Safe Operating Area For TO-220

Thermal Impedance For TO-220

Thermal Impedance For TO-220FPSafe Operating Area For TO-220FP

4/11

Thermal Impedance For TO-247Safe Operating Area For TO-247

Loading...

Loading...