SGS Thomson Microelectronics STP80NF10FP Datasheet

1/9September 2002

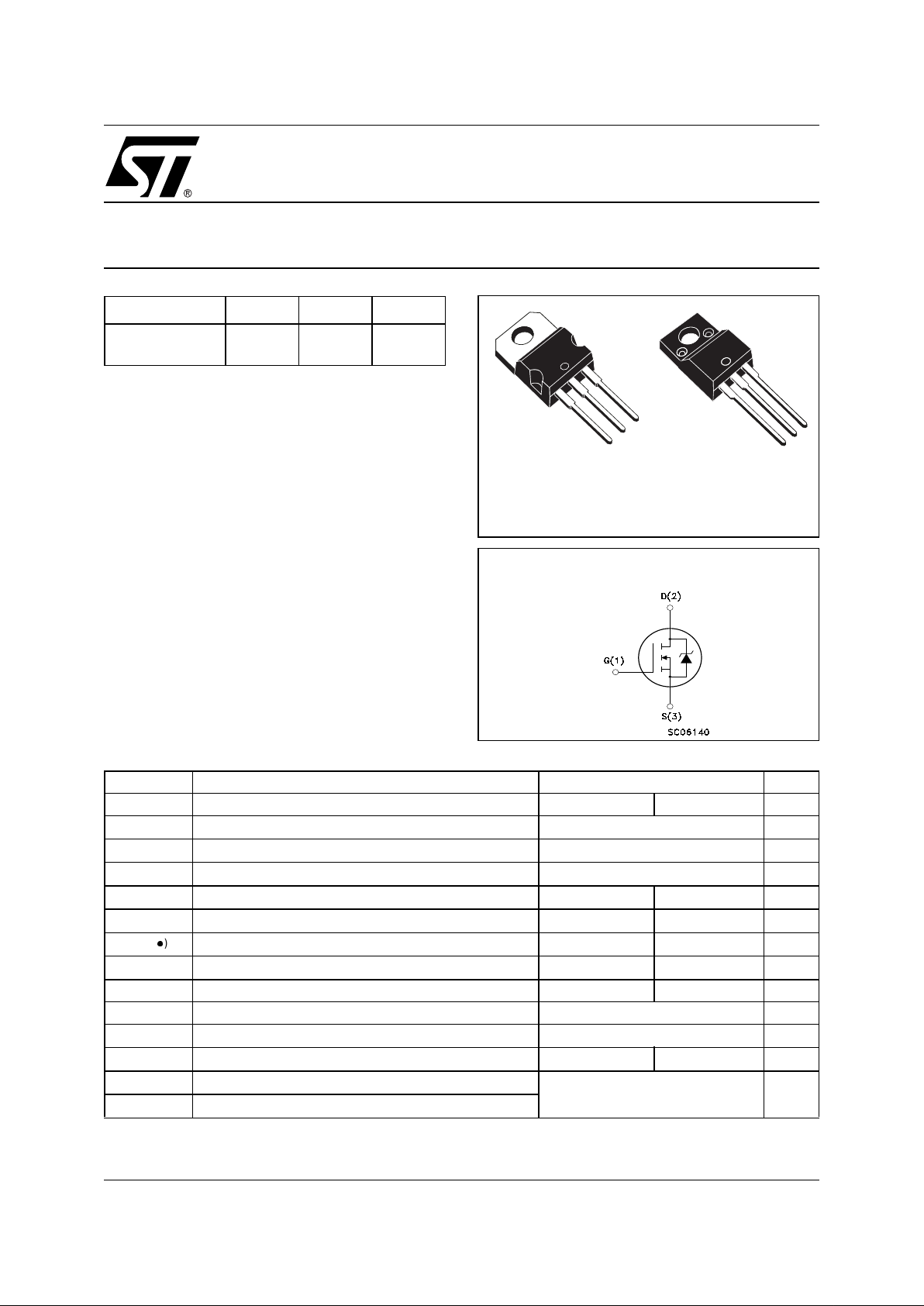

STP80NF10

STP80NF10FP

N-CHANNEL 100V - 0.012Ω - 80A TO-220/TO-220FP

LOW GATE CHARGE STripFET™II POWER MOSFET

(1) ISD ≤80A, di/dt ≤300A/µs, VDD ≤ V

(BR)DSS

, Tj ≤ T

JMAX.

(2) Starting Tj = 25°C, ID = 80A, VDD = 50V

■ TYPICAL R

DS

(on) = 0.012Ω

■ EXCEPTIONA L dv/d t CAPABILITY

■ 100% AVALANCHE TESTED

■ APPLICATION ORIENTED

CHARACTERIZATION

DESCRIPTION

This Power MOSFET series realized with STM icroelectronics unique STripFET process has specifically been designed to minimize input capacitance and

gate charge. It is therefore suitable as primary

switch in advanced high-efficiency isolated D C-DC

converters for T el ecom and Computer application. It

is also intended for any application with low gate

charge drive requirements.

APPLICATIONS

■ HIGH-EFFICIENCY DC-DC CONVERTERS

■ UPS AND MOTOR CONTROL

ABSOLUTE MAXIMUM RATINGS

(●) Pulse width limited by safe operating area

(*) Limited by Package

TYPE V

DSS

R

DS(on)

I

D

STP80NF10

STP80NF10FP

100 V

100 V

< 0.015 Ω

< 0.015 Ω

80 A

38 A

Symbol Parameter Value Unit

STP80NF10 STP80NF10FP

V

DS

Drain-source Voltage (VGS = 0)

100 V

V

DGR

Drain-gate Voltage (RGS = 20 kΩ)

100 V

V

GS

Gate- source Voltage ±20 V

I

D

(*) Drain Current (continuous) at TC = 25°C

80 38 A

I

D

Drain Current (continuous) at TC = 100°C

66 27 A

I

DM

(l)

Drain Current (pulsed) 320 152 A

P

TOT

Total Dissipation at TC = 25°C

300 45 W

Derating Factor 2 0.3 W/°C

dv/dt (1) Peak Diode Recovery voltage slope 9 V/ns

E

AS

(2)

Single Pulse Avalanche Energy 360 mJ

V

ISO

Insulation Withstand Voltage (DC) - 2500 V

T

stg

Storage Temperature

– 55 to 175 °C

T

j

Max. Operating Junction Temperature

TO-220

1

2

3

1

2

3

TO-220FP

INTERNAL SCHEMATIC DIAGRAM

STP80NF10/STP80NF10FP

2/9

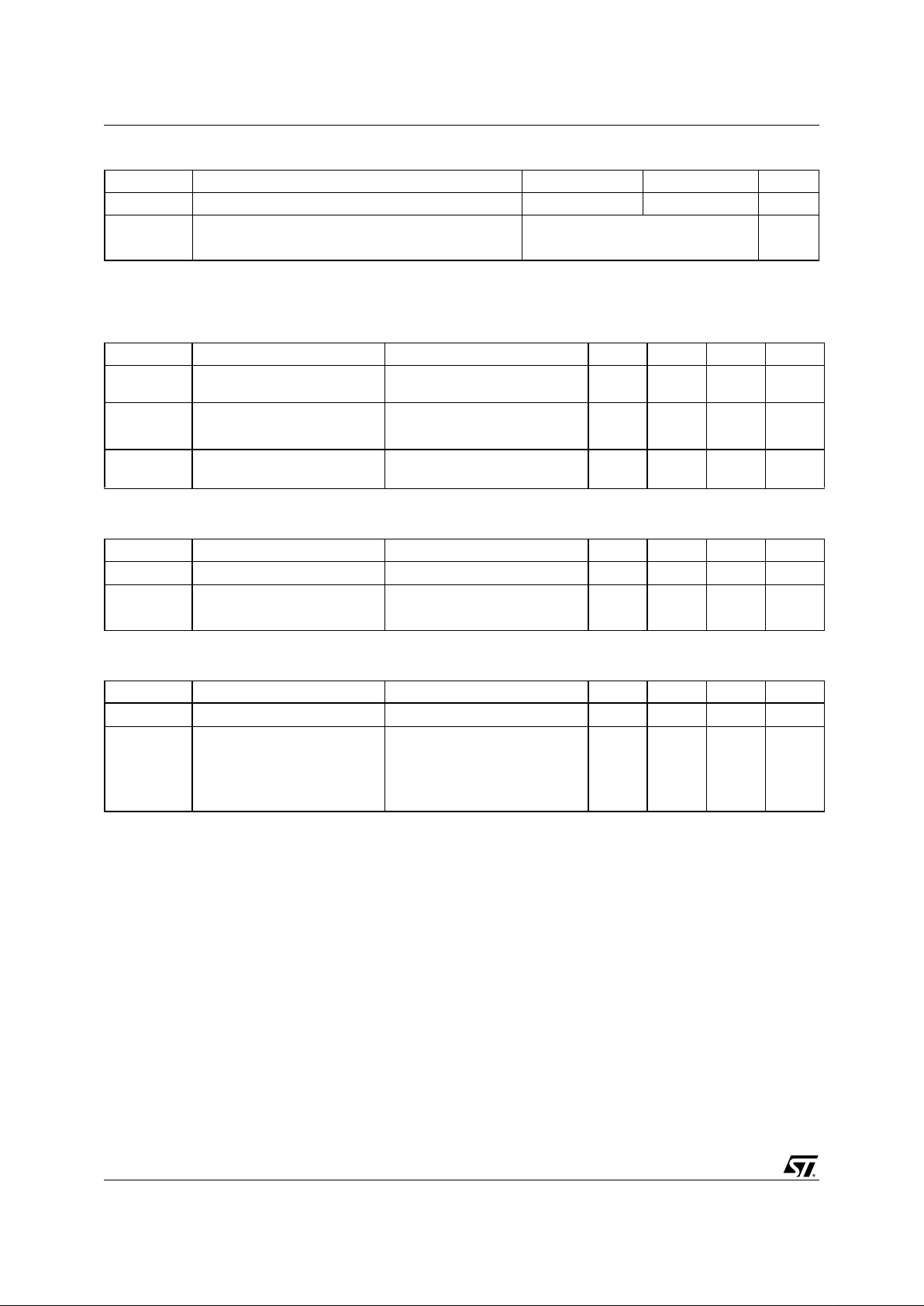

THERMA L D ATA

ELECTRICAL CHARACTERISTICS (T

CASE

= 25 °C UNLESS OTHERWISE SPECIFIED)

OFF

ON

(1)

DYNAMIC

TO-220 TO-220FP

Rthj-case Thermal Resistance Junction-case Max 0.5 3.33 °C/W

Rthj-amb Thermal Resistance Junction-ambient Max 62.5 °C/W

T

l

Maximum Lead Temperature For Soldering Purpose 300 °C

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

ID = 250 µA, VGS = 0 100 V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

1µA

V

DS

= Max Rating, TC = 125 °C

10 µA

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= ±20V ±100 nA

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

Gate Threshold Voltage

V

DS

= VGS, ID = 250µA

234V

R

DS(on)

Static Drain-source On

Resistance

VGS = 10V, ID = 40 A

0.012 0.015 Ω

Symbol Parameter Test Conditions Min. Typ. Max. Unit

g

fs

(1) Forward Transconductance VDS =25V , ID=40 A 80 S

C

iss

Input Capacitance

V

DS

= 25V, f = 1 MHz, VGS = 0

4300 pF

C

oss

Output Capacitance 600 pF

C

rss

Reverse Transfer

Capacitance

230 pF

3/9

STP80NF10/STP80NF10FP

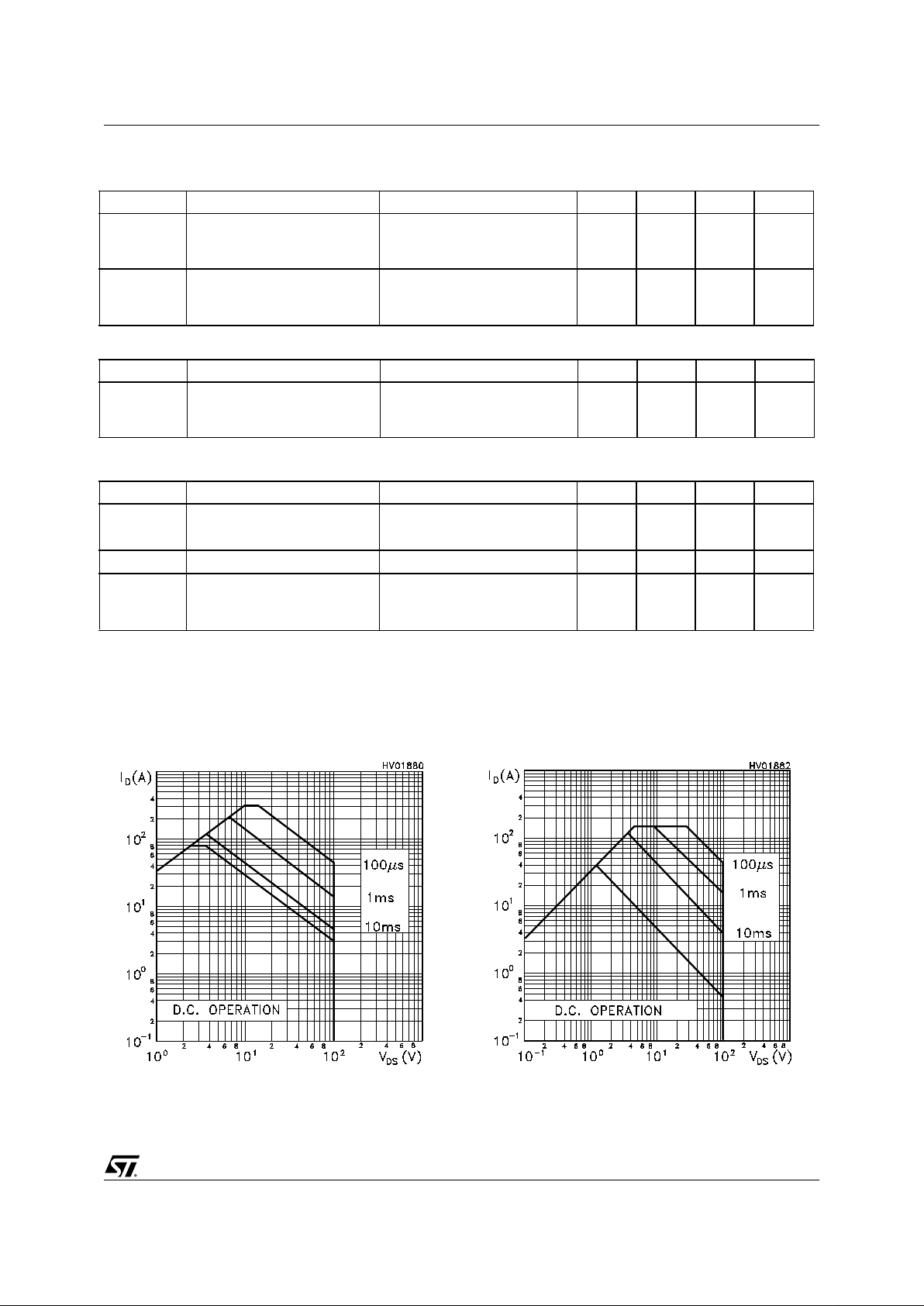

ELECTRICAL CHARACTERISTICS (CONTINUED)

SWITCHING ON

SWITCHING OFF

SOURCE DRAIN DIODE

Note: 1. Pulsed: Pul se duration = 300 µs, duty cy cle 1.5 %.

2. Pulse width l i m i t ed by safe ope rating area.

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(on)

Turn-on Delay Time

V

DD

= 50V, ID = 40A

R

G

= 4.7Ω VGS = 10V

(see test circuit, Figure 3)

40 ns

t

r

Rise Time 145 ns

Q

g

Q

gs

Q

gd

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

V

DD

= 80V, ID = 80A,

VGS = 10V

140

23

51

189

nC

nC

nC

Symbol Param eter Test Conditions Mi n. Typ. Max. Unit

t

d(off)

t

f

Turn-off-Delay Time

Fall Time

VDD = 50V, ID = 40A,

RG= 4.7Ω, V

GS

= 10V

(see test circuit, Figure 3)

134

115

ns

ns

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

Source-drain Current 80 A

I

SDM

(2)

Source-drain Current (pulsed) 320 A

VSD (1)

Forward On Voltage

ISD = 80A, VGS = 0

1.3 V

t

rr

Q

rr

I

RRM

Reverse Recovery Time

Reverse Recovery Charg e

Reverse Recovery Curren t

I

SD

= 80A, di/dt = 100A/µs,

V

DD

= 50V, Tj = 150°C

(see test circuit, Figure 5)

155

0.85

11

ns

µC

A

Safe Operating Area for TO-220FPSafe Operating Area for TO-220

Loading...

Loading...