SGS Thomson Microelectronics STLVDS105BTR, STLVDS105BDR, STLVDS105BD Datasheet

4-PORT LVDS AND 4-PORT TTL-TO LVDS

■ RECEIVER AND DRIVERS MEET OR

EXCEED THE REQUIREMENTS OF ANSI

EIA/TIA-644 STANDARD: RECEIVERS

LOW-VOLTAGE TTL (LVTTL) LEVELS

DESIGNED FOR SIGNALING RATES UP TO

630Mbps

■ OPERATES FROM A SINGLE 3.3V SUPPLY

■ LOW VOLTAGE DIFFERENTIAL SIGNALING

WITH TYPICAL OUTPUT VOLTAGE OF

350mV AND A 100Ω LOAD

■ PROPAGATION DELAY TIME: 2.2ns (TYP)

■ ELECTRICALLY COMPATIBLE WITH LVDS,

PECL, LVPECL, LVTTL, LVCOMOS, GTL,

BTL, CTT, S STL, OR HSTL OUTPUTS W ITH

EXTERNAL NETWORK

■ BUS TERMINAL ESD (HBM) EXCEEDS 7KV

■ SO AND TSSOP PACKAGING

DESCRIPTION

The STL VDS 105 is a differential line receiver and

a LVTTL input connected to four differential line

drivers that implement the electrical

characteristics of low voltagedifferential signaling,

for point to point baseband data transmission over

controlled impedance media of approximately

100Ω. The trans mission media can be

printed-circuit board traces, backplanes, or cable.

STLVDS105

REPEATERS

SOP TSSOP

LVDS, as specified in EIA/TIA-644 is a data

signaling technique that offers low-power, low

noise coupling, and switching s peed to transmit

data at a speed up to 630Mbps at relatively long

distances.

The drivers integrated into t he same substra te,

along with the low pulse skew of balanced

signaling, allow extremely precise timing

alignment of the signals repeated from the input.

The device allows extremely precise timing

alignment of the signal rep eated from the input.

This is particularly advantageous in distribution or

expansion of s ignals such as clock or serial data

stream.

ORDERING CODES

Type

STLVDS105BD -40 to 85 °C SO-16 (Tube) 50parts per tube / 20tube per box

STLVDS105BDR -40to 85 °C SO-16 (Tape & Reel) 2500 parts per reel

STLVDS105BTR -40 to 85 °C TSSOP16 (Tape & Reel) 2500 parts per reel

Temperature

Range

Package Comments

1/8May 2003

STLVDS105

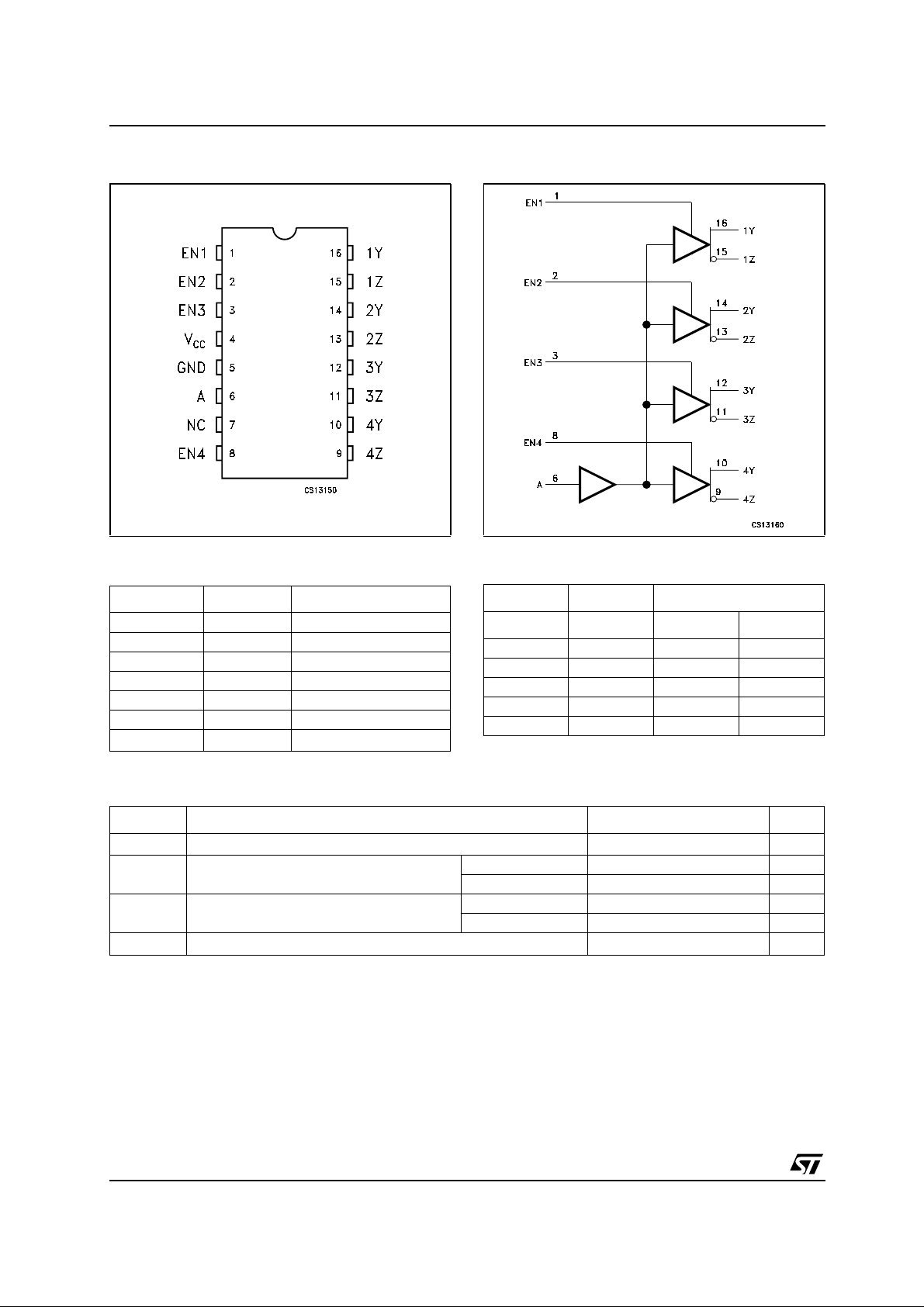

PIN CONFIGURATION

PIN DESCRIPTION

PlN N° SYMBOL NAME AND FUNCTION

1, 2, 3, 8 EN1 to EN4 Enable Driver Inputs

6 A Receiver Input

7 NC Not Connected

9, 11, 13, 15 1Z to 4Z Driver Inputs

10, 12, 14, 16 1X to 4X Driver Inputs

5 GND Ground

4

V

CC

Supply Voltage

FUNCTIONAL DIAGRAM

FUNCTIONAL TABLE

INPUT ENABLES OUTPUTS

A #EN #Y #Z

LHLH

HHHL

Open H L H

XLZZ

XXZZ

L=Low level, H=High Level, Z= High Impedance

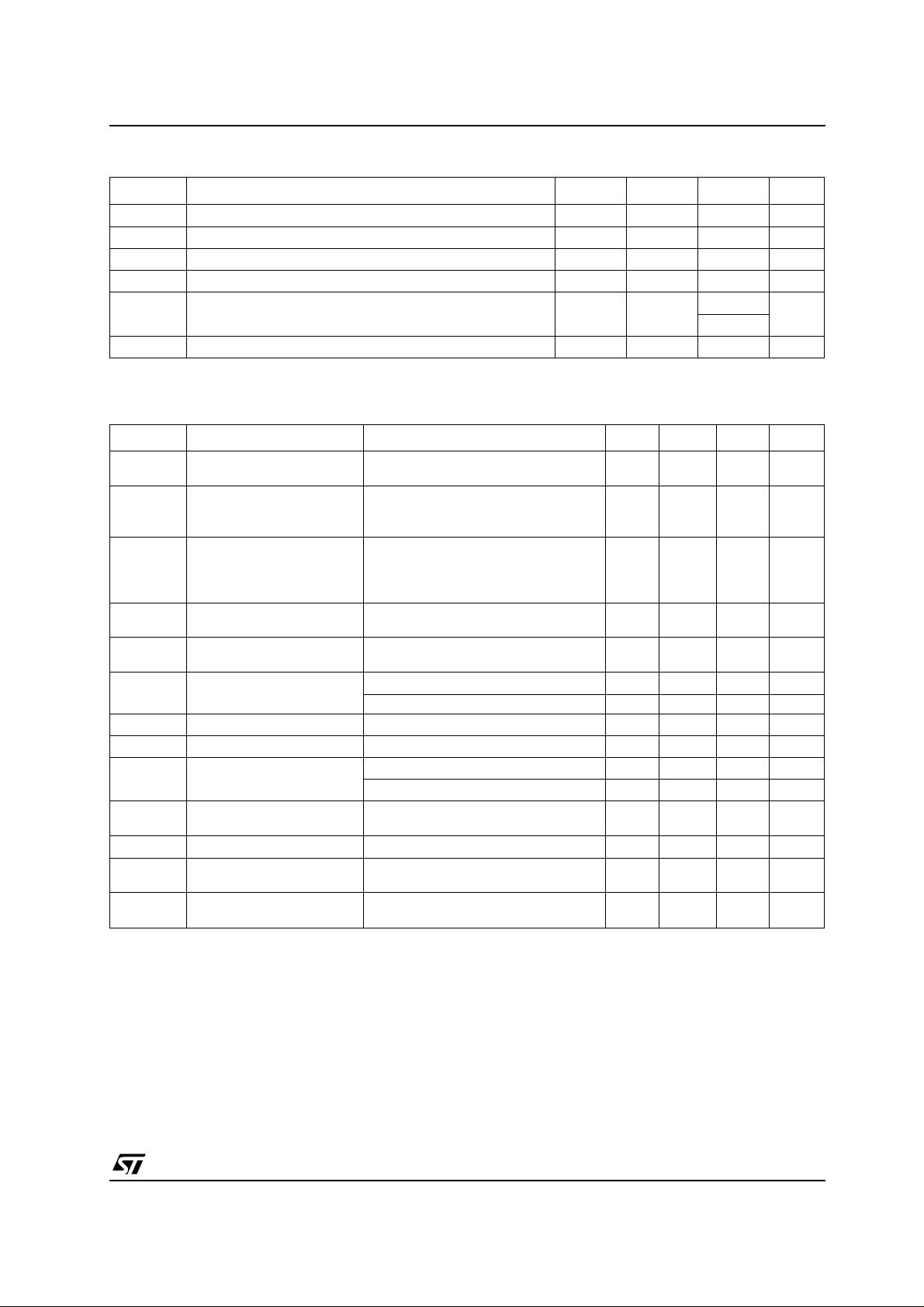

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

V

ESD ESD Protection Voltage (HBM) Y, Z, to GND 7 KV

T

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is

not implied.

Note 1: All voltages except differential I/O bus voltage, are with respect to the network ground terminal.

2/8

Supply Voltage (Note 1)

CC

Voltage Range Enable Inputs -0.5 to 6 V

R

-0.5 to 4 V

A, Y or Z -0.5 to 4 V

All Pins 2 KV

Storage Temperature Range

stg

-65 to +150 °C

STLVDS105

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

V

V

V

|V

V

T

Supply Voltage 3.0 3.3 3.6 V

CC

HIGH Level Input Voltage 2.0 V

IH

LOW Level Input Voltage 0.8 V

IL

| Magnitude Of Differential Input Voltage 0.1 3.6 V

ID

Common Mode Input Voltage |VID|/2 24-|VID|/2 V

IC

-0.8

V

CC

Operating Temperature Range

A

-40

85

°C

ELECTRICAL CHARACTERISTICS (T

operating conditions unless otherwise noted. All typical values are at T

= -40 to 85°C, and VCC= 3.3V ±10% over recommended

A

=25°C)

A

Symbol Parameter Test Conditions Min. Typ. Max. Unit

| Differential Output Voltage

|V

OD

Magnitude

∆|V

| Change in Differential

OD

Output Voltage Magnitude

RL= 100Ω VID= ±100mV 247 340 454 mV

-50 50 mV

Between Logic State

∆V

OC(SS)

Change in Steady-state

Common Mode Output

-50 50 mV

Voltage Between Logic

State

V

OC(SS)

V

OC(PP)

I

CC

Steady-state Common

Mode Output Voltage

Peak to Paek Common

mode Output Voltage

Supply Current Enabled, RL=100Ω 18 28 mA

1.125 1.2 1.375 V

25 150 mV

Disabled 0.3 1 mA

I

I

I

OC

I

OZ

I

O(OFF)

C

C

High Level Input Current VIH=2V 7 20 µA

IH

Low Level Input Current VIL= 0.8V 3 10 µA

IL

Short Circuit Output Current V

High Impedance Output

or V

O(Y)

=0 ± 10 mA

V

OD

=0V ± 10 mA

O(Z)

VO= 0 or 2.4V ± 1 µA

Current

Power OFF Output Current VCC= 1.5V VO= 2.4V 0.3 ± 1 µA

Input Capacitance (A or B

IN

Inputs)

Output Capacitance (Y or Z

O

Outputs)

= 0.4 sin (4e

V

I

= 0.4 sin (4e

V

I

6πt

)+0.5V

6πt

)+0.5V, Disabled

5pF

9.4 pF

3/8

Loading...

Loading...