PROGRAMMABLE LOW VOLTAGE

1:10 DIFFERENTIAL LVDS CLOCK DRIVER

■ 100ps PART-TO PART SKEW

■ 50ps BANK SKEW

■ DIFFERENTIAL DESIGN

■ MEETS LVDS SPEC. FOR DRIVER

OUTPUTS AND RECEIVER INPUTS

■ REFERENCE VOLTAGE AVAILABLE

OUTPUT V

■ LOW VOLTAGEV

2.625V

■ HIGH SIGNALLING RATE CAPABILITY

(EXCEEDS 622MHz)

■ SUPPORT OPEN, SHORT AND

TERMINATED INPUT FAIL-SAFE (LOW

OUTPUT STATE)

■ PROGRAMMABLE DRIVERS POWER OFF

CONTROL

BB

RANGE OF 2.375V TO

CC

STLVD111

TQFP32

DESCRIPTION

The STLVD111 is a low skew program mable 1 to

10 differential LVDS driver, designed for clock

distribution. The select signal is fanned out to 10

identical differential outputs.

The STLVD111 is provided with a 11 bit shift

register with a serial in and a Control Register.

The purpose is to enable or power off each output

clock c hannel and to s elect the clock input . The

produced with low skew as the key goal. Optimal

design and layout serve to minimize gate to gate

skew within a device. The net result is a

dependable guaranteed low skew dev ice.

The STLVD111 can be used for high performanc e

clock distribution in 2.5V systems with LVDS

levels. Designers can take adv antage of the

device’s performance to d istribute low skew

clocks across the backplane or the board.

STLVD111 is s pec ific ally designed, modelled and

ORDERING CODES

Type

STLVD111BF -40 to 85 °C TQFP32 (Tray) 250 parts per Tray

STLVD111BFR -40 to 85 °C TQFP32 (Tape & Reel) 2400 parts per reel

Temperature

Range

Package Comments

1/12December 2002

STLVD111

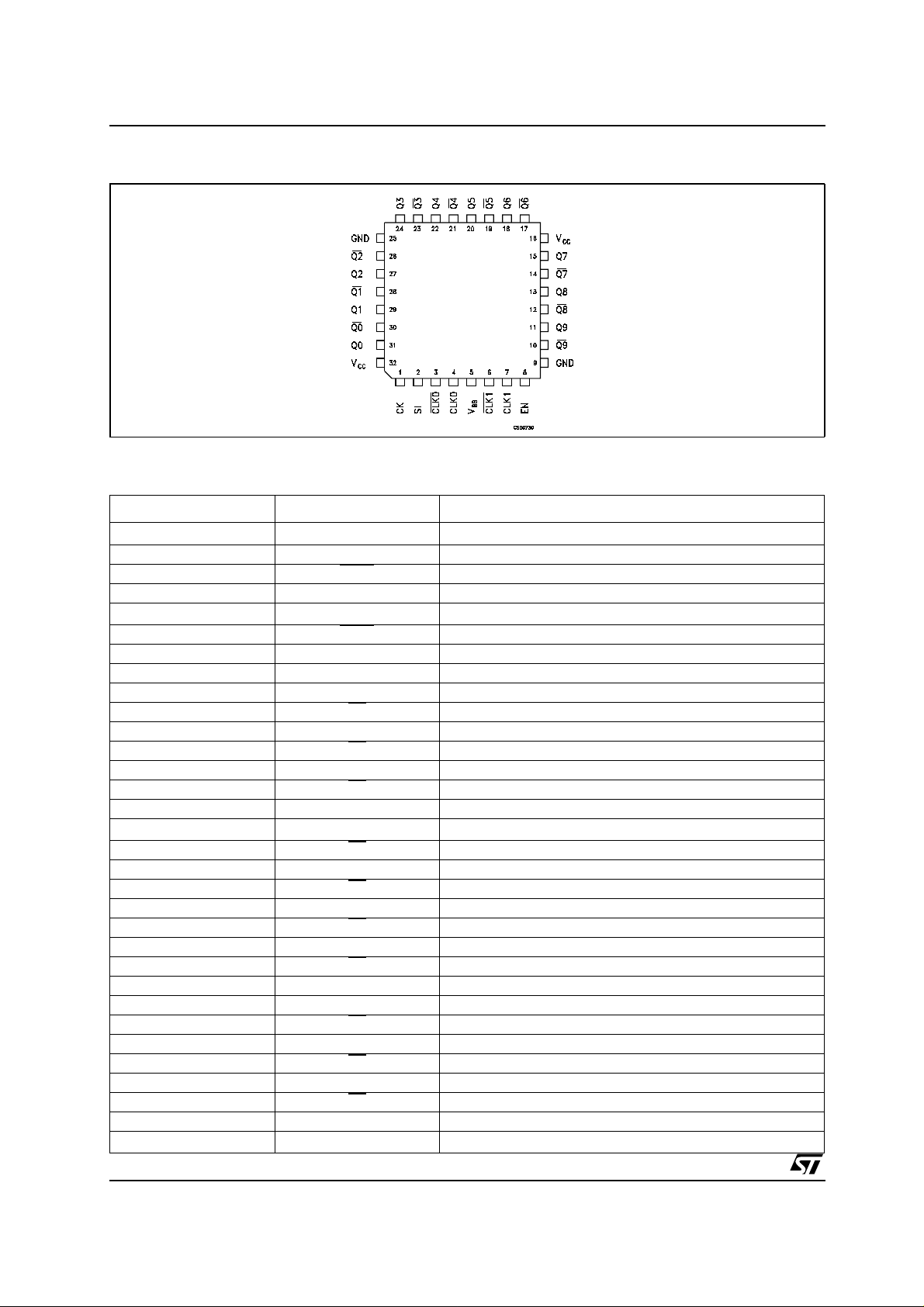

PIN CONFIGURATION

PIN DESCRIPTION

PlN N° SYMBOL NAME AND FUNCTION

1 CK Control Register Clock

2 SI Control Register Serial IN/CLK_SEL

3 CLK0

4 CLK0 Differential Input

5

6 CLK1

7 CLK1 Differential Input

8 EN Device Enable/Program

9 GND Ground

10 Q9

11 Q9 Differential Outputs

12 Q8

13 Q8 Differential Outputs

14 Q7

15 Q7 Differential Outputs

16

17 Q6

18 Q6 Differential Outputs

19 Q5

20 Q5 Differential Outputs

21 Q4

22 Q4 Differential Outputs

23 Q3

24 Q3 Differential Outputs

25 GND Ground

26 Q2

27 Q2 Differential Outputs

28 Q1

29 Q1 Differential Outputs

30 Q0

31 Q0 Differential Outputs

32

2/12

Differential Input

V

BB

Output Reference Voltage

Differential Input

Differential Outputs

Differential Outputs

Differential Outputs

V

CC

Supply Voltage

Differential Outputs

Differential Outputs

Differential Outputs

Differential Outputs

Differential Outputs

Differential Outputs

Differential Outputs

V

CC

Supply Voltage

STLVD111

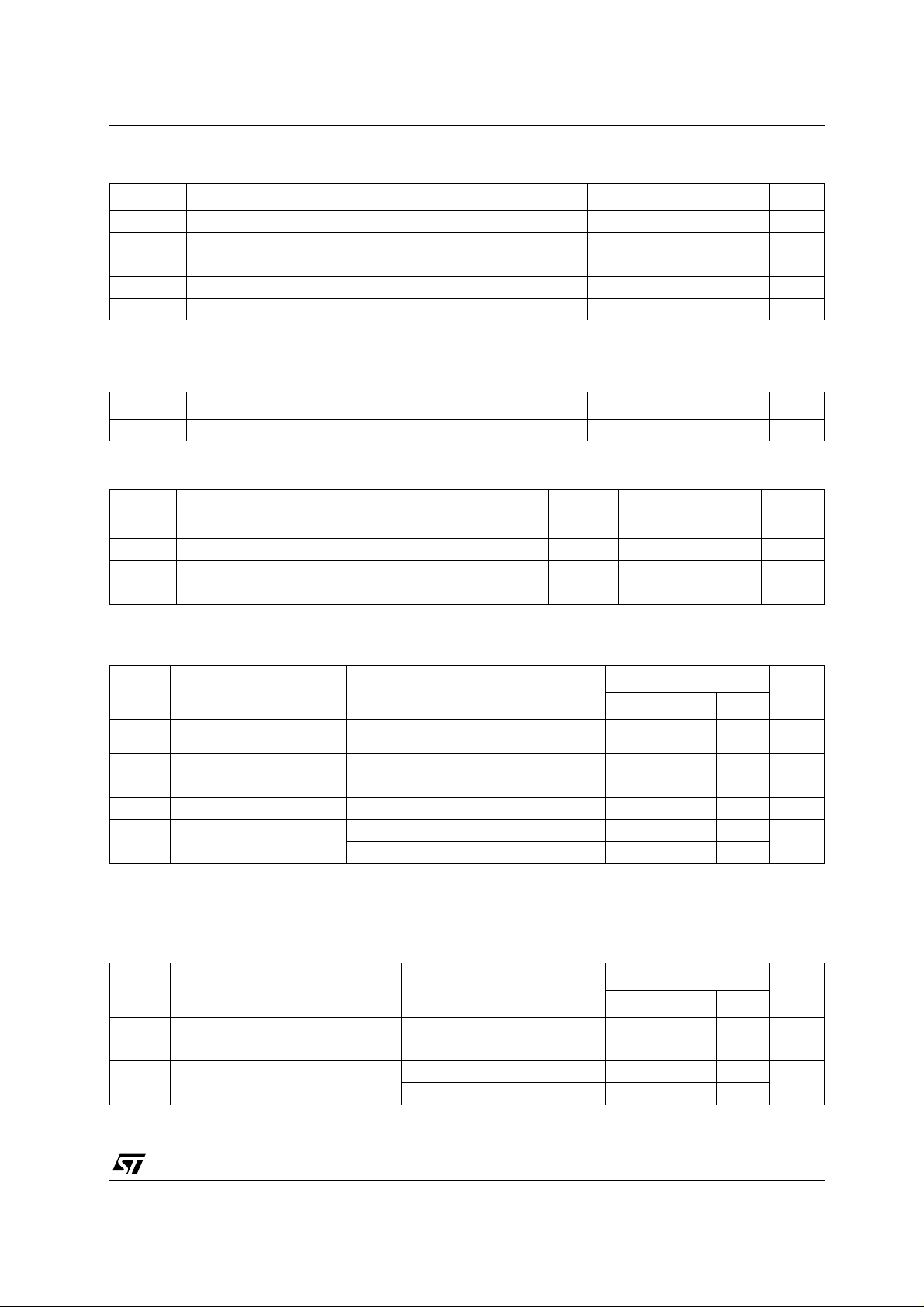

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

V

V

I

OSD

ESD Electrostatic Discharge (HBM 1.5KΩ, 100pF)

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is

not implied.

THERMAL DATA

Symbol Parameter Value Unit

R

RECOMMENDED OPERATIN G CONDITIONS

Symbol Parameter Min TYP Max Unit

V

CC

V

IC

T

A

T

Supply Voltage

CC

Input Voltage -0.2 to (VCC+0.2)

I

Output Voltage -0.2 to (VCC+0.2)

O

Driver Short Circuit Current

-0.3 to 2.8 V

Continuous

>2 KV

Thermal Resistance Junction-Case

Tj-c

Supply Voltage

2.375 2.625 V

13 °C/W

Receiver Common Mode Input Voltage 0.5(VID) 2-0.5(VID)

Operating Free-Air Temperature Range

Operating Junction Temperature

J

-40 85 °C

-40 105 °C

V

V

V

DRIVER ELECTRICAL CHARACTERISTICS (T

= -40 to 85 °C, VCC= 2.5V ± 5%, unless otherwise

A

specified (Note 1, 2)

Symbol Parameter Test Conditions

Min. Typ. Max.

V

∆V

V

∆V

NOTE 1: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground

unless otherwise specified.

NOTE 2: All typical values are given for V

Output Differential Voltage

OD

(Fig. 2)

ODVOD

OS

OSVOS

I

OS

Magnitude Change 30 mV

Offset Voltage -40 ≤ TA≤ 85°C 1.05 1.15 1.25 V

Magnitude Change 30 V

Output Short Circuit Current VO=0V 15 30 mA

RL=100Ω 400 500 600 mV

=0V 7 15

V

OD

=2.5VandTA= 25°C unless otherwise stated.

CC

Value

Unit

RECEIVER ELECTRICAL CHARACTERISTICS (TA=-40to85°C,VCC= 2. 5V ± 5%, unless otherwise

specified (Note 1, 2)

Symbol Parameter Test Conditions

Min. Typ. Max.

V

V

NOTE 1: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground

unless otherwise specified.

NOTE 2: All typical values are given for V

Input Threshold High 100 mV

IDH

Input Threshold Low -100 mV

IDL

Input Current VI= 0V 42 100 µA

I

IN

=0V

V

I

CC

=2.5VandTA= 25°C unless otherwise stated.

CC

Value

Unit

210

3/12

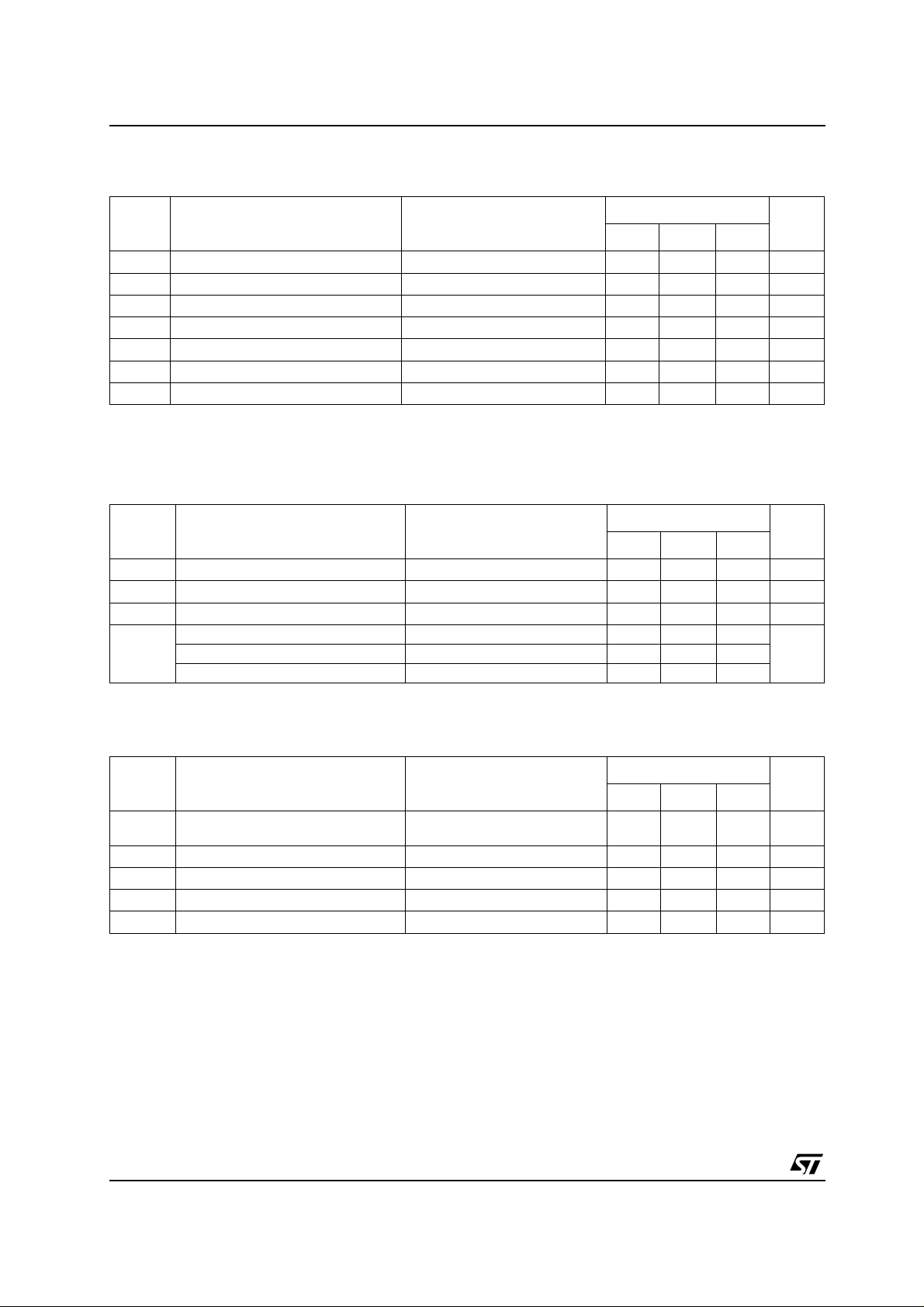

STLVD111

DRIVER ELECTRICAL CHARACTERISTICS (TA= -40 to 85 °C, VCC= 2.5V ± 5%, unless otherwise

specified (Note 1, 2)

Symbol Parameter Test Conditions

Unit

Min. Typ. Max.

Value

Output Reference Voltage VCC= 2.5 V 1.15 1.25 1.35 V

V

BB

I

C

NOTE 1: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground

unless otherwise specified.

NOTE 2: All typical values are given for V

Power Supply Current All driver enabled and loaded 125 160 mA

CCD

Input Capacitance VI=0VtoV

C

IN

Output Capacitance 5 pF

OUT

Logic Input High Threshold VCC= 2.5 V 2 V

V

IH

V

Logic Input Low Threshold VCC= 2.5 V 0.8 V

IL

Logic Input Current VCC= 2.5 V, VIN=VCCorGND ±10 µA

I

I

=2.5VandTA= 25°C unless otherwise stated.

CC

CC

5pF

LVDS TIMING CHARACTERISTICS (TA= -40 to 85 °C, VCC= 2.5V ± 5%, unless otherwise specified

(Note 4)

Symbol Parameter Test Conditions

Min. Typ. Max.

t

TLH,tTHL

t

PHL,tPLH

f

MAX

t

SKEW

Transition Time RL= 100 Ω,CL= 5 pF, Fig. 5, 6) 220 300 ps

Propagation Delay Time (Fig. 5, 6) 2 2.5 ns

Maximum Input Frequency 700 900 MHz

Bank Skew (Fig. 1) 50 ps

Part to Part Skew (Fig. 2) 100

Pulse Skew (Fig. 3) 50

NOTE 4: Generator waveforms for all test conditions: f=1MHz, ZO=50Ω(unless otherwise specified).

Value

Unit

CONTROL REGISTER TIMING CHARACTERISTICS (TA=-40to85°C,VCC= 2.5V ±5%,EN=H, unless

otherwise specified (Figure 4)

Symbol Parameter Test Conditions

f

MAX

t

Maximum Frequency of Shift

(Fig. 7) 100 150 MHz

Register

Clock to SI Setup Time (Fig. 7) 2 ns

t

s

Clock to SI Hold Time (Fig. 7) 1.5 ns

t

h

Enable to Clock Removal Time (Fig. 7) 1.5 ns

rem

Minimum Clock Pulse Width (Fig. 7) 3 ns

t

W

4/12

Min. Typ. Max.

Value

Unit

Loading...

Loading...