STLC5466

64 CHANNEL-MULTI HDLC WITH

N X 64KB/S SWITCHING MATRIX ASSOCIATED

PRELIMINARY DATA

■

64 TX HDLCs with broadcasting capability and/

or CSMA/CR function with automatic restart in

case of Tx frame abort

■

64 RX HDLCs including Address

Recognition

■

16 Command/Indicate Channels (4 or 6-bit

primitiv e )

■

16 Monitor Channels processed in accordance

with GCI or V*

■

256 x 256 Switching Matrix without blocking

and with Time Slot Sequence Integrity and

loopback per bidirectional connection

■

DMA Controller for 64 Tx Channels and 64 Rx

Channels

■

HDLCs AND DMA CONTROLLER ARE

CAPABLE OF HANDLING A MIX OF

LAPD,LAPB, SS7, CAS AND

PROPRIETARY SIGN AL L IN G S

■

External shared memory access

between DMA Controller and Micro

processor

■

SINGLE MEMORY SHARED BETWEEN

n x MULTI-HDLCs AND SINGLE MICRO

PROCESSOR ALLOWS TO HANDLE n x 64

CHANNELS

■

Bus Arbitration

■

Interface for various 8,16 or 32 bit

Microprocessors with fetch memory

to accelerate the exchanges

between Microprocessor and

SHARED MEMORY

■

SDRAM Controller allows to inter

face up to 16 Megabytes of

Synchronous Dynamic RAM

■

Interrupt Controller to store

automatically events in shared memory

■

Boundary scan for test facility

■

TQFP176 package 24 x 24 x 1.40

#MS-026BGA

■

HCMOS6; 0.35 micron; 3.3volts +/-5%

■

Operating temperature: -40 to +85 °/C

DESCRIPTION

The STLC5466 is a Subscriber line interface card

controller for Central Office, Central Exchange, NT2

and PBX capable of handling:

■

16 U Interfaces or

■

2 Megabits line interface cards or

■

16 SLICs (Plain Old Telephone Service) or

■

Mixed analogue and digital Interfaces

(SLICs or U Interfaces) or

■

16 S Interfaces

■

Switching Network with centralized processing.

TQFP176

(Plastic Quad Flat Pack)

ORDERING NUM BER:

STLC5466

November 1999

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

1/130

STLC5466

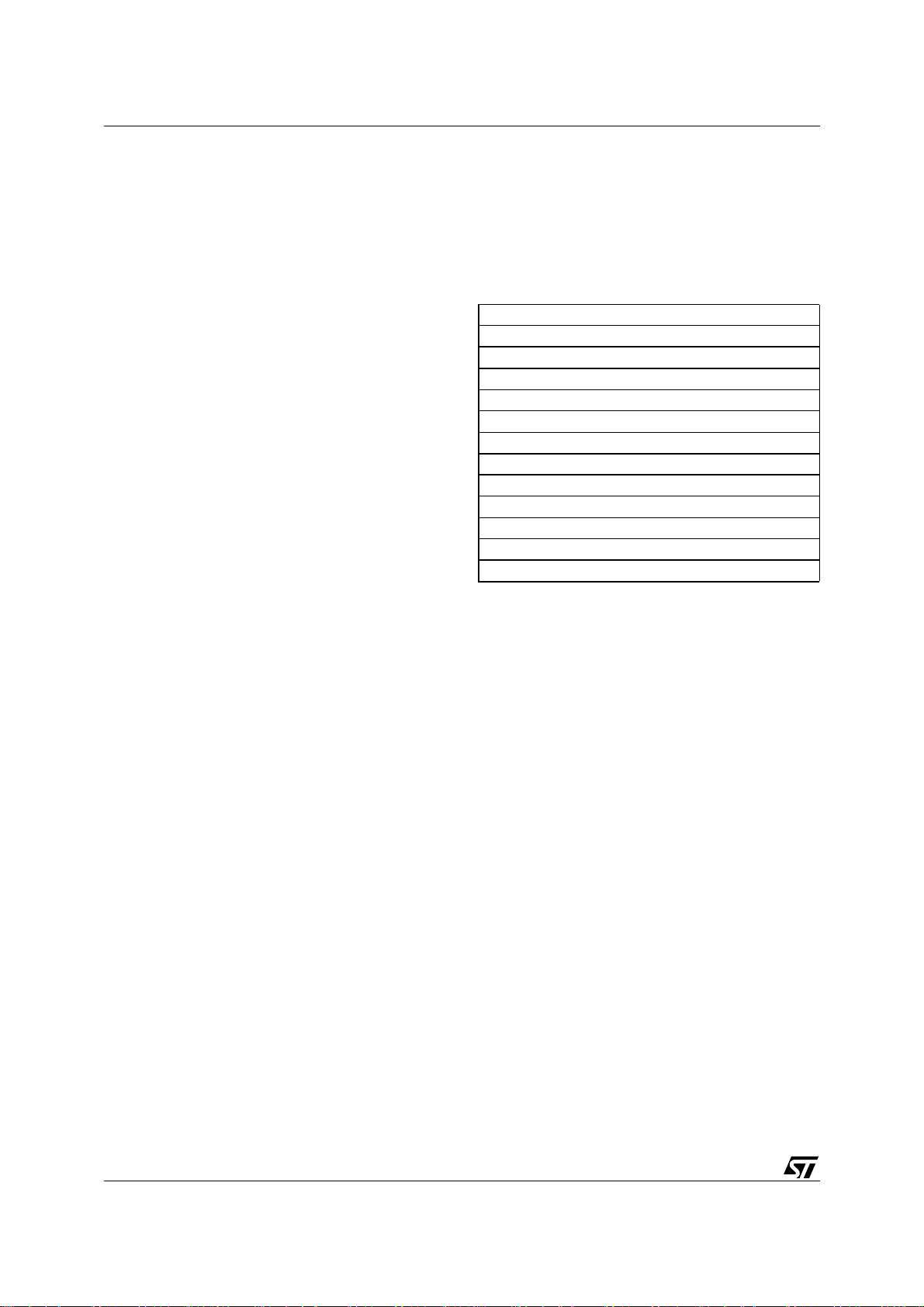

TABLE OF CONTENTS

I PIN INFORMATION................................................................................................................6

I.1 PIN CONNECTIONS....... .......................................................................................................6

I.2 PIN DESCRIPTION................................................................. ..............................................7

I.3 PIN DEFINITION...................................................................... ............................................12

I.3.1 Input Pin Definition................................................................................................................12

I.3.2 Output Pin Definition ............................................................................................................12

I.3.3 Input/Output Pin Definition. ..................................................................................................12

II BLOCK DIAGRAM...............................................................................................................13

III FUNCTIONAL DESCRIPTION................ ...................................... ...................................... .13

III.1 THE SWITCHING MATRIX N X 64 KBITS/S........................................................................13

III.1.1 Function Desc ription.............................................................................................................13

III.1.2 Architecture of the Matrix .....................................................................................................13

III.1.3 Connection Fun ction ............................................................................................................13

III.1.4 Loop Back Functio n ....................................................................................................... ......15

III.1.5 Delay through the Matrix ......................................................................................................15

III.1.5.1 Variable Delay Mode ........................................................................................................15

III.1.5.2 Sequence Integrity Mode..................................................................................................15

III.1.6 Connection Memo ry .............................................................................................................15

III.1.6.1 Description .......................................................................................................................15

III.1.6.2 Access to Connection Memory .........................................................................................15

III.1.6.3 Access to Data Memory....................................................................................................15

III.1.7 Switching at 32 Kbit/s ...........................................................................................................15

III.1.8 Switching at 16 Kbit/s ...........................................................................................................16

III.2 HDLC CONTROLLER.............................................................. ............................................16

III.2.1 Function desc r iption .............................................................................................................16

III.2.1.1 Format of the HDLC Frame..............................................................................................16

III.2.1.2 Composition of an HDLC Frame .......................................................................................16

III.2.1.3 Description and Functions of the HDLC Bytes..................................................................16

III.2.2 CS M A/CR Capability ............................................................................................................17

III.2.3 Time Slot Assigner Memory .................................................................................................17

III.2.4 D ata Storage Structure .........................................................................................................18

III.2.4.1 Reception..........................................................................................................................18

III.2.4.2 Transmission.....................................................................................................................18

III.2.4 .3 Frame Relay ......... .................................................................................................... ........18

III.2.5 Transparent Modes ....................................................................................... .......................18

III.2.6 C om m and of the HDLC Channels ........................................................................................19

III.2.6 .1 Reception Cont ro l.............................................................................................................19

III.2.6.2 Transmission Control........................................................................................................19

III.3 C/I AND MONITOR .................................................................. ............................................19

III.3.1 Function Desc ription ................................................................................................... .........19

III.3.2 GCI and V* Protocol .............................................................................................................19

2/130

STLC5466

III.3.3 Structure of the Treatment ...................................................................................................20

III.3.4 CI and Monitor Channel Configuration.................................................................. .......... .. ....20

III.3.5 CI and Monitor Transmission/Reception Command.............................................................20

III.4 SCRAMBLER AND DESCRAMBLER...................................... ............................................20

III.5 CONNECTION BETWEEN “ISDN CHANNELS” AND GCI CHANNELS..............................20

III.6 MICROPROCESSOR INTERFACE......................................... ............................................21

III.6.1 Description ...........................................................................................................................21

III.6.2 Buffer ...................................................................................................................................21

III.6.2 .1 Write FIFO ........................................................................................................................21

III.6.2.2 Read Fetch Memory .........................................................................................................23

III.6.2.3 Definition of the Interface for the different microprocessors..............................................23

III.7 MEMORY INTERFACE........................................................... ............................................23

III.7.1 Function Desc ription ................................................................................................... .........23

III.7.2 Choice of memory versus microprocessor and capacity required ........................................23

III.7.3 Memory Cycle.......................................................................................................................23

III.7.4 Memories composed of different circuits ..............................................................................23

III.7.4.1 Memory obtained with 1M x16 SDRAM circuit............................... .......... .. ....... .......... ......23

III.7.4.2 Memory obtained with 2M x 8 SDRAM circuit...................................................................23

III.7.4.3 Memory obtained with 8M x 8 SDRAM circuit...................................................................23

III.7.4.4 Memory obtained with 4M x 16 SDRAM circuit.................................................................24

III.8 BUS ARBITRATION................................................................ ............................................24

III.9 CLOCKS.. .................................................................................................................... ........24

III.9.1 C lo ck Distribution Selection and Supervision .......................................................................24

III.9.2 VCXO Frequency Synchronizat ion .......................................................................................24

III.10 INTERRUPT CONTROLLER................................................... ............................................25

III.10.1 Description ........................................................................................................... ................25

III.10.2 Operating Interrupts (INT0 Pin).............................................................................................25

III.10.3 Time Base Interrupts (INT1 Pin)...........................................................................................25

III.10.4 Emergency Interrupts (WDO Pin)......................................................................................... 25

III.10.5 Interrupt Queues ..................................................................................................................25

III.11 WATCHDOG............................................................................ ............................................25

III.12 RESET.................................................................................................................................25

III.13 BOUNDARY SCAN.................................................................. ............................................26

IV DC SPECIFICATIONS..........................................................................................................27

V LIST OF REGISTERS ..........................................................................................................29

VI INTERNAL REGISTERS......................................................................................................31

VI.1 IDENTIFICATION AND DYNAMIC COMMAND REGISTER... IDCR (00)H.........................31

VI.2 GENERAL CONFIGURATION REGISTER 1..........................GCR1 (02)H........................31

VI.3 INPUT MULTIPLEX CONFIGURATION REGISTER 0............IMCR0 (04)H.......................33

3/130

STLC5466

VI.4 INPUT MULTIPLEX CONFIGURATION REGISTER 1 ...........IMCR1 (06)H.......................34

VI.5 OUTPUT MULTIPLEX CONFIGURATION REGISTER 0........ OMCR0 (08)H.....................34

VI.6 OUTPUT MULTIPLEX CONFIGURATION REGISTER 1........ OMCR1 (0A)H ....................34

VI.7 SWITCHING MATRIX CONFIGURATION REGISTER...........SMCR (0C)H.......................35

VI.8 CONNECTION MEMORY DATA REGISTER .........................CMDR (0E)H.......................37

VI.9 CONNECTION MEMORY ADDRESS REGISTER .................CMAR (10)H.......................41

VI.10 SEQUENCE FAULT COUNTER REGISTER .........................SFCR (12)H ........................45

VI.11 TIME SLOT ASSIGNER ADDRESS R EG IST ER 1.. ................TAAR1 (14) H......... .............45

VI.12 TIME SLOT ASSIGNER DATA REGISTER 1.........................TADR1 (16)H......................45

VI.13 HDLC TRANSMIT COMMAND REGISTER 1.........................HTCR1 (18)H......................46

VI.14 HDLC RECEIVE COMMAND REGISTER 1 ............................HRCR1 (1A)H .....................48

VI.15 ADDRESS FIELD RECOGNITION ADDRESS REGISTER 1.AFRAR1 (1C)H ...................50

VI.16 ADDRESS FIELD RECOGNITION DATA REGISTER 1......... AFRDR1 (1E)H...................50

VI.17 FILL CHARACTER REGISTER 1 ............................................FCR1 (20)H........................51

VI.18 GCI CHANNELS DEFINITION REGISTER 0 .........................GCIR0 (22)H.......................51

VI.19 GCI CHANNELS DEFINITION REGISTER 1..........................GCIR1 (24)H.......................51

VI.20 GCI CHANNELS DEFINITION REGISTER 2..........................GCIR2 (26)H.......................52

VI.21 GCI CHANNELS DEFINITION REGISTER 3..........................GCIR3 (28)H.......................52

VI.22 TRANSMIT COMMAND / INDICATE REGISTER ..................TCIR (2A)H.........................52

VI.23 TRANSMIT MONITOR ADDRESS REGISTER.......................TMAR (2C)H.......................53

VI.24 TRANSMIT MONITOR DATA REGISTER ..............................TMDR (2E)H.......................54

VI.25 TRANSMIT MONITOR INTERRUPT REGISTER....................TMIR (30)H .........................55

VI.26 MEMORY INTERFACE CONFIGURATION REGISTER......... MICR (32)H.........................55

VI.27 INITIATE BLOCK ADDRESS REGISTER 1 ...........................IBAR1 (34)H .......................56

VI.28 INTERRUPT QUEUE SIZE REGISTER ................................. IQSR (36)H.........................56

VI.29 INTERRUPT REGISTER ........................................................IR (38)H..............................57

VI.30 INTERRUPT MASK REGISTER ..............................................IMR (3A)H...........................58

VI.31 TIMER REGISTER 1 ...............................................................TIMR1 (3C)H ......................59

VI.32 TEST REGISTER....... .............................................................TR (3E)H.... .........................59

VI.33 GENERAL CONFIGURATION REGISTER 2..........................GCR2 (42)H........................60

VI.34 SPLIT FETCH MEMORY REGISTER.....................................SFMR (4E)H.......................61

VI.35 TIME SLOT ASSIGNER ADDRESS R EG IST ER 2.. ................TAAR2 (54) H......... .............62

VI.36 TIME SLOT ASSIGNER DATA REGISTER 2.........................TADR2 (56)H......................62

VI.37 HDLC TRANSMIT COMMAND REGISTER 2 ........................HTCR2 (58)H......................63

4/130

STLC5466

VI.38 HDLC RECEIVE COMMAND REGISTER 2 ...........................HRCR2 (5A)H.....................65

VI.39 ADDRESS FIELD RECOGNITION ADDRESS REGISTER 2 AFRAR2 (5C)H ...................67

VI.40 ADDRESS FIELD RECOGNITION DATA REGISTER 2......... AFRDR2 (5E)H...................67

VI.41 FILL CHARACTER REGISTER 2 ...........................................FCR2 (60)H........................68

VI.42 SDRAM MODE REGISTER.....................................................SDRAMR (72)H..................68

VI.43 INITIATE BLOCK ADDRESS REGISTER 2 ...........................IBAR2 (74)H .......................69

VI.44 TIMER REGISTER 2 ...............................................................TIMR2 (7C)H ......................70

VII EXTERNAL REGISTERS.....................................................................................................71

VII.1 INITIALIZATION BLOCK IN EXTERNAL MEMORY (IBA1 AND IBA2) 71

VII.2 RECEIVE DESCRIPTOR......................................................... 72

VII.2.1 Bits written by the Microprocessor only ...............................................................................72

VII.2.2 Bits written by the Rx DMAC only ........................................................................................72

VII.2.3 Receive Buff e r ......................................................................................................... ............73

VII.3 TRANSMIT DESCRIPTOR ...................................................... ............................................73

VII.3.1 Bits written by the Microprocessor only ...............................................................................73

VII.3.2 Bits written by the Tx DMAC only ........................................................................................74

VII.3.3 Transmit Buffer ....................................................................................................................74

VII.4 RECEIVE & TRANSMIT HDLC FRAME INTERRUPT ............ ............................................75

VII.5 RECEIVE COMMAND / INDICATE INTERRUPT.................... ............................................76

VII.5.1 Receive Command / Indicate Interrupt when TSV = 0 ... ......................................................76

VII.5.2 Receive Command / Indicate Interrupt when TSV = 1 ... ......................................................77

VII.6 RECEIVE MONITOR INTERRUPT......................................................................................77

VII.6.1 Receive Monitor Interrupt when TSV = 0 .............................................................................77

VII.6.2 Receive Monitor Interrupt when TSV = 1 .............................................................................78

VIII TQFP176 PACKAGE MECHANICAL DATA.......................................................................79

IX FIGURES AND TIMING........................................................................................................80

5/130

6/130

N.C

VSS12

TMS

TDI

TDO

TCK

VDD3

VSS3

NCS0

NCS1

INT0

INT1

SIZE0/NLDS/NLBA

SIZE1/NBHE/NUDS

NDSACK0/NDTACK

NDSACK1/READY

NAS/ALE

R/W / NW R

NDS/NRD/CLKOUT

MOD0

MOD1

MOD2

VDD4

VSS4

A0/AD0

A1/AD1

A2/AD2

A3/AD3

A4/AD4

A5/AD5

A6/AD6

A7/AD7

A8/AD8

A9/AD9

VDD5

VSS5

A10/AD10

A11/AD11

A12/AD12

A13/AD13

A14/AD14

A15/AD15

VDD13

N.C

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

44

N.C

41

42

43

NDIS/NCS2

NTRST

VDD12

NREADY

VSS13

A17

A16

N.C

92

91

90

89

40

DOUT7

A18

93

39

DOUT6

A19

94

38

DOUT5

A20

95

37

DOUT4

A21

96

36

DOUT3

A22

97

35

DOUT2

A23

98

33

34

DOUT0

DOUT1

VDD6

VSS6

100

99

31

32

VDD2

VSS2

D1

D0

102

101

29

30

DIN7

DIN8

D3

D2

104

103

27

28

DIN5

DIN6

D5

D4

106

105

25

26

DIN3

DIN4

D7

D6

108

107

23

24

DIN1

DIN2

D9

D8

110

109

20

21

22

FSCV

PSS

DIN0

STLC54 66

D12

D11

D10

113

112

111

19

FSCG

D13

114

18

FS

D14

115

16

17

VDD1

VSS1

VDD7

D15

117

116

14

15

FRAMEA

FRAMEB

VSS7

TRI

119

118

13

CLOCKB

TRO

120

12

CLOCKA

NWE

121

11

DCLK

NRAS

122

10

7

8

9

CB1

EC1

VCXO IN

VCXO OUT

UDQM

LDQM

NCE1

NCE0

126

125

124

123

4

5

6

MCLK

SFS

WDO

NCE3/ADM13

NCE2/ADM12

CB2

129

128

127

2

3

VSS15

NRESET

VDD14

EC2

131

130

1

N.C

N.C

132

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

N.C

VDD15

NTEST

VSS11

VDD11

DM15

DM14

DM13

DM12

DM11

DM10

DM9

DM8

DM7

DM6

DM5

VSS10

VDD10

DM4

DM3

DM2

DM1

DM0

DIN9

SCANM

NCAS

ADM11

ADM10

VSS9

VDD9

ADM9

ADM8

ADM7

ADM6

ADM5

ADM4

ADM3

ADM2

ADM1

ADM0

VSS8

VDD8

VSS14

N.C

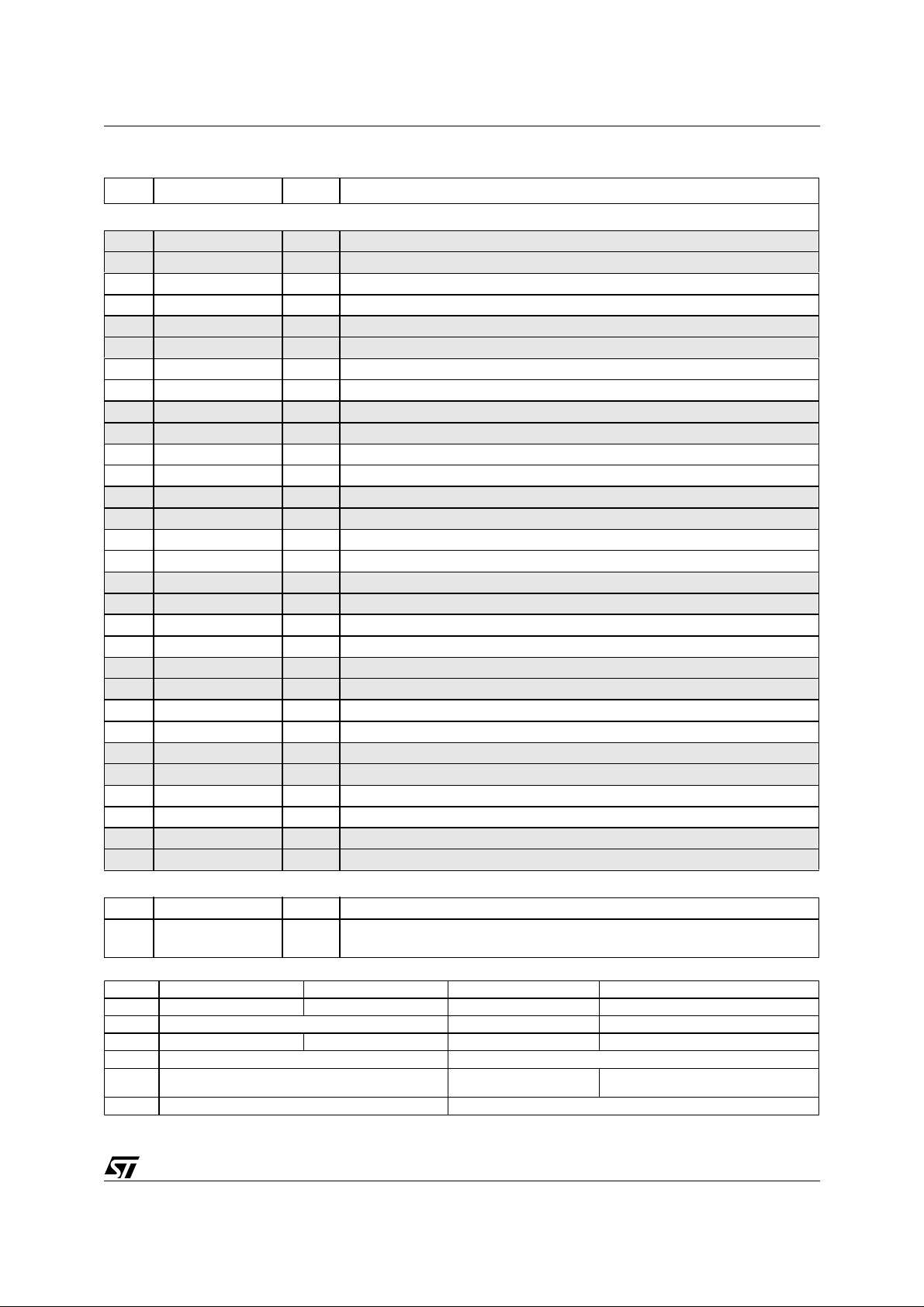

I - PIN INFORMATION

I.1 - Pin Connections

STLC5466

STLC5466

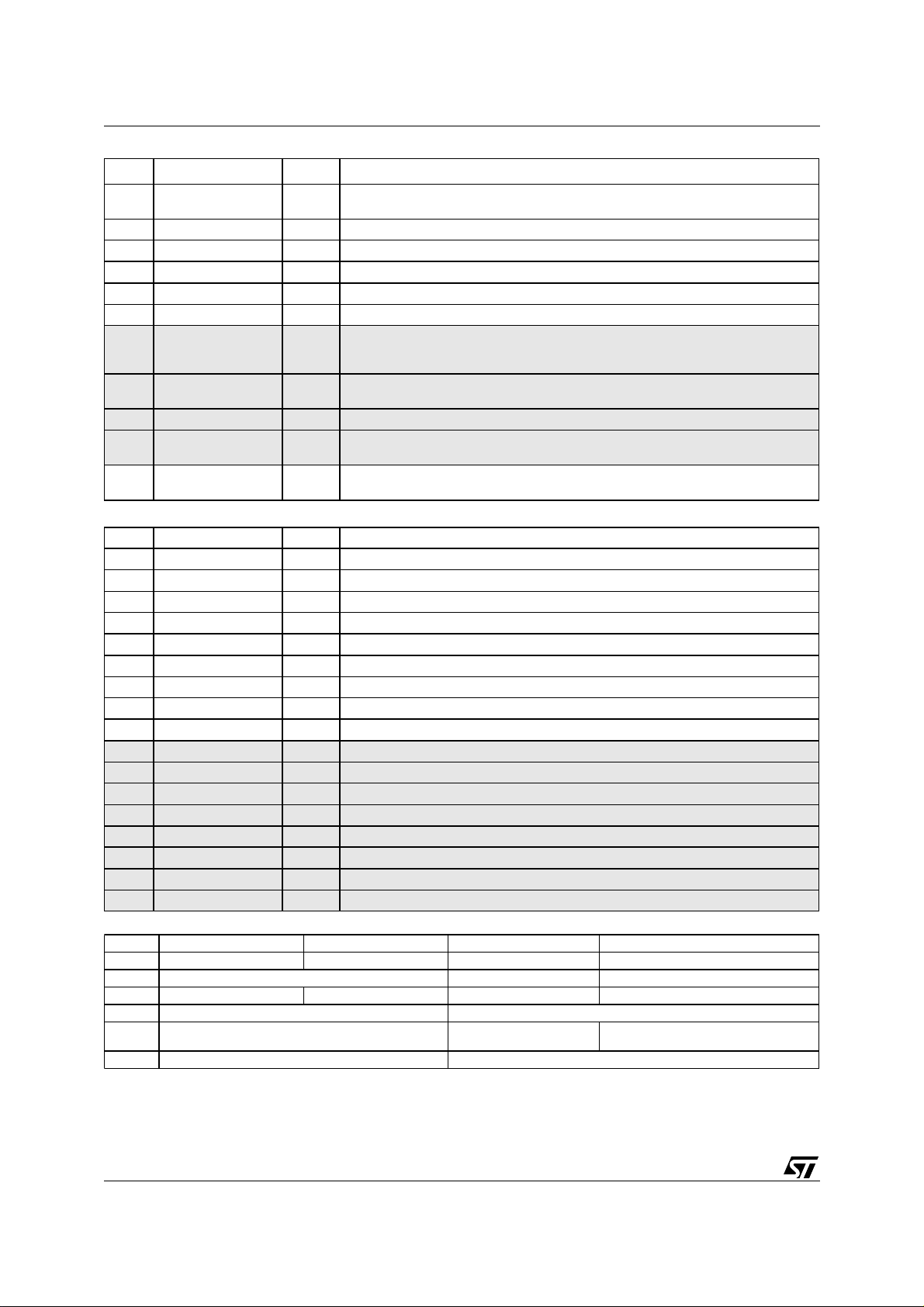

I.2 - Pin Description

Pin N° Symbol Type Function

30 POWER PINS (all the power and ground pins must be connected)

16 V

17 V

31 V

32 V

51 V

52 V

67 V

68 V

79 V

80 V

99 V

100 V

117 V

118 V

135 V

136 V

147 V

148 V

159 V

160 V

172 V

173 V

43 V

46 V

87 V

90 V

131 V

134 V

175 V

2 V

DD1

SS1

DD2

SS2

DD3

SS3

DD4

SS4

DD5

SS5

DD6

SS6

DD7

SS7

DD8

SS8

DD9

SS9

DD10

SS10

DD11

SS11

DD12

SS12

DD13

SS13

DD14

SS14

DD15

SS15

CLOCKS

4 MCLK I3_ft Master clock. This input can receive an external clock at 66, 50 or 33MHz.

5 SFS O3_ft Superframe Synchronisation.

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Power DC supply

Ground DC ground

Programmable signal from 250 microseconds to 15 seconds.

Type

TTL I1_ft = Input T T L I2_ft = I1_ft+pull up I3_ft = I1_ft+hysteresis I4_ft = I3_ft+pul l up

TTL I/O6 _ft = Input TTL/ Output T TL 6 m A I5_ft = I3_f t+pull down ;

TTL O3 _ft = Output TTL 3 mA O3T_ft = O3_ft+Tristate O6_ft = Output TTL 6mA

TTL O6D_ft = Output TTL 6mA, Open Drain O6DT_ft = Output TTL 6mA, Open Drain or Tristate

CMOS I/O8_fnt = Input TTL, /Output CMOS 8mA; O8T_fnt = Output CMOS

CMOS O4_fnt = Output CMOS 4mA

ft: five volts tolerant fnt: five volts not tolerant

8mA

I/O8 _fnt = Inpu t T TL, /Output CMO S

8mA

7/130

STLC5466

Pin N° Symbol Type Function

9 VCXO IN I3_ft VCXO input signal. This signal is compared to clock A(orB)

10 VCXO OUT O3_ft VCXO error signal. This pin delivers the result of the comparison.

12 CLOCKA I3_ft Input Clock A (4096kHz or 8192kHz)

13 CLOCKB I3_ft Input Clock B (4096kHz or 8192kHz)

14 FRAMEA I3_ft Clock A at 8kHz

15 FRAMEB I3_ft Clock B at 8kHz

11 DCLK O6_ft Data Clock issued from Input Clock A (or B). This clock is delivered by the cir-

19 FSCG O6_ft Frame synchronization for GCI at 8kHz.

20 FSCV* O6_ft Frame synchronization for V Star at 8kHz

18 FS I3_ft Frame synchronization.

21 PSS O3_ft Programmable synchronization Signal.

TIME DIVISION MULTIPLEXES (TDM)

22 DIN0 I3_ft TDM0 Data Input 0

23 DIN1 I3_ft TDM1 Data Input 1

24 DIN2 I3_ft TDM2 Data Input 2

25 DIN3 I3_ft TDM3 Data Input 3

26 DIN4 I3_ft TDM4 Data Input 4

27 DIN5 I3_ft TDM5 Data Input 5

28 DIN6 I3_ft TDM6 Data Input 6

29 DIN7 I3_ft TDM7 Data Input 7

30 DIN8 I3_ft TDM8 Data Input 8, Direct access to 1st 32 HDLC Controller

153 DIN9 I3_ft TDM9 Data Input 9, Direct access to 2nd 32 HDLC Controller

33 DOUT0 O6DT_ft TDM0 Data Output 0

34 DOUT1 O6DT_ft TDM1 Data Output 1

35 DOUT2 O6DT_ft TDM2 Data Output 2

36 DOUT3 O6DT_ft TDM3 Data Output 3

37 DOUT4 O6DT_ft TDM4 Data Output 4

38 DOUT5 O6DT_ft TDM5 Data Output5

39 DOUT6 O6DT_ft TDM6 Data Output6

40 DOUT7 O6DT_ft TDM7 Data Output 7

selected inside the

Multi-HDLC

.

cuit at 4096kHz (or 204 8kHz ). DOUT 0/7 are transm itted on th e rising ed ge of

this signal. DIN0/7 are sampled on the falling edge of this signal.

This clock is issued from FRAME A (or B).

This signal synchronizes DIN0/8 and DOUT0/7 and CB.

PSS is programmed by the PS bit of connection memory.

Type

TTL I1_ft = Input T T L I2_ft = I1_ft+pull up I3_ft = I1_ft+hysteresis I4_ft = I3_ft+pul l up

TTL I/O6 _ft = Input TTL/ Output T TL 6 m A I5_ft = I3_f t+pull down ;

TTL O3 _ft = Output TTL 3 mA O3T_ft = O3_ft+Tristate O6_ft = Output TTL 6mA

TTL O6D_ft = Output TTL 6mA, Open Drain O6DT_ft = Output TTL 6mA, Open Drain or Tristate

CMOS I/O8_fnt = Input TTL, /Output CMOS 8mA; O8T_fnt = Output CMOS

CMOS O4_fnt = Output CMOS 4mA

ft: five volts tolerant fnt: five volts not tolerant

8mA

I/O8 _fnt = Inpu t T TL, /Output CMO S

8mA

8/130

STLC5466

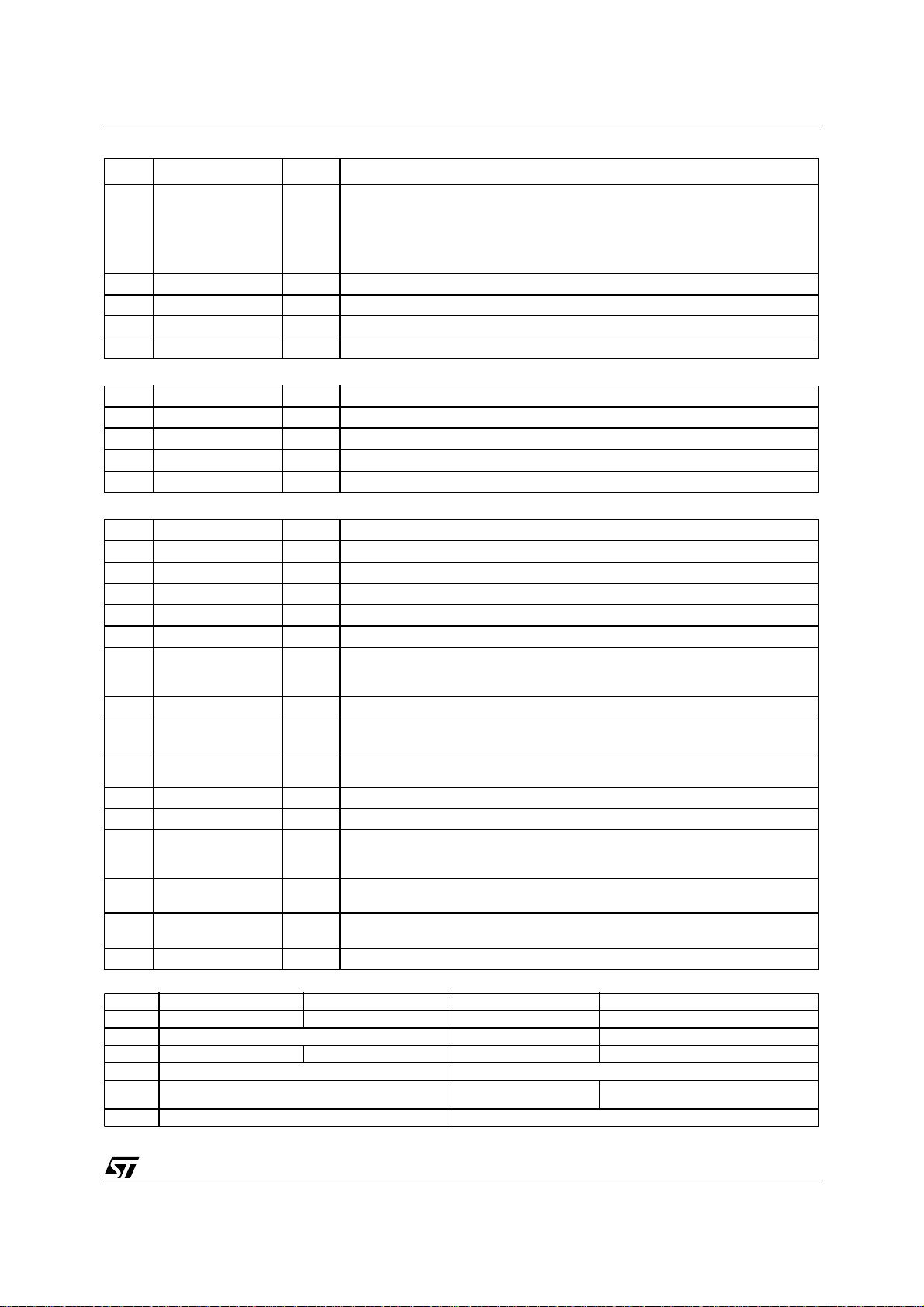

Pin N° Symbol Type Function

41 NDIS/NCS2 I 3_ft If 386EX interfa ce is not se lecte d: DO UT 0/ 7 Not Disab le. Wh en th is pin is at

7 CB1 O6D_ft Contention Bus (CSMA/CR) for 1st 32 HDLC Controller

8 EC1 I3_ft Echo for 1st 32 HDLC Controller. Wired at VSS if not used.

128 CB2 O6D_ft Contention Bus (CSMA/CR) for 2nd 32 HDLC Controller

130 EC2 I3_ft Echo for 2nd 32 HDLC Controller. Wired at V

BOUDARY SCAN

42 NTRST I4_ft Reset for boundary scan

47 TMS I2_ft Mode Selection for boundary scan

48 TDI I2_ft Input Data for boundary scan

49 TDO O3T_ft Output Data for boundary scan

50 TCK I4_ft Clock for boundary scan

MICROPROCESSOR INTERFACE

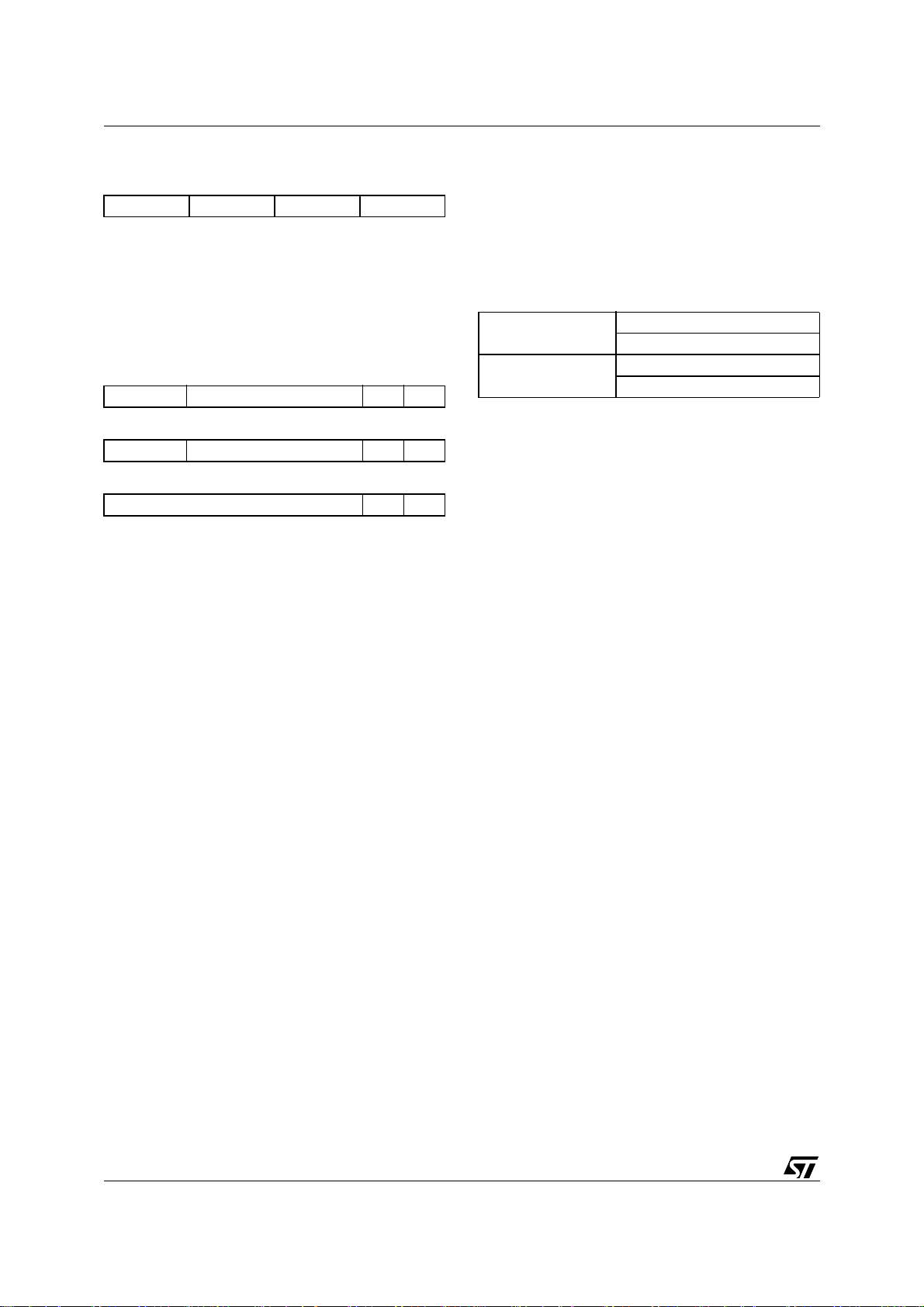

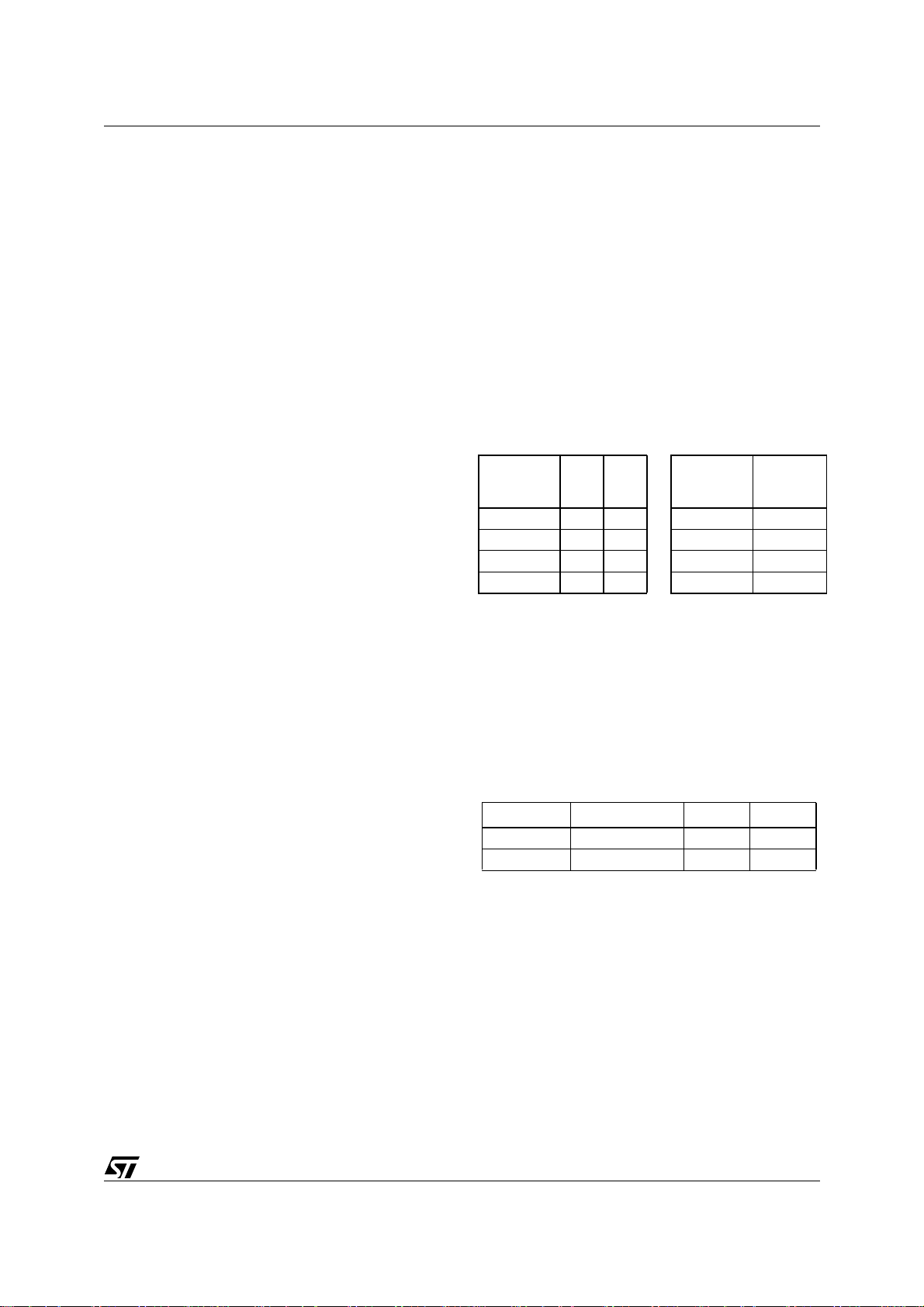

64 MOD0 I1_ft 1 1 0 0 1 1 0 0

65 MOD1 I1_ft 1 1 0 0 0 0 1 1

66 MOD2 I1_ft 01100110

3 NRESET I3_ft Circuit Reset

53 NCS0 I3_ft Chip Select 0: internal registers are selected

54 NCS1 I3_ft Chip Select 1: external memory is selected

55 INT0 O3_ft Interrupt generated by HDLC, RxC/I or RxMON. Active high.

56 I NT1 O3_ft Interrupt1.This pin goes to 5V whe n the selected clock A (or B) has disap-

6 WDO O3_ft Watch Dog Output.This pin goes to 5V during 250µs when the microprocessor

57 SIZE0/NLDS/NLBA I3_ft Transfer Size0 (68020)/Lower Data Stobe/Local Bus Access# when 386EX

58 SIZE1/NBHE/NUDS I3_ft Transfer Size1(68020)/Bus High Enable (Intel) / Upper Data Strobe (68000)

59 NDSACK0/

NDTACK/

NREADY

60 NDSACK1/

READY

61 NAS/

O6T_ft/

O6T_ft/

O6D_ft

O6T_ft

O6T_ft

I3_ft Address Strob e(Mot orola ) /

ALE/NADS

62 R/W / NWR I3_ft Read/Write (Motorola) / Write(Intel)

0V, the Data Output 0/7 are at high impedance. Wired at VDD if not used.

If 386EX interface is selected: NCS2 (Chip Select 2) equivalent to NCS1.

Chip Select 2: external memory is selected

During Chip select (NCS2=0), the output Ready (pin 59) is low impedance and

outside Chip select (NCS2=1), the output Ready is high impedance.

if not used.

SS

80C188 80C186 68000 68020 ST9 ST10 m ST10Nm 386EX

During Chip select (NCS1=0), the output Ready (pin 59) is low impedance and

outside Chip select (NCS1=1), the output Ready is high impedance.

peared; 250µs after reset this pin goes to 5V also if clock A is not present.

has not reset the Watch Dog during the programmable time.

Data Strobe, Acknowledge and Size0 (68020)/

Data Transfer Acknowledge (68000 and ST10)/

READY# (386EX)

Data Strobe, Acknowledge and Size1 (68020)/

Data Transfer Acknowledge (Intel)

Address Latch Enable(Intel) / Address Status 386EX

Type

TTL I1_ft = Input T T L I2_ft = I1_ft+pull up I3_ft = I1_ft+hysteresis I4_ft = I3_ft+pul l up

TTL I/O6 _ft = Input TTL/ Output T TL 6 m A I5_ft = I3_f t+pull down ;

TTL O3 _ft = Output TTL 3 mA O3T_ft = O3_ft+Tristate O6_ft = Output TTL 6mA

TTL O6D_ft = Output TTL 6mA, Open Drain O6DT_ft = Output TTL 6mA, Open Drain or Tristate

CMOS I/O8_fnt = Input TTL, /Output CMOS 8mA; O8T_fnt = Output CMOS

CMOS O4_fnt = Output CMOS 4mA

ft: five volts tolerant fnt: five volts not tolerant

8mA

I/O8 _fnt = Inpu t T TL, /Output CMO S

8mA

9/130

STLC5466

Pin N° Symbol Type Function

63 NDS/

NRD/CLKOUT

69 A0/AD0 I/O6_ft Address bit 0 (Motorola) / Address/Data bit 0 (Intel)

70 A1/AD1 I/O6_ft Address bit 1 (Motorola) / Address/Data bit 1 (Intel)

71 A2/AD2 I/O6_ft Address bit 2 (Motorola) / Address/Data bit 2 (Intel)

72 A3/AD3 I/O6_ft Address bit 3 (Motorola) / Address/Data bit 3 (Intel)

73 A4/AD4 I/O6_ft Address bit 4 (Motorola) / Address/Data bit 4 (Intel)

74 A5/AD5 I/O6_ft Address bit 5 (Motorola) / Address/Data bit 5 (Intel)

75 A6/AD6 I/O6_ft Address bit 6 (Motorola) / Address/Data bit 6 (Intel)

76 A7/AD7 I/O6_ft Address bit 7 (Motorola) / Address/Data bit 7 (Intel)

77 A8/AD8 I/O6_ft Address bit 8 (Motorola) / Address/Data bit 8 (Intel)

78 A9/AD9 I/O6_ft Address bit 9 (Motorola) / Address/Data bit 9 (Intel)

81 A10/AD10 I/O6_ft Address bit 10 (Motorola) / Address/Data bit 10 (Intel)

82 A11/AD11 I/O6_ft Address bit 11 (Motorola) / Address/Data bit 11 (Intel)

83 A12/AD12 I/O6_ft Address bit 12 (Motorola) / Address/Data bit 12 (Intel)

84 A13/AD13 I/O6_ft Address bit 13 (Motorola) / Address/Data bit 13 (Intel)

85 A14 /AD1 4 I/O6_ft Add ress bit14 (Moto rola) / Address/D ata bit 14 (Intel)

86 A15 /AD1 5 I/O6_ft Add ress bit15 (Moto rola) / Address/D ata bit 15 (Intel)

91 A 16 I1_ft Address bit16 from µP

92 A 17 I1_ft Address bit17 from µP

93 A 18 I1_ft Address bit18 from µP

94 A 19 I1_ft Address bit19 from µP

95 A20 I1_ft Address bit 20 from µP

96 A21 I1_ft Address bit 21 from µP

97 A22 I1_ft Address bit 22 from µP

98 A23 I1_ft Address bit 23 from µP

101 DO I/O6_ft Data bit 0 for µP if not multiplexed (see Note 1).

102 D1 I/O6_ft Data bit 1 for µP if not multiplexed

103 D2 I/O6_ft Data bit 2 for µP if not multiplexed

104 D3 I/O6_ft Data bit 3 for µP if not multiplexed

105 D4 I/O6_ft Data bit 4 for µP if not multiplexed

106 D5 I/O6_ft Data bit 5 for µP if not multiplexed

107 D6 I/O6_ft Data bit 6 for µP if not multiplexed

108 D7 I/O6_ft Data bit 7 for µP if not multiplexed

109 D8 I/O6_ft Data bit 8 for µP if not multiplexed

110 D9 I/O6_ft Data bit 9 for µP if not multiplexed

111 D10 I/O6_ft Data bit 10 for µP if not multiplexed

I3_ft Data Strobe (Motorola) External resistor at Vss if 68000/

Read Data (Intel)/CLKOUT if 386EX

Type

TTL I1_ft = Input T T L I2_ft = I1_ft+pull up I3_ft = I1_ft+hysteresis I4_ft = I3_ft+pul l up

TTL I/O6 _ft = Input TTL/ Output T TL 6 m A I5_ft = I3_f t+pull down ;

TTL O3 _ft = Output TTL 3 mA O3T_ft = O3_ft+Tristate O6_ft = Output TTL 6mA

TTL O6D_ft = Output TTL 6mA, Open Drain O6DT_ft = Output TTL 6mA, Open Drain or Tristate

CMOS I/O8_fnt = Input TTL, /Output CMOS 8mA; O8T_fnt = Output CMOS

CMOS O4_fnt = Output CMOS 4mA

ft: five volts tolerant fnt: five volts not tolerant

8mA

I/O8 _fnt = Inpu t T TL, /Output CMO S

8mA

10/130

Pin N° Symbol Type Function

112 D11 I/O6_ft Data bit 11 for µP if not multiplexed

113 D12 I/O6_ft Data bit 12 for µP if not multiplexed

114 D13 I/O6_ft Data bit 13 for µP if not multiplexed

115 D14 I/O6_ft Data bit 14 for µP if not multiplexed

116 D15 I/O6_ft Data bit 15 for µP if not multiplexed

MEMORY INTERFAC E

119 TRI I3_ft Token Ring Input (for use

120 TRO O4_fnt Token Ring Output (for use

Multi-HDLC

Multi-HDLC

s in cascade)

s in cascade)

121 NWE O8T_fnt Write Enable for SDRAM

122 NRAS O8T_fnt Row Address Strobe for SDRAM

123 NCE0 O8T_fnt Chip Select 0 for SDRAM

124 LDQM O8T_fnt Lower Data inputs/outputs mask enable for SDRAM

125 NCE1 O8T_fnt Chip Select 1 for SDRAM

126 UDQM O8T_fnt Upper Data inputs/outputs mask enable for SDRAM

127 NCE2/

ADM12

O8T_fnt Chip Select 2 for SDRAM/

Address bit 12 for 8Mx8 SDRAM circuit

129 NCE3/ADM13 O8T_fnt Chip Select 3 for SDRAM/Address bit 13 for 8Mx8 SDRAM circuit

137 ADM0 O8T_fnt Address bit 0 for SDRAM

138 ADM1 O8T_fnt Address bit 1 for SDRAM

139 ADM2 O8T_fnt Address bit 2 for SDRAM

140 ADM3 O8T_fnt Address bit 3 for SDRAM

141 ADM4 O8T_fnt Address bit 4 for SDRAM

142 ADM5 O8T_fnt Address bit 5 for SDRAM

143 ADM6 O8T_fnt Address bit 6 for SDRAM

144 ADM7 O8T_fnt Address bit 7 for SDRAM

145 ADM8 O8T_fnt Address bit 8 for SDRAM

146 ADM9 O8T_fnt Address bit 9 for SDRAM

149 ADM10 O8T_fnt Address bit 10 for SDRAM

150 ADM11 O8T_fnt Address bit 11 for SDRAM

151 NCAS O8T_fnt Column Address Strobe for SDRAM

152 SCANM I5_ft Scan mode reserved for device test

154 DM0 I/O8_fnt SDRAM Data bit 0

155 DM1 I/O8_fnt SDRAM Data bit 1

156 DM2 I/O8_fnt SDRAM Data bit 2

157 DM3 I/O8_fnt SDRAM Data bit 3

158 DM4 I/O8_fnt SDRAM Data bit 4

161 DM5 I/O8_fnt SDRAM Data bit 5

STLC5466

Type

TTL I1_ft = Input T T L I2_ft = I1_ft+pull up I3_ft = I1_ft+hysteresis I4_ft = I3_ft+pul l up

TTL I/O6 _ft = Input TTL/ Output T TL 6 m A I5_ft = I3_f t+pull down ;

TTL O3 _ft = Output TTL 3 mA O3T_ft = O3_ft+Tristate O6_ft = Output TTL 6mA

TTL O6D_ft = Output TTL 6mA, Open Drain O6DT_ft = Output TTL 6mA, Open Drain or Tristate

CMOS I/O8_fnt = Input TTL, /Output CMOS 8mA; O8T_fnt = Output CMOS

CMOS O4_fnt = Output CMOS 4mA

ft: five volts tolerant fnt: five volts not tolerant

8mA

I/O8 _fnt = Inpu t T TL, /Output CMO S

8mA

11/130

STLC5466

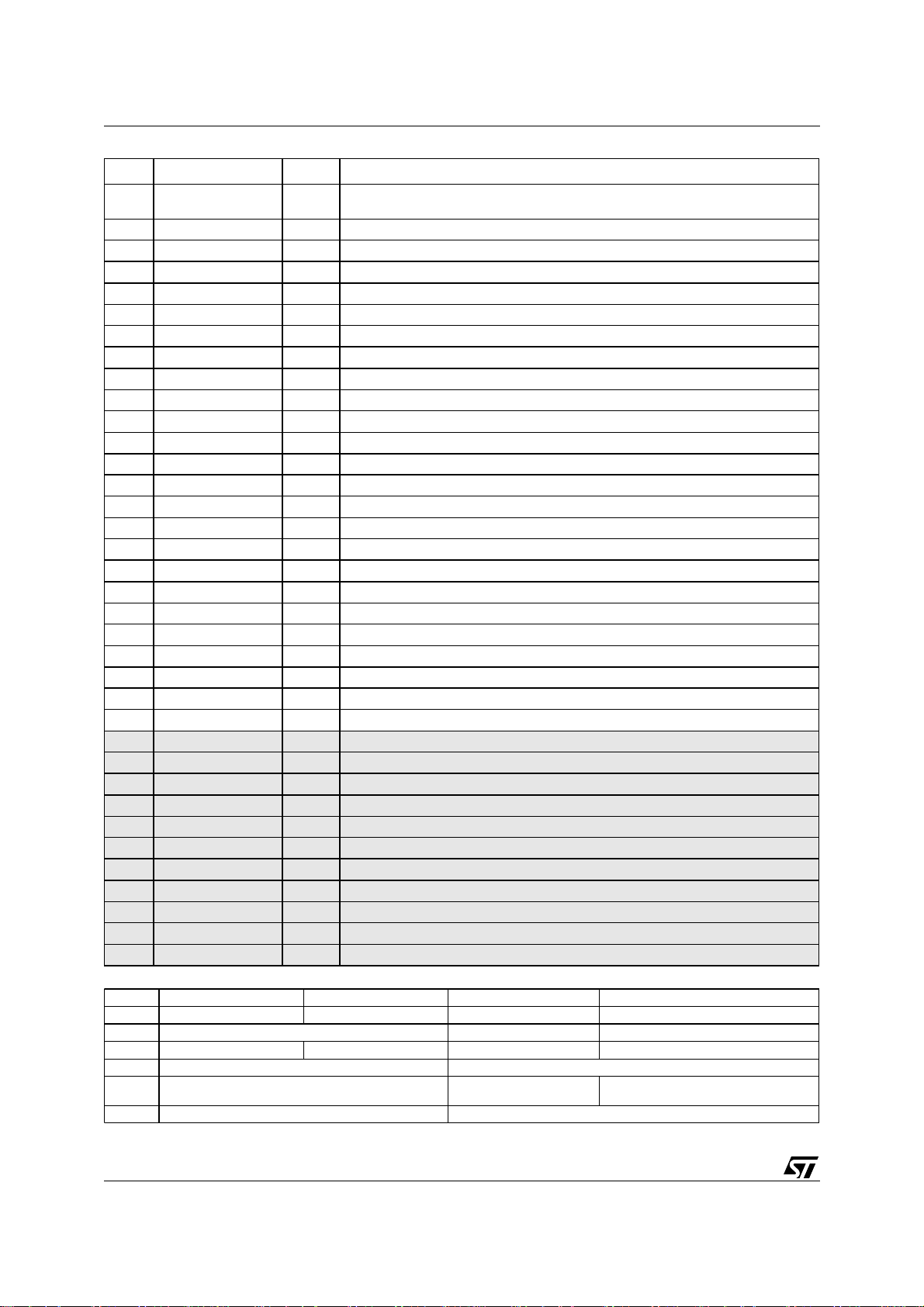

Pin N° Symbol Type Function

162 DM6 I/O8_fnt SDRAM Data bit 6

163 DM7 I/O8_fnt SDRAM Data bit 7

164 DM8 I/O8_fnt SDRAM Data bit 8

165 DM9 I/O8_fnt SDRAM Data bit 9

166 DM10 I/O8_fnt SDRAM Data bit 10

167 DM11 I/O8_fnt SDRAM Data bit 11

168 DM12 I/O8_fnt SDRAM Data bit 12

169 DM13 I/O8_fnt SDRAM Data bit 13

170 DM14 I/O8_fnt SDRAM Data bit 14

171 DM15 I/O8_fnt SDRAM Data bit 15

174 NTEST I2_ft Test Control. When this pin is at 0V each output is high impedance.

Type

TTL I1_ft = Input T T L I2_ft = I1_ft+pull up I3_ft = I1_ft+hysteresis I4_ft = I3_ft+pul l up

TTL I/O6 _ft = Input TTL/ Output T TL 6 m A I5_ft = I3_f t+pull down ;

TTL O3 _ft = Output TTL 3 mA O3T_ft = O3_ft+Tristate O6_ft = Output TTL 6mA

TTL O6D_ft = Output TTL 6mA, Open Drain O6DT_ft = Output TTL 6mA, Open Drain or Tristate

CMOS I/O8_fnt = Input TTL, /Output CMOS 8mA; O8T_fnt = Output CMOS

CMOS O4_fnt = Output CMOS 4mA

Notes : 1.

ft: five volts tolerant fnt: five volts not tolerant

8mA

D0/15 input/output pins must be connected to one single external pull up resistor if not used.

I/O8 _fnt = Inpu t T TL, /Output CMO S

8mA

I.1 - Pin Definition

The pins of the circuit are five volts tolerant except

the pins assigned to SDRAM interface.

I.1.1 - Input Pin Definition

I1_ft Input TTL, five volts tolerant

I2_ft Input 1 TTL + pull up, five volts tolerant

I3_ft Input 2 TTL + hysteresis, five volts tolerant

I4_ft Input 3 TTL + hysteresis +pull up, five volts tolerant.

I5_ft Input 4 TTL + hysteresis +pull down, five volts tolerant

I.1.2 - Output Pin Definition

O3_ft Output TTL 3 mA, five volts tolerant

O3T_ft Output TTL 3 mA, Tristate, five volts tolerant

O6_ft Output TTL 6mA, five volts tolerant

O6D_ft Output TTL 6mA,Open Drain, five volts tolerant

O6DT_ft Output TTL 6mA,Open Drain or Tristate. (Programmable pin), five volts tolerant

O4_fnt Output CMOS 4mA, five volts not tolerant

O8T_fnt Output CMOS 8mA, Tristate, five volts not tolerant

Moreover, each output is high impedance when the NTEST Pin is at 0 volt.

I.1.3 - Input/Output Pin Definition.

I/O6_ft Input TTL/ Ou tput TTL 6 mA five volts tolerant

I/O8_fnt Input TTL/Output CMOS 8mA, five volts not tolerant

12/130

STLC5466

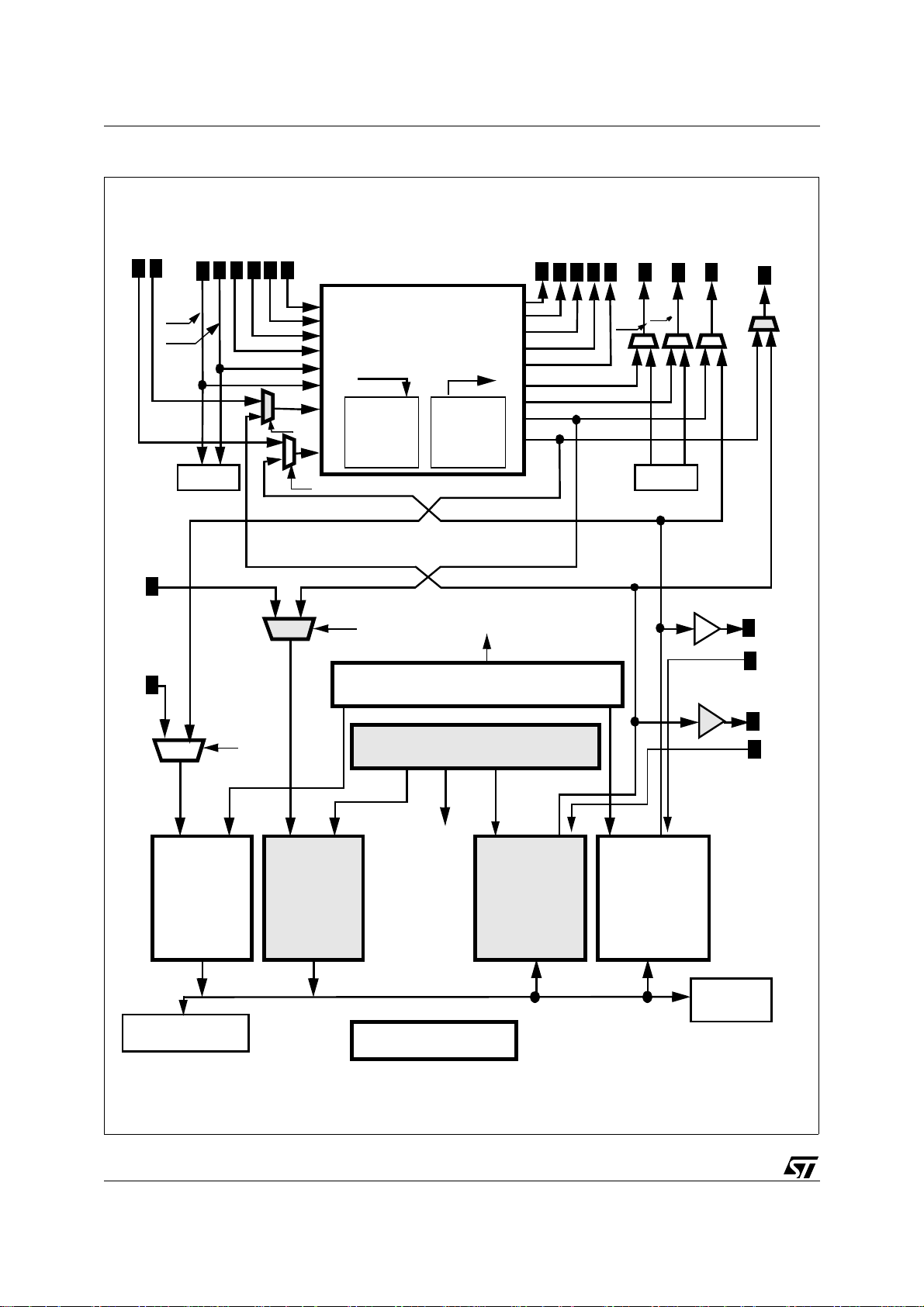

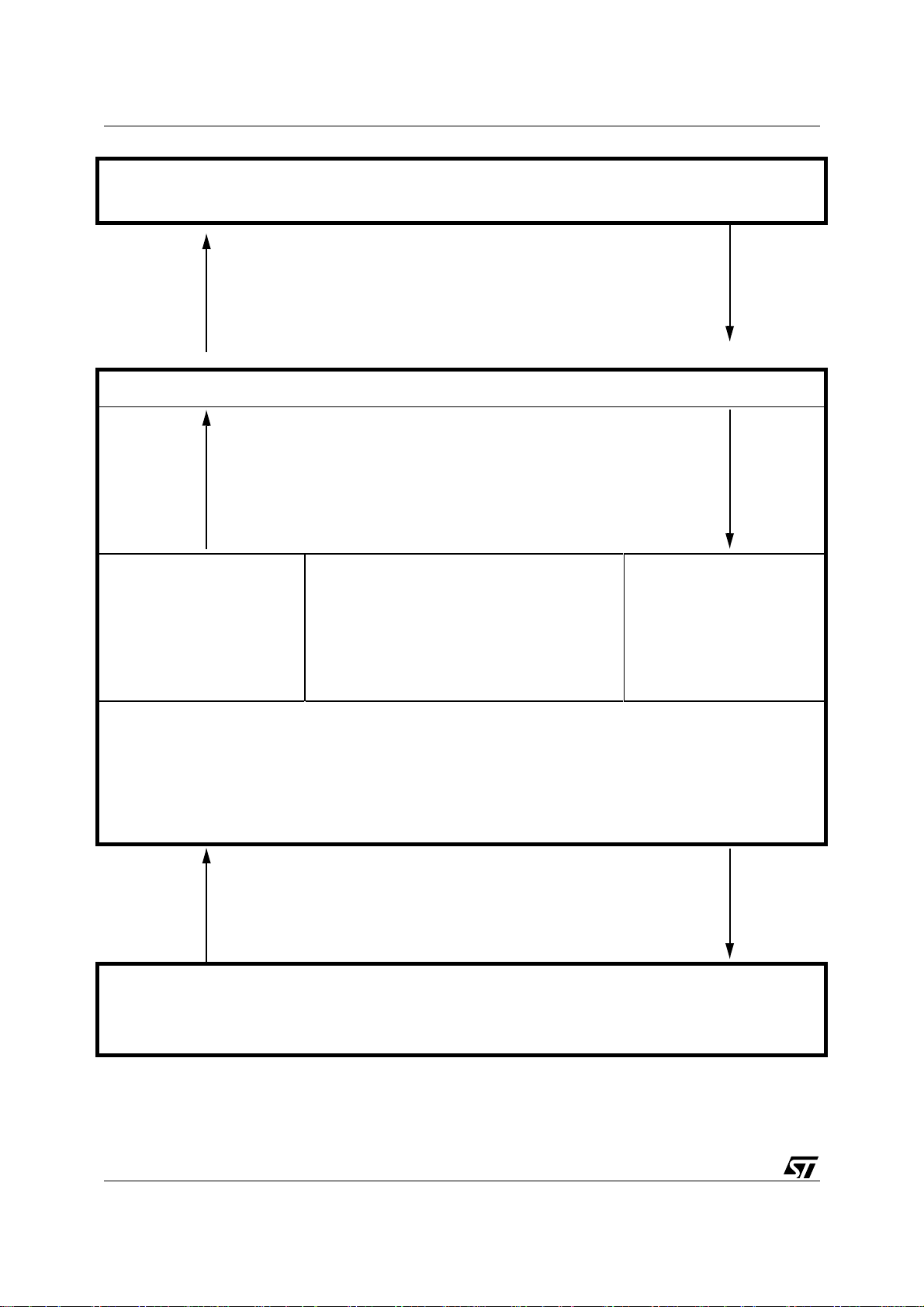

II - BLOCK DIAGRAM

The top level functionalities of

on the general block diagram.

There are:

– The switching ma trix,

– The 2 time slot assigners,

– The 2 x 32 HDLC transmitters with associ ated

DMA controllers,

– The 2 x 32 HDLC receivers with associated

DMA controllers,

– The 16 Command/Indicate and Monitor Channel

transmitters belonging to the two Gene ral Com ponent Interfaces (GCI),

– The 16 Command/Indicate and Monitor Channel

receivers belonging to the two General Component Interfaces (GCI),

– The Synchronous Dyn amic Mem ory interface,

– The microprocessor interface including Write

FIFO and Fetch Memory,

– The bus arbitration,

– The clock selection and time synchronization

function,

– The interrupt controller,

– The watchdog

III - FUNCTIONAL DESCRIPTION

III.1 - The Switching Matrix N x 64 KBits/S

III.1.1 - Function Description

The matrix performs a non-bl ock ing switc h of 256

time slots from 8 Input Time Division Multiplex

(TDM) at 2 Mbit/s to 8 output Time D ivision Mu ltiplex at 2 Mb it/s. A T DM at 2 Mbit/s consist s of 32

Time Slots (TS) at 64 kbit/s. One Time Division

Multiplex at 4 Mbit/s can take place of two Time Division Mu ltiplex at 2 Mbit/s . This TDM at 4 Mbi t/s

is composed of 64 Time Slots (TS) at 64 kbit/s.

The matrix is designed to sw itch a 64 k bit/ s cha nnel (Variable delay mode) or an hyperchannel of

data (Sequence integrity mode). So, it will both

provide minimum throughput switching delay for

voice applications and time slot sequence integrity

for data applications on a per channel basis.

The requirements of the Sequence I ntegrity (n*64

kbit/s) mode are the following:

All the time slots of a given input frame must be put

out during a same output frame.

The time slots of an hyperchannel (concatenation

of TS in the same TDM) are not crossed together

at output in different frames.

In variable delay mode, the time slot is put out as

soon as possible. (The delay is two or three time

slots minimum between input and output).

Multi-HDLC

appear

For test facilities, any time slot of an Output TDM

(OTDM) can be internally looped back into the

same Input TDM number (ITDM) at the same time

slot number.

A Pseudo Random Sequence Generator and a

Pseudo Random Sequence Analyser are implemented in the matrix. They allow the generation of

a sequence on a channel or on a hyperchannel, to

analyse it and verify its integrity after several

switching in the matrix or some passing of the sequence across different boards.

The Frame Signal (FS) synchronises ITDM and

OTDM but a programmable delay or advance can

be introduced separately on each ITDM and

OTDM (a half bit time, a bit time or two bit times).

An additional pin (PSS) permits the generation of

a programmable signa l composed of 256 bits per

frame at a bit rate of 2048 kbit/s. The programmation of this signal is performed thanks to PS bit of

Connection Memory.

An external pin (NDIS) asserts a h igh impedance

on all the TDM out puts of the matrix when active

(during the initialization of the board for example).

III.1.2 - Architecture of the Matrix

The matrix is essentially composed of buffer data

memories and a Connection Memory.

The received serial data is first converted to parallel by a serial to parallel converter and stored consecutively in a 256 position Buf fer Data Memory

(see Figure).

To satisfy the Seque nce Integrity (n*6 4 kbit/s) requirements, the data memory is built with an even

memory, an odd mem ory and an out put mem ory.

Two consecutive frames are stored alternatively in

the odd and even memory. During the time an input frame is stored, the one previously stored is

transferred into the output memory according to

the connection memory switching orders. A frame

later, the output memory is read and data is converted to serial and transferred to the output TDM.

III.1.3 - Connection Fu nct i on

Two types of connections are offered:

– unidirectional connec tion and

– bidirectional connec t ion.

An unidirectional connection makes only the

switch of an input t ime s lo t through an output one

whereas a bidirectional connection establishes the

link in the other direction too. So a double connection can be achieved by a single comm and (see

Figure).

13/130

STLC5466

Figure 1 :

DIN 6

DIN 7

GCI1

DIN 9

DIN 8

BLOCK DIAGRAM

DIN 3

DIN 4

DIN 5

GCI0

RX GCI

DIN 2

DIN 1

DIN 0

D6

SWIT C H ING MA TRIX

0

1

2

3

4

n x 64 kb/s

Scrambler/Descrambler

for 32 channels

5

Pseudo

6

Random

Sequence

7

Analyser

D7

V10b

FIRST TIME SLOT ASSIGNER

Pseudo

Random

Sequence

Generator

0

1

2

3

4

5

6

7

V10a

NDIS

DOUT 0

DOUT 1

DOUT 2

DOUT 3

GCI0

DOUT 4

GCI1

TX GCI

DOUT 6

DOUT 5

V10a

DOUT 7

V10b

CB1

EC1

CB2

FIRST

32 RX HDLC

with Address

Recognition

32 RX DMAC

Microprocessor

interface

14/130

V10a

SECOND

32 RX HDLC

with Address

Recognition

32 RX DMAC

SECOND TIME SLOT ASSIGNER

V10b

SECOND

32 TX HDLC

with C SMA CR

for Contention

Bus

32 TX DMAC

Internal Bus

BUS ARBITRATION

EC2

FIRST

32 TX HDLC

with CSMA CR

for Contention

Bus

32 TX DMAC

SDRAM

Controller

V10a, bit V10 of TADR1

V10b, bit V10 of TADR2

D6, bit of GCR2

D7, bit of GCR1

STLC5466

III.1.4 - Loop Back Function

Any time slot of an Output TDM can be internally

looped back on the t ime slot wh ich has the same

TDM number and the same TS number

(OTDMi, TSj) ----> (ITDMi, TSj).

In the case of a bidirect ional connection, onl y the

one specified by the microprocessor is concerned

by the loop back (see Figure).

III.1.5 - Delay through the Matrix

III.1.5.1 - Variable Delay Mode

In the variable delay mode, the delay through the

matrix depends on t he relat ive posi tions of t he i nput and output time slots in the frame.

So, some limits are fixed:

– the maximum del ay is a frame + 2 time slots,

– the minimum delay is programmable.

Three time slots if IMTD = 1, in this case n = 2 in

the formula hereafter or

two time slots if IMTD = 0, in this case n = 1 in

the same formula (see Paragraph “Switching

Matrix Configuration Register SMCR (0C)

”).

H

All the possibilities can be ranked in three cases:

a) If OTSy > ITSx + n then the variable delay is:

OTSy - ITSx Time slots

b) If ITSx

<

OTSy < ITSx+n then the variable delay

is:

OTSy - ITSx + 32 Time slots

c) OTSy < ITSx then the variable delay is:

32 - (ITSx - OTSy) Time slots.

N.B. Rule b) and rule c) are identical.

For n = 1 and n = 2, (see Figure).

III.1.5.2 - Sequence Integrity Mode

In the sequence integrity mode (SI = 1, bit located

in the Connection Memory), the input time slots

are put out 2 frames later (see Figure). In this

case, the delay is defined by a single expression:

Constant Delay = (32 - ITSx) + 32 + OTSy

So, the delay in sequence i ntegrity mode varies

from 33 to 95 time slots.

III.1.6 - Connection Memory

III.1.6.1 - Description

The connection memory is composed of 256 locations addressed by the number of OTDM and T S

(8x32).

Each location permits:

– to connect each input time slot to one output

time slot (If two or more output time slots are

connected to the same input time slot number,

there is broadcasting).

– to select the variable delay mode or the se-

quence integrity mode for any time slot.

– to loop back an output time slot. In this case the

contents of an i nput time slot (ITSx, ITDMp) is

the same as the output time slot (OTSx, OTDMp).

– to output the contents of the corresponding con-

nection memory instead of the data which has

been stored in data memory.

– to output the sequenc e of the pseudo random

sequence generator on an output time slot: a

pseudo random sequence can be inserted in

one or several time slots (hyperchannel) of the

same Output T DM; this insertion must be enabled by the microprocessor in the configuration

register of the matrix.

– to define the source of a sequence by the pseu-

do random sequence analyser: a pseudo random sequence can be extracted from one or

several time slots (hyperchannel) of the same

Input TDM and rout ed to the analyser; this extraction can be en abled by the microprocessor

in the configuration register of the m atrix (SMCR).

– to ass ert a high impedance level on an output

time slot (disconnection).

– to deliver a programmable 256-bit sequence

during 125 microseconds on the Programmable

synchronization Signal pin (PSS).

III.1.6.2 - Access to Connection Memory

Supposing that the Switching Matrix Configuration

Register (SMCR) has been already written by t he

microprocessor, it is possi ble to access to the connection memory from microprocessor with the

help of two registers:

– Connection Memory Data Register (CMDR) and

– Connection Memory Address Register (CMAR).

III.1.6.3 - Access to Data Memory

To extract the contents of the data memory it is

possible to read the data memory from microprocessor with the help of the two registers:

– Connection Memory Data Register (CMDR) and

– Connection Memory Address Register (CMAR).

III.1.7 - Switching at 32 Kbit/s

Four TDMs can be programmed individually to

carry 64 channels at 32 Kbit/s (only if these TDMs

are at 2 Mbit/s).

Two bits (SW0/1) located in SMCR define the type

of channels of two couples of TDMs.

SW0 defines TDM0 and TDM4 (GCI0) and SW1

defines TDM1 and TDM5 (GCI1).

If TDM0 or/and TDM1 carry 64 channels at 32

15/130

STLC5466

Kbit/s then TDM2 or/and TDM3 are not available

externally they are used internally to perform the

function.

See figure: Downstream switching at 32 kb/s.

See figure: Upstream switching at 32 kb/s.

III.1.8 - Switching at 16 Kbit/s

The TDM4 and TDM5 can be GCI multiplexes.

Each GCI multiplex comprises 8 GCI channels.

Each GCI channel comprises one D channel at 16

Kbit/s. See figure: GCI channel definition, GCI

Synchro signal delivered by the Multi-HDLC

It is possible to switch the contents of 16 D channels from the 16 GCI channels to 4 timeslots of the

256 output timeslots.

In the other di rection the cont ents of an sel ected

timeslot is automatically switched to 4 D channels

at 16 Kbit/s.

See Connection Memory Data Register CMDR

(0E)H.

III.2 - HDLC CONTROLLER

III.2.1 - Function description

Two independent HDLC controllers allow to process 64 channels.

Each internal HDLC controller can run up to 32

channels in a conventional HDLC mode or in a

transparent (non-HDLC) mode (configurable per

channel).

Each channel bit rate is programmable from 4kbit/

s to 64kbit/s. All the configurations are also possible from 32 cha nnels (from 4 to 6 4 kbit/s) to one

channel at 2 Mbit/s.

– First HDLC controller

In reception for the first HDL C cont roller, the co ntents of each time slot can directly come from the

input TDM DIN8 (direct H DLC Input) or from a ny

other TDM input after switching t owards the output

7 of the matrix (configurable per time slot).

In transmission, the HDLC frames are sent on the

output DOUT6 and on the output CB1 (with or

without contention mechanism), or are switched

tow ar ds th e ot her TD M out put vi a th e in put 7 of th e

matrix.

– Second HDLC controller

In reception for the second HDLC c ontroller, the

contents of each time slot can directly com e from

the input TDM DIN9 (direct HDLC Input) or from

any other TDM input after switching towards the

output 6 of the matrix (configurable per time slot).

In transmission, the HDLC frames are sent on the

output DOUT7 and on the output CB2 (with or

without contention mechanism), or are switched

towards the other TDM output via the input 6 of the

matrix .

III.2.1.1 - Format of the HDLC Frame

The format of an HDLC frame is the s ame in receive and transmit direction and shown here after.

III.2.1.2 - Composition of an HDLC Frame

Opening Flag

Address Field (first byte)

Address Field (second byte)

Command Field (first byte)

Command Field (second byte)

Data (first byte)

Data (optional)

Data (last byte)

FCS (first byte)

FCS (second byte)

Closing Flag

– Opening Fl ag

– One or two bytes for address recognition (recep-

tion) and insertion (transmission)

– Data bytes with bit stuffing

– Frame Check S equence: CRC with polynomial

G(x) = x

16

+x12+x5+1

– Closing Flag.

III.2.1.3 - Description and Functions of the

HDLC Bytes

–FLAG

The binary sequence 01111110 m arks the be-

ginning and the end of the HDLC Frame.

Note: In reception, three possible flag configura-

tion are allowed and correctly detected:

- two normal consecutive flags:

...01111110 01111110...

- two consecutive flags with a “0” common:

...011111101111110...

- a global common flag:...01111110...

this flag is the closing flag for the current frame

and the opening flag for the next frame

– ABORT

The binary sequence 11111 11 marks an Abort

command.

In reception, seven consecutive 1’s, inside a

message, are detected as an abort command

and generates an interrupt to the host.

In transmit direction, an abort is sent upon com-

mand of the micro-processor. No ending flag is

expected after the abort command.

16/130

STLC5466

– BIT STUFFING AND UNSTUFFING

This operation is done to avoid the c on fusio n of

a data byte with a flag.

In transmission, if five consecutive 1’s appear in

the serial stream being transmitted, a zero is automatically inserted (bit stuffing) after the fifth

“1”.

In reception, if five consecutive “1” followed by a

zero are received, the “0” is assumed to have

been inserted and is automatically deleted (bit

unstuffing).

– FRAME CHECK SEQUENCE

The Frame Check Sequence is calculated according to the recommendation Q921 of the

CCITT.

– ADDRESS RECOGNITION

In the frame, one or two bytes are transmitted to

indicate the destination of the message. Two

types of addresses are possible:

- a specific destination address

- a broadcast address.

In reception, the controller compares the receive

addresses to internal registers, which contain

the address message. 4 bits in the receive command register (HRCR) inform the receiver of

which registers, it has to take into account for the

com parison. The rece iver compar es th e two address bytes of the message to the specific board

address and the broadcast address. Upon an

address match, the address and the data following are written to the data buffers ; upon an address mismatch, the frame is ignored. So, it

authorizes the filtering of the messages. If no

comparison is specified, each frame is received

whatever its address field.

In Transmission, the controller sends t he frame

including the destination or b roadcast addresses.

III.2.2 - CSMA/CR Capability

An HDLC channel can come in and go out by any

TDM input on the matrix.

For time constraints, direct HDLC Access is

achieved by the input TDM (DIN 8 for the first

HDLC controller and DIN9 for the second HDLC

controller) and the output TDM (DOUT6 for the

first and DOUT7 for the second HDLC controller).

In transmission, a time slot of a TDM can be

shared between different s ources in Multi-point to

point configuration (different subscriber’s boards

for example). The arbit ratio n system is the CSMA/

CR (Carrier Sense Multiple access with Contention Resolution).

The contention is resolved by a bus connected to

the CB1 pin (Contention Bus) for t he first HDLC

controller and CB2 pin for the second HDLC con-

troller. These two bus are respe ctively a 2Mbit/s

wire line common to all the potential sources.

If the first HDLC controller (or the second) has obtained the access t o the bu s, the data to transmit

is sent simultaneously on the CB1 line (or the CB2

line) and the output TDM. The result of the contention is read back on the Echo line (EC1o r EC2). If

a collision is detected, the transmission is stopped

immediately. A contention on a bit basis is so

achieved. Each message to be sent with CSMA/

CR has a priority class (PRI = 8, 10) indicated by

the Transmit Descriptor and some rules are implemented to arbitrate the access to the line. The

CSMA/CR Algorithm is given. Whe n a request to

send a message occurs, the transmitter determines if the shared channel is free. The

HDLC

listens to the Echo line. If C or more consecutive “1” are detected (C depending on the message’s priority), the

message. Each bit sent is sampled back and compared with the original value to send. If a bit is different, the transmission is instantaneously

stopped (before the end of this bit time) and will restart as soon as the

channel is free without interrupting the microprocessor.

After a successful transmi ssion of a message, a

programmable pen alty PEN(1 or 2) is applied to

the transmitter. It guarantees that the same transmitter will not take the b us another time b efore a

transmitter which has to send a message of same

priority.

In case of a collision, the frame which has been

aborted is automatically retransmitted by the DMA

controller without warning the microprocessor of

this collision. The frame can be located in several

buffers in external memory. The collision can be

detected from the second bit of the opening frame

to the last but one bit of the closing frame.

III.2.3 - Ti m e Slot Assigner Memory

Each HDLC channel is bidirectional and is defined

by two Time Slot Assigners (TSA).

TSA is a memory of 32 words (one per phys ical

Time Slot) where all of the 32 input and output time

slots of the HDLC controllers can be associated to

logical HDLC channels. Super channels are created by assigning the same logical chann el num ber

to several physical time slot s.

The following features are programmed for each

HDLC time slot:

– Time slot used or not

– One logical channel number

– Its so u r ce:

- DIN 8 or the output 7 of the matrix for the first

Time Slot Assigner

Multi-H DLC

Multi-HDLC

begins to send its

will detect that the

Multi-

17/130

STLC5466

- DIN 9 or the output 6 of the matrix for the second Time Slot Assigner.

– Its bit rate and conc erned bit s (4k bit/s to 64kbit /

s). 4kbit/s correspond to one bit transmitted

each two frames. This bit is repeated twice in

transmission. This bit must be present in two

consecutive frames in reception.

– Its destination for the first Time Slot Assigner:

- direct output on DOUT6

- direct output on DOUT6 and on the Contention

Bus (CB1)

- on another OTDM via input 7 of the matrix and

on the Contention Bus (CB1)

– Its destination for the second Time Slot Assig n-

er:

- direct output on DOUT7

- direct output on DOUT7 and on the Contention

Bus (CB2)

- on another OTDM via input 6 of the matrix and

on the Contention Bus (CB2)

III.2.4 - Data Storage Structure

Data associated with each Rx and Tx HDLC channel is stored in external memory; The data transfers between the HDLC controllers and m emory

are ensured by 2*32 DMAC (Direct Memory Access Controller) in reception and 2*32 DMA C in

transmission.

The storage structure chosen i n bot h di rections is

composed of one circular queue of buffers per

channel. In such a queue, each data buffer is

pointed to by a Descriptor located in external

memory too. The main information contained in

the Descriptor is the address of the Data Buf fer, its

length and the address of the next Descriptor; so

the descriptors can be linked together.

This struct ur e allow s to:

– Store receive frames of variable and unknown

length

– Read transmit frames stored in external memory

by the host

– Easily perform the frame relay function.

III.2.4.1 - Reception

At the initialization of the application, the host has

to prepare two Initialization Block registers. Each

Initialization Block located in shared memory contains the first receive buffer descriptor address for

each channel, and the receive circular queues. At

the opening of a receive channel, the DMA controller reads the address of the first buffer descriptor corresponding to this channel in the

initialization Block. Then, the data transfer can occur without intervention of the processor.

A new HDLC frame always begins in a new buffer.

A long frame can be split between several buffers

if the buffer size is not sufficient. All the information

concerning the fram e a nd its l ocatio n in the c ircular queue is included in the Receive Buffer Descriptor:

– The Receive Buffer Address (RBA),

– The size of the receive buffer (SOB),

– The number of bytes written into the buffer

(NBR),

– The Next Receive Descriptor Address (NRDA),

– The status concerning the receive frame,

– The control of the queue.

III.2.4.2 - Transmission

In transmission, the data is manage d by a sim ilar

structure as in reception

By the same way, a frame can be split up between

consecutive transmit buffers.

The main information contained in the Transmit

Desc rip t or ar e:

– transmit buffer address (TBA),

– number of bytes to transmit (NBT) concerning

the buffer,

– next transmit descriptor address (NTDA),

– status of the frame after transmission,

– control bit of the queue,

– CSMA/CR priority (8 or 10).

III.2.4.3 - Frame Relay

The principle of the frame relay is to transmit a

frame which has been received without treatment.

A new heading is just added. This will be easily

achieved, taking into account that the queue structure allows the transmission of a frame s plit between several buffers.

III.2.5 - Transparent Modes

In the transparent mode, the

data in a completely transparent manner without

performing any bit manipulation or Flag insertion.

The transparent mode is per byte function; the

channel used for this mode is n*64 kb/s mandatory.

Two transparent modes are offered:

– First mode: for the receive channels, the

HDLC

continu ously w rites rece ived b ytes (from

the received timeslot) into the external memory

as specified in the current receive descriptor

without taking into account the Fill Character

Register.

– Second mo de: the Fill Character Register spec-

ifies the “fill c ha ra c te r” w hic h m u st be tak en int o

account. In reception, the “fill character” is de-

Multi-HDLC

transmits

Multi-

18/130

STLC5466

tected in each timeslot and will not be transferred to the external memory. The detection of

“Fill character” marks the end of a message and

generates an interrupt if BINT=1). When the “Fill

character” is not detected a new message is re-

ceiving.

As for the HDLC mode the correspondence between the physical time slot and the logical channel is fully defined in the two Time Slot Assigners

(Time slot used or not used, logical channel

number, source, destination).

III.2.6 - Command of the HDLC Channels

The microprocessor is able to control each HDLC

receive and transmit channel. Some of the com mands are specific to the transmission or t he reception but others are identical.

III.2.6.1 - Reception Control

– The configuration of the controller operating

mode is: HDLC mode or Transparent mode.

– The control of the controller: START, HALT,

CONTINUE, ABORT.

START: On a start comm and, the RxDM A con-

troller reads the address of the first descriptor in

the initialization block memory and is ready to

receive a frame.

HALT: For overloading reasons, the microproc-

essor can decide to halt the reception. The DMA

controller finishes transfer of the current frame

to external memory and stops. The channel can

be restarted on CONTINUE command.

CONTINUE: The reception restarts in the next

descriptor.

ABORT: On an abort command, the reception is

instantaneously stopped. The channel can be

restarted on a START or CONTINUE command.

– Reception of FLAG (01111110) or IDLE

(11111111) between Frames.

– Address recognition. The microprocessor de-

fines the addresses that the Rx controller has to

take into account.

– In transparent mode: “fill character” register is

selected or not.

III.2.6.2 - Transmission Control

– The configuration of the controller operating

mode is: HDLC mode or Transparent mode.

– The control of the controller: START, HALT,

CONTINUE, ABORT.

START: On a start comm and, t he Tx DM A controller reads the address of the first descriptor in

the initialization block memory and tries to transmit the first frame if End Of Queue is not at “1”.

HALT: The transmitter finishes to send the current frame and stops.The channel can be restarted on a CONTINUE command.

CONTINUE: if the CONTINUE command occurs

after HALT command, the HDLC Transmitter restarts by transmitting t he next bu ffer as sociat ed

to the next descriptor.

If the CONTINUE command occurs after an

ABORT command which has occurred during a

frame, the HDLC transmitter restarts by transmitting the frame which has been effectively

aborted by the microprocessor.

ABORT: On an abort comm and, the transmission of the current frame is instantaneously

stopped, an ABORT sequence “1111111” is

sent, followed by IDLE or FLAG bytes. The

channel can be restarted on a START or CONTINUE command.

– Transmission of FLAG (01111110) or IDLE

(111111111) between frames can be selected.

– CRC can be generat ed or no t. If the CRC is not

generated by the HDLC Controller, it must be located in the shared memory.

– In transparent mode: “fill character” register can

be selected or not.

III.3 - C/I and Monitor

III.3.1 - Function Description

The

Multi-HDLC

is able to operate both GCI and

V* links. The TDM DIN/DOUT 4 and 5 are internally connected to the CI and Monitor receivers/transmitters. Since the controllers handle up to 16CI

and 16 Monitor channels simultaneously, the

ti-HDLC

The

can manage up to 16 level 1 circuits.

Multi-H D L C

can be used to support the CI and

Mul-

monitor channels based on the following protocols:

– ISDN V* protocol

– ISDN GCI protocol

– Analog GCI protocol.

III.3.2 - GCI and V* Protocol

A TDM can carry 8 GCI channels or V* channels.

The monitor and S/C bytes always stand at the

same position in the TDM in both cases.

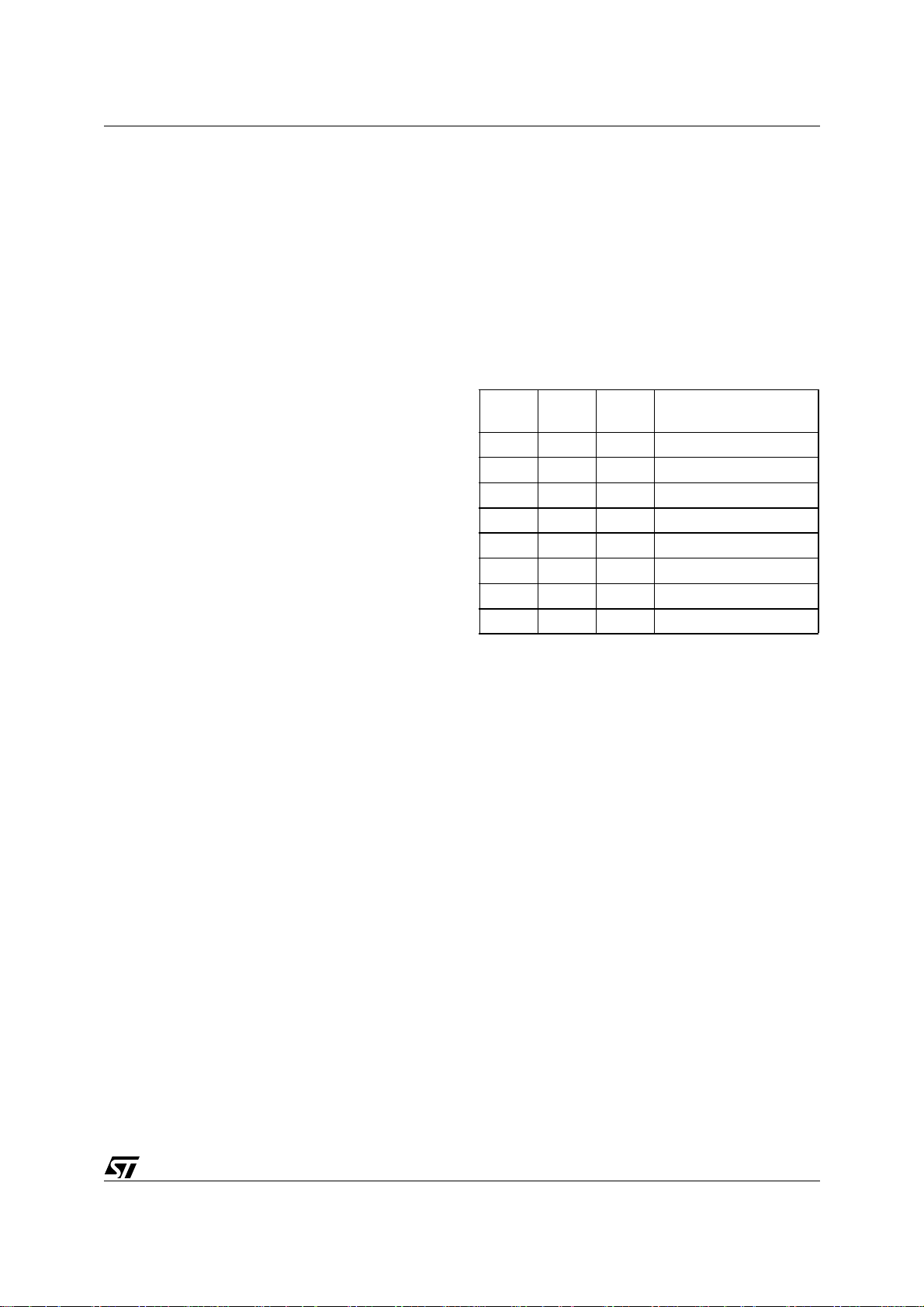

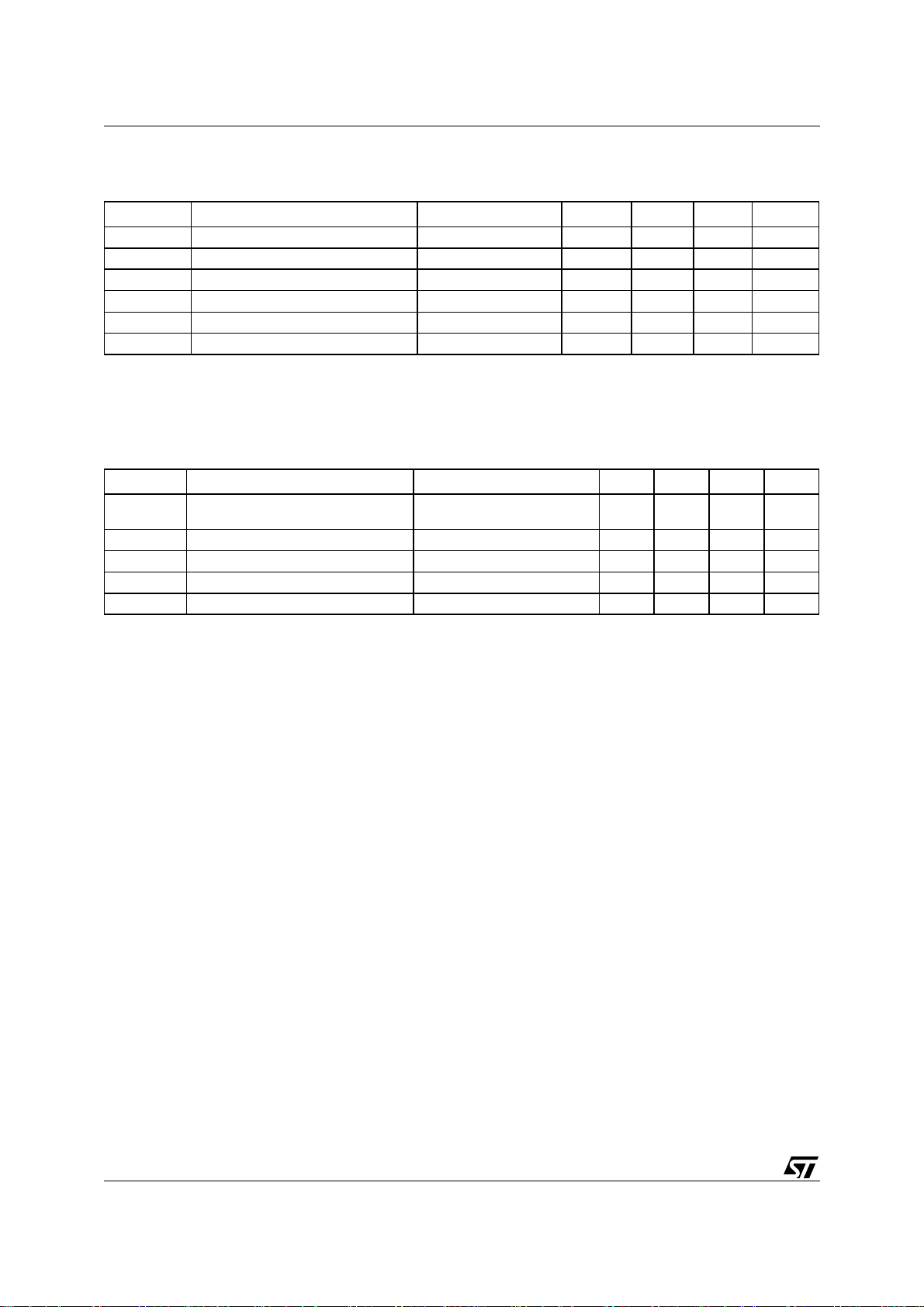

CGI Channel 0

TS0 TS1 TS2 TS3 TS28 TS29 TS30 TS31

B1 B2 MON S/C B1 B2 MON S/C

CGI Channel 1 to Channel 6

CGI Channel 7

19/130

STLC5466

The GCI or V* channels are composed of 4 bytes

and have both the same general structure.

B1 B2 MON S/C

B1, B2 : B ytes of data. Those bytes are not af-

fected by the monitor and CI protocols.

MON : Monitor channel for operation and

maintenance information.

S/C : Signalling and control information.

Only Monitor hands hakes and S/C bytes are dif-

ferent in the three protocols:

ISDN V* S/C byte

D 2 bits C/I 4 bits T E

ISDN GCI S/C byte

D 2 bits C/I 4 bits A E

Analog GCI S/C byte

C/I 6 bits A E

CI : The Comm and/Indicate channel is used for

activation/deactivation of lines and control

functions.

D : These 2 bits carry the 16 kbit/s ISDN basic

access D channel.

In GCI protocol, A and E are the handshake bits

and are used to control the transfer of information

on monitor channels.The E bit indicates the transfer of each new byte in one direction and the A bit

acknowledges this byte transfer in the reverse direction.

In V* protocol, there isn’t any handshake

mode.The transmitter has only to mark the validity

of the Monitor byte by positioning the E bit (T is not

used and is forced to “1”).

For more information about the GCI and V*, ref er

to the General Interface Circuit Specification

(issue1.0, march 1989) and the France Telecom

Specification about ISDN Basic Access second

generation (November 1990).

III.3.3 - Structure of the Treatment

In reception GCI/V* TDM’s are connected to DIN 4

and DIN 5. The D channel s are switched t hrough

the matrix towards the output 7 and output6 then

towards the HDLC receivers. The Monitor and S/C

bytes are multiplexed and sent to the CI and Monitor receive rs .

In transmission, the S/C and Monitor bytes are recombined by multiplexing the information provided

by the Monitor, C/I and the HDLC Transmitter.

Like in reception, the D channel is switched

through the matrix (input 7 towards DOUT 4 and

DOUT 5).

III.3.4 - CI and Monitor Channel Configuration

Monitor channel data is located in a time slot; the

CI and monitor handshake bits are in the next time

slot.

Each channel can be defined independently. A table with all the possible configurations is presented hereafter (Table 13).

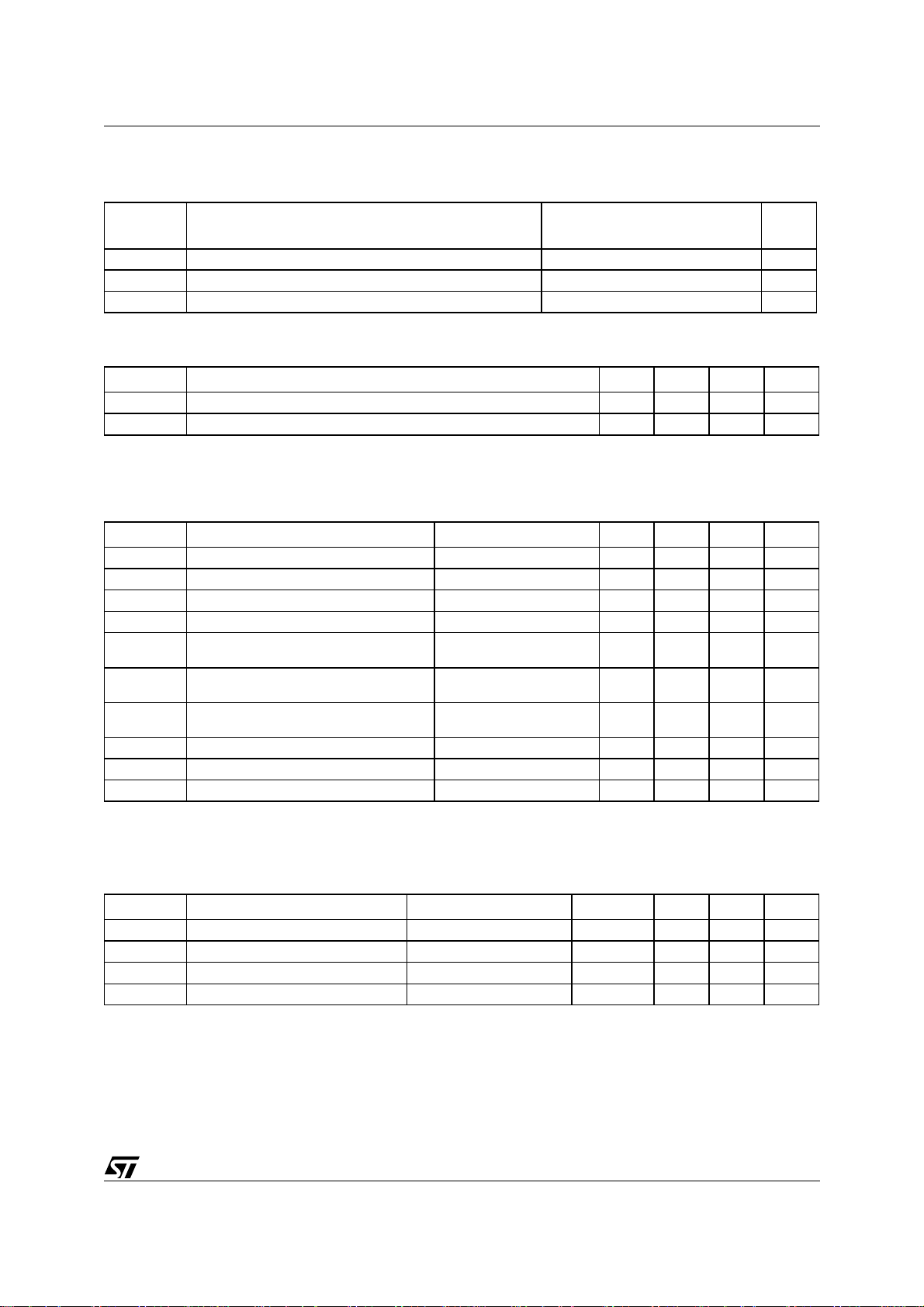

Table 13: C/I and MON Channel Configuration

C/I validated

or not

Monitor validated

or not

Note:

A mix of V* and GCI monitoring can be performed for two dis-

tinct chan nels in the sam e applicat io n.

CI For analog subscriber (6 bits)

CI For ISDN subscriber (4 bits)

Monitor V*

Monitor GCI

III.3.5 - CI and Monitor Transmission/Reception

Command

The reception of C/I and Monitor messages are

managed by two interrupt queues.

In transmission, a transmit command register is

implemented for each C/I and monitor channel

(16C/I transmit command registers and 16 Monitor

transmit command regist ers). Those regist ers are

accessible in read and write modes by the microprocessor.

III.4 - Scrambler and Descrambler

The TDM4 and TDM5 can be GCI multipexes.

Each GCI multipex comprises 8 GCI channels.

Each GCI channe l comprises two B chann els at

64 Kbit/s.

In reception it is possible to switch and to scramble

the contents of 32 B channels of GCI channels to

32 timeslots of the 256 output timeslots. In transmission these 32 timeslots are assigned to 32 B

channels.

In the other direction the contents of an selected B

channels is automatically switched an d descrambled to one B channel of 16 GCI channel.

See SCR bit of Connection Memory Data Register

CMDR (0E)H.

III.5 - Connection between “ISDN channels”

and GCI channels.

Three timeslots are assigned to one “ISDN channels”. Each “ISDN channels” comprises three

channels: B1+B2+B* with B*= D1,D2, A, E, S1,

S2, S3, S4 (See figure).

– Upstream. From GCI channels to ISDN chan-

nels.

• in reception: 16 GCI channels (B1+B2+MON+

D+C/I),

20/130

STLC5466

• in transmission: 16 ISDN channels (B1+B2+B*).

It is possible to swit ch t he c ontents of B 1, B2 and

D channels from 16 GCI channels in any 16 “ISDN

channels”, TDM side.

The contents of B1 and/or B2 can be scrambled or

not. If scrambled the number of the 32 timeslots

(TDM side) are different mandatory.

Receiving the contents of M onitor and Command

/ Indicate channels from 16 G CI channels. Pr imitives and messages are stored automatically in

the external shared memory.

Transmitting “six bit word” (A, E, S1, S2, S3, S4)

to any 16 “ISDN channels” TDM side or not. See

SBV bit of General Configuration Register GCR

(02)H.

– Downstream. From ISDN channels to GCI chan-

nels.

• in reception: ISDN channel (B1+B2+B*)

• in transmission: GCI channel (B1+B2+MON+

D+C/I)

It is possible to swit ch t he c ontents of B 1, B2 and

D channels from 16 “ISDN channels”, TDM side in

16 GCI channels.

The contents of B1 and/or B2 can be descrambled

or not. If descrambled the 32 B1/B2 belong to GCI

channels mandatory.

Receiving six bit word (A, E, S1, S2, S3, S4) from

any 16 “ISDN channels”, TDM side. The 16 “six bit

word” are stored automatically in the external

shared memory.

Transmitting the contents of Monitor and Command / Indicate channels to 16 GCI channels. See

SBV bit of General Configuration Register GCR

(02)H.

– Alarm Indication Signal.

This detection concerns 16 hyperchannels. One

hyperchannel comprises 16 bits (B1 and B2 only).

The Alarm Indications for the 16 hyperchannels

are stored automatically in the external shared

memory. See AISD bit of Switchi n g Matrix C onfiguration Register SMCR (0C)H.

III.6 - Microprocessor Interface

III.6.1 - Description

Multi-HDLC

The

circuit can be controlled by several types of microprocess ors (ST9/10, Intel /Motorola 8 or 16 data bits interfaces) such as:

– ST9/10 fa mily

– INTEL 80C188 8 bits

– INTEL 80C186 16 bits

– INTEL 386EX 16 bits

– MOTOROLA 68000 16 bits

– MOTOROLA 68020 32 bits

Table 14 :

MOD2

Pin

During the initialization of the

Microprocessor Interface Selection

MOD1

Pin

0 1 1 80C188

1 1 1 80C186

1 0 0 68000

0 0 0 68020

0 0 1 ST9

1 0 1 ST10 A/D multiplexed

1 1 0 ST10 A/D Not multiplexed

0 1 0 386EX

MOD0

Pin

Microprocessor

Multi-HD LC

circuit,

the microprocessor interface is informed of the

type of microprocessor that is connected by polarisation of three external pins MOD 0/2.

Three chip Select (CS0/2) pins are provided. CS0

will select the internal registers and CS1 the external memory. CS2 can be used to select the external memory in INTEL 386EX application only (see

pin 41 definition).

III.6.2 - Buffer

A Buffer is located in the microprocessor interface.

It is used whatever microprocessor selected

thanks to MOD0/2 pins. It allows to reduce the

shared memory access cycles for the microprocessor.

This Buffer consists of o ne Write FIFO and one

Read Fetch Memory (see Figure).

III.6.2.1 - Write FIFO

When the microprocessor delivers the address

word named Ax to write dat a named [Ax] in the

shared memory in fact it writes data [Ax] and address word Ax in the Write FIFO (8 words). If Ax is

in Fetch Memo r y, [Ax ] is re moved i n Fetch Memory.

There is no wait time for the microprocessor if the

Write FIFO is not full entirely.

21/130

STLC5466

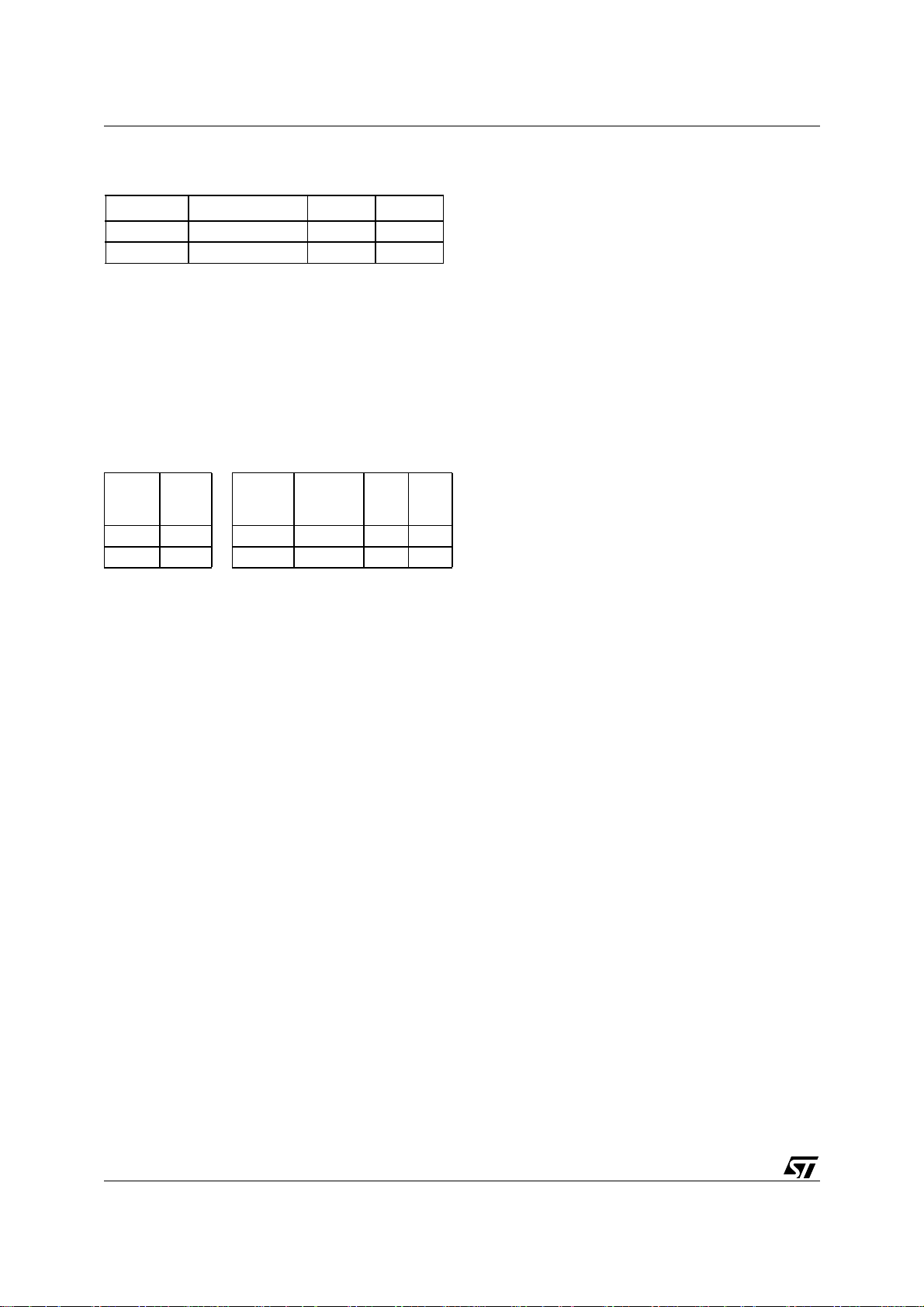

Shared memory

SDRAM Bus

To shared memory SDRAM Controller From shared memory

MHDLC Internal Bus

Ax, [Ax] Read Fetch 64 words

Ay, [Ay] Memory

Az, [Az]

At, [At] Write FIF O

Up to eight wo rds

Input register used to

store data in Write

FIFO

from microprocessor

Fetch Memory

An, [An]

MHDLC microprocessor interface To microprocessor

Microprocessor Bus

Microprocessor

Figure 2 :

22/130

Exchange between Microprocessor and Shared memory across MHDLC

STLC5466

III.6.2.2 - Read Fetch Memory

When the microprocessor delivers the address

word named An to read data named [An] out of the

shared memory in fact it reads data [An] from the

Read Fetch Memory (64 words).

The number of wait cycle f or the microp rocessor i s

strongly reduced. If An, address word delivered by

the microprocessor, and data [An] are already in

the Read Fetch Memory and validated then there