1/6

PRELIMINARY DATA

July 2001

STD8NS25

N-CH A NNEL 250V - 0.38Ω - 8A DPAK

MESH OVERLAY™ MOSFET

■ TYPICAL R

DS

(on) = 0.38 Ω

■ EXTREMELY HIGH dv /d t C APABILITY

■ 100% AVALANCHE TESTED

DESCRIPTION

Using the latest high voltage MESH OVERLAY™

process, STMicroelectronics has designed an advanced family of power MOSFETs with outstanding

performance. The new patented STrip layout coupled with the Company’s proprietary edge termination structure, makes it suitable in coverters for

lighting applications.

APPLICATIONS

■ HIGH CURRENT, HIGH SPEED SWITCHING

■ SWITH MODE POWER SUPPLI ES ( SMPS)

■ DC-DC CONVERTERS FOR TELECOM,

INDUSTRIAL, AND LIGHTING EQUIPMENT

ABSOLUTE MAXIMUM RATINGS

(•)Pu l se width limited by safe operating area

TYPE V

DSS

R

DS(on)

I

D

STD8NS25 250 V < 0.45 Ω 8 A

Symbol Parameter Value Unit

V

DS

Drain-source Voltage (VGS = 0)

250 V

V

DGR

Drain-gate Voltage (RGS = 20 kΩ)

250 V

V

GS

Gate- source Voltage ± 20 V

I

D

Drain Current (continuos) at TC = 25°C

8A

I

D

Drain Current (continuos) at TC = 100°C

5A

I

DM

(●)

Drain Current (pulsed) 32 A

P

TOT

Total Dissipation at TC = 25°C

80 W

Derating Factor 0.64 W/°C

dv/dt (1) Peak Diode Recovery voltage slope 5 V/ns

E

AS

(2)

Single Pulse Avalanche Energy 209 mJ

T

stg

Storage Temperature –65 to 150 °C

T

j

Max. Operating Junction Temperature 150 °C

(1) ISD≤ 8A, di/dt≤300 A/µs, VDD≤ V

(BR)DSS

, Tj≤ T

jMAX

(2) Start i ng Tj = 25°C, I

AR

= 50A, VDD=20 V

INTERNAL SCHEMATIC DIAGRAM

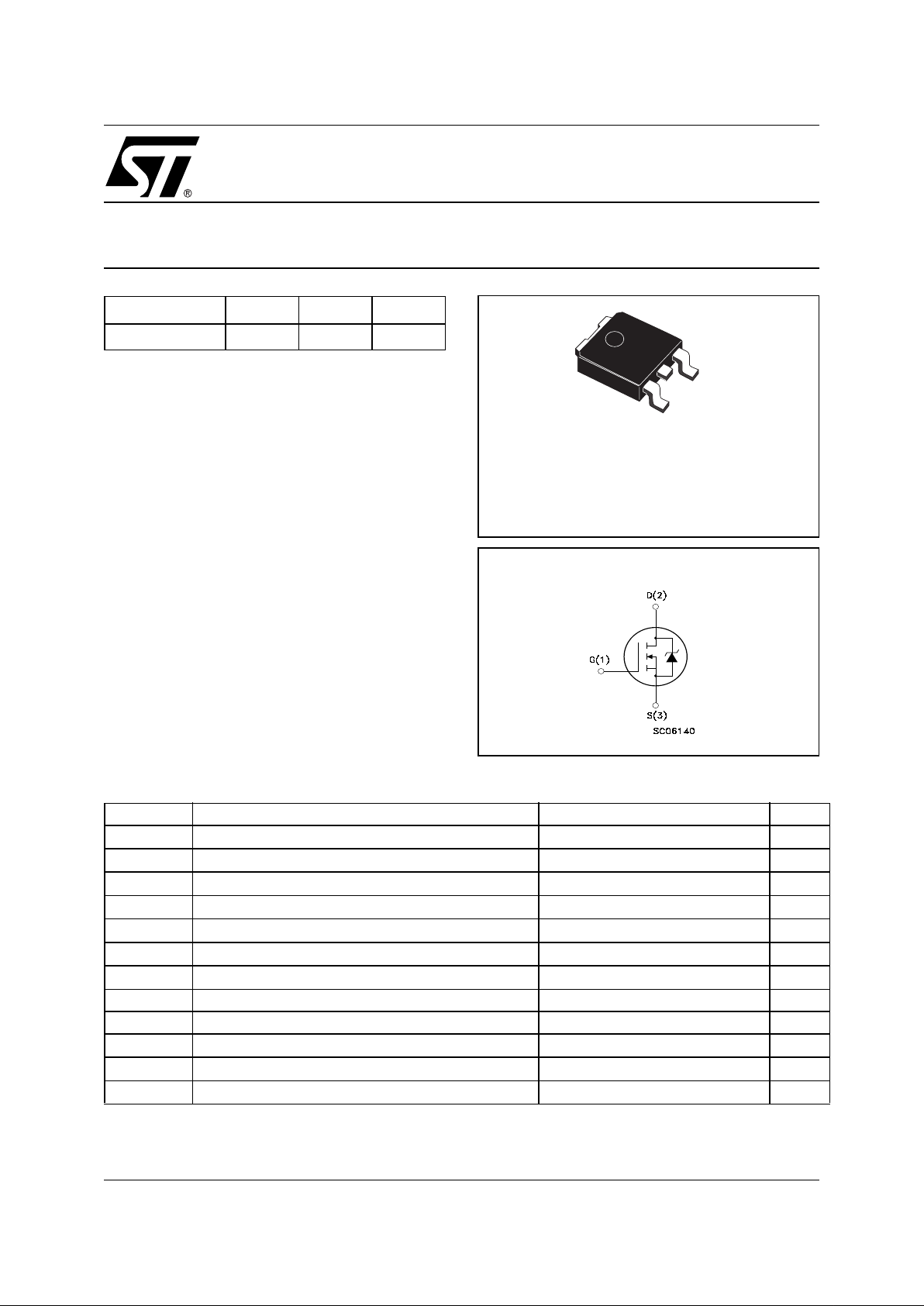

DPAK

1

3

STD8NS25

2/6

THERMA L D ATA

AVALANCHE CHARACTERISTICS

ELECTRICAL CHARACTERISTICS (TCASE = 25 °C UNLESS OTHERWISE SPECIFIED)

OFF

ON

(1)

DYNAMIC

Rthj-case Thermal Resistance Junction-case Max 1.56 °C/W

Rthj-amb Thermal Resistance Junction-ambient Max 62.5 °C/W

T

l

Maximum Lead Temperature For Soldering Purpose 300 °C

Symbol Parameter Max Value Unit

I

AR

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

j

max)

8A

E

AS

Single Pulse Avalanche Energy

(starting T

j

= 25 °C, ID = IAR, VDD = 50 V)

300 mJ

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

ID = 250 µA, VGS = 0 250 V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

1µA

V

DS

= Max Rating, TC = 125 °C

10 µA

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= ±20V ±100 nA

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

Gate Threshold Voltage

V

DS

= VGS, ID = 250µA

234V

R

DS(on)

Static Drain-source On

Resistance

VGS = 10V, ID = 4 A

0.38 0.45 Ω

Symbol Parameter Test Conditions Min. Typ. Max. Unit

g

fs

(1) Forward Transconductance VDS > I

D(on)

x R

DS(on)max,

I

D

=4A

78 S

C

iss

Input Capacitance

V

DS

= 25V, f = 1 MHz, VGS = 0

770 pF

C

oss

Output Capacitance 118 pF

C

rss

Reverse Transfer

Capacitance

48 pF

Loading...

Loading...