SGS Thomson Microelectronics STD7NS20 Datasheet

STD7NS20

N - CHANNEL 200V - 0.35Ω - 7A - DPAK

MESH OVERLAY MOSFET

PRELIMINARY DATA

■

TYPICAL R

DS(on)

= 0.35

Ω

■

EXTREMELY HIGH dv/dt CAPABILITY

■

100% AVALANCHE TESTED

■

VERY LOW INTRINSIC CAPACITANCES

■

GATE CHARGE MINIMIZED

■

FOR TAPE & REEL AND OTHER

PACKAGING OPTIONS CONTACT SALES

OFFICES

DESCRIPTION

This power MOSFET is designed using the

company’s consolidated strip layout-based MESH

OVERLAY process. This technology matches

and improves the performances compared with

standard parts from various sources.

APPLICATIONS

■

HIGH CURRENT SWITCHING

■

UNINTERRUPTIBLE PO WER S UPPLY (UPS)

■

DC/DC COVERTERS FOR TELECOM,

INDUSTRIAL, AND LIGHTING EQUIPMENT.

®

INTERNAL SCHEMATIC DIAGRAM

November 1998

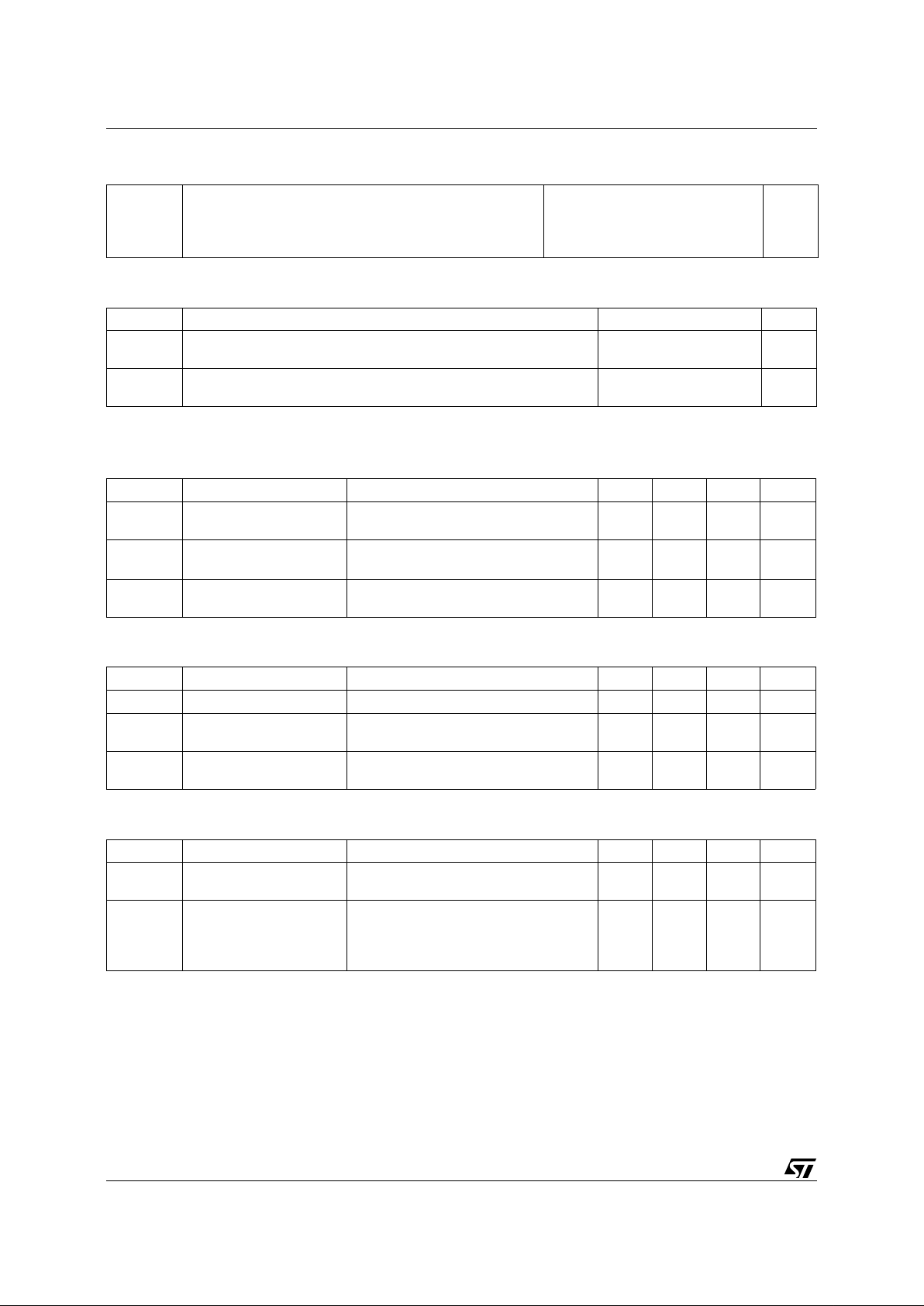

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DS

Drain-source Voltage (VGS = 0) 200 V

V

DGR

Drain- gate Voltage (RGS = 20 kΩ)

200 V

V

GS

Gate-source Voltage ± 20 V

I

D

Drain Current (continuous) at Tc = 25 oC7A

I

D

Drain Current (continuous) at Tc = 100 oC4.4A

I

DM

(•) Drain Current (pulsed) 28 A

P

tot

Total Dissipation at Tc = 25 oC45W

Derating Factor 0.37 W/

o

C

dv/dt(

1

) Peak Diode Recovery voltage slope 5 V/ns

T

stg

Storage Temperature -65 to 150

o

C

T

j

Max. Operating Junction Temperature 150

o

C

(•) Pulse width limited by safe operating area (1) ISD ≤ 7A, di/dt ≤ 300 A/µs, VDD ≤ V

(BR)DSS

, Tj ≤ T

JMAX

First Digit of the Datecode Being Z or K Identifies Silicon Characterized in this Dat asheet

TYPE V

DSS

R

DS(on)

I

D

STD7NS20 200 V < 0.40 Ω 7 A

1

3

DPAK

TO-252

(Suffix "T4")

1/5

THERMAL DATA

R

thj-case

Rthj-am b

R

thc-sink

T

l

Thermal Resistance Junction-case Max

Thermal Resistance Junction-ambient Max

Thermal Resistance Case-sink Typ

Maximum Lead Temperature For Soldering Purpose

2.7

100

1.5

275

o

C/W

oC/W

o

C/W

o

C

AVALANCHE CHARACTERIST ICS

Symbol Parameter Max Value Unit

I

AR

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

j

max)

7A

E

AS

Single Pulse Avalanche Energy

(starting T

j

= 25 oC, ID = IAR, V

DD

= 50 V)

60 mJ

ELECTRICAL CHARACTERISTICS

(T

case

= 25 oC unless otherwise specified)

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

I

D

= 250 µA V

GS

= 0

200 V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

V

DS

= Max Rating Tc = 125 oC

1

10

µA

µA

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= ± 20 V

± 100 nA

ON (∗)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

Gate Threshold Voltage

V

DS

= VGS ID = 250 µA

234V

R

DS(on)

Static Drain-source On

Resistance

VGS = 10V ID =3.5 A 0.35 0.40 Ω

I

D(on)

On State Drain Current VDS > I

D(on)

x R

DS(on)max

V

GS

= 10 V

7A

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

g

fs

(∗) Forward

Transconductance

VDS > I

D(on)

x R

DS(on)max

ID = 3.5 A 3 4 S

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

V

DS

= 25 V f = 1 MHz V

GS

= 0 540

90

35

700

120

50

pF

pF

pF

STD7NS20

2/5

Loading...

Loading...