SGS Thomson Microelectronics STD5NM50-1 Datasheet

STD5NM50

STD5NM50-1

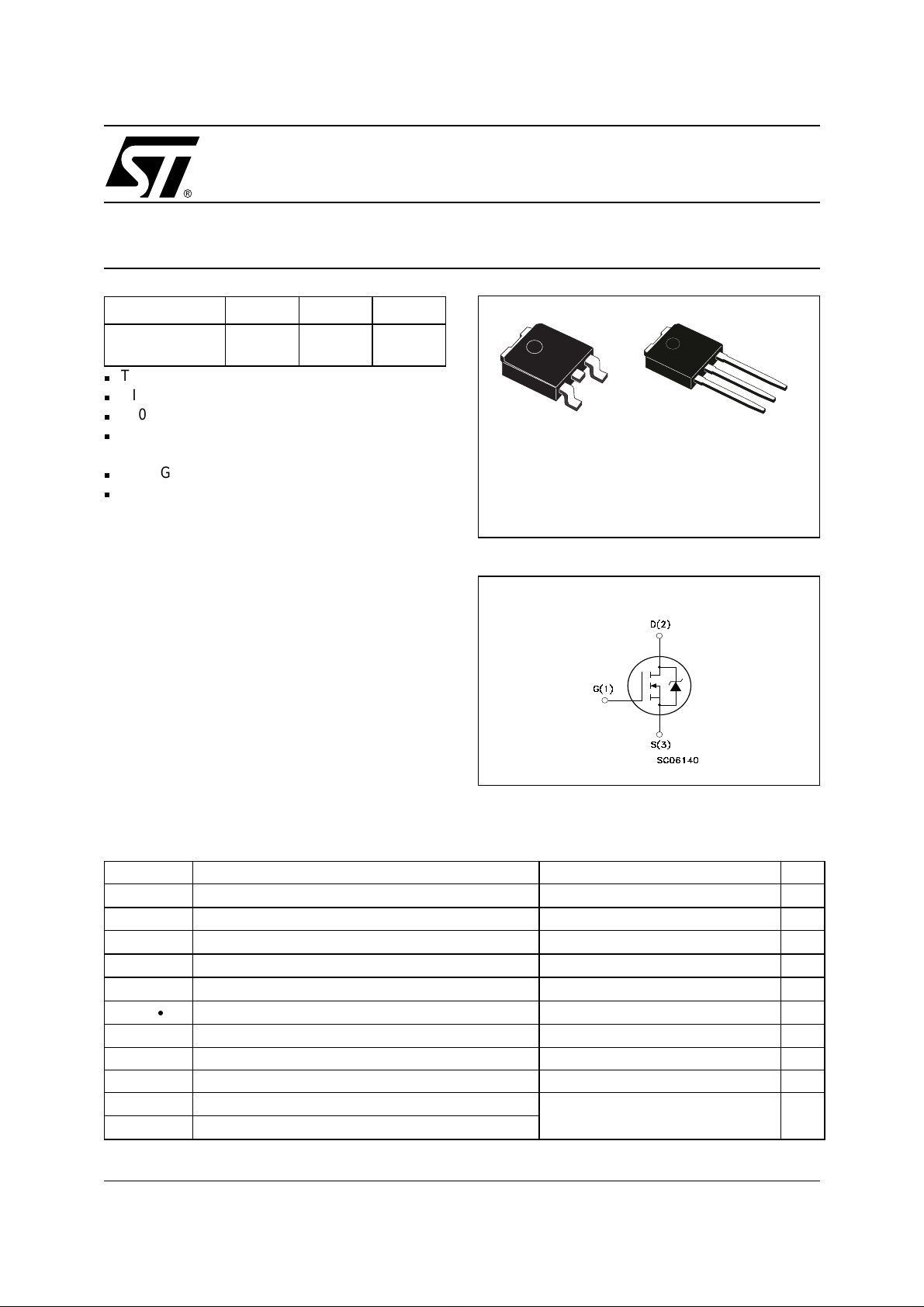

N-CHANNEL 500V - 0.7Ω - 7.5A DPAK/IPAK

MDmesh™Power MOSFET

TYPE V

STD5NM50

STD5NM50- 1

n

TYPICAL RDS(on) = 0.7Ω

n

HIGH dv/dt AND AVALANCHE CAPABILITIES

n

100% AVALANCHE TESTED

n

LOW INPUT CAPACITANCE AND GATE

DSS

500V

500V

R

DS(on)

<0.8Ω

<0.8Ω

I

D

7.5 A

7.5 A

CHARGE

n

LOW GATE INPUT RESIST ANC E

n

TIGHT PROCESS CONTROL AND HIGH

MANUFACTURING YIELDS

DESCRIPTION

The MDmesh™

is a new revolutionary MOSFET

technology that associates the Multiple Drain process with the Company’s PowerMESH™ horizontal

layout. The resulting product has an outstanding low

on-resistance, impressively high dv/dt and excellent

avalanche characteristics. The adoption of the

Company’s proprietary strip technique yields overall

dynamic performance that is significantly better than

that of similar competition’s products.

APPLICATIONS

The MDmesh™ family is very suitable for increasing

power density of high voltage converters allowing

system miniaturization and higher efficiencies.

3

1

DPAK

TO-252

INTERNAL SCHEMATIC DIAGRAM

IPAK

TO-251

(Add Suffix “-1”)

3

2

1

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DS

V

DGR

V

GS

I

D

I

D

I

DM

P

TOT

dv/dt (1) Peak Diode Recovery voltage slope 15 V/ns

T

stg

T

j

(•)Pu l se width limited by safe operating area

Drain-source Voltage (VGS = 0)

Drain-gate Voltage (RGS = 20 kΩ)

Gate- source Voltage ±30 V

Drain Current (continuous) at TC = 25°C

Drain Current (continuous) at TC = 100°C

(l)

Drain Current (pulsed) 30 A

Total Dissipation at TC = 25°C

Derating Factor 0.8 W/°C

Storage Temperature

Max. Operating Junction Temperature

(1) ISD ≤ 5A, di/dt ≤ 400A/µ s, VDD ≤ V

500 V

500 V

7.5 A

4.7 A

100 W

– 55 to 150 °C

, Tj ≤ T

(BR)DSS

JMAX.

1/10September 2002

STD5NM50/STD5NM50-1

THERMA L D ATA

Rthj-case Thermal Resistance Junction-case Max 1.25 °C/W

Rthj-amb Thermal Resistance Junction-ambient Max 100 °C/W

T

l

AVALANCHE CHARACTERISTICS

Symbol Parameter Max Value Unit

I

AR

E

AS

Maximum Lead Temperature For Soldering Purpose 300 °C

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

max)

j

Single Pulse Avalanche Energy

(starting T

= 25 °C, ID = IAR, VDD = 50 V)

j

2.5 A

300 mJ

ELECTRICAL CHARACTERISTICS (T

= 25 °C UNLESS OTHERWISE SPECIFIED)

CASE

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

ID = 250 µA, VGS = 0 500 V

Breakdown Voltage

ON

I

I

GSS

(1)

DSS

Zero Gate Voltage

Drain Current (V

GS

Gate-body Leakage

Current (V

DS

= 0)

= 0)

V

= Max Rating

DS

V

= Max Rating, TC = 125 °C

DS

V

= ±30V ±100 nA

GS

1µA

10 µA

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

R

DS(on)

Gate Threshold Voltage

Static Drain-source On

V

= VGS, ID = 250µA

DS

VGS = 10V, ID = 2.5A

345V

0.7 0.8 Ω

Resistance

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

(1) Forward Transconductance VDS = 25Vx, ID= 2.5A 3.5 S

g

fs

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance 88 pF

Reverse Transfer

Capacitance

C

(2) Equivalent Output

oss eq.

Capacitance

R

G

1. Pulsed: Pu l se duration = 300 µs, duty c ycle 1.5 %.

2. C

Gate Input Resistance f=1 MHz Gate DC Bias = 0

is defined as a constant equivalent capacitance giving the same charging time as C

oss eq.

.

V

DSS

V

= 25V, f = 1 MHz, VGS = 0

DS

415 pF

12 pF

VGS = 0V, VDS = 0V to 400V 50 pF

3 Ω

Test Signal Level = 20mV

Open Drain

when VDS increase s fr om 0 to 80%

oss

2/10

STD5NM50/STD5NM50-1

ELECTRICAL CHARACTERISTICS (CONTINUED)

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

t

d(on)

Q

Q

Q

t

r

g

gs

gd

Turn-on Delay Time

Rise Time 8 ns

Total Gate Charge

Gate-Source Charge 5 nC

Gate-Drain Charge 6 nC

SWITCHING OFF

Symbol Param eter Test Conditions Min. Typ. Max. U nit

t

r(Voff)

t

t

f

c

Off-voltage Rise Time

Fall Time 6 ns

Cross-over Time 13 ns

SOURCE DRAIN DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

VSD (1)

t

rr

Q

rr

I

RRM

t

rr

Q

rr

I

RRM

Note: 1. Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %.

2. Pulse width lim i t ed by safe ope rating area.

(2)

Source-drain Current 7.5 A

Source-drain Current (pulsed) 30 A

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charg e 1.1 µC

Reverse Recovery Curren t 11.5 A

Reverse Recovery Time

Reverse Recovery Charg e

Reverse Recovery Curren t

= 250V, ID = 2.5A

DD

RG= 4.7Ω VGS = 10V

(see test circuit, Figure 3)

V

= 400V, ID = 7.5A

DD

VGS = 10V

V

= 400V, ID = 5A,

DD

R

= 4.7Ω, V

G

GS

= 10V

(see test circuit, Figure 5)

ISD = 7.5A, VGS = 0

I

= 5A, di/dt = 100A/µs,

SD

VDD = 100V, Tj = 25°C

(see test circuit, Figure 5)

= 5A, di/dt = 100A/µs,

I

SD

VDD = 100V, Tj = 150°C

(see test circuit, Figure 5)

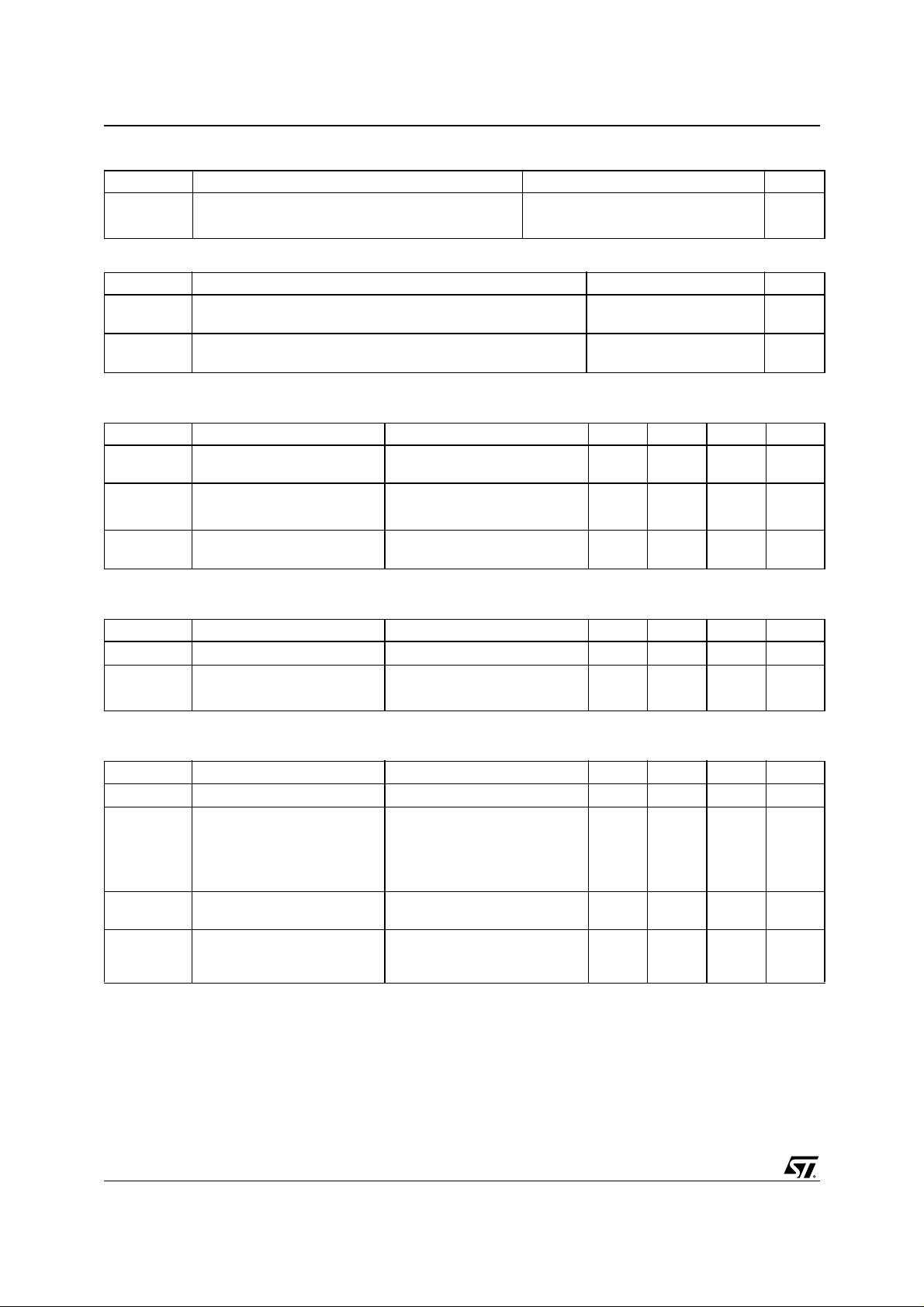

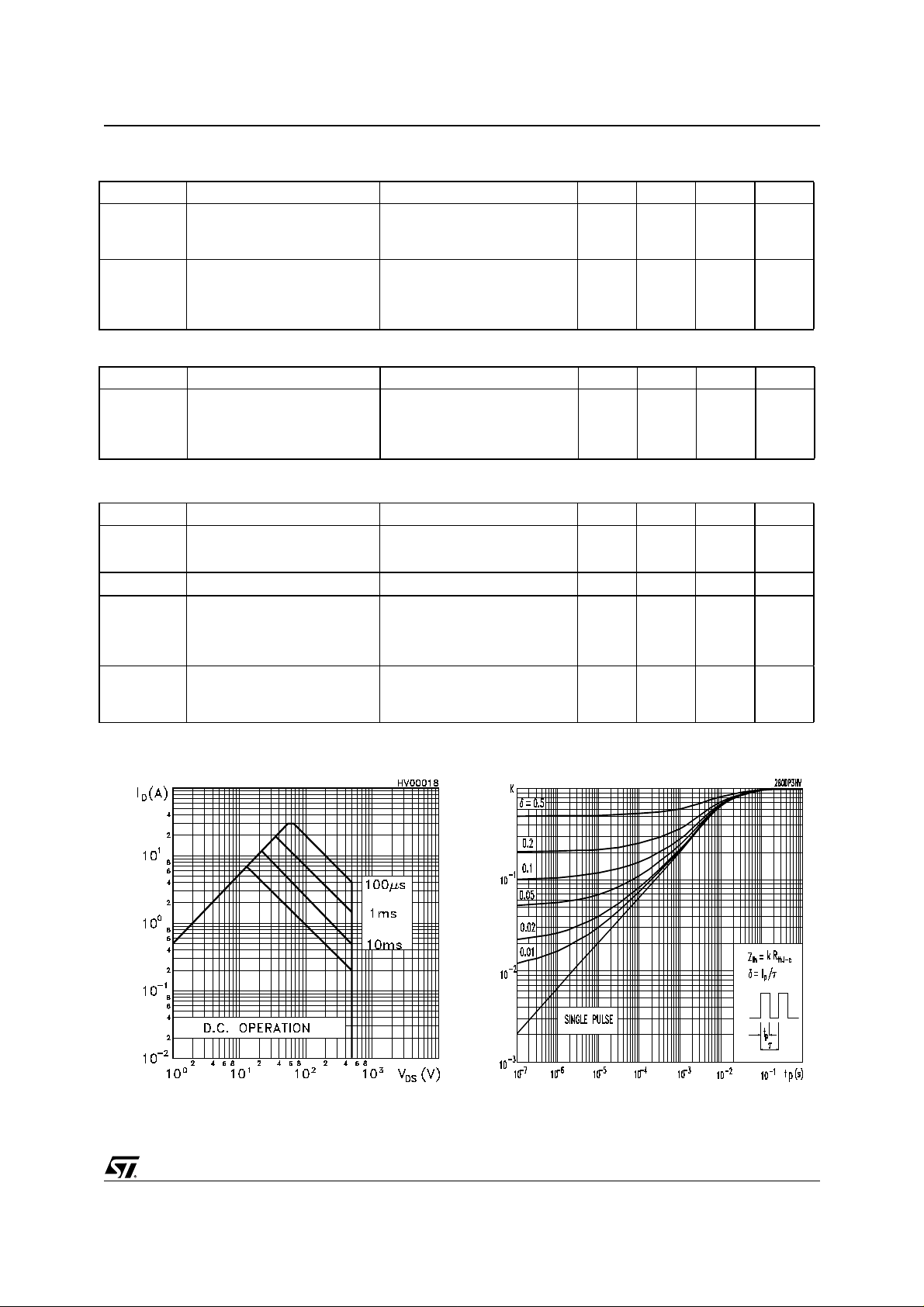

Thermal Impeda nce Safe Operating Area

16 ns

13 nC

14 ns

1.5 V

185 ns

270

1.6

12

ns

µC

A

3/10

Loading...

Loading...