SGS Thomson Microelectronics STD3NA50 Datasheet

STD3NA50

N - CHANNEL ENHANCEMENT MODE

POWER MOS TRANSISTOR

■ TYPICAL R

DS(on)

= 2.4 Ω

■ AVALANCHE RUGGED TECHNOLOGY

■ 100% AVALANCHE TESTED

■ REPETITIVE AVALANCHE DATA AT 100

o

C

■ APPLICATION ORIENTED

CHARACTERIZATION

■ THROUGH-HOLE IPAK (TO-251) POWER

PACKAGE IN TUBE (SUFFIX ”-1”)

■ SURFACE-MOUNTINGDPAK (TO-252)

POWER PACKAGE IN TAPE & REEL

(SUFFIX ”T4”)

APPLICATIONS

■ HIGH SPEED SWITCHING

■ UNINTERRUPTIBLE POWER SUPPLY (UPS)

■ MOTOR CONTROL, AUDIO AMPLIFIERS

■ INDUSTRIALACTUATORS

■ DC-DC & DC-AC CONVERTERS FOR

TELECOM, INDUSTRIAL AND CONSUMER

ENVIRONMENT

■ PARTICULARLY SUITABLE FOR

ELECTRONIC FLUORESCENT LAMP

BALLASTS

INTERNAL SCHEMATIC DIAGRAM

TYPE V

DSS

R

DS(on)

I

D

STD 3NA50 500 V < 3 Ω 2.7 A

November 1996

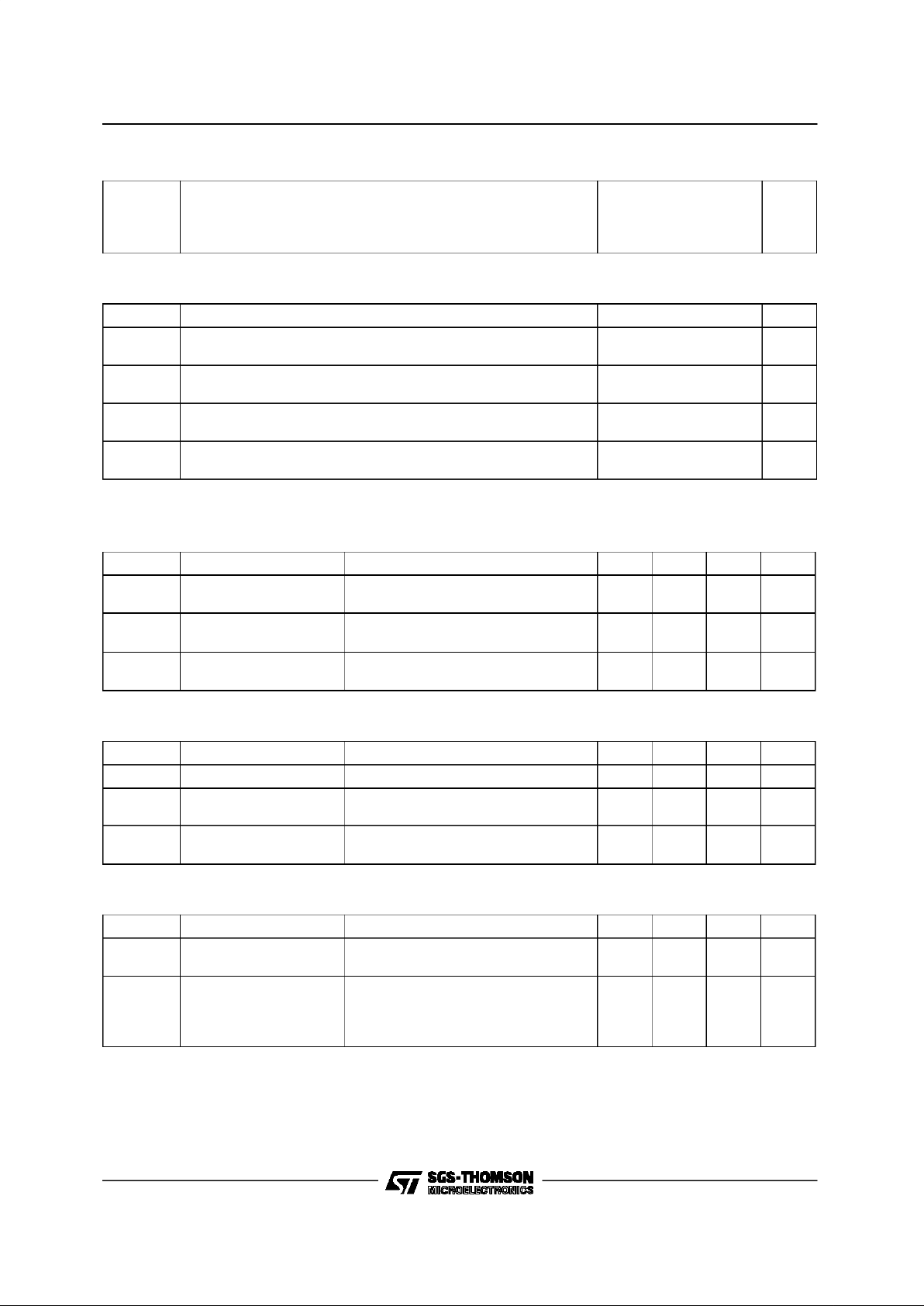

ABSOLUTE MAXIMUM RATINGS

Symb o l Paramet er Val u e Unit

V

DS

Drain - s ource Voltage (VGS= 0) 500 V

V

DGR

Drain- gate Voltage (RGS=20kΩ) 500 V

V

GS

Gate-source Voltage ± 30 V

I

D

Drain Current (continuous) at Tc=25oC2.7A

I

D

Drain Current (continuous) at Tc=100oC1.7A

I

DM

(•) Drain Current (pulsed) 10.8 A

P

tot

Total Di ssipation a t Tc=25oC50W

Derat ing Factor 0.4 W/

o

C

T

stg

St or a ge Tem perature -65 t o 150

o

C

T

j

Max. Operating Jun ction T emperature 150

o

C

(•) Pulsewidth limited bysafe operating area

1

3

2

IPAK

TO-251

(Suffix ”-1”)

1

3

DPAK

TO-252

(Suffix ”T4”)

1/10

THERMAL DATA

R

thj-case

R

thj-amb

R

thj-amb

T

l

Thermal Resistance Junction - cas e Max

Thermal Resistance Junction- ambient Max

Thermal Resistance Case-sink Typ

Maximum L ead Temperat ur e For Soldering Purpos e

2.5

80

0.7

275

o

C/W

o

C/W

o

C/W

o

C

AVALANCHE CHARACTERISTICS

Symbol Parameter Max Valu e Uni t

I

AR

Avalanc h e Cu rr ent , Repet itive or Not-Rep etitive

(pulse width limited by Tjmax, δ <1%)

2.7 A

E

AS

Single Pul se Avalanche Ener gy

(starti ng Tj=25oC, ID=IAR,VDD=50V)

40 mJ

E

AR

Repetitive Avalanc he Energ y

(pulse width limited by Tjmax, δ <1%)

2mJ

I

AR

Avalanc h e Cu rr ent , Repet itive or Not-Rep etitive

(Tc= 100oC, pulse width l imited by Tjmax, δ <1%)

1.7 A

ELECTRICAL CHARACTERISTICS (T

case

=25oC unless otherwisespecified)

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain - s ource

Break d own Volta ge

ID=250µAVGS= 0 500 V

I

DSS

Zer o G at e V oltage

Drain Current (V

GS

=0)

V

DS

=MaxRating

V

DS

= Max Rating x 0.8 Tc=125oC

25

250

µA

µA

I

GSS

Gat e- body Leakage

Current (VDS=0)

VGS= ± 30 V ± 100 nA

ON (∗)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

Gate Threshold Voltage VDS=VGSID=250µA 2.25 3 3.75 V

R

DS(on)

St at ic Drain-s our ce O n

Resistance

VGS=10V ID= 1.5 A 2.4 3 Ω

I

D(on)

On State Drain Current VDS>I

D(on)xRDS(on)max

VGS=10V

3.3 A

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

g

fs

(∗)Forward

Tr ansconductance

VDS>I

D(on)xRDS(on)maxID

=1.5A 1.2 2.2 S

C

iss

C

oss

C

rss

Input Capacitance

Out put Capacitance

Reverse Transfer

Capacitance

VDS=25V f=1MHz VGS=0 370

62

20

485

81

27

pF

pF

pF

STD3NA50

2/10

ELECTRICAL CHARACTERISTICS (continued)

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(on)

t

r

Turn-on T ime

Rise Time

VDD=250V ID=1.5A

RG=18 Ω VGS=10V

(see test circuit, figure 3)

14

23

20

30

ns

ns

(di/dt)

on

Turn-on Current S lope VDD=400V ID=3A

RG=18 Ω VGS=10V

(see test circuit, figure 5)

340 A/µs

Q

g

Q

gs

Q

gd

Total Gate Charge

Gat e- Source Charge

Gate-Drain Charge

VDD= 400 V ID=3A VGS=10V 21

6

9

28 nC

nC

nC

SWITCHING OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

r(Voff)

t

f

t

c

Off -voltage Rise Time

Fall Time

Cross-over Time

VDD=400V ID=3A

RG=18 Ω VGS=10V

(see test circuit, figure 5)

13

11

26

18

16

35

ns

ns

ns

SOURCE DRAINDIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

(•)

Source-drain C urrent

Source-drain C urrent

(pulsed)

2.7

10.8

A

A

V

SD

(∗) Forward On Voltage ISD=2.7A VGS=0 1.6 V

t

rr

Q

rr

I

RRM

Reverse Recovery

Time

Reverse Recovery

Charge

Reverse Recovery

Current

ISD=3A di/dt=100A/µs

VDD= 100 V Tj=150oC

(see test circuit, figure 5)

350

4.2

24

ns

µC

A

(∗) Pulsed:Pulse duration = 300 µs, dutycycle 1.5 %

(•) Pulse widthlimited by safeoperating area

Safe Operating Area Thermal Impedance

STD3NA50

3/10

Loading...

Loading...