SGS Thomson Microelectronics STD2NA50T4, STD2NA50-1 Datasheet

STD2NA50

N - CHANNEL ENHANCEMENT MODE

POWER MOS TRANSISTOR

PRELIMINARY DATA

■ TYPICAL R

DS(on)

= 3.25 Ω

■ ± 30V GATE TO SOURCE VOLTA GE RATING

■ 100% AVALANCHE TESTED

■ REPETITIVE AVA LANCHE DATA AT 100

o

C

■ LOW INTRINSIC CAPACITANCES

■ GATE CH ARGE MINIMIZED

■ REDUCED THRESHOLD VO LTA GE SPREA D

■ THROUGH-HO LE IPAK (TO -251) POWE R

PACKAGE IN TU BE (SUFFIX "-1")

■ SURFACE-MOUNTING DPAK (TO-252)

POWER PACKAGE IN TAPE & REEL

(SUFFIX "T4")

APPLICATIONS

■ MEDIUM CURRENT, HIGH SPEED

SWITCHING

■ SWITCH MODE P OW ER SUP P LIE S (S MP S)

■ CONSUMER AND INDUSTRIAL LIGHTING

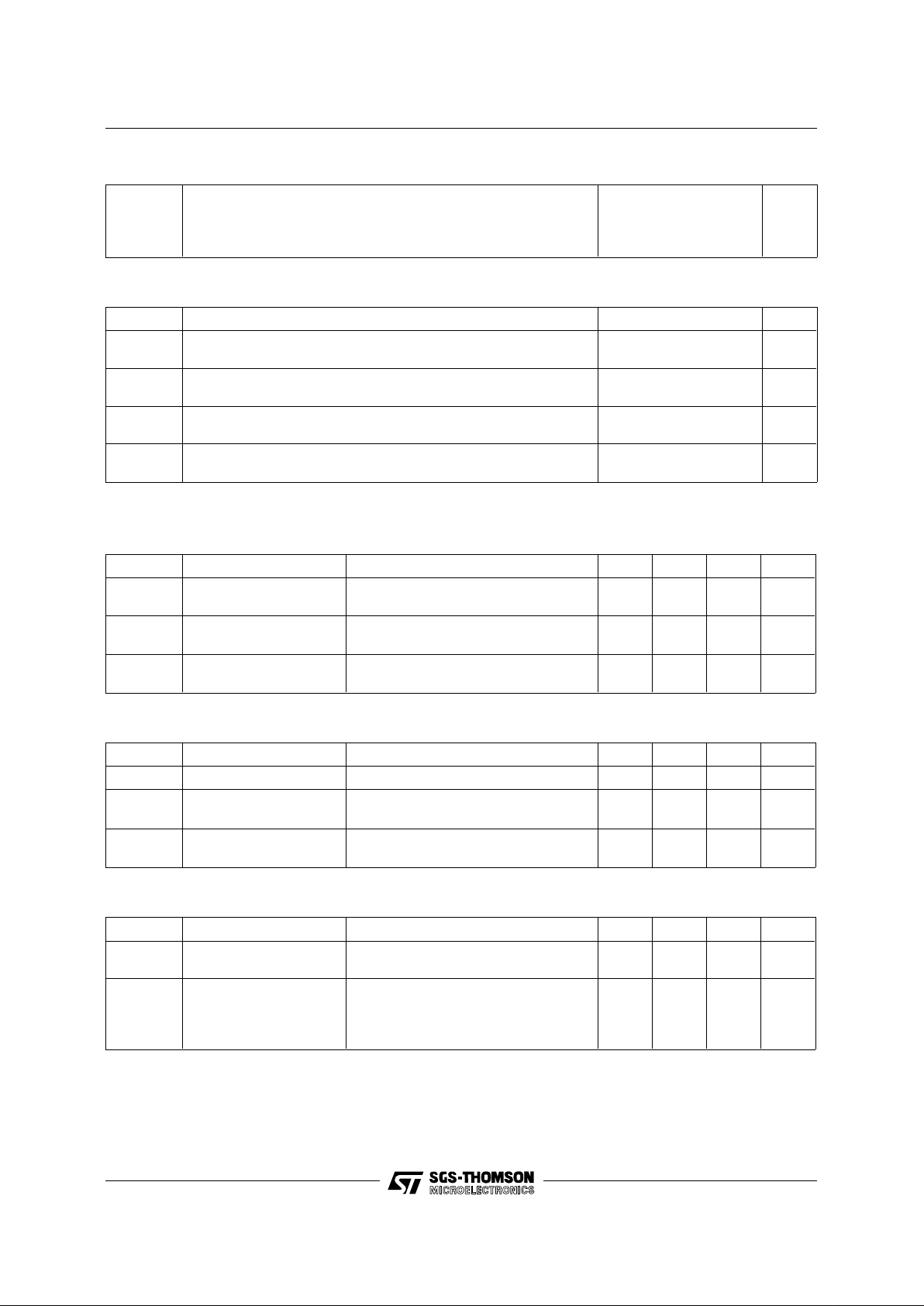

INTERNAL SCHEMATIC DIAGRAM

ABSOL UT E MAXIMU M RATINGS

Symbol Parameter Value Unit

V

DS

Drain-source Voltage (VGS = 0) 500 V

V

DGR

Drain- gate Voltage (RGS = 20 kΩ) 500 V

V

GS

Gate-source Voltage ± 30 V

I

D

Drain Current (continuous) at Tc = 25 oC 2.2 A

I

D

Drain Current (continuous) at Tc = 100 oC 1.4 A

I

DM

(•) Drain Current (pulsed) 8.8 A

P

tot

Total Dissipation at Tc = 25 oC45W

Derating Factor 0.36 W/

o

C

T

stg

Storage Temperature -65 to 150

o

C

T

j

Max. Operating Junction Temperature 150

o

C

(•) Pulse width limited by safe operating area

TYPE V

DSS

R

DS(on)

I

D

STD2NA50 500 V < 4 Ω 2.2 A

March 1996

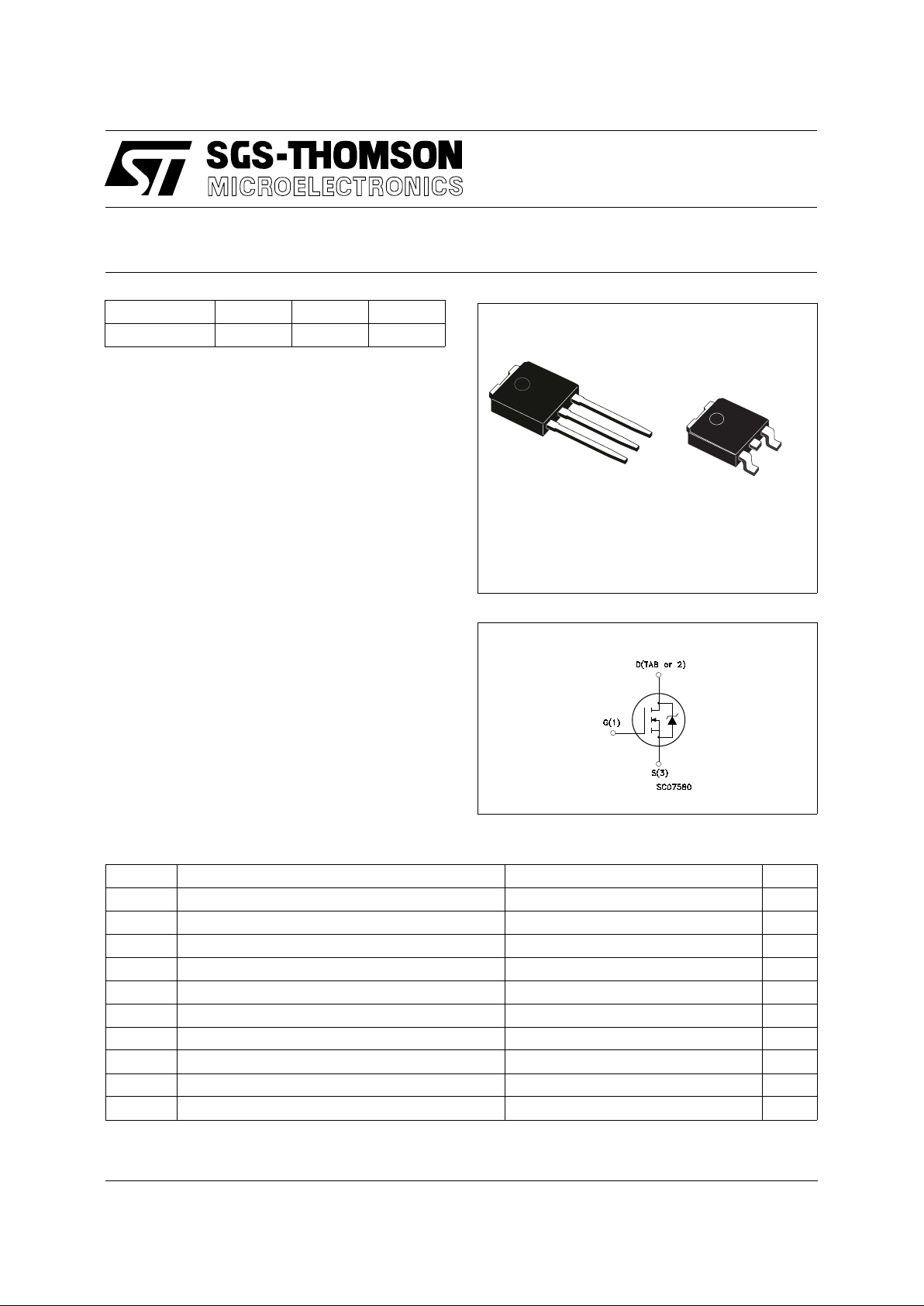

3

2

1

IPAK

TO-251

(Suffix "- 1")

1

3

DPAK

TO-252

(Suffix "T4")

1/6

THERMAL DATA

R

thj-case

R

thj-amb

R

thc-si n k

T

l

Thermal Resistance Junction-case Max

Thermal Resistance Junction-ambient Max

Thermal Resistance Case-sink Typ

Maximum Lead Temperature For Soldering Purpose

2.78

100

1

275

o

C/W

o

C/W

o

C/W

o

C

AVALANCHE CHARACTERI S TICS

Symbol Parameter Max Value Unit

I

AR

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

j

max, δ < 1%)

2.2 A

E

AS

Single Pulse Avalanche Energy

(starting T

j

= 25 oC, ID = IAR, V

DD

= 50 V)

25 mJ

E

AR

Repetitive Avalanche Energy

(pulse width limited by T

j

max, δ < 1%)

1mJ

I

AR

Avalanche Current, Repetitive or Not-Repetitive

(T

c

= 100 oC, pulse width limited by Tj max, δ < 1%)

1.4 A

ELECTRICAL CHARACTERISTICS (T

case

= 25 oC unless otherwise specified)

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

ID = 250 µA V

GS

= 0 500 V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

V

DS

= Max Rating x 0.8 Tc = 125 oC

250

1000µAµA

I

GSS

Gate-Source Leakage

Current (V

DS

= 0)

V

GS

= ± 30 V 100 mA

ON (∗)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

Gate Threshold Voltage V

DS

= V

GS ID

= 250 µA 2.25 3 3.75 V

R

DS(on)

Static Drain-source On

Resistance

VGS = 10 V ID = 1.1 A

V

GS

= 10 V ID = 1.1 A Tc = 100oC

3.25 4

8

Ω

Ω

I

D(on)

On State Drain Current VDS > I

D(on)

x R

DS(on)max

V

GS

= 10 V

2.2 A

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

g

fs

(∗) Forward

Transconductance

VDS > I

D(on)

x R

DS(on)max

ID = 1.1 A 0.7 1.9 S

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

V

DS

= 25 V f = 1 MHz V

GS

= 0 300

55

15

400

70

20

pF

pF

pF

STD2NA50

2/6

Loading...

Loading...