SGS Thomson Microelectronics STP95NF03, STB95NF03-1, STB95NF03 Datasheet

1/9March 2003

STB95NF03

N-CHANNEL 30V - 0.0065 Ω - 95A D²PAK

STripFET™ II POWER MOSFET

■ TYPICAL R

DS

(on) = 0.0065 Ω

■ STANDARD THRESHOLD DRIVE

■ 100% AVALANCHE TESTED

■ SURFACE-MOUNTING D

2

PAK (TO-263)

POWER PACKAG E IN TU BE (NO SU FFIX) OR

IN TAPE & REEL (SUFFIX “T4”)

DESCRIPTION

This Power MOSFET is the latest dev elo pment of

STMicroelectronis unique "Single Feature Size™"

strip-based process. The resulting transistor

shows extremely high packing density for low onresistance, rugged avalanche characteristics and

less critical alignment steps therefore a remarkable manufacturing reproducibility.

APPLICATIONS

■ HIGH CURRENT, HIGH SPEED SWITCHING

■ DC-DC & DC-AC CONVERTERS

■ SOLENOID AND RELAY DRIVERS

TYPE

V

DSS

R

DS(on)

I

D

STB95NF03 30 V <0.007

Ω

80 A

1

3

D2PAK

TO-263

(Suffix “T4”)

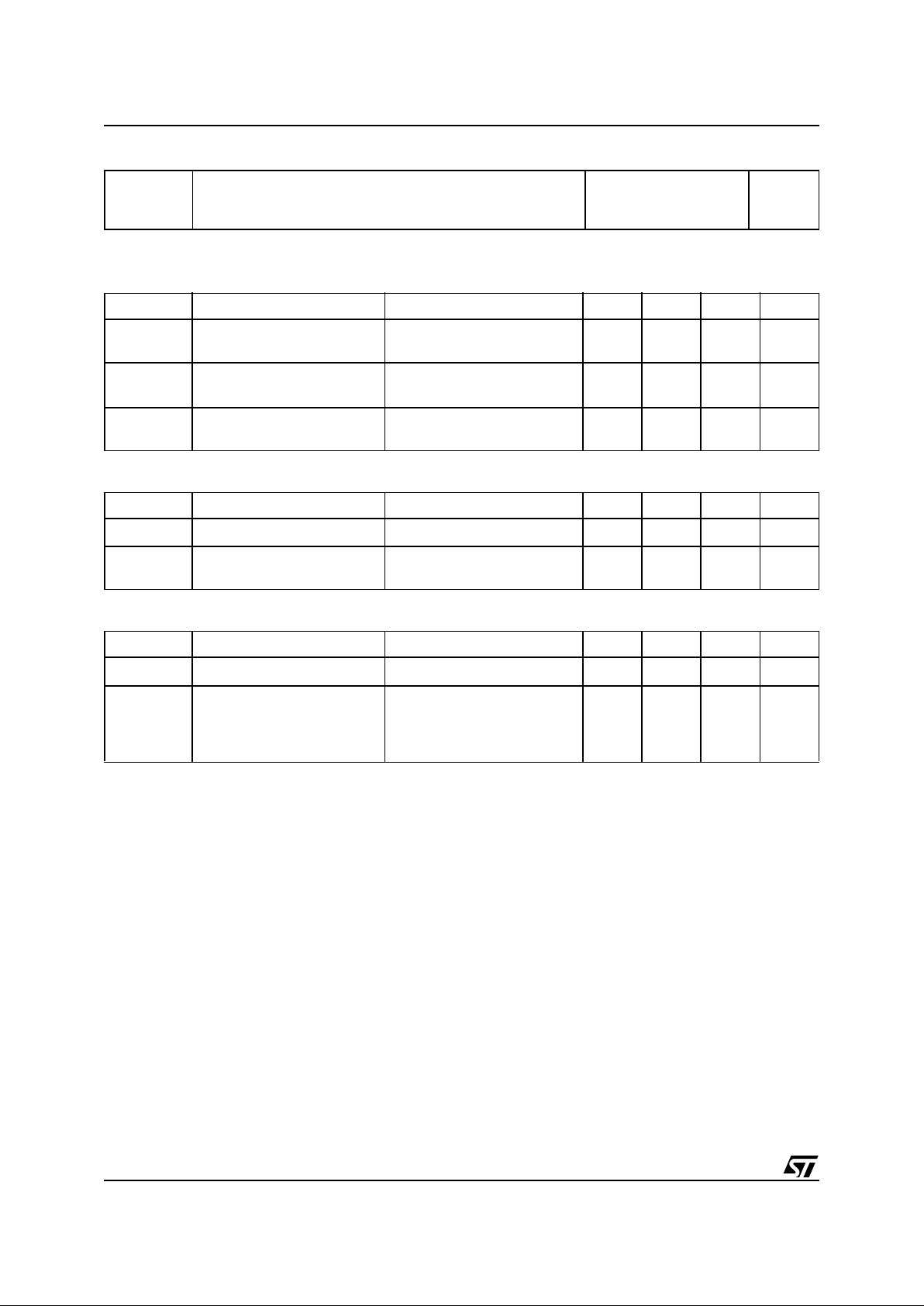

ABSOLUTE MAXIMUM RATINGS

(

•)

Pulse width limited by safe operating area.

(*) Curren t Lim i ted by Pack age

(1) ISD ≤ 95A, di/dt ≤ 150A/µs, VDD ≤ V

(BR)DSS

, Tj ≤ T

JMAX.

(2) Starting Tj = 25 oC, ID = 47.5A, VDD = 25V

Symbol Parameter Value Unit

V

DS

Drain-source Voltage (VGS = 0)

30 V

V

DGR

Drain-gate Voltage (RGS = 20 kΩ)

30 V

V

GS

Gate- source Voltage ± 20 V

I

D

(

∗

)

Drain Current (continuous) at T

C

= 25°C

80 A

I

D

Drain Current (continuous) at TC = 100°C

80 A

I

DM

(

•)

Drain Current (pulsed) 320 A

P

tot

Total Dissipation at TC = 25°C

150 W

Derating Factor 1 W/°C

dv/dt

(1)

Peak Diode Recovery voltage slope 3.0 V/ns

E

AS

(2)

Single Pulse Avalanche Energy 720 mJ

T

stg

Storage Temperature

-55 to 175 °C

T

j

Operating Junction Temperature

INTERNAL SCHEMATIC DIAGRAM

STB95NF03

2/9

THERMA L D ATA

ELECTRICAL CHARACTERISTICS (T

case

= 25 °C unless otherwise specified)

OFF

ON

(*)

DYNAMIC

Rthj-case

Rthj-amb

T

l

Thermal Resistance Junction-case

Thermal Resistance Junction-ambient

Maximum Lead Temperature For Soldering Purpose

Max

Max

1

62.5

300

°C/W

°C/W

°C

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

I

D

= 250 µA VGS = 0

30 V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

V

DS

= Max Rating TC = 125°C

1

10

µA

µA

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= ± 20 V

±100 nA

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

Gate Threshold Voltage

V

DS

= V

GS

ID = 250 µA

24V

R

DS(on)

Static Drain-source On

Resistance

V

GS

= 10 V ID = 45 A

0.0065 0.0070

Ω

Symbol Parameter Test Conditions Min. Typ. Max. Unit

g

fs

(*)

Forward Transconductance

V

DS

= 15 V ID =45 A

50 S

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

V

DS

= 25V f = 1 MHz VGS = 0

2450

880

170

pF

pF

pF

3/9

STB95NF03

SWITCHING ON

(*)

SWITCHING OFF

(*)

SOURCE DRAIN DIODE

(*)

(*)

Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %.

(

•)

Pulse width l i m i ted by T

jmax

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(on)

t

r

Turn-on Time

Rise Time

V

DD

= 15 V ID = 47.5 A

R

G

= 4.7

Ω

VGS = 10 V

20

195

ns

ns

Q

g

Q

gs

Q

gd

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

V

DD

=15V ID=95A VGS=10V

59

18

21

70 nC

nC

nC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(off)

t

f

Turn-off Delay Time

Fall Time

V

DD

= 20 V ID = 47.5 A

R

G

= 4.7Ω, V

GS

= 10 V

35

35

ns

ns

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

(

•)

Source-drain Current

Source-drain Current (pulsed)

95

320

A

A

V

SD

(*)

Forward On Voltage

I

SD

= 95 A VGS = 0

1.3 V

t

rr

Q

rr

I

RRM

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

I

SD

= 95 A di/dt = 100A/µs

V

DD

= 20 V Tj = 150°C

(see test circuit, Figure 5)

60

120

4

ns

nC

A

Thermal Impedance

ELECTRICAL CHARACTERISTICS (continued)

Safe Operating Area

Loading...

Loading...