SGS Thomson Microelectronics STB85NF3LL Datasheet

STB85NF3LL

N-CHANNEL 30V - 0.006Ω - 85A D2PAK

LOW GATE CHARGE STripFET™II POWER MOSFET

TYPE V

DSS

R

DS(on)

I

D

STB85NF3LL 30 V < 0.008 Ω 85 A

■ TYPICAL R

■ OPTIMAL R

■ CONDUCTION LOSSES REDUCED

■ SWITCHING LOSSES REDUCED

■ ADD SUFFIX “T4” FOR ORDERING IN TAPE &

(on) = 0.0075Ω (@4.5V)

DS

(on) x Qg TRADE-OFF @4.5V

DS

REEL

DESCRIPTION

This application specific Power MOSFET is the third

genaration of STMicroelectronics unique “ Single

Feature Size” strip-based process. The resulting

transistor shows the best trade-off between on-resistance and gate charge. When used a s high and

low side in buck regulators , it gives the best performance in terms of both conduction and switching

losses. This is extremely important for motherboards where fast switching and high e fficiency are

of paramount importance.

APPLICATIONS

■ SPECIFICALLY DESIGNED AND OPTIMISED

FOR HIGH EFFICIENCY CPU CORE DC/DC

CONVERTERS

3

1

D2PAK

INTERNAL SCHEMATIC DIAGRAM

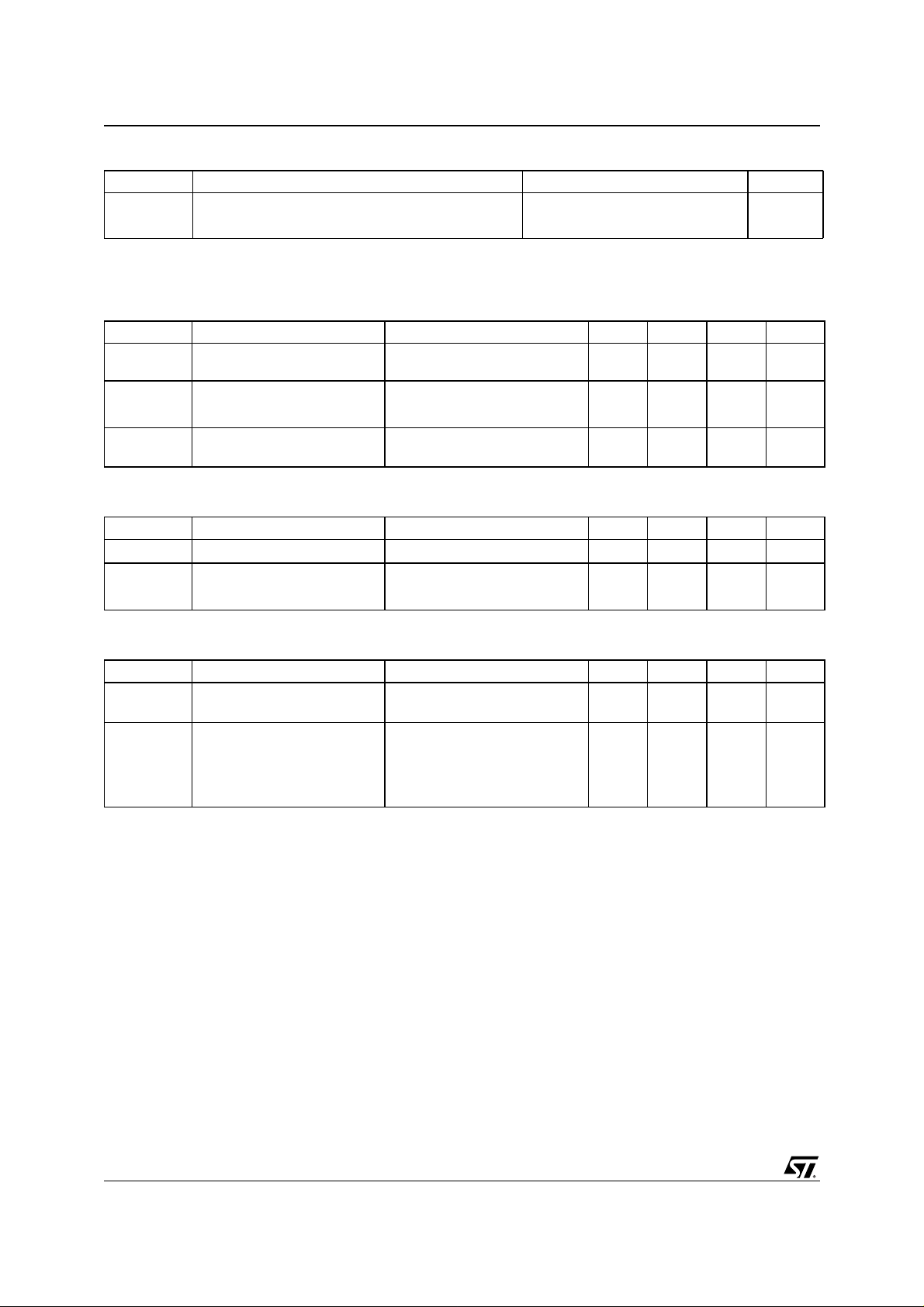

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DS

V

DGR

V

GS

V

GSM

I

D

I

D

I

DM

P

TOT

T

stg

T

j

(●) Pulse width limited by safe operating area

Drain-source Voltage (VGS = 0)

Drain-gate Voltage (RGS = 20 kΩ)

30 V

30 V

Gate- source Voltage ± 16 V

Gate-source Voltage Pulsed

≤50µs; duty cycle 25%; Tj ≤ 150°C)

(t

p

Drain Current (continuos) at TC = 25°C

Drain Current (continuos) at TC = 100°C

(l)

Drain Current (pulsed) 340 A

Total Dissipation at TC = 25°C

± 20 V

85 A

60 A

110 W

Derating Factor 0.73 W/°C

Storage Temperature –65 to 175 °C

Max. Operating Junction Temperature 175 °C

1/9November 2001

STB85NF3LL

THERMA L D ATA

Rthj-case Thermal Resistance Junction-case Max 1.36 °C/W

Rthj-amb Thermal Resistance Junction-ambient Max 62.5 °C/W

T

l

ELECTRICAL CHARACTERISTICS (TCASE = 25 °C UNLESS OTHERWISE SPECIFIED)

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

I

DSS

I

GSS

ON

(1)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

R

DS(on)

Maximum Lead Temperature For Soldering Purpose 300 °C

Drain-source

ID = 250 µA, VGS = 0 30 V

Breakdown Voltage

Zero Gate Voltage

Drain Current (V

GS

= 0)

Gate-body Leakage

Current (V

DS

= 0)

Gate Threshold Voltage

Static Drain-source On

Resistance

V

= Max Rating

DS

V

= Max Rating, TC = 125 °C

DS

V

= ± 16V ±100 nA

GS

V

= VGS, ID = 250µA

DS

VGS = 10V, ID = 40 A

VGS = 4.5V, ID = 40 A

1V

0.006 0.008 Ω

0.0075 0.0095 Ω

1µA

10 µA

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

(1) Forward Transconductance VDS > I

g

fs

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance 635 pF

Reverse Transfer

Capacitance

ID= 40 A

V

DS

D(on)

x R

DS(on)max,

= 25V, f = 1 MHz, VGS = 0

30 S

2210 pF

138 pF

2/9

STB85NF3LL

ELECTRICAL CHARACTERISTICS (CONTINUED)

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

t

d(on)

Q

Q

Q

t

r

g

gs

gd

Turn-on Delay Time

Rise Time 130 ns

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

SWITCHING OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(off)

t

d(off)

t

f

t

f

t

c

Turn-off-Delay Time

Fall Time

Off-voltage Rise Time

Fall Time

Cross-over Time

SOURCE DRAIN DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

VSD (1)

t

rr

Q

rr

I

RRM

Note: 1. Pulsed: Pu l se duration = 300 µs, duty c yc l e 1.5 %.

2. Pulse width li mited by safe operating area.

Source-drain Current 85 A

(2)

Source-drain Current (pulsed) 340 A

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

= 15V, ID = 30A

DD

R

= 4.7Ω VGS = 4.5V

G

(see test circuit, Figure 3)

= 24V, ID = 60A,

V

DD

VGS = 4.5V

= 15V, ID = 30A,

V

DD

RG=4.7Ω, V

GS

= 4.5V

(see test circuit, Figure 3)

GS

=30A

D

= 4.5V

Vclamp =24V, I

R

=4.7Ω, V

G

(see test circuit, Figure 5)

ISD = 85A, VGS = 0

= 85A, di/dt = 100A/µs,

I

SD

VDD = 15V, Tj = 150°C

(see test circuit, Figure 5)

22 ns

30

40 nC

9

12.5

36.5

36.5

32

23

40

1.3 V

65

105

3.4

nC

nC

ns

ns

ns

ns

ns

ns

nC

A

Thermal ImpedenceSafe Operating Area

3/9

Loading...

Loading...