SGS Thomson Microelectronics STB7002TR, STB7002 Datasheet

1/7January, 22 2002

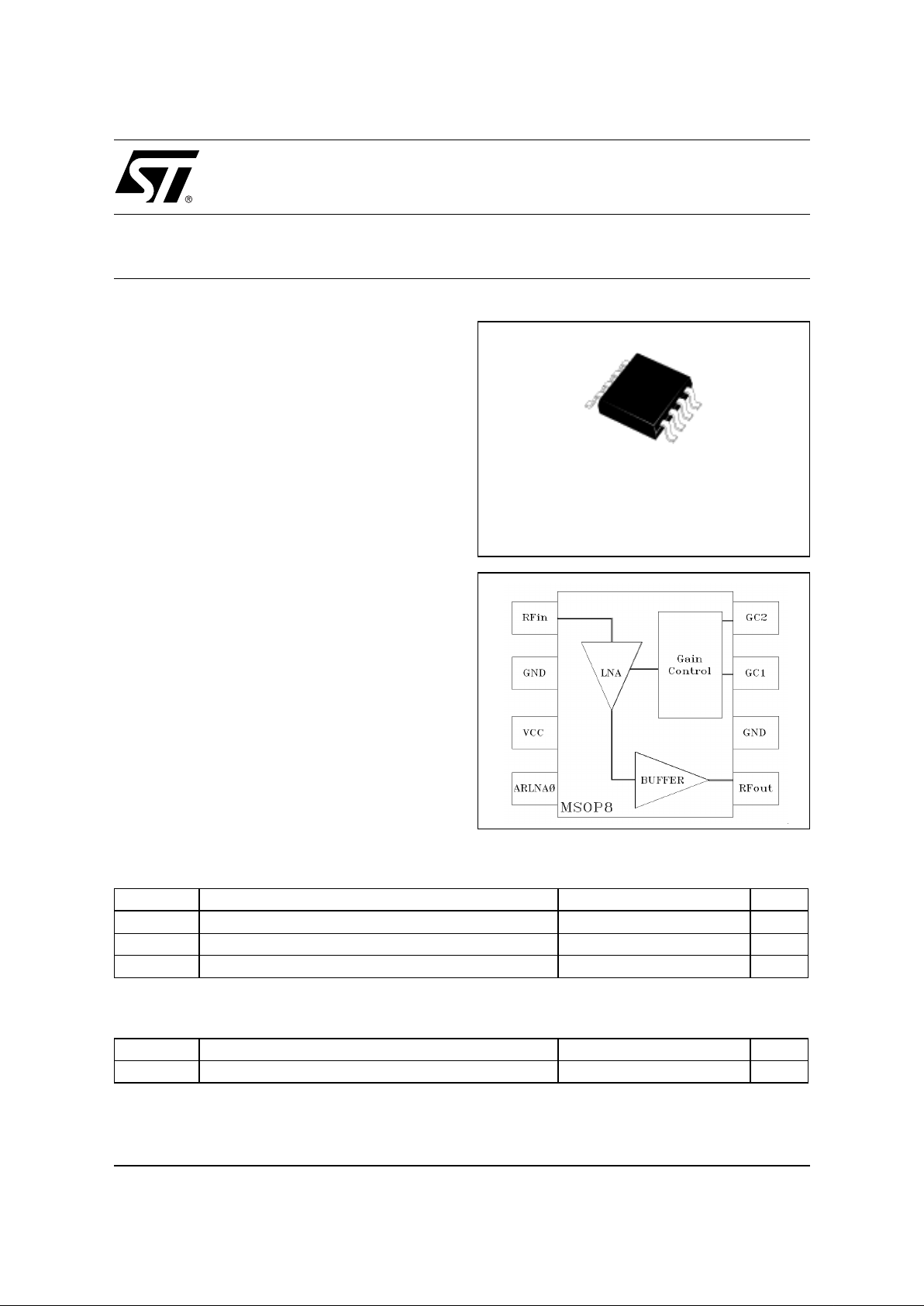

STB7002

1.8GHz THREE GAIN LEVEL LNA

• FULLY INTEGRATED 1.8GHz LNA

• THREE GAIN LEVELS (0dB, 18dB, 26dB typ.

@ 2.8V)

• LOW NOISE FIGURE

• TEMPERATURE COM PENSATED

APPLICATIONS

• DCS HANDSETS

DESCRIPTION

The STB7002 is a Silicon monolithic amplifier, that

offers low noise figure and three gain levels for

1.8GHz applications. STB7002 is housed in a

small industry-standard MSOP8-EP surface

mount package, requiring very little board space

(50% reduction vs SO8 Package). MSOP8-EP

dimensions are 3mmx5mm with a 1.1mm

thickness. STB7002 is ESD protected and

requires minimum external components in the

application circuit, for the on-chip bias and gain

control. Furthermore, temperature and supply

voltage compensation ensu res high stability over

a wide range of operating conditions.

MSOP8-EP

(exposed pad)

ORDER CODE

STB7002

BRANDING

7002

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

cc

Supply voltage 4 V

Tj Junction Temperature 150 °C

T

stg

Storage temperature -40 to +85 °C

THERMA L DA TA

Symbol Parameter Value Unit

R

th(j-a)

Junction -ambient Thermal Resistance TBD °C/W

STB7002

2/7

ELECTRICAL SPECIFICATION (T

amb

= 25°C, Vcc = 2.8V)

Note(1) : Gp1 m in gain, Gp2 mid gain and Gp3 max gain.

Symbol Parameters Test Conditions Min. Typ. Max. Unit

Vcc Supply voltage 2.7 2.8 2.9 V

I

bias

Bias current

for G

p1

(1)

G

p2

(1)

G

p3

(1)

8

14

10

11.5

17.5

15.0

15.0

22.519mA

Istby

Standby current 20 µA

f Frequency range 1805 1880 MHz

G

p1,2,3

Power gain

G

p1

G

p2

G

p3

-3.0

16.0

24.0

0.0

18.0

26.0

3.0

20.0

28.0

dB

NF

1,2,3

Noise figure

for G

p1

G

p2

G

p3

9

2.9

2.6

dB

P1dB

1,2,3

Input 1 dB Compr.Power

for G

p1

G

p2

G

p3

-15.5

-19

-27

dBm

IIP3

1,2,3

Input Third Order Intercept

for G

p1

G

p2

G

p3

-4

-9

-17

dBm

VSWRi

Input VSWR

for G

p1

G

p2

G

p3

2.5:1

2.2:1

1.5:1

VSWRo

Output VSWR

for G

p1

G

p2

G

p3

1.3:1

1.5:1

1.8:1

AZout Zout LNA on/off 15 %

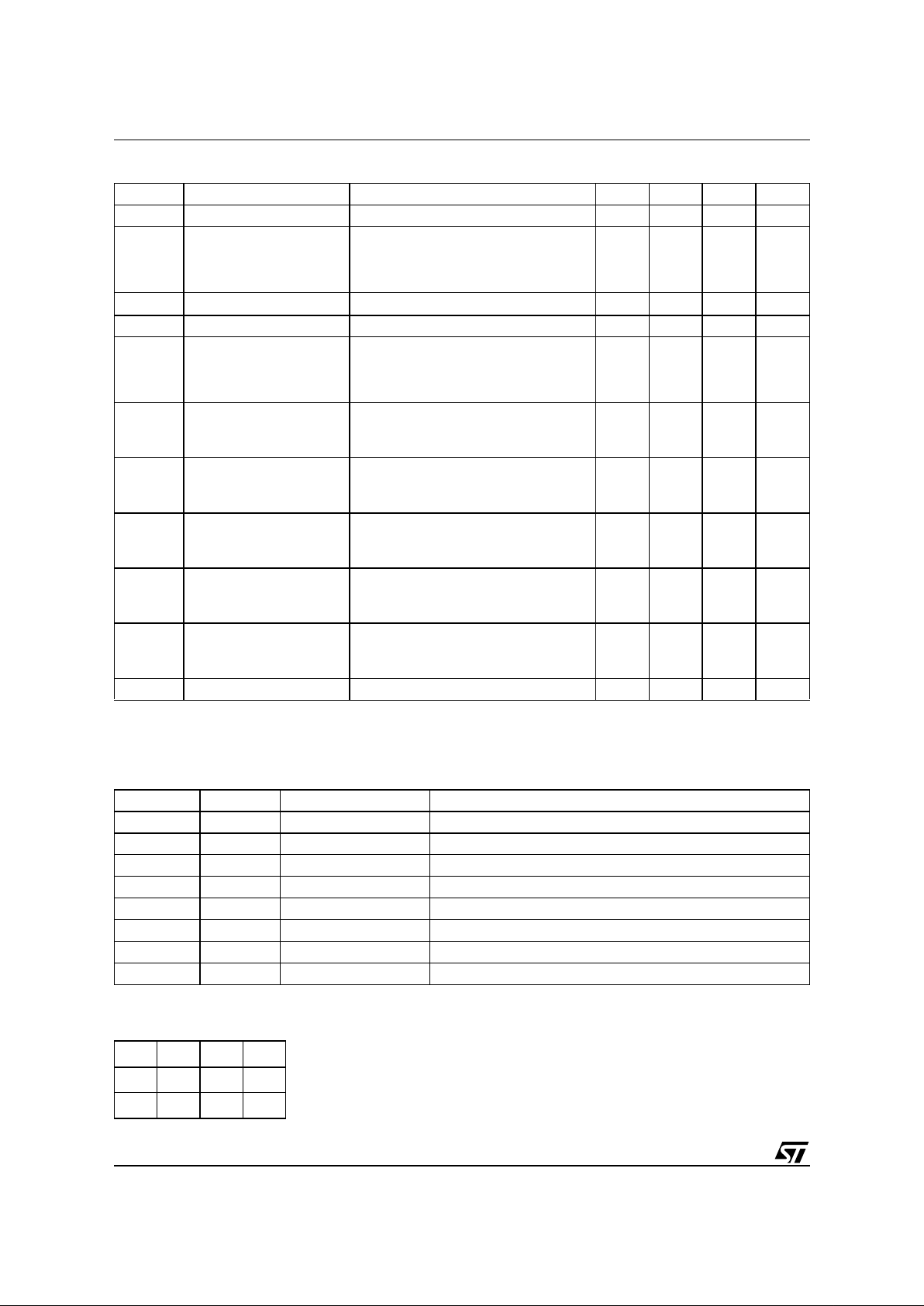

PINOUT

Pin Number Symbol Description Evaluation circuit components

1 RFin RF input L2 = 3.3nH, C2 =0.5pF

2 Gnd Ground

3 Vcc Voltage supply C4 = 4pF, L1 = 110nH, C7 = 10nF

4 ARLNA0 Enable for power down C3 = 10nF

5 RFout RF output C9 = 3pf, L3 = 5.6nH, C10 = 10nF, C11 = 100pF, L4 = 110nH

6 Gnd Ground

7 GC1 Gain selection C5 = 10nF

8 GC2 Gain selection C8 = 10nF

GAIN SELECTI0 N

G

p1Gp2Gp3

GC1 001

GC2 011

3/7

STB7002

TEST CIRCUIT SCHEMATIC

RF_IN

1

GND

2

VCC

3

ARLNA0

4

GC2

8

GC1

7

GND

6

RF_OUT

5

STB7002

U1

C4

4p

C7

10n

C2

0.5p

C8

10n

C5

10n

C9

3p

C10

10n

C11

100p

C3

10n

L1

110n

L2

3.3n

*

VCC

L3

5.6n

L4

110n

VCC

1

2

JP1

BIAS

C6

4u7

VCC

S2

SW SPDT

S1

SW SPDT

S3

SW SPDT

VCC

VCC

VCC

J1

SMA_IN

J2

SMA_OUT

RF_IN

1

GND

2

VCC

3

ARLNA0

4

GC2

8

GC1

7

GND

6

RF_OUT

5

STB7002

U1

C4

4p

C7

10n

C2

0.5p

C8

10n

C5

10n

C9

3p

C10

10n

C11

100p

C3

10n

L1

110n

L2

3.3n

*

VCC

L3

5.6n

L4

110n

VCC

1

2

JP1

BIAS

C6

4u7

VCC

S2

SW SPDT

S1

SW SPDT

S3

SW SPDT

VCC

VCC

VCC

J1

SMA_IN

J2

SMA_OUT

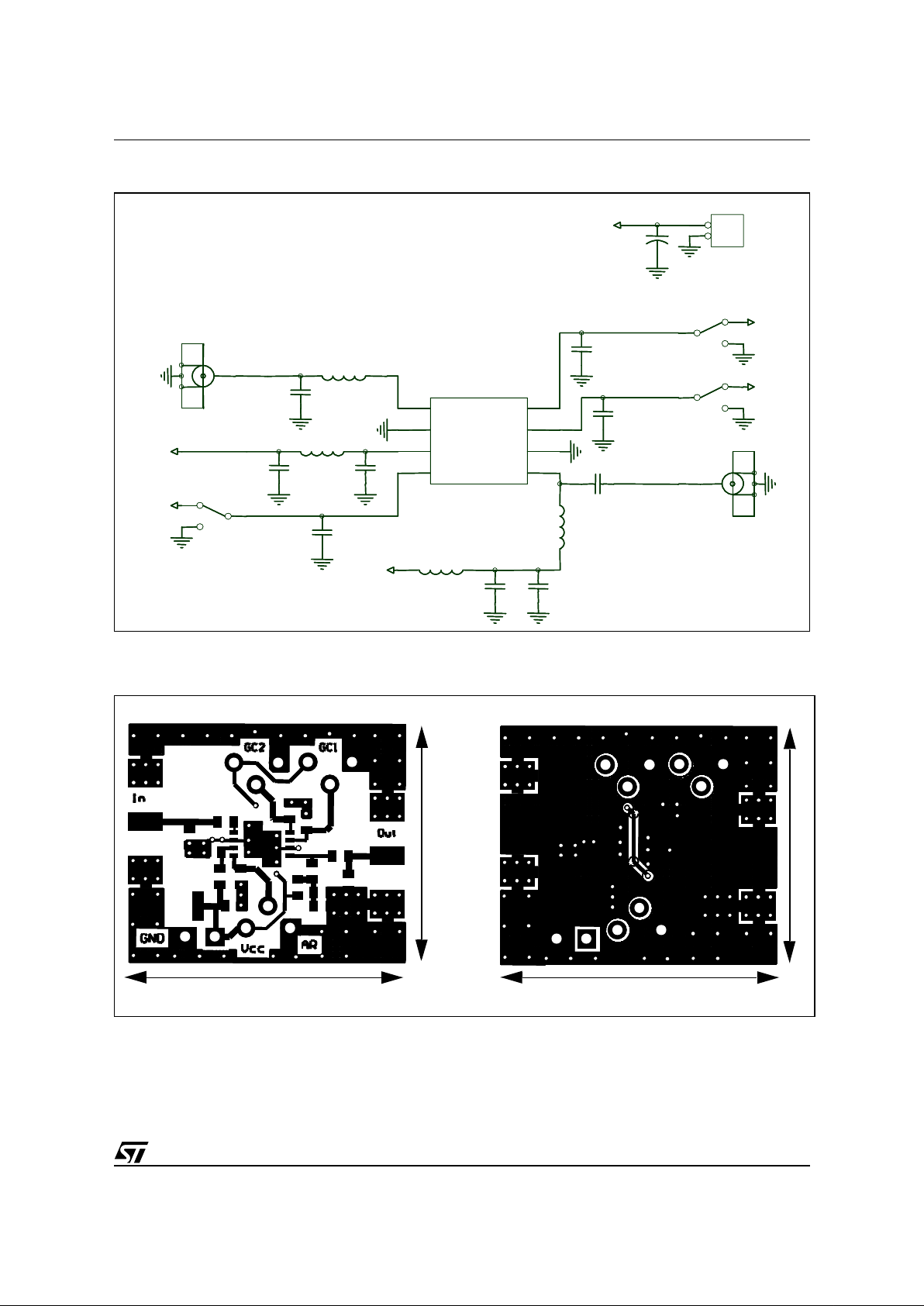

TEST CIRCUIT PHOTOMASTER (board dimention s 23.5x20. 3mm )

BOTTOM VIEW

23.5mm

20.3mm

TOP VIEW

23.5mm

20.3mm

Loading...

Loading...