■ ONE CHIP SYSTEM TO INTERFACE

ACTIVEANTENNA TO ST20GP1

MICROCONTROLLER

■ COMPLETERECEIVERUSINGNOVEL

DUAL CONVERSION ARCHITECTURE WITH

SINGLEIF FILTER

■ MINIMUMEXTERNAL COMPONENTS

■ COMPATIBLEWITH GPS L1 SPS SIGNAL

■ INTERNALLY STABILISEDPOWERRAILS

■ CMOSOUTPUTLEVELS

■ FROM 3.3 TO 5.9V SUPPLY VOLTAGE

■ TQFP32PACKAGE

DESCRIPTION

The STB5600, using STMicroelectronics HSB2,

High Speed Bipolar technology, implements a

GlobalPositioningSystem RF front-end.

The chipprovidesdown conversionfrom the GPS

(L1) signalat 1575 MHz via an IF of 20MHz to an

output frequency of 4MHz suitable for ST20GP1

GPS processor.

It uses a single external reference oscillator to

generate both RF local oscillator signals and the

processorreference clock.

STB5600

GPS RF FRONT-END IC

TQFP32

MARKING:

STB5600

TRACEAB. CODE

ASSY CODE

PIN CONNECTION (top view)

August 1998

1/10

STB5600

FUNCTIONAL DESCRIPTION

The STB5600 GPS front-end is fed with the signal from an active antenna, via a ceramicRF filter. The

gain between the antenna element and the STB5600 is expected to be between 10dB and 35dB

overall,made up of the antenna LNAgain, the feeder loss, connectorloss,and the ceramicfilterloss.

In order to use an off-the-shelfceramic filter, conventionally50 Ohms single ended, a matchingcircuit is

used. (see appendixA.1), which provides a 300 Ohm differential drive to the STB5600. A similar circuit

can be used to feed the LO signalif using the recommendedlow-costoscillator circuit (appendix A.3).

Note that the STB5600 radio architecture and the oscillator described here are covered by various

patents held by SGS-Thomson and by others.The use of the circuits described in this data-sheetfor any

other purpose may infringe such patents.

- RF SECTION

The differential input signal is amplified by the RF-Amp and mixed with the oscillator signal amplified

from the LO+,LO- inputs to generate a balanced 20.46MHz IF signal. The LO buffer amplifier may be

fed differentialor single ended signals, at levelsbetween -60dBmand -20dBm .

- IF SECTION

The 20MHz differentialsignal from the mixer is fed throughan external LC filter to suppressundesirable

signals and mixer products. The multi-stage high-sensitivity limiting amplifier is connected to a D-type

latch clocked by an internallyderived 16MHz clock.. The effect of sampling the 20MHz signal at 16MHz

is to create a sub-samplingalias at 4MHz. Thisis fedto the outputlevel-converters.

- DIVIDER SECTION

The 80MHz oscillator signal may be provided single-ended or differentially to the high impedance

80MHz+, 80MHz- inputs. Any unused inputs should be connected to GNDLOGIC via a 1nF capacitor.

The 80MHz signal is amplified, then divided by 5 to create the 16.368MHz clock required by the

ST20GP1processor, alsoused to clock the outputlatch of the STB5600.

- OUTPUT SECTION

The output latch samples the 20.46MHz intermediate frequency at a 16.368MHz rate, performing the

dual function of second downconversion and latching. The downconversion occurs by sub-sampling

aliasing, such that the digital output representsa 4.096MHzcentrefrequency

The output buffers perform level translation from the internal ECL levels to CMOS compatible outputs

referred to external ground.

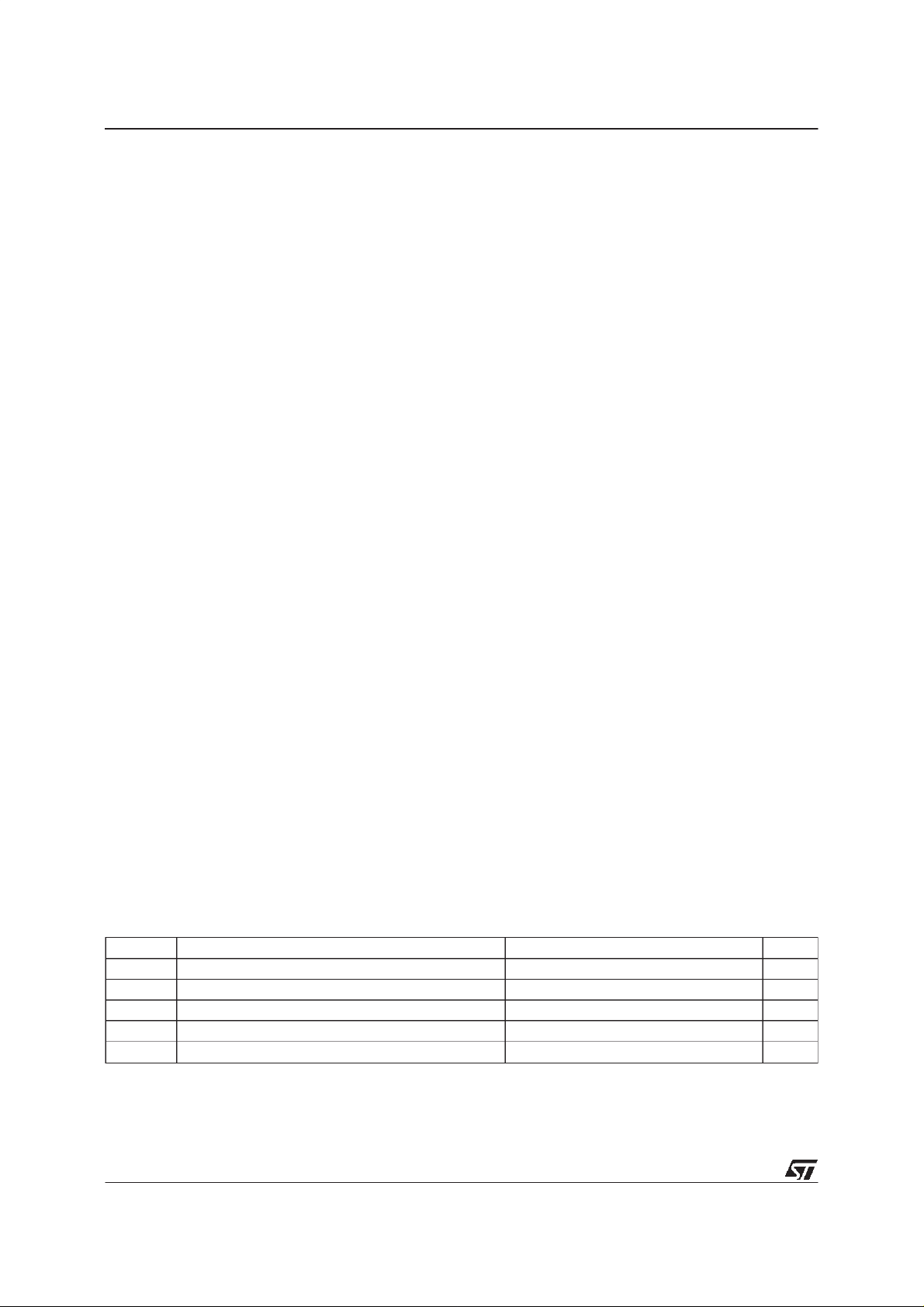

ABSOLUTE MAXIMUM RATINGS

Symb o l Parame t er Val u e Uni t

V

RF+, RF- RF Input 8 dBm

T

R

thj-amb

2/10

DC Supply Voltage 5.9 V

CC

Junct ion Temperature 150

T

j

Stora ge Temperature Range -40 to 125

stg

Therma l Resi s t ance Junction-ambient 80

o

o

o

C/W

C

C

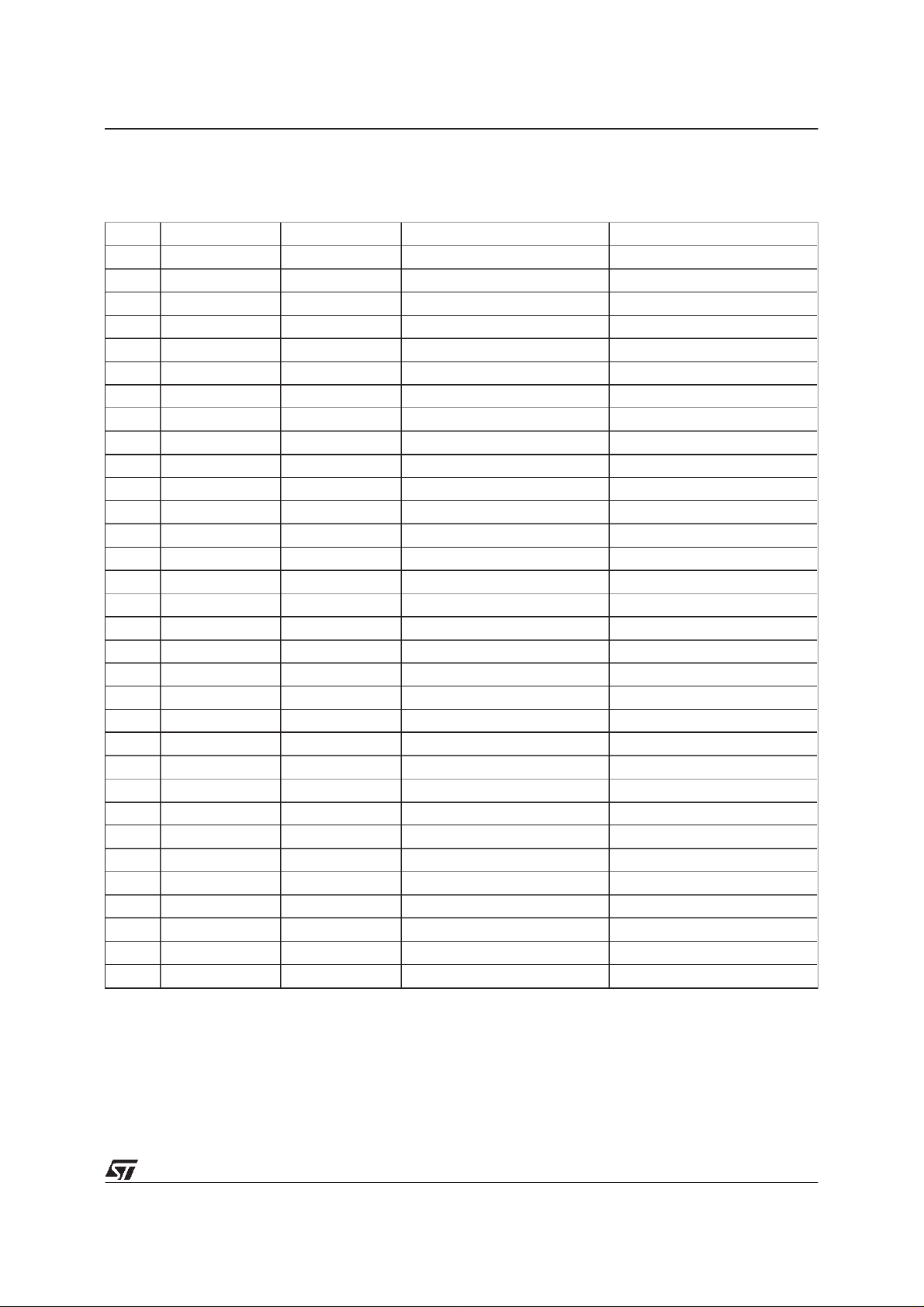

PIN CONFIGURATION

STB5600

Apply5V at the CE, V

CCRF,VCCIF,VCCLOGIC

pins, apply 3 V at the V

CCDRIVE

Pin Symb o l Typ . DC Bi as Dexrip tion External ci rc u i t

1 IF 1+ 3.6 V Mixer Out put 1 see a pplic a ti on circ uit

2 IF1- 3.6 V Mixer Out put 2 see a pplic a ti on circ uit

3V

CCRF

5 V RF P ow er Supply 100 nF to V

4 RF+ 3.5 V RF I npu t AC Coup led

5 RF- 3.5 V RF Input AC Coupled

6V

7V

CCRF

EERF

5 V RF P ow er Supply 100 nF to VEERF

2 V RF V o lt age Refer en ce 100 nF to V CC RF

8 GNDRF 0 V RF Gr ound

9V

CCRF

5 V RF P ow er Supply 100 nF to VEERF

10 LO+ 3.5 V Local Oscillat or Input AC C oupled

11 LO- 3.5 V Local Os ci llat or I n put AC C oupled

12 V

13 V

CCRF

CCLOGIC

5 V RF P ow er Supply 100 nF to VEERF

5 V Logic P o wer Supply 100 nF to V EELOGI C

14 8 0 M Hz+ 4 V 80 MH z Clock I np ut AC C oupled

15 80 MHz- 4 V 80 MHz Clock Inp ut AC C oup led

16 V

17 V

CCLOGIC

EELO GI C

5 V Logic P o wer Supply 100 nF to V EELOGI C

2 V Logic Voltage Refere nc e 100 nF to V CCLOGIC

18 CLOCK + 0 .3 V or 3 V 16 M Hz Cl ock CM O S O u t put 7 p F to GND

19 Not Connected

20 GND

DRIVE

0 V CMOS Drive Gro und

21 DAT A 0.3 V or 3 V 4 M H z Dat a CMOS Out put 7 p F to GND

22 GND

23 V

CCDR I VE

DRIVE

0 V CMOS Drive Gro und

3 V CMOS Drive Po wer Supply

24 CE 3 V Chip E nable

25 GND 0 V Substrat e Gr ound

26 GND

27 GND

28 V

29 V

EEIF

CCIF

LOGIC

IF

0 V Logic Ground

0 V IF G round

2 V IF Voltage Reference 100 nF to VCCI F

5 V IF P ow er Supply 100 nF to V EE I F

30 IF2- 4 V Limit ing A mplifier I nput see a pplic a ti on circ uit

31 I F 2+ 4 V Limiting Am p lif ier I nput see a pplic a ti on circ uit

32 V

CCIF

5 V IF P ow er Supply 100 nF to V EE I F

EERF

DRIVE

DRIVE

3/10

Loading...

Loading...