Page 1

.

HALF DUPLEX ASYNCHRONOUS 2400bps

FSK MODEM

.

Tx CARRIER FREQUENCY SYNTHESIZED

FROM EXTERNAL CRYSTAL

.

LOW DISTORTION Tx SIGNAL

.

Rx SENSITIVITY BETTER THAN 1mV

.

CARRIER DETE CT ION

.

WATCH-DOG INPUT

.

RESET AND MASTER CLOCK OUTPUTS

FOR MICROCONTRO LLER

.

POWER AMPLIFIER BIAS CURRENT CONTROL (HIGH IMPEDANCE IN Rx MODE)

.

SIMPLE AND ECONOMICAL APPLICATION

SCHEMATICS

.

COMPATIBLE WITH CENELEC EN 50065-1

AND FCC SPECIFICATION

.

CARRIER DETECT CLAMPING ON RxD

PROGRAMMABLE (ALLOWING DEMODULATION ON VERY LOW RECEIVE LEVEL,

1mV

TYPICAL LY)

RMS

RMS

ST7537HS1

HOME AUT O MATION MO DE M

PLCC28

(Plastic Chip Carrier)

ORDER CODE : ST7537HS1

DESCRIPTIO N

The ST7537HS1 is a half duplex asynchronous

FSK MODEM designed for home automation communication on the domestic electric mains which

complies with the EN 50065-1 CENELEC standard.

It mainly operates from a 10V power supply and a

5V power supply for the microcontroller digital interface.

It is interfaced to the power line by an external

driver, and a transformer (see Application Schematic Diagram). Its data transmission rate is

2400 bps and its carrier frequency is 132.45kHz.

June 1995

PIN CONNECTIONS

RxFO

RAI

3

4

TxIFI

PAFB

ATO

PABC

PABC

TEST1

TEST2

5

6

7

8

9

10

11

12

TEST3

13

TEST4

AV

DV

DD

2

14

DD

V

DV

CM

1

15

SS

AV

XTAL1

28

16

SS

DEMI

IFO

26

27

25

DV

CC

24

RSTO

23

RxD

22

TxD

21

CD

20

Rx/Tx

19

WD

18

17

MCLK

XTAL2

7537H-01.EPS

1/9

Page 2

ST7537HS1

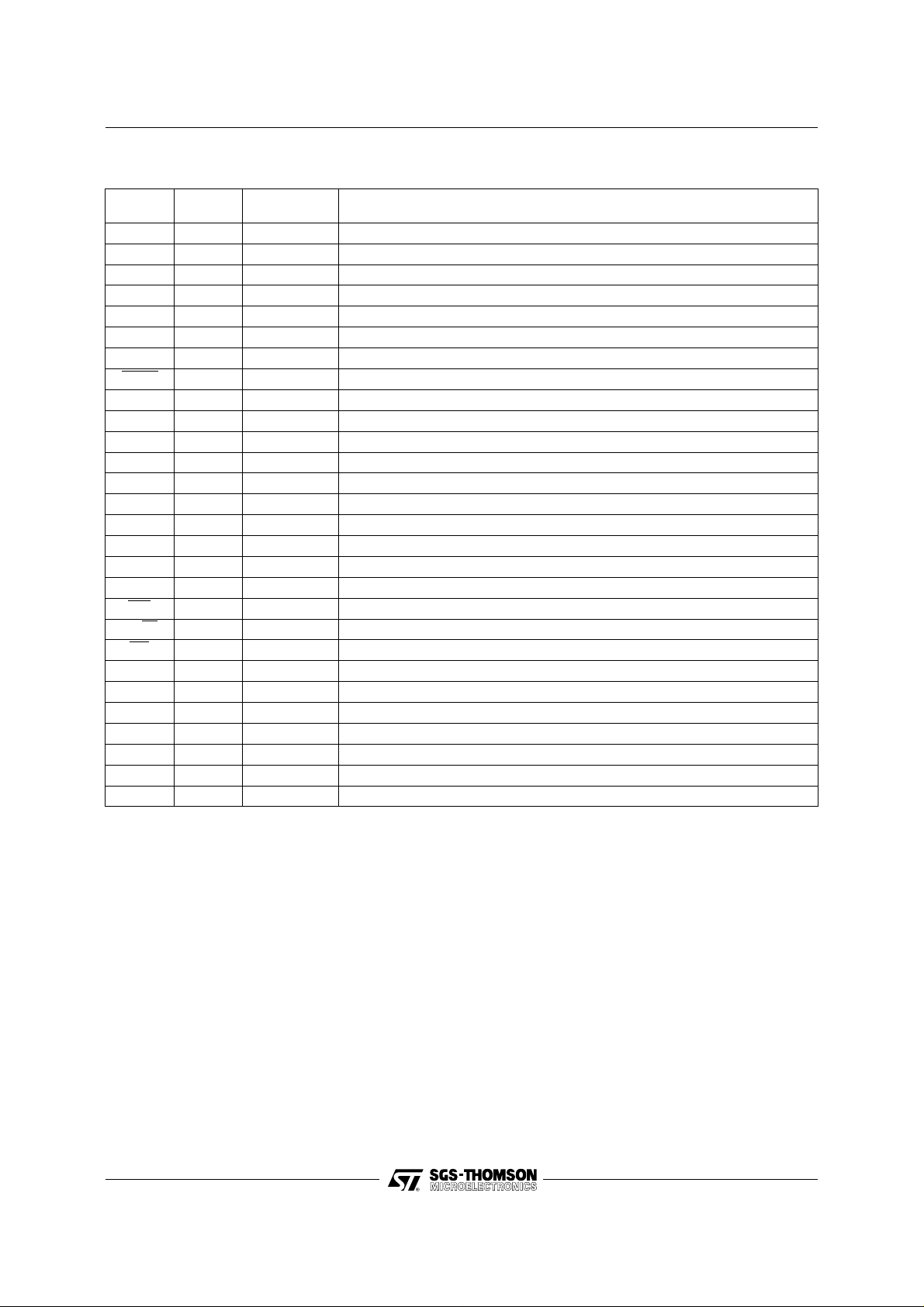

PIN DESCRIPTION

Pin

Name

V

CM

AV

DD

RAI 3 Analog Receive Analog Input

RxFO 4 Analog Receive Filter Output

TxIFI 5 Analog Transmit and Intermediate Frequency Filters Test Input (mode TEST3)

PAFB 6 Analog Power Amplifier Feed-back Input

ATO 7 Analog Analog Transmit Output

PABC 8 Digital (10V) Power Amplifier Bias Current Control Complementary Output

PABC 9 Digital (10V) Power Amplifier Bias Current Control Output

TEST1 10 Digital Tx to Rx Automatic Mode Switching Control Input

TEST2 11 Digital Automatic Mode Switching Time and Watch-dog Time Reduction Control Input

TEST3 12 Digital TxIFI Selection Input

TEST4 13 Digital Undelayed Reset Input

DV

DD

DV

SS

XTAL1 16 Digital (10V) Crystal Oscillator Input

XTAL2 17 Digital (10V) Crystal Oscillator Output

MCLK 18 Digital Master Clock Output

WD 19 Digital Watch-dog Input

Tx 20 Digital Rx or Tx Mode Selection Input

Rx/

CD 21 Digital Carrier Detect Output

TxD 22 Digital Transmit Data Input

RxD 23 Digital Receive Data Output

RSTO 24 Digital Reset Output

DV

CC

IFO 26 Analog Intermediate Frequency Filter Output

DEMI 27 Analog Demodulator Input

AV

SS

Pin

Number

Pin

Type

1 Analog Common Mode Voltage

2 Supply Analog Power Supply : 10V ±5 %

14 Supply Digital Power Supply : 10V ±5%

15 Supply Digital Ground : 0V

25 Supply Digital Buffers Supply Voltage : 5V ±5 %

28 Supply Analog Ground : 0V

Description

7537H-01.TBL

2/9

Page 3

BLOCK DIAG RAM

AV

DD

2 14 28 15 1 25

DV

DD

AV

DV

SS

SS

V

CM

DV

ST7537HS1

CC

RAI

RxFO

CD

ATO

PAFB

PABC

PABC

RxD

3

4

21

7

6

9

8

23

TEST1 TEST2 TEST3 TEST4

Rx BAND-PASS

A.A.

FILTER

CARRIER

DETECTION

OUTPUT

AMPLIFIER

TEST LOGIC

S.C. FILTER

SMT.

FILTER

SMT.

FILTER

REFERENCE

Tx BAND-PASS

S.C. FILTER

13121110

20dB GAIN

VOLTAGE

TRANSMIT SECTION

The transmit mode is set when Rx/

Tx = 0, if R x/Tx

is held at 0 longer than 1 second, then the device

switches automatically in the Rx mode. A new

activation of the Tx mode requires Rx/

Tx to be

returned to 1 for a minimum 2 microsecond period

before being set to 0.

The Transmit Data (TxD) enter asynchronously the

FSK modulator with a nominal intra-message data

rate of 2400 bps.

The basic transmit frequencies are :

- f(TxD=0) = 133.05kHz

- f(TxD=1) = 131.85kHz

These frequencies are synthesized from a

11.0592MHz crys tal oscillator; their precis ion is the

same as the crystal one’s (100ppm).

The modulated signal coming out of the FSK modulator is filtered by a switched-capacitor band-pass

filter (Tx band-pass) in order to limit the output

spectrum and to reduce the level of harmonic components.

The final stage of t he Tx path co nsists of an operational amplifier which needs a feed-back signal

(PAFB) from the power amplifier as shown on

Application Schematic Diagram.

In Tx mode the Rec eive Data (R xD) signa l is set to 1.

MUX

POST-DEMO

S.C. FILTER

MUX

A.A. FILTER

A.A. FILTER

CORRELATOR

FSK DEMODULATOR

I.F. BAND-PASS

S.C. FILTER

MODULATOR

SMT.

FILTER

TIME BASE

RESET LOGIC

CONTROL LOGIC

FSK

IFO

26

17

XTAL2

16

XTAL1

18

MCLK

19

WD

24

RSTO

20

Rx/Tx

22

TxD

TxIFI

5

27

DEMI

ST7537HS1

RECEIVE SECTION

The receive section is active when Rx/

Tx = 1.

The Rx signal is applied on RAI and filtered by a

band-pass switched capacitor filter (Rx b and-pass)

centered on the carrier frequency and whose bandwidth is around 12kHz.

The Rx filter output is amplified by a 20dB gain

stage which provides symetrical limitations for

large voltage. The resulting signal is down-converted by a mixer which receives a local oscillator

synthesized by the FSK modulator block. Finally an

intermediate frequency band-pass filter (IF bandpass) whose central frequency is 5.4k Hz improves

the signal to noise ratio before entering the FSK

demodulator.

The coupling of the intermediate frequency filter

output (IFO) to the FSK demodulator input (DE MI)

is made by an external capacitor C5 (100nF ±10%,

10V) which cancels the Rx path offset voltage.

The RxD output delivers the demodulated signal if

the carrier detect (

high level when

CD) signal is low and is set to

CD = 1.

The RxD output can delivers the demodulated

signal whatever the lev el of

CD (0 or 1) if R x/Tx = 1

and TxD = 0 (see Figure 1).

7537H-02.EPS

3/9

Page 4

ST7537HS1

Figure 1 : Data Timing Chart

Rx/Tx

CD

TxD

RxD

DATA DATA

ADDITIONAL DIG ITAL AND ANALOG F UN CTIONS

Time base

A time base section delivers all the internal clocks

from a crystal oscillator (1 1.0592MHz). The cryst al

is connected between XT AL1 and XT AL2 pins and

needs two external capacitors C3 and C4 (22pF

±10%, 10V) for proper operation.

Reset and watch-dog

The reset output (RSTO) is driven high when the

supply voltage is low er than Vrh (typically 7.6V) with

an hysteresis V rh-V rl (typically 300m V) or when n o

negative transition occurs on the watch-dog input

(

WD) for more than 1.5 second (see the timing

chart on Figure 2). When a reset occurs RSTO is

held high for at least 50ms.

Signal detection

The Carrier Detect output (

CD) is driven low when

the input signal amplitude on RAI is greater than

V

for at least TCD (typically 6ms see the timing

CD

chart on Figure 3). When the input signal desappears or becomes lower than V

for at least T cd before returning to a high level. V

, CD is held low

CD

CD

is the carrier detection threshold voltage which is

set internally to detect 5mV

RMS

typically.

External power amplifier bias control

Two dedicated digital output (PABC and

PAB C)

delivering a signal between 0V and 10V are driven

low respectively hi gh, when the circuit is set in the

receive mode (Rx/

Tx=1) or when the transmit mo de

time out (1 second) is exceeded; in the same time

the output A TO is put in a high impedance state.

TEST IN G FEATURE S

- An additionnal amplifier allows the observation of

the Rx band-pass filter output on pin RxFO.

- A direct input to the Tx b and-pass filter and to the

IF filter (TxIFI) is selected when TEST3 = 1.

- The 1 second normal duration of the Tx to Rx

mode automatic switching is reduced to 488µs

and the 1.5 second watch-dog time out is reduced

to 46.3µs when TEST2 = 1.

- When TEST1 = 1 the Tx to Rx mode automatic

switching is desactivated and the functional mode

of the circuit is fully controlled by Rx/

Tx.

- TEST4 is a reset input which allows an undelayed

control of RSTO and of the internal state of the

circuit.

POWER SUPPLIES WIRING PRECAUTIONS

The ST7537HS1 has two positive power supply

terminals (AV

(AV

,DVSS) in order to separate internal analog

SS

,DVDD) and two ground terminals

DD

and digital supplies. The analog and digital terminals of each supply pair must be connected together externally for proper operation.

The V

must be protected against s hort -circuit for

DD

proper operation.

7537H-03.EPS

4/9

Page 5

ST7537HS1

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

/DVDDSupply Voltage (1) - 0.3, + 12 V

AV

DD

V

V

O

V

O

I

O

V

V

O

I

O

P

D

T

oper

T

stg

Notes : 1. The voltages are referenced to AV

GENERAL ELECTRICAL CHARACTERISTICS

(A/DV

DD

Symbol Parameter Test Conditions Min. Typ. Max. Unit

AV

DD

DV

DD

AI

+

DD

DI

DD

DV

CC

DI

CC

V

IH

V

IL

V

OH

V

OL

DC Duty Cycle MCLK Output, C

Digital Input Voltage DVSS - 0.3, DVDD + 0.3 V

I

Digital Output Voltage (microcontroller interface) DVSS - 0.3, DVCC + 0.3 V

Digital Output Voltage (PABC and PABC) DVSS - 0.3, DVDD + 0.3 V

Digital Output Current - 5, + 5 mA

Analog Input Voltage AVSS - 0.3, AVDD + 0.3 V

I

Analog Output Voltage AVSS - 0.3, AVDD + 0.3 V

Analog Output Current - 5, + 5 mA

Power Dissipation 500 mW

Operating Temperature 0, + 70

Storage Temperature - 55, + 150

and DVSS.

2. Absolute maximum ratings are values beyond which damage to device may occur . Functio nal operation under

these conditions is not implied.

= 10V, A/DVSS = 0V, DVCC = 5V and 0oC ≤ T

SS

≤ 70oC, unless otherwise specificied)

amb

Supply Voltage 9.5 10 10.5 V

Supply Current 30 mA

Digital Output Supply Voltage 4.75 5.25 V

Digital Output Supply Current 1.5 mA

High Level Input Voltage Digital Inputs 4.2 V

Low Level Input Voltage Digital Inputs 0.8 V

High Level Output Voltage IOH = -100µA

• Digital Outputs

• Digital Outputs PABC and PABC

4.9

9.8

Low Level Output Voltage IOL = 100µA

• Digital Outputs

• Digital Outputs PABC and PABC

= 15pF 40 60 %

L

0.1

0.2VV

o

C

o

C

7537H-02.TBL

V

V

7537H-03.TBL

TRANSMITTER ELECTRICAL CHARACTERISTICS

(A/DV

Symbol Parameter Test Conditions Min. Typ. Max. Unit

= 10V, A/DVSS = 0V, DVCC = 5V and 0oC ≤ T

DD

VTAC Max Carrier Output AC Voltage

HD2 Second Harmonic Distortion - 50 dB

HD3 Third Harmonic Distortion - 60 dB

= 5.6kΩ

R

L

RL(AVSS) = 5.6kΩ

R(ATO, PAFB) = 1kΩ

≤ 70oC, unless otherwise specificied)

amb

0.8 1.0 1.3 V

FD FSK Peak-to-peak Deviation 1200 Hz

RMS

7537H-04.TBL

5/9

Page 6

ST7537HS1

RECEIVER ELECTRICAL CHARACTERISTICS

(A/DV

Symbol Parameter Test Conditions Min. Typ. Max. Unit

Note 1 : This parameter is guaranteed by correlation

ADDITIONAL DIGITAL AND ANALOG FUNCT IO NS ELECTRI CAL C HARACTERIST I CS

(A/DV

Symbol Parameter Test Conditions Min. Typ. Max. Unit

= 10V, A/DVSS = 0V, DVCC = 5V and 0oC ≤ T

DD

V

V

R

Input Sensitivity 1 10 mV

IN

Maximum Input Signal 2 V

IN

Input Impedance 15 kΩ

IN

≤ 70oC, unless otherwise specificied)

amb

RMS

GRx Receive Gain f = 132.45kHz 20 dB

BER Bit Error Rate (1) S/N = 15dB, S = 10mV

t

DEM

V

V

V

t

RST

t

t

t

OUT

t

WD

WM

CD

Demodulation Time Alternate 0 , 1 sequence 3 T bit

Carrier Detection Level f = 132.45kHz, sine wave 5 10 mV

CD

= 10V, A/DVSS = 0V, DVCC = 5V and 0oC ≤ T

DD

High Level Reset Voltage See Figure 2 7.9 V

RH

Low Level Reset Voltage See Figure 2 7.6 V

RL

≤ 70oC, unless otherwise specificied)

amb

Reset Time See Figure 2 50 ms

Watch-dog Pulse Width See Figure 2 500 ns

Watch-dog Pulse Period See Figure 2 800 µs

Watch-dog Time Out See Figure 2 1.5 s

Carrier Detection Time See Figure 3 3 6.5 ms

, N : white 10-510

RMS

-3

RMS

RMS

7537H-05.TBL

7537H-06.TBL

Figure 2 : Reset and Watch-dog Timing Chart

V

RH

DV

DD

RSTO

WD

t

RST

Figure 3 : Carrier Detection Timing Chart

V

CD

RAI

t

CD

CD

V

RL

t

OUT

t

WD

t

WM

t

RST

7537H-04.EPS

t

CD

7537H-05.EPS

6/9

Page 7

FILTER TEMPLATES

Receive and Transmit Filter Intermediate FrequencyFilter

Frequency

(kHz)

Min. Typ. Max. Min. Typ. Max.

92 - 30 2.4 - 35

126.45 - 5 - 3 - 2 4.3 - 4 - 3 - 1

Ref 132.45 0 Ref 5.4 0

138.45 - 5 - 3 - 2 6.5 - 5 - 3 - 2

180 - 30 11.6 - 35

Gain (dB)

Frequency

(kHz)

APPLICATION SCHEMATIC INFORMATIONS

RESISTORS CAPACITORS

R1 180Ω C1 1µF Ceramic 50

R2 2.2Ω C2 470nF Paper, class X2

R3 2.2Ω C3 (2) 22pF 10% Ceramic 10V

R4 2.2Ω C4 (2) 22pF 10% Ceramic 10V

R5 2.2Ω C5 100nF 10% Ceramic 10V

R6 180Ω C6 6.8nF 5% Plastic Film 50V

R7 47kΩ C7 100nF Ceramic 10V

R8 1kΩ C8 2.2µF

R9 1kΩ 5% C9 100nF Ceramic 10V

R11 47kΩ C10 2.2µF

INDUCTOR C11 (1) 100nF Ceramic 10V

L1 10µH ≅ 1.5Ω C12 (1) 100nF Ceramic 10V

TRANSISTORS TRANSIL

Q1 : 2N2907

Q2 : 2N2222

Q3 : 2N2222

Q4 : 2N2907

Q5 : 2N2907

Q6 : 2N2222

Notes : 1. These capacitors might not be necessary if the overall power supplies decoupling is sufficient.

2. The value of these capacitors depends on the crystal parameters.

TRL1 : SGS-THOMSON P6KE6V8CP

TRANSFORMER

TR1 : TOKO T1002 N

CRYSTAL

QTZ1 : 11.0592MHz parallel resonance

ST7537HS1

Gain (dB)

7537H-07.TBL

7537H-08.TBL

7/9

Page 8

ST7537HS1

APPLICATION SCHEMATIC DIAGRAM

C7

Q5

Thermal

coupling

+10V

C8

C10

2

14

AV

1

18

19

20

21

22

23

24

25

C12

V

CM

MCLK

WD

Rx/Tx

CD

TxD

RxD

RSTO

DV

CC

AV

28

DDDVDD

DV

SS

SS

15 16 17

C9

INTERFACE

MICROCONTROLLER

5V R7

C5

2627

DEMI IFO

RAI

PAFB

S

T

7

5

3

7

H

S

1

XTAL1 XTAL2

C3 C4

ATO

PABC

PABC

RxFO

TEST1

TEST2

TEST3

TEST4

TXIFI

QTZ1

3

6

7

8

9

4

10

11

12

13

5

R11 R1

R9

R8

R4

R6

R3

Q6

Q1

Q3

R2

R5

Thermal

coupling

Q2

Q4

C11

TRL1

L1

C6

C1

0V

C2

MAINS

50/60Hz

7537H-06.EPS

8/9

Page 9

PACKAGE MECHANICAL DATA

28 PINS - PLASTIC CHIP CARRIE R

ST7537HS1

B

M

M

M1

M1

4

5

21

2628

25

Fe

e3

E

F1

11

12

19

18

D2

A

G

(Seating Plane Coplanarity)

Dimensions

Min. Typ. Max. Min. Typ. Max.

A 12.32 12.57 0.485 0.495

B 11.43 11.58 0.450 0.456

D 4.2 4.57 0.165 0.180

D1 2.29 3.04 0.090 0.120

D2 0.51 0.020

E 9.91 10.92 0.390 0.4 30

e 1.27 0.050

e3 7.62 0.300

F 0.46 0.018

F1 0.71 0.028

G 0.101 0.004

M 1.24 0.049

M1 1.143 0.045

Millimeters Inches

D1

D

PMPLCC28.EPS

PLCC28.TBL

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility

for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result

from its use. No licence is granted by implication or otherwi se under any patent or patent rights of SGS-THOMSON Microelectronics.

Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all

information previously suppli ed. SGS-THOMSON Microele ctronics products are not authorized for use as critical components in life

support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1995 SGS-THOMSON Microelectronics - All Rights Reserved

2

Purchase of I

2

C Patent. Rights to use these components in a I2C system, is granted provided that the system conforms to

I

Australia - Brazil - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco

The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips

2

C Standard Specifications as defined by Philips.

the I

SGS-THOMSON Microelectronics G ROUP OF COMPANIES

9/9

Loading...

Loading...