Rev. 1.0

September 1999 1/125

This ispreliminary information on anew product in development or undergoing evaluation. Details are subject tochange without notice.

ST72334J/N,

ST72314J/N, ST72124J

8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY,

ADC, 16-BIT TIMERS, SPI, SCI INTERFACES

PRODUCT PREVIEW

■ 8K or 16K Program memory

(ROM or Single voltage FLASH)

with read-out protection

■ 256-bytes EEPROM Data memory

■ In-Situ Programming (Remote ISP)

■ Enhanced Reset System

■ Low voltage supply supervisor with

3 programmable levels

■ Low consumption resonator or RC oscillators

and by-passfor external clock source, with safe

control capabilities

■ 4 Power saving modes

■ Standard Interrupt Controller

■ 44 or 32 multifunctional bidirectional I/O lines:

– External interrupt capability (4 vectors)

– 21 or 19 alternate function lines

– 12 or 8 high sink outputs

■ Real time base, Beep and Clock-out capabilities

■ Configurable watchdog reset

■ Two 16-bit timers with:

– 2 input captures(only one on timer A)

– 2 output compares (only one on timer A)

– External clock input on timer A

– PWM and Pulse generator modes

■ SPI synchronous serial interface

■ SCI asynchronous serial interface

■ 8-bit ADC with 8 input pins

(6 only on ST72334Jx,

not available on ST72124J2)

■ 8-bit data manipulation

■ 63 basic instructions

■ 17 main addressing modes

■ 8 x 8 unsigned multiply instruction

■ True bit manipulation

■ Full hardware/software development package

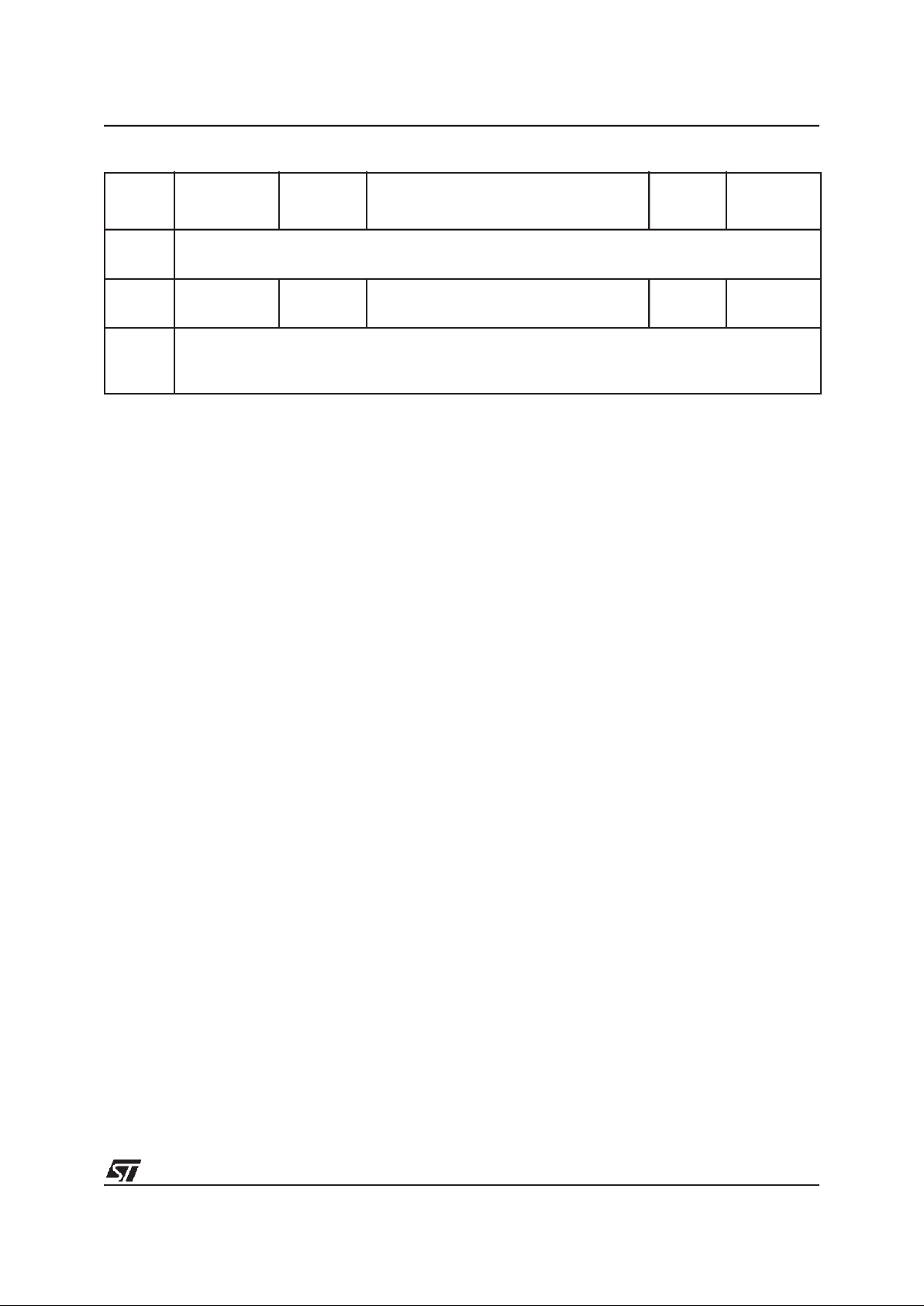

Device Summary

TQFP44

10x10

PSDIP42

PSDIP56

TQFP64

14 x 14

Features ST72124J2 ST72314J2 ST72314J4 ST72314N2 ST72314N4 ST72334J2 ST72334J4 ST72334N2 ST72334N4

Program memory- bytes 8K 8K 16K 8K 16K 8K 16K 8K 16K

RAM (stack) - bytes 384 (256) 384 (256) 512 (256) 384 (256) 512 (256) 384 (256) 512 (256) 384 (256) 512 (256)

EEPROM - bytes - - - --256 256 256 256

Peripherals

Watchdog,

16-bit Tim-

ers, SPI,

SCI

Watchdog, 16-bit Timers, SPI, SCI, ADC

Operating Supply 3.0V to 5.5V

CPU Frequency 500 kHz to 8 MHz (with 1 to 16 MHz oscillator)

Operating Temperature -40°Cto+85°C (-40°C to +105/125°C optional)

Packages TQFP44 / SDIP42 TQFP64 / SDIP56 TQFP44 / SDIP42 TQFP64 / SDIP56

1

Table of Contents

125

2/125

2

1 PREAMBLE: ST72C334 VERSUS ST72E331 SPECIFICATION . . . . . . . . . . . . . ............ 5

2 GENERAL DESCRIPTION . . . . . . ................................................ 6

2.1 INTRODUCTION . . . . . . . . . . . . . ............................................ 6

2.2 PIN DESCRIPTION . . ..................................................... 7

2.3 REGISTER & MEMORY MAP . . . ...........................................12

2.4 FLASH PROGRAM MEMORY . . . . . . . . . . . . .................................. 16

2.4.1 Introduction . . . .................................................... 16

2.4.2 Main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.4.3 Structural organisation . . . . . . . . . . . . . . ................................. 16

2.4.4 In-Situ Programming (ISP) mode . . . . . .................................. 16

2.5 PROGRAM MEMORY READ-OUT PROTECTION . . . . . . . . . . . . . . . . . . ............ 16

2.6 DATA EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ........................... 17

2.6.1 Introduction . . . .................................................... 17

2.6.2 Main Features . . . . . . ...............................................17

2.6.3 Memory Access . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . .................... 18

2.6.4 Data EEPROM and Power Saving Modes . . . . . . . . . . . . . ................... 19

2.6.5 Data EEPROM AccessError Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.6.6 Register Description . . . . . . ........................................... 20

3 CENTRAL PROCESSING UNIT . . ............................................... 21

3.1 INTRODUCTION . . . . . . . . . . . . . ...........................................21

3.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . .............................. 21

3.3 CPU REGISTERS . . . .................................................... 21

4 SUPPLY, RESET AND CLOCK MANAGEMENT . . . . ................................24

4.1 LOW VOLTAGE DETECTOR (LVD) . . . .. . . . . . . . . . ........................... 25

4.2 RESET SEQUENCE MANAGER (RSM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ........26

4.3 CLOCK SECURITY SYSTEM (CSS) . . . . ..................................... 32

4.3.1 Clock Filter Control . . ...............................................32

4.3.2 Safe Oscillator Control . . . . ........................................... 32

4.4 SUPPLY, RESET AND CLOCK REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . 33

4.5 MAIN CLOCK CONTROLLER (MCC) . . . . .................................... 34

5 INTERRUPTS & POWER SAVING MODES . . . . . . . ................................. 36

5.1 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5.2 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ........ 38

5.2.1 Introduction . . . .................................................... 38

5.2.2 HALT Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . ........................... 38

5.2.3 WAIT Mode ....................................................... 40

5.2.4 SLOW Mode . . . . . . . . . . . . . . . . . . . . . . . . .............................. 41

6 ON-CHIP PERIPHERALS . . . . . . . . . . . ...........................................42

6.1 I/O PORTS . . . . . . . . . . . . . . . . . . ...........................................42

6.1.1 Introduction . . . .................................................... 42

6.1.2 Functional Description . . . . ........................................... 42

6.1.3 I/O Port Implementation . .. . . . . . . . . . . . . . . . . ........................... 44

6.1.4 Register Description . . . . . . ........................................... 45

6.2 MISCELLANEOUS REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

6.2.1 I/O Port Interrupt Sensitivity Description . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . 47

Table of Contents

3/125

3

6.2.2 I/O Port Alternate Functions ...........................................47

6.2.3 Miscellaneous Registers Description .................................... 48

6.3 WATCHDOG TIMER (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . 50

6.3.1 Introduction . . . .................................................... 50

6.3.2 Main Features . . . . . . ...............................................50

6.3.3 Functional Description . . . . ........................................... 50

6.3.4 Hardware Watchdog Option . . . . . . . . . . ................................. 51

6.3.5 Low Power Modes . . . ............................................... 51

6.3.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . ................................. 51

6.3.7 Register Description . . . . . . ........................................... 51

6.4 16-BIT TIMER . . . . . . . . . . . . . . . . . . ........................................53

6.4.1 Introduction . . . .................................................... 53

6.4.2 Main Features . . . . . . ...............................................53

6.4.3 Functional Description . . . . ........................................... 53

6.4.4 Low Power Modes . . ............................................... 64

6.4.5 Interrupts . . . . . ....................................................64

6.4.6 Register Description . . . . . . ........................................... 65

6.5 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . ...........70

6.5.1 Introduction . . . .................................................... 70

6.5.2 Main Features . . . . . . ...............................................70

6.5.3 General description . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.5.4 Functional Description . . . . ........................................... 72

6.5.5 Low Power Modes . . . ............................................... 79

6.5.6 Interrupts . . . . . ....................................................79

6.5.7 Register Description . . . . . . ........................................... 80

6.6 SERIAL COMMUNICATIONS INTERFACE (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

6.6.1 Introduction . . . .................................................... 83

6.6.2 Main Features . . . . . . ...............................................83

6.6.3 General Description . . . . . . ........................................... 83

6.6.4 Functional Description . . . . ........................................... 85

6.6.5 Low Power Modes . . . ............................................... 90

6.6.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . ................................. 90

6.6.7 Register Description . . . . . . ........................................... 91

6.7 8-BIT A/D CONVERTER (ADC) . . . . . . . . . . . . . . . . . . ........................... 95

6.7.1 Introduction . . . .................................................... 95

6.7.2 Main Features . . . . . . ...............................................95

6.7.3 Functional Description . . . . ........................................... 95

6.7.4 Low Power Modes . . . ............................................... 96

6.7.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . ................................. 96

6.7.6 Register Description . . . . . . ........................................... 97

7 INSTRUCTION SET . . . . . . . . . . . . . . . . . . ........................................ 99

7.1 ST7 ADDRESSING MODES . . . . . . . . . .. . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.1.1 Inherent . . . . . . . . . . . .............................................. 100

7.1.2 Immediate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . 100

7.1.3 Direct . .......................................................... 100

7.1.4 Indexed (No Offset, Short, Long) . . . . .. . . . . . . .......................... 100

7.1.5 Indirect (Short, Long) . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

7.1.6 Indirect Indexed (Short, Long) . ....................................... 101

Table of Contents

125

4/125

7.1.7 Relative mode (Direct, Indirect) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

7.2 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . ................................102

8 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . ............................. 105

8.1 ABSOLUTE MAXIMUM RATINGS . . . ....................................... 105

8.2 RECOMMENDED OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

8.3 DC ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . ..........107

8.4 GENERAL TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....... 107

8.5 I/O PORT CHARACTERISTICS ............................................108

8.6 SUPPLY, RESET AND CLOCK CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . 109

8.6.1 Supply Manager ................................................... 109

8.6.2 Reset Sequence Manager . . . ........................................ 109

8.6.3 Multi-Oscillator, Clock Security System . . . . . . . . . . . . . . . . . . . . . . . . . . ....... 109

8.7 MEMORY AND PERIPHERAL CHARACTERISTICS . . . . . . . . ................... 111

9 GENERAL INFORMATION . . . . . . . . . . ..........................................117

9.1 PACKAGES . . . . . . . . . . . . . . . . . .......................................... 117

9.1.1 Package Mechanical Data . . . . . . . . . . ................................. 117

9.1.2 User-supplied TQFP64 Adaptor / Socket . . . . . . .......................... 119

9.1.3 User-supplied TQFP44 Adaptor / Socket . . . . . . .......................... 120

9.2 DEVICE CONFIGURATION AND ORDERING INFORMATION . . . . . .............. 121

9.2.1 Option Bytes . . . . . . . . . . . . . . . . . . . . . . . . .............................121

9.2.2 Transfer Of Customer Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . .............. 122

10 SUMMARY OF CHANGES . .................................................. 124

Table of Contents

5/125

1 PREAMBLE: ST72C334 VERSUS ST72E331 SPECIFICATION

New Features available on the ST72C334

■ 8 or 16K FLASH/ROM with In-Situ Programming and Read-out protection

■ New ADC with a better accuracy and conversion time

■ New configurable Clock, Reset and Supply system

■ New power saving mode with real time base: Active Halt

■ Beep capability on PF1

■ New interrupt source: Clock securitysystem (CSS) or Main clock controller (MCC)

ST72C334 I/O Confuguration and Pinout

■ Same pinout as ST72E331

■ PA6 and PA7 are true open drain I/O ports without pull-up (same as ST72E331)

■ PA3, PB3, PB4 and PF2 have no pull-up configuration (all IOs present on TQFP44)

■ PA5:4, PC3:2, PE7:4 and PF7:6 have high sink capabilities (20mA on N-buffer, 2mA on P-buffer and

pull-up). On the ST72E331, all these pads (except PA5:4) were 2mA push-pull pad without high sink

capabilities. PA4 and PA5 were 20mA true open drain.

New Memory Locations in ST72C334

■ 20h: MISCR register becomes MISCR1 register (naming change)

■ 29h: new control/status register for the MCC module

■ 2Bh: new control/status register for the Clock, Reset and Supply control. This register replaces the

WDGSR register keeping the WDOGF flag compatibility.

■ 40h: new MISCR2 register

4

ST72334J/N, ST72314J/N, ST72124J

6/125

2 GENERAL DESCRIPTION

2.1 INTRODUCTION

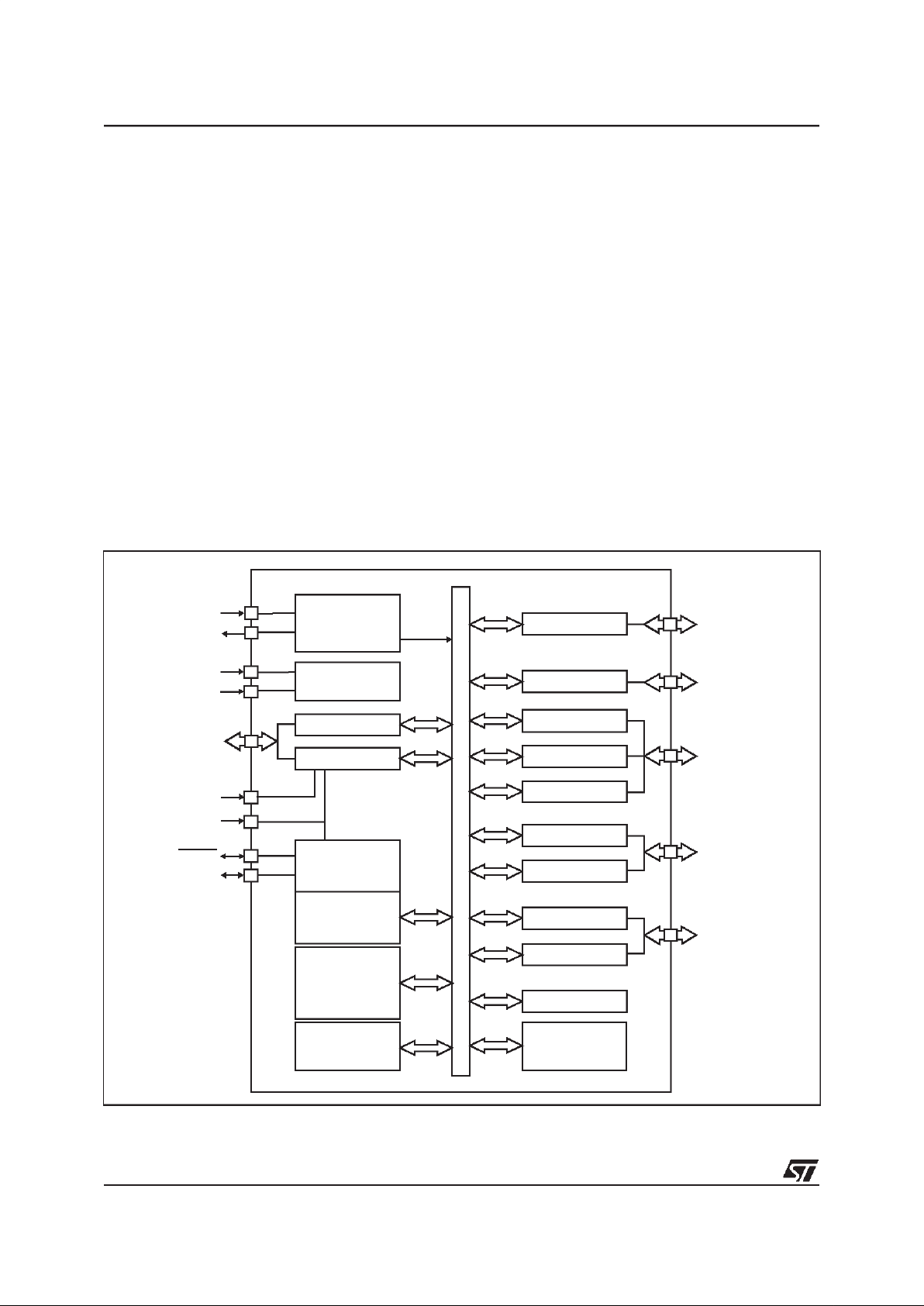

The ST72334J/N,ST72314J/N and ST72124J devices aremembers of the ST7 microcontroller family. They can be grouped as follows:

– ST72334J/Ndevices are designed formid-range

applications with Data EEPROM, ADC, SPI and

SCI interface capabilities.

– ST72314J/N devices target the same range of

applications but without Data EEPROM.

– ST72124J devices are for applications that do

not need Data EEPROM and the ADC peripheral.

All devices are based on a common industrystandard 8-bit core, featuringan enhanced instruction set.

The ST72C334J/N, ST72C314J/N and

ST72C124J versions feature single-voltage

FLASH memory with byte-by-byte In-Situ Programming (ISP) capability.

Under software control, all devices can be placed

in WAIT, SLOW, ACTIVE-HALT or HALT mode,

reducing power consumption when the application

is in idle or standby state.

The enhanced instruction set and addressing

modes of the ST7 offer both power and flexibilityto

software developers, enabling the design ofhighly

efficient andcompact application code. In addition

to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing

modes.

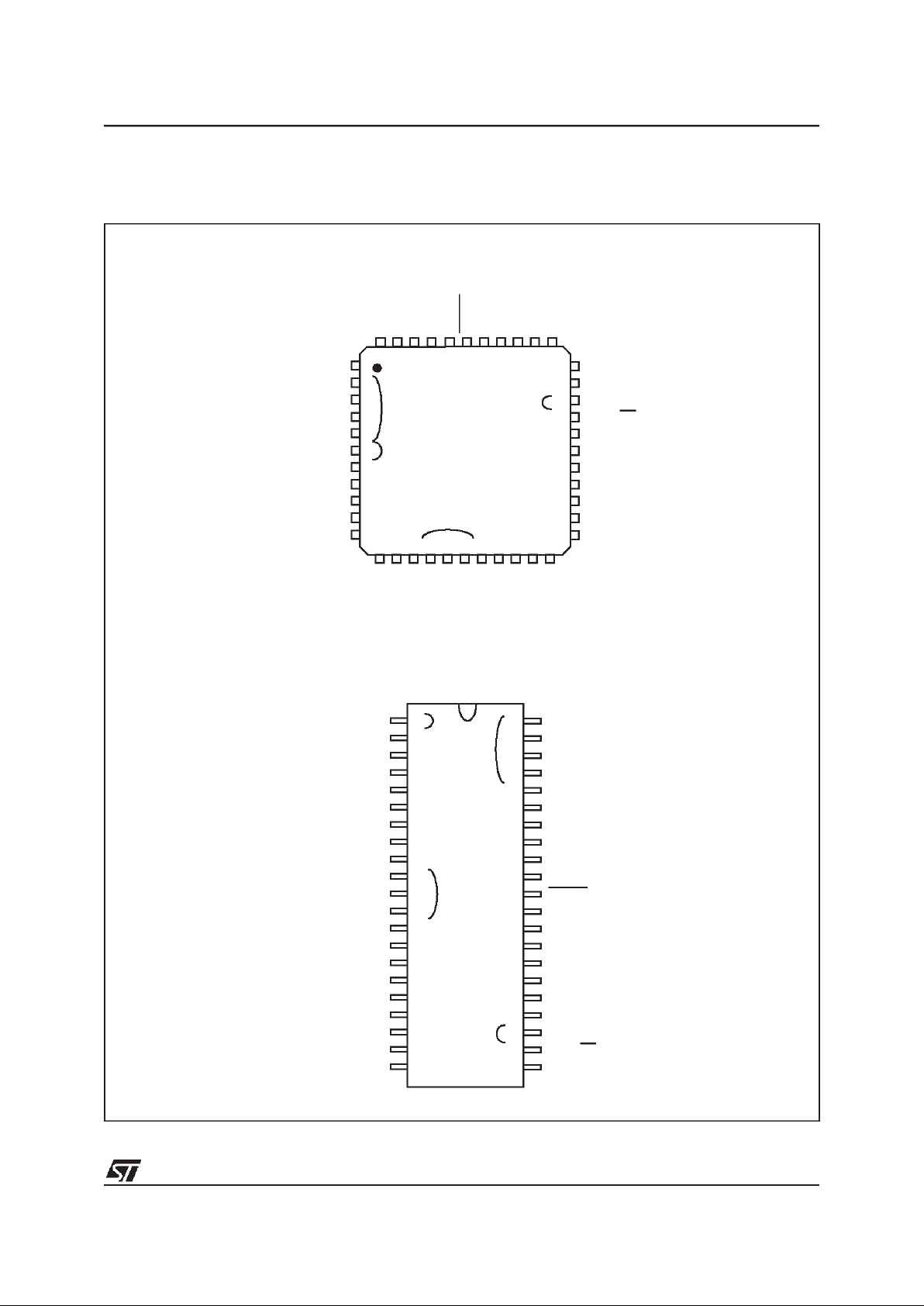

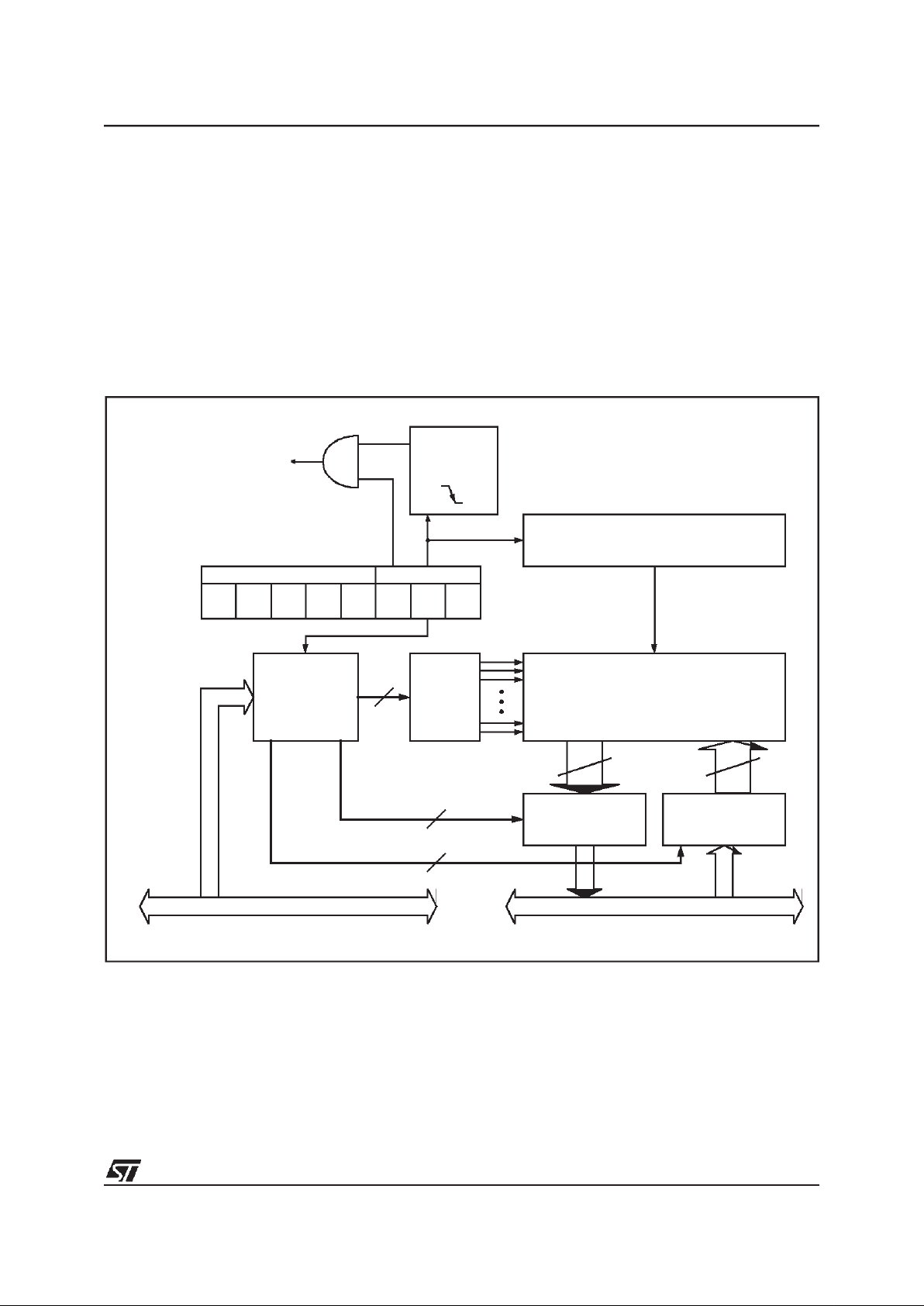

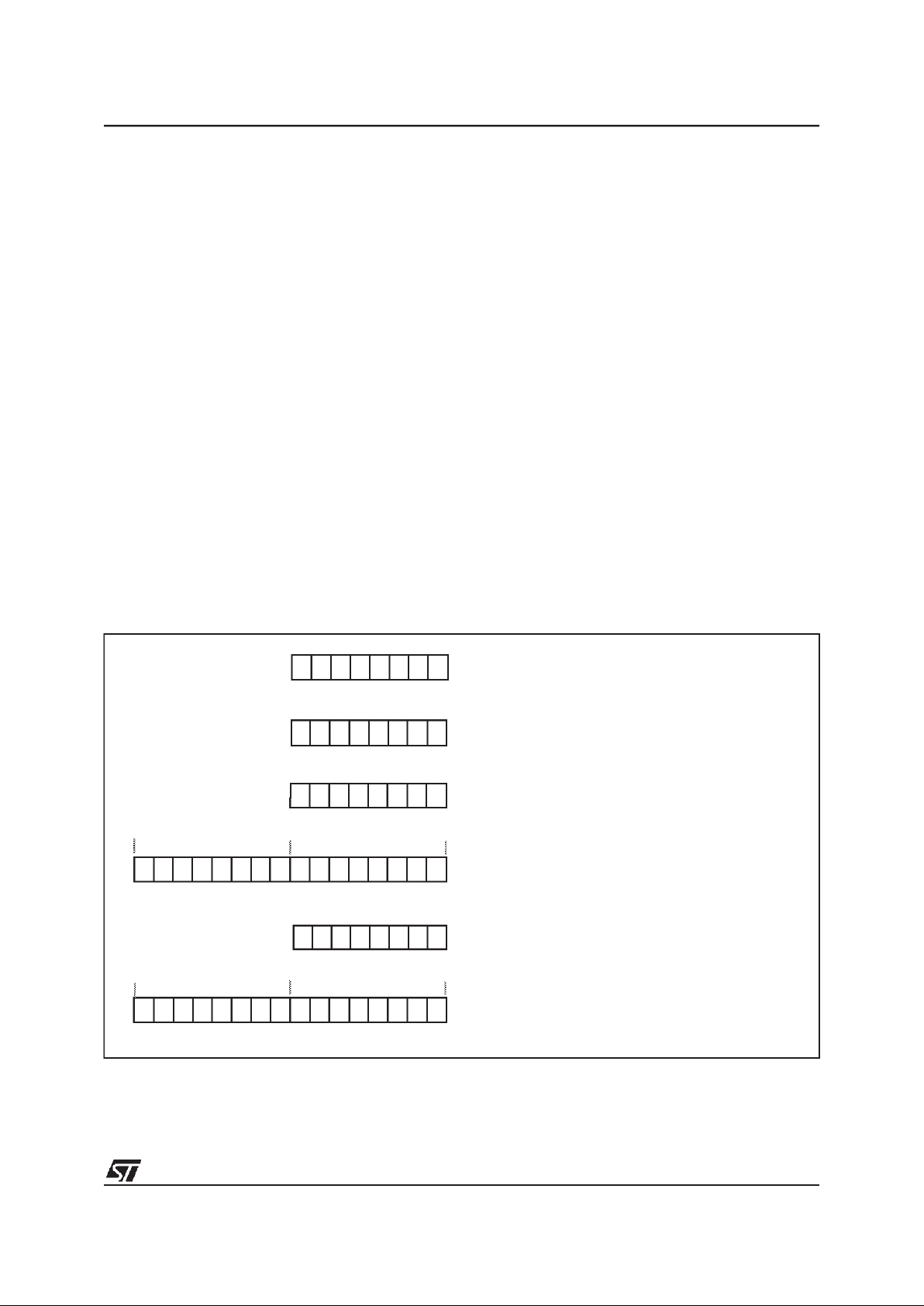

Figure 1. Device Block Diagram

8-BIT CORE

ALU

ADDRESS AND DATABUS

RESET

PORT B

TIMER B

PORT C

SPI

PORT E

SCI

PORT F

TIMER A

WATCHDOG

Internal

CLOCK

CONTROL

RAM

(384 or 512 Bytes)

PORT D

8-BIT ADC

PORT A

V

SSA

V

DDA

Data-EEPROM

(256 Bytes)

AND LVD

PC7:0

V

SS

V

DD

POWER

SUPPLY

PROGRAM

(8 or 16K Bytes)

MEMORY

OSC1

OSC2

MULTI OSC

+

CLOCK FILTER

V

PP

/TEST

(8 bits)

PF7,6,4,2:0

(6 bits)

PE7:0

(6 bits for N versions)

(2 bits for J versions)

PD7:0

(8 bits for N versions)

(6 bits for J versions)

PA7:0

(8 bits for N versions)

(5 bits for J versions)

PB7:0

(8 bits for N versions)

(5 bits for J versions)

5

ST72334J/N, ST72314J/N, ST72124J

7/125

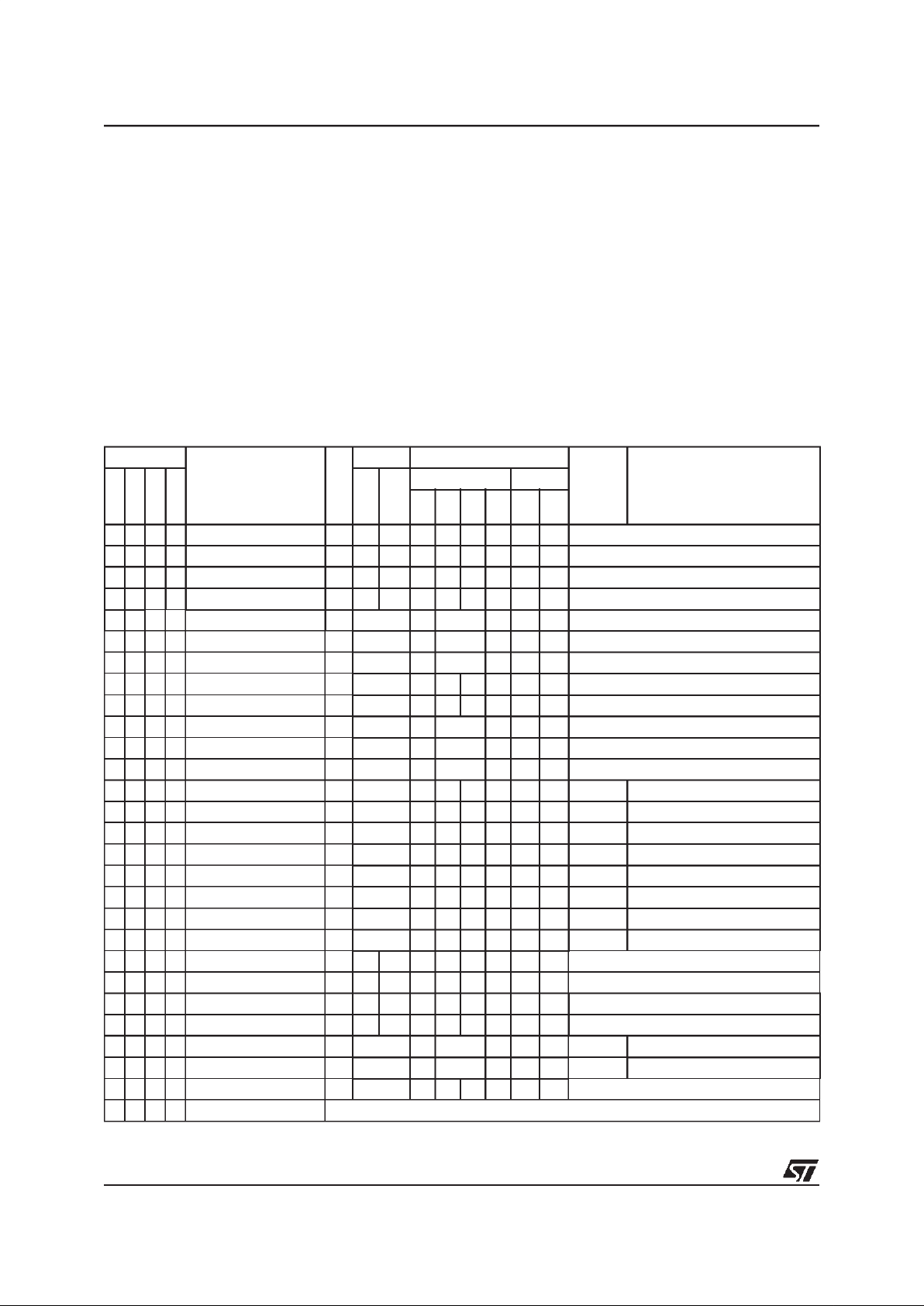

2.2 PIN DESCRIPTION

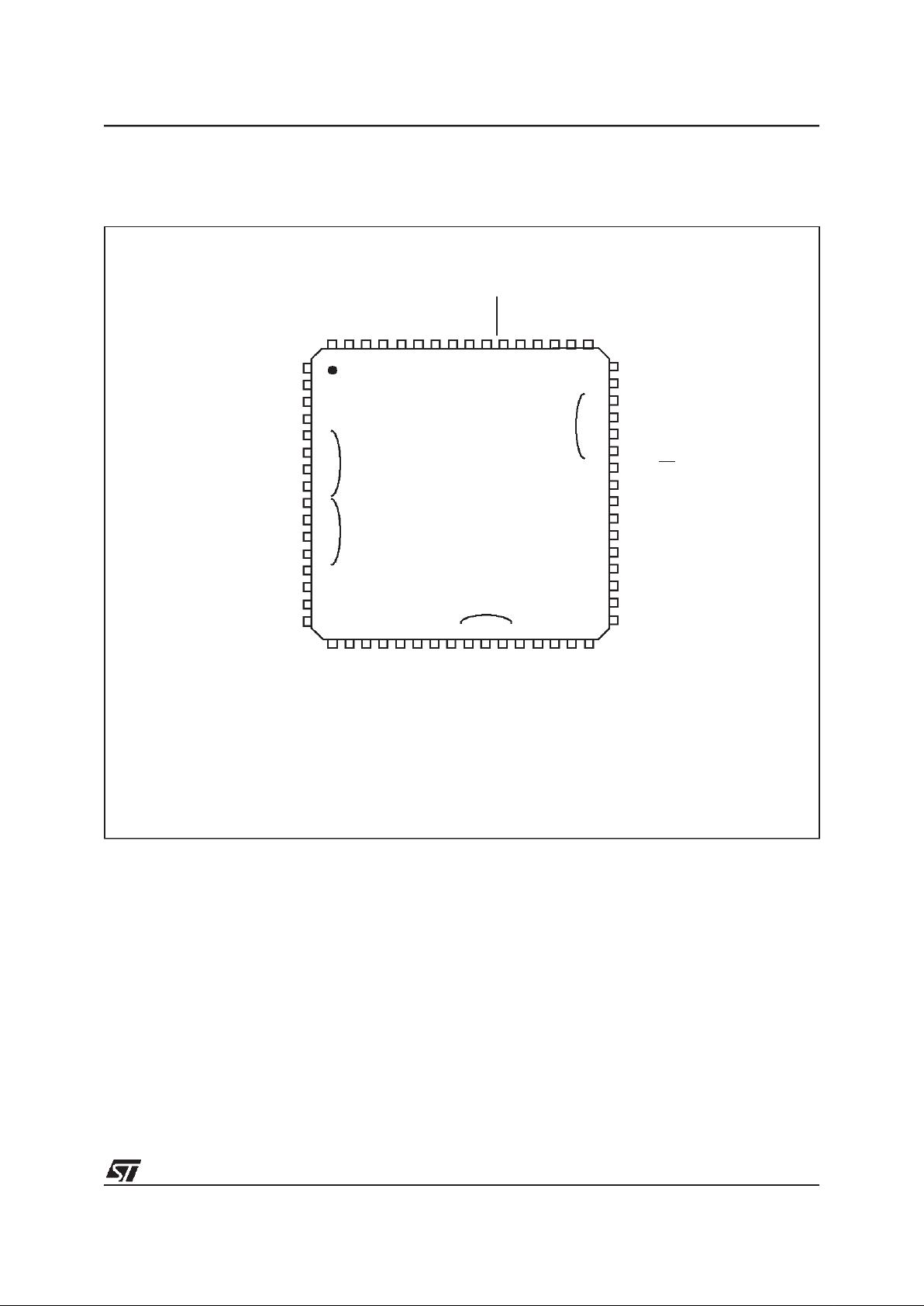

Figure 2. 64-Pin TQFP Package Pinout (N versions)

V

DDA

V

SSA

V

DD_3

V

SS_3

MCO / PF0

BEEP / PF1

PF2

NC

OCMP1_A / PF4

NC

ICAP1_A / (HS) PF6

EXTCLK_A / (HS) PF7

AIN4 / PD4

AIN5 / PD5

AIN6 / PD6

AIN7 / PD7

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

17 18 19 20 21 22 23 24 29 30 31 3225 26 27 28

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

EI2

EI3

EI0

EI1

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

AIN0 / PD0

AIN1 / PD1

AIN2 / PD2

AIN3 / PD3

(HS) PE4

(HS) PE5

(HS) PE6

(HS) PE7

PA1

PA0

PC7 / SS

PC6 / SCK / ISPCLK

PC5 / MOSI

PC4 / MISO / ISPDATA

PC3 (HS)/ ICAP1_B

PC2 (HS)/ ICAP2_B

PC1 / OCMP1_B

PC0 / OCMP2_B

V

SS_0

V

DD_0

V

SS_1

V

DD_1

PA3

PA2

V

DD

_2

OSC1

OSC2

V

SS

_2

NCNCRESET

ISPSEL

PA7 (HS)

PA6 (HS)

PA5 (HS)

PA4 (HS)

NCNCPE1 / RDI

PE0 / TDO

6

ST72334J/N, ST72314J/N, ST72124J

8/125

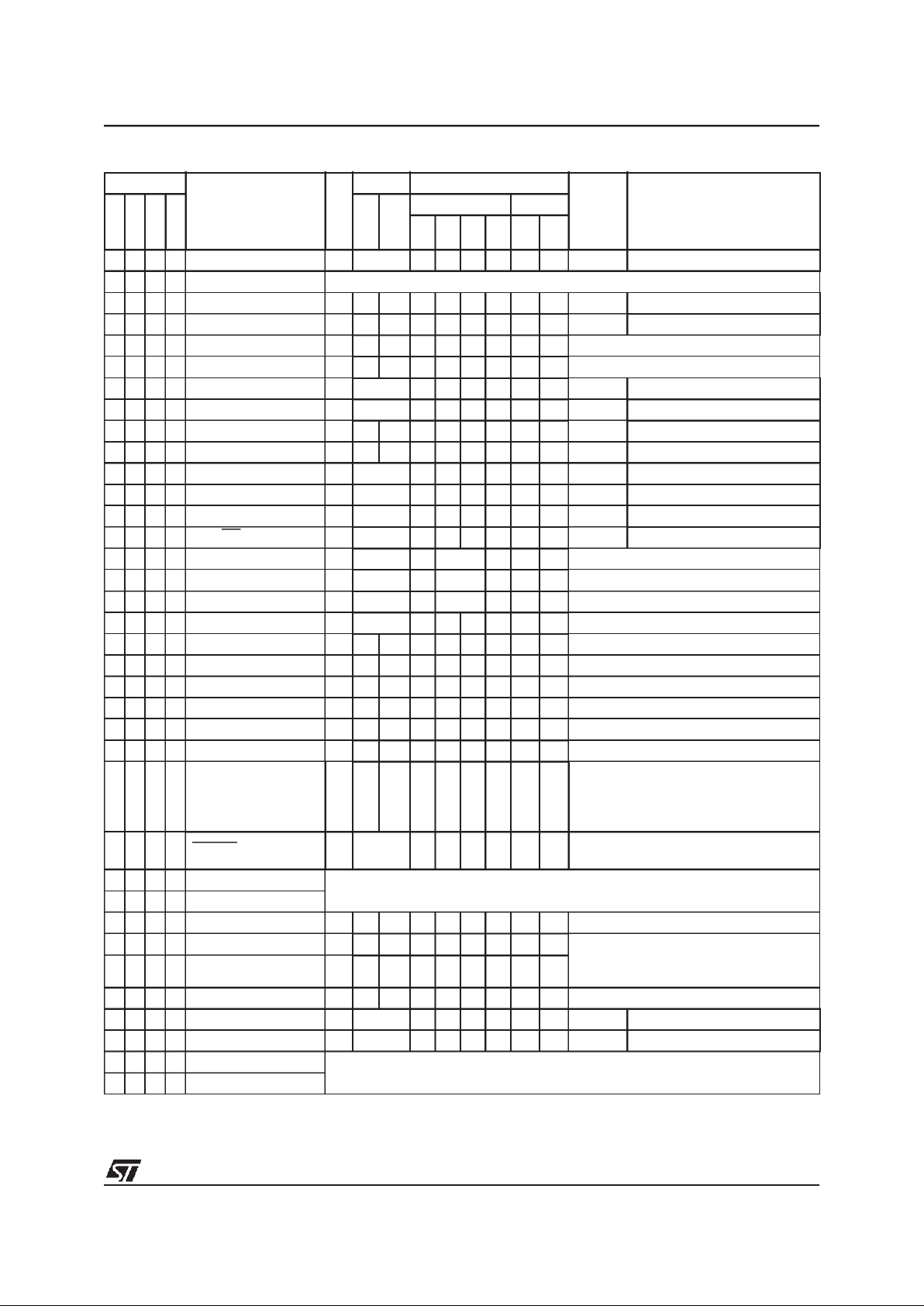

PIN DESCRIPTION (Cont’d)

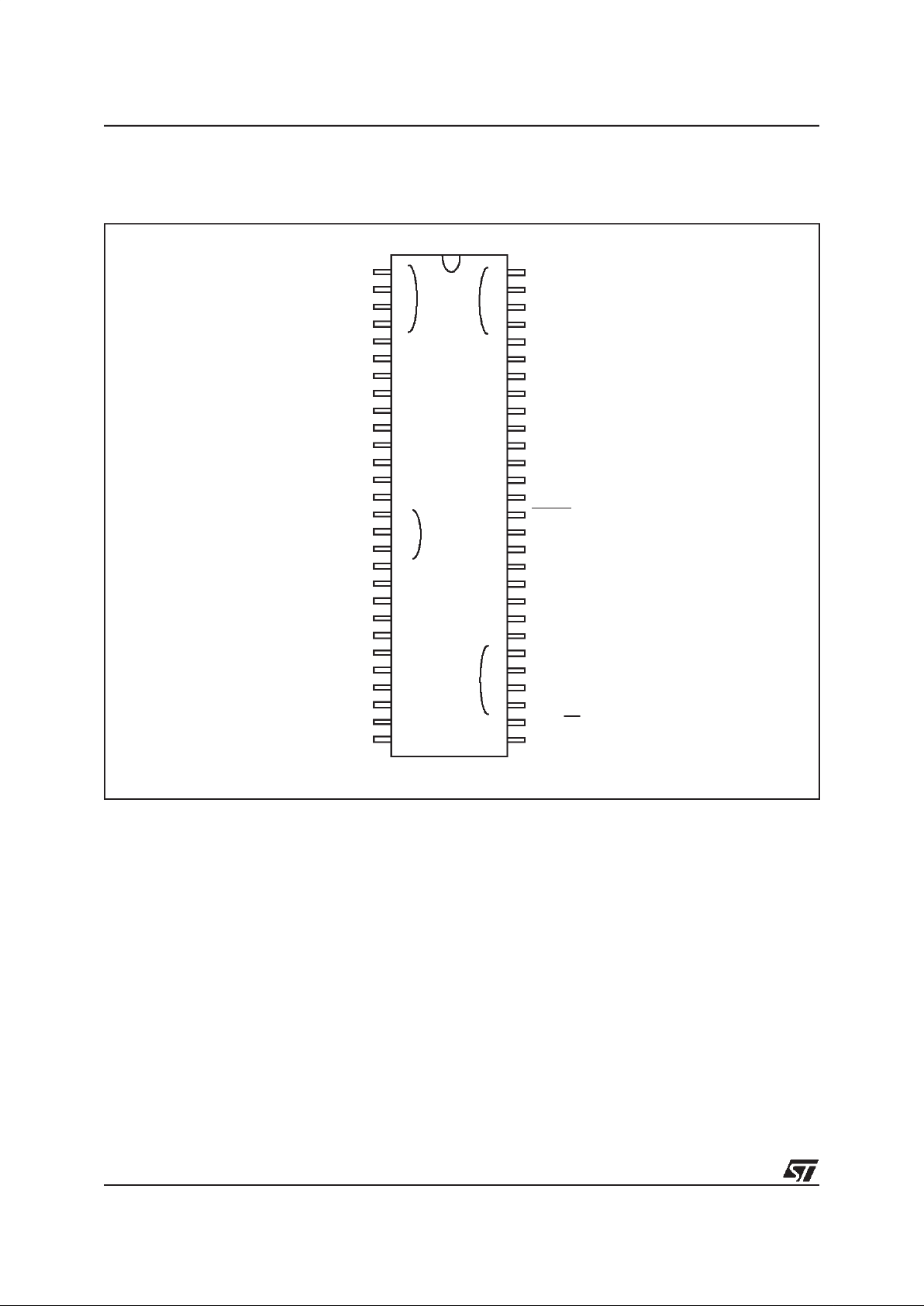

Figure 3. 56-Pin SDIP Package Pinout (N versions)

52

51

50

49

48

47

46

45

44

43

42

41

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

53

54

55

56

PB4

PB5

BEEP / PF1

MCO / PF0

V

SSA

V

DDA

AIN7 / PD7

AIN6 / PD6

AIN5 / PD5

AIN2 / PD2

AIN1 / PD1

AIN0 / PD0

PB7

PB6

AIN4 / PD4

AIN3 / PD3

PB3

PB2

ISPSEL

RESET

V

SS

_2

OSC2

OSC1

V

DD

_2

PE0 / TDO

PE5 (HS)

PE6 (HS)

PE7 (HS)

PB0

PB1

PE4 (HS)

PE1 / RDI

EI3

EI0

EI2

EI1

21

20

17

18

19

V

DD_0

EXTCLK_A / (HS) PF7

ICAP1_A / (HS) PF6

OCMP1_A / PF4

PF2

40

39

38

37

36

V

SS_1

PA4 (HS)

PA5 (HS)

PA6 (HS)I

PA7 (HS)

23

22

OCMP2_B / PC0

V

SS_0

28

27

24

25

26

MOSI / PC5

ISPDATA/ MISO /PC4

ICAP1_B / (HS) PC3

ICAP2_B / (HS) PC2

OCMP1_B / PC1

35

34

PA3

V

DD_1

33

32

31

30

29

PC6 / SCK / ISPCLK

PC7 / SS

PA0

PA1

PA2

ST72334J/N, ST72314J/N, ST72124J

9/125

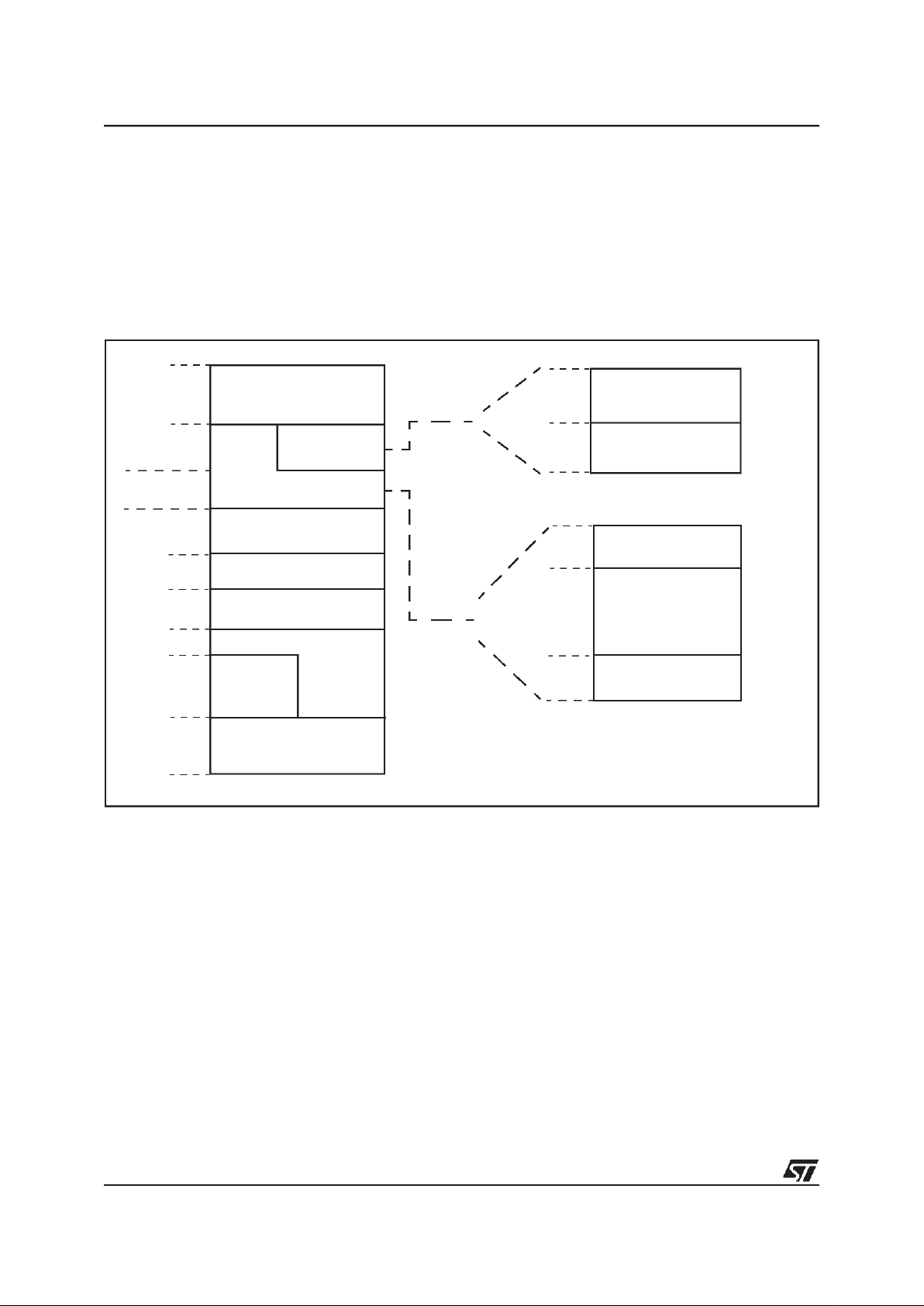

PIN DESCRIPTION (Cont’d)

Figure 4. 44-Pin TQFP and 42-Pin SDIP Package Pinouts (J versions)

MCO / PF0

BEEP / PF1

PF2

OCMP1_A / PF4

ICAP1_A / (HS) PF6

EXTCLK_A / (HS) PF7

V

DD_0

V

SS_0

AIN5 / PD5

V

DDA

V

SSA

44 43 42 41 40 39 38 37 36 35 34

33

32

31

30

29

28

27

26

25

24

23

12 13 14 15 16 17 18 19 20 21 22

1

2

3

4

5

6

7

8

9

10

11

EI2

EI3

EI0

EI1

PB3

PB4

AIN0 / PD0

AIN1 / PD1

AIN2 / PD2

AIN3 / PD3

AIN4 / PD4

PE1 / RDI

PB0

PB1

PB2

PC6 / SCK / ISPCLK

PC5 / MOSI

PC4 / MISO / ISPDATA

PC3 (HS) / ICAP1_B

PC2 (HS) / ICAP2_B

PC1 / OCMP1_B

PC0 / OCMP2_B

V

SS_1

V

DD_1

PA3

PC7 / SS

V

SS

_2

RESET

ISPSEL

PA7 (HS)

PA6 (HS)

PA5 (HS)

PA4 (HS)

PE0 / TDO

V

DD

_2

OSC1

OSC2

38

37

36

35

34

33

32

31

30

29

28

27

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

39

40

41

42

PB4

AIN0 / PD0

OCMP2_B / PC0

EXTCLK_A / (HS) PF7

ICAP1_A / (HS) PF6

OCMP1_A / PF4

PF2

BEEP / PF1

MCO / PF0

AIN5 / PD5

AIN4 / PD4

AIN3 / PD3

AIN2 / PD2

AIN1 / PD1

V

SSA

V

DDA

PB3

PB2

PA4 (HS)

PA5 (HS)

PA6 (HS)

PA7 (HS)

ISPSEL

RESET

V

SS

_2

V

DD

_2

PE0 / TDO

PE1 / RDI

PB0

PB1

OSC1

OSC2

EI3

EI0

EI2

EI1

21

20

17

18

19

MOSI / PC5

ISPDATA / MISO / PC4

ICAP1_B / (HS) PC3

ICAP2_B/ (HS) PC2

OCMP1_B / PC1

26

25

24

23

22

PC6 / SCK / ISPCLK

PC7 / SS

PA3

V

DD_1

V

SS_1

ST72334J/N, ST72314J/N, ST72124J

10/125

PIN DESCRIPTION (Cont’d)

Legend / Abbreviations:

Type: I = input, O = output, S = supply

Input level: A = Dedicated analog input

In/Output level: C = CMOS 0.3VDD/0.7VDD,

CT= CMOS 0.3VDD/0.7VDDwith input trigger

Output level: HS = high sink (on N-buffer only),

Port configuration capabilities:

– Input: float = floating, wpu = weak pull-up, int = interrupt, ana = analog

– Output: OD = open drain, T = true open drain, PP = push-pull

Note: the Reset configuration of each pin is shown in bold.

Table 1. Device Pin Description

Pin n°

Pin Name

Type

Level Port

Main

function

(after

reset)

Alternate function

TQFP64

SDIP56

QFP44

SDIP42

Input

Output

Input Output

float

wpu

int

ana

OD

PP

1 49 PE4 (HS) I/O CTHS X X X X Port E4

2 50 PE5 (HS) I/O C

T

HS X X X X Port E5

3 51 PE6 (HS) I/O C

T

HS X X X X Port E6

4 52 PE7 (HS) I/O C

T

HS X X X X Port E7

5 53 2 39 PB0 I/O C

T

X EI2 X X Port B0

6 54 3 40 PB1 I/O C

T

X EI2 X X Port B1

7 55 4 41 PB2 I/O C

T

X EI2 X X Port B2

8 56 5 42 PB3 I/O C

T

X EI2 X X Port B3

9 1 6 1 PB4 I/O C

T

X EI3 X X Port B4

10 2 PB5 I/O C

T

X EI3 X X Port B5

11 3 PB6 I/O C

T

X EI3 X X Port B6

12 4 PB7 I/O C

T

X EI3 X X Port B7

13 5 7 2 PD0/AIN0 I/O C

T

X X X X X Port D0 ADC Analog Input 0

14 6 8 3 PD1/AIN1 I/O C

T

X X X X X Port D1 ADC Analog Input 1

15 7 9 4 PD2/AIN2 I/O C

T

X X X X X Port D2 ADC Analog Input 2

16 8 10 5 PD3/AIN3 I/O C

T

X X X X X Port D3 ADC Analog Input 3

17 9 11 6 PD4/AIN4 I/O C

T

X X X X X Port D4 ADC Analog Input 4

18 10 12 7 PD5/AIN5 I/O C

T

X X X X X Port D5 ADC Analog Input 5

19 11 PD6/AIN6 I/O C

T

X X X X X Port D6 ADC Analog Input 6

20 12 PD7/AIN7 I/O C

T

X X X X X Port D7 ADC Analog Input 7

21 13 13 8 V

DDA

S Analog Power Supply Voltage

22 14 14 9 V

SSA

S Analog Ground Voltage

23 V

DD_3

S Digital Main Supply Voltage

24 V

SS_3

S Digital Ground Voltage

25 15 15 10 PF0/MCO I/O C

T

X EI1 X X Port F0 Main clock output (f

OSC

/2)

26 16 16 11 PF1/BEEP I/O C

T

X EI1 X X Port F1 Beep signal output

27 17 17 12 PF2 I/O C

T

X EI1 X X Port F2

28 NC Not Connected

ST72334J/N, ST72314J/N, ST72124J

11/125

29 18 18 13 PF4/OCMP1_A I/O C

T

X X X X Port F4 Timer A Output Compare 1

30 NC Not Connected

31 19 19 14 PF6 (HS)/ICAP1_A I/O C

T

HS X X X X Port F6 Timer A Input Capture 1

32 20 20 15 PF7 (HS)/EXTCLK_A I/O C

T

HS X X X X Port F7 Timer A External Clock Source

33 21 21 V

DD_0

S Digital Main Supply Voltage

34 22 22 V

SS_0

S Digital Ground Voltage

35 23 23 16 PC0/OCMP2_B I/O C

T

X X X X Port C0 Timer B Output Compare 2

36 24 24 17 PC1/OCMP1_B I/O C

T

X X X X Port C1 Timer B Output Compare 1

37 25 25 18 PC2 (HS)/ICAP2_B I/O C

T

HS X X X X Port C2 Timer B Input Capture 2

38 26 26 19 PC3 (HS)/ICAP1_B I/O C

T

HS X X X X Port C3 Timer B Input Capture 1

39 27 27 20 PC4/MISO I/O C

T

X X X X Port C4 SPI Master In / Slave Out Data

40 28 28 21 PC5/MOSI I/O C

T

X X X X Port C5 SPI Master Out / Slave In Data

41 29 29 22 PC6/SCK I/O C

T

X X X X Port C6 SPI Serial Clock

42 30 30 23 PC7/SS I/O C

T

X X X X Port C7 SPI Slave Select (active low)

43 31 PA0 I/O C

T

X EI0 X X Port A0

44 32 PA1 I/O C

T

X EI0 X X Port A1

45 33 PA2 I/O C

T

X EI0 X X Port A2

46 34 31 24 PA3 I/O C

T

X EI0 X X Port A3

47 35 32 25 V

DD_1

S Digital Main Supply Voltage

48 36 33 26 V

SS_1

S Digital Ground Voltage

49 37 34 27 PA4 (HS) I/O C

T

HS X X X X Port A4

50 38 35 28 PA5 (HS) I/O C

T

HS X X X X Port A5

51 39 36 29 PA6 (HS) I/O C

T

HS X T Port A6

52 40 37 30 PA7 (HS) I/O C

T

HS X T Port A7

53 41 38 31 ISPSEL I

Must be tied low in user mode. In programming mode when available, this pin

acts as In-Situ Programming mode selection.

54 42 39 32 RESET I/O C X X

Top priority non maskable interrupt (active low)

55 NC

Not Connected

56 NC

57 43 40 33 V

SS_3

S Digital Ground Voltage

58 44 41 34 OSC2 These pins connect a parallel-resonant

crystal or an external clock source tothe

on-chip main oscillator.

59 45 42 35 OSC1

60 46 43 36 V

DD_3

S Digital Main Supply Voltage

61 47 44 37 PE0/TDO I/O C

T

X X X X Port E0 SCI Transmit Data Out

62 48 1 38 PE1/RDI I/O C

T

X X X X Port E1 SCI Receive Data In

63 NC

Not Connected

64 NC

Pin n°

Pin Name

Type

Level Port

Main

function

(after

reset)

Alternate function

TQFP64

SDIP56

QFP44

SDIP42

Input

Output

Input Output

float

wpu

int

ana

OD

PP

ST72334J/N, ST72314J/N, ST72124J

12/125

2.3 REGISTER & MEMORY MAP

As shown in the Figure 5, the MCU is capable of

addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 128

bytes of register locations, 384 or 512 bytes of

RAM, up to 256 bytes of data EEPROM and 4 or

8 Kbytes of user program memory. The RAM

space includes up to 256 bytes for the stack from

0100h to 01FFh.

The highest address bytes contain the user reset

and interrupt vectors.

Figure 5. Memory Map

0000h

Interrupt & Reset Vectors

HW Registers

027Fh

0080h

Short Addressing

RAM (zero page)

16-bit Addressing

RAM

007Fh

0200h / 0280h

0BFFh

Reserved

0080h

(see Table 2)

0C00h

FFDFh

FFE0h

FFFFh

(see Table 6 page 37)

027Fh

C000h

Reserved

256 Bytes Data EEPROM

0CFFh

0D00h

BFFFh

00FFh

0100h

01FFh

0200h

8K Bytes

E000h

16K Bytes

Program

Short Addressing

RAM (zero page)

0080h

00FFh

01FFh

01FFh

384 Bytes RAM

512 Bytes RAM

256 Bytes Stack or

16-bit Addressing RAM

256 Bytes Stack or

16-bit Addressing RAM

0100h

Memory

Program

Memory

ST72334J/N, ST72314J/N, ST72124J

13/125

REGISTER & MEMORY MAP (Cont’d)

Table 2. Hardware Register Map

Address Block

Register

Label

Register Name

Reset

Status

Remarks

0000h

0001h

0002h

Port A

PADR

PADDR

PAOR

Port A Data Register

Port A Data Direction Register

Port A Option Register

00h

00h

00h

R/W

R/W

R/W

1)

0003h Reserved Area (1 Byte)

0004h

0005h

0006h

Port C

PCDR

PCDDR

PCOR

Port C Data Register

Port C Data Direction Register

Port C Option Register

00h

00h

00h

R/W

R/W

R/W

0007h Reserved Area (1 Byte)

0008h

0009h

000Ah

Port B

PBDR

PBDDR

PBOR

Port B Data Register

Port B Data Direction Register

Port B Option Register

00h

00h

00h

R/W

R/W

R/W

1)

000Bh Reserved Area (1 Byte)

000Ch

000Dh

000Eh

Port E

PEDR

PEDDR

PEOR

Port E Data Register

Port E Data Direction Register

Port E Option Register

00h

00h

00h

R/W

R/W

R/W

1)

000Fh Reserved Area (1 Byte)

0010h

0011h

0012h

Port D

PDDR

PDDDR

PDOR

Port D Data Register

Port D Data Direction Register

Port D Option Register

00h

00h

00h

R/W

R/W

R/W

1)

0013h Reserved Area (1 Byte)

0014h

0015h

0016h

Port F

PFDR

PFDDR

PFOR

Port F Data Register

Port F Data Direction Register

Port F Option Register

00h

00h

00h

R/W

R/W

R/W

0017h

to

001Fh

Reserved Area (9 Bytes)

0020h MISCR1 Miscellaneous Register 1 00h R/W

0021h

0022h

0023h

SPI

SPIDR

SPICR

SPISR

SPI Data I/O Register

SPI Control Register

SPI Status Register

xxh

0xh

00h

R/W

R/W

Read Only

0024h

to

0028h

Reserved Area (5 Bytes)

0029h MCC MCCSR Main Clock Control / Status Register 01h R/W

ST72334J/N, ST72314J/N, ST72124J

14/125

002Ah WATCHDOG WDGCR Watchdog Control Register 7Fh R/W

002Bh CRSR Clock, Reset, Supply Control / Status Register 00h R/W

002Ch Data-EEPROM EECSR Data-EEPROM Control/Status Register 00h R/W

002Dh

0030h

Reserved Area (4 Bytes)

0031h

0032h

0033h

0034h

0035h

0036h

0037h

0038h

0039h

003Ah

003Bh

003Ch

003Dh

003Eh

003Fh

TIMER A

TACR2

TACR1

TASR

TAIC1HR

TAIC1LR

TAOC1HR

TAOC1LR

TACHR

TACLR

TAACHR

TAACLR

TAIC2HR

TAIC2LR

TAOC2HR

TAOC2LR

Timer A Control Register 2

Timer A Control Register 1

Timer A Status Register

Timer A Input Capture 1 High Register

Timer A Input Capture 1 Low Register

Timer A Output Compare 1 High Register

Timer A Output Compare 1 Low Register

Timer A Counter High Register

Timer A Counter Low Register

Timer A Alternate Counter High Register

Timer A Alternate Counter Low Register

Timer A Input Capture 2 High Register

Timer A Input Capture 2 Low Register

Timer A Output Compare 2 High Register

Timer A Output Compare 2 Low Register

00h

00h

xxh

xxh

xxh

80h

00h

FFh

FCh

FFh

FCh

xxh

xxh

80h

00h

R/W

R/W

Read Only

Read Only

Read Only

R/W

R/W

Read Only

Read Only

Read Only

Read Only

Read Only

2)

Read Only

2)

R/W

2)

R/W

2)

0040h MISCR2 Miscellaneous Register 2 00h R/W

0041h

0042h

0043h

0044h

0045h

0046h

0047h

0048h

0049h

004Ah

004Bh

004Ch

004Dh

004Eh

004Fh

TIMER B

TBCR2

TBCR1

TBSR

TBIC1HR

TBIC1LR

TBOC1HR

TBOC1LR

TBCHR

TBCLR

TBACHR

TBACLR

TBIC2HR

TBIC2LR

TBOC2HR

TBOC2LR

Timer B Control Register 2

Timer B Control Register 1

Timer B Status Register

Timer B Input Capture 1 High Register

Timer B Input Capture 1 Low Register

Timer B Output Compare 1 High Register

Timer B Output Compare 1 Low Register

Timer B Counter High Register

Timer B Counter Low Register

Timer B Alternate Counter High Register

Timer B Alternate Counter Low Register

Timer B Input Capture 2 High Register

Timer B Input Capture 2 Low Register

Timer B Output Compare 2 High Register

Timer B Output Compare 2 Low Register

00h

00h

xxh

xxh

xxh

80h

00h

FFh

FCh

FFh

FCh

xxh

xxh

80h

00h

R/W

R/W

Read Only

Read Only

Read Only

R/W

R/W

Read Only

Read Only

Read Only

Read Only

Read Only

Read Only

R/W

R/W

0050h

0051h

0052h

0053h

0054h

0055h

0056h

0057h

SCI

SCISR

SCIDR

SCIBRR

SCICR1

SCICR2

SCIERPR

SCIETPR

SCI Status Register

SCI Data Register

SCI Baud Rate Register

SCI Control Register 1

SCI Control Register 2

SCI Extended Receive Prescaler Register

Reserved area

SCI Extended Transmit Prescaler Register

C0h

xxh

00xx xxxx

xxh

00h

00h

---

00h

Read Only

R/W

R/W

R/W

R/W

R/W

R/W

Address Block

Register

Label

Register Name

Reset

Status

Remarks

ST72334J/N, ST72314J/N, ST72124J

15/125

Notes:

1) The bits corresponding to unavailable pins are forced to 1by hardware, this affects the reset status value.

2) External pin not available.

3) Not used in versions without Low Voltage Detector Reset.

0058h

006Fh

Reserved Area (24 Bytes)

0070h

0071h

ADC

ADCDR

ADCCSR

Data Register

Control/Status Register

xxh

00h

Read Only

R/W

0072h

to

007Fh

Reserved Area (14 Bytes)

Address Block

Register

Label

Register Name

Reset

Status

Remarks

ST72334J/N, ST72314J/N, ST72124J

16/125

2.4 FLASH PROGRAM MEMORY

2.4.1 Introduction

Flash devices have a single voltage non-volatile

FLASH memory that may be programmed in-situ

(or plugged in a programming tool) on a byte-bybyte basis.

2.4.2 Main features

■ Remote In-Situ Programming (ISP) mode

■ Up to 16 bytes programmedin the same cycle

■ MTP memory (Multiple Time Programmable)

■ Read-out memory protection against piracy

2.4.3 Structural organisation

The FLASH program memory is organised in a

single 8-bit wide memory block which can be used

for storing both code and data constants.

The FLASH program memory is mappedin the upper part of the ST7 addressing space (F000hFFFFh) and includes the reset and interrupt user

vector area .

2.4.4 In-Situ Programming (ISP) mode

The FLASH program memory canbe programmed

using Remote ISP mode. This ISP mode allows

the contentsoftheST7program memory to be updated usingastandard ST7 programming tools after the device is mounted on the application board.

This feature can be implemented with a minimum

number of added components and board area impact.

An exampleRemote ISP hardware interface to the

standard ST7 programming tool is described below. For more details on ISP programming, refer to

the ST7 Programming Specification.

Remote ISP Overview

The Remote ISP mode is initiatedby a specific sequence on the dedicated ISPSEL pin.

The Remote ISP is performedin three steps:

– Selection of the RAM execution mode

– Download of Remote ISP codein RAM

– Execution ofRemote ISP code in RAM to pro-

gram the user program into the FLASH

Remote ISP hardware configuration

In Remote ISP mode, the ST7 has to be supplied

with power (VDDand VSS) and a clock signal (oscillator and application crystal circuit for example).

This mode needs five signals (plus the VDDsignal

if necessary) to be connected to the programming

tool. This signals are:

– RESET: device reset

–VSS: device ground power supply

– ISPCLK: ISP outputserial clock pin

– ISPDATA: ISP input serial data pin

– ISPSEL: Remote ISP modeselection. Thispin

must be connected to VSSon the application

board

If any of thesepins areused for other purposeson

the application, a serial resistor has to be implemented to avoid a conflict ifthe other deviceforces

the signal level.

Figure 6 shows a typical hardware interface to a

standard ST7 programming tool. For more details

on the pin locations, refer to the device pinout description.

Figure 6. Typical Remote ISP Interface

2.5 Program Memory Read-out Protection

The read-out protection is enabled through an option bit.

For FLASH devices, when this option is selected,

the program and data stored in the FLASH memory are protected against read-out piracy (including

a re-write protection). When this protection option

is removed the entire FLASH program memory is

first automatically erased.

1

ISPSEL

V

SS

RESET

ISPCLK

ISPDATA

OSC1

OSC2

V

DD

ST7

HE10 CONNECTOR TYPE

TO PROGRAMMINGTOOL

10kΩ

C

L0

C

L1

APPLICATION

4.7kΩ

1

XTAL

ST72334J/N, ST72314J/N, ST72124J

17/125

2.6 DATA EEPROM

2.6.1 Introduction

The Electrically Erasable Programmable Read

Only Memory can be used as a non volatile backup for storing data.Using the EEPROM requires a

basic access protocol described in this chapter.

2.6.2 Main Features

■ Up to 16 Bytes programmed in the same cycle

■ EEPROM mono-voltage (charge pump)

■ Chained erase and programming cycles

■ Internal control of the global programming cycle

duration

■ End of programming cycle interrupt flag

■ WAIT mode management

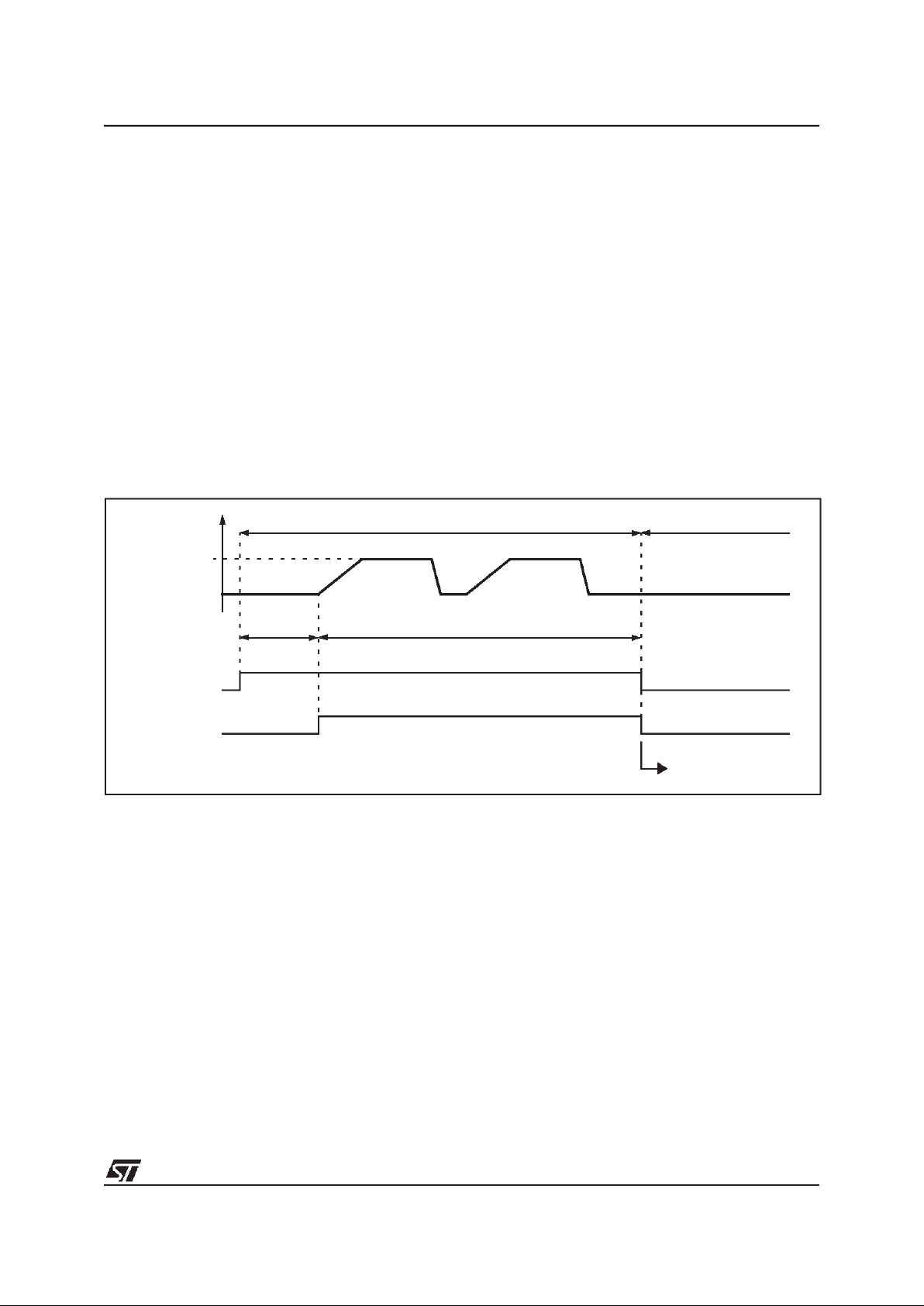

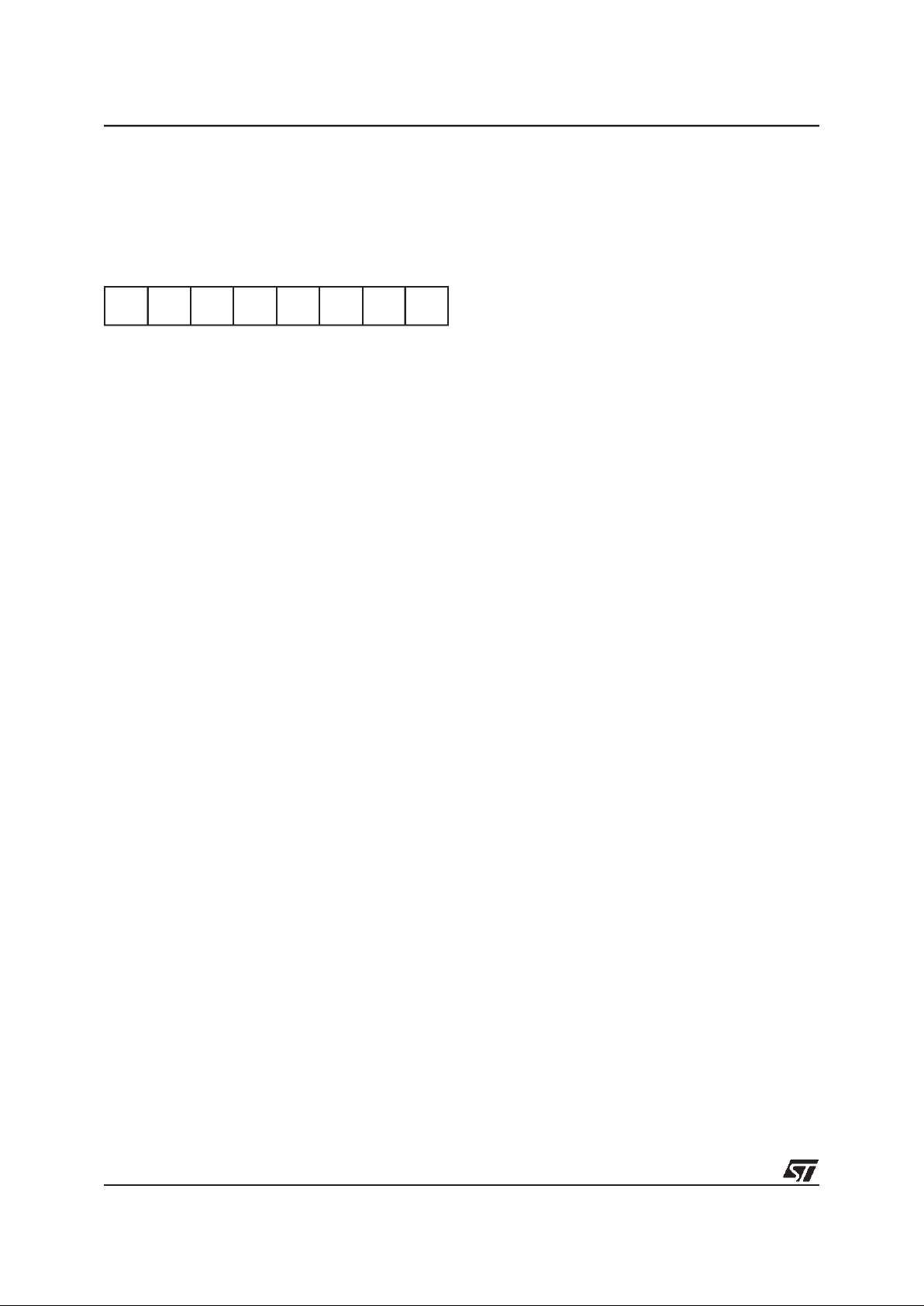

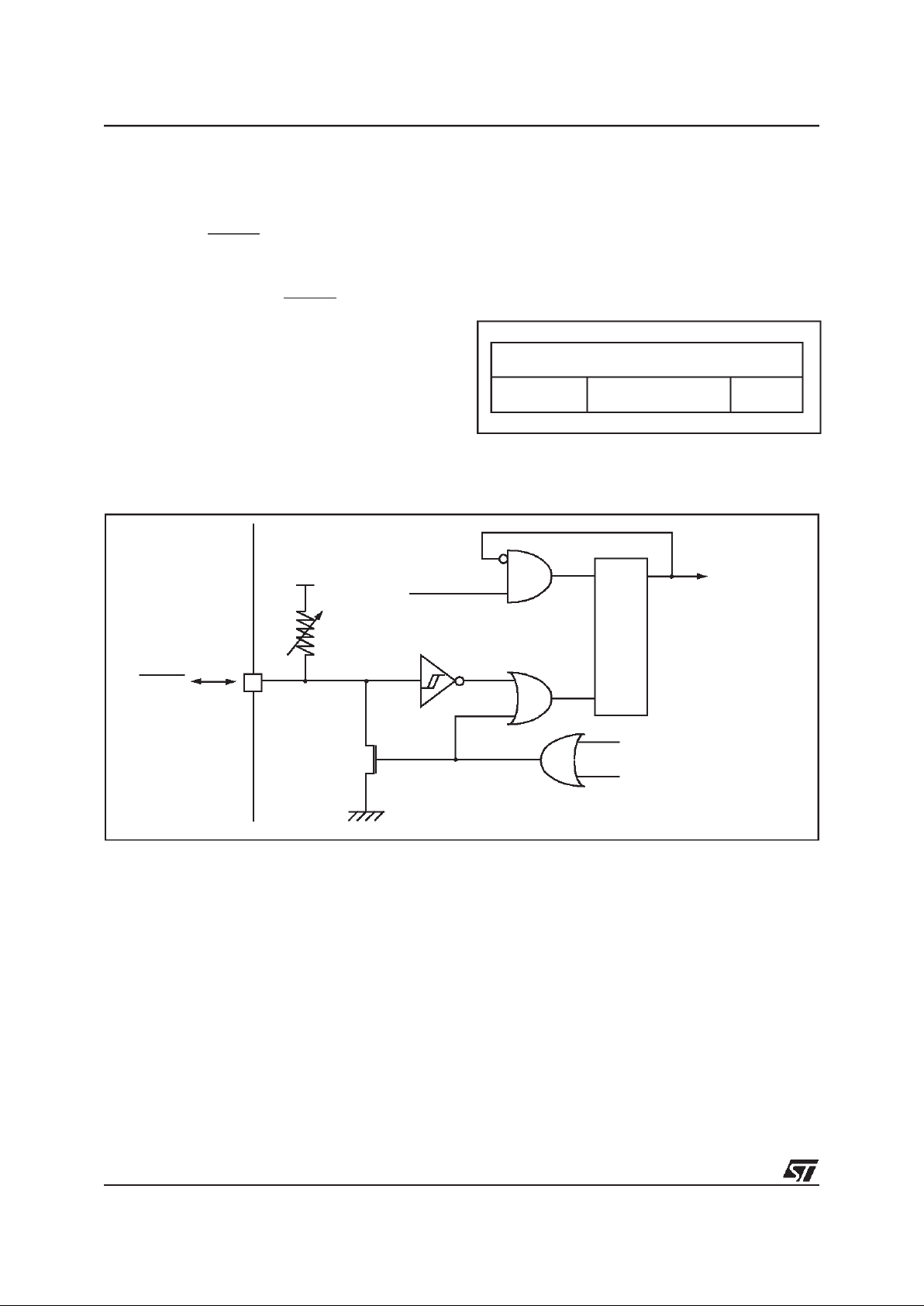

Figure 7. EEPROM Block Diagram

EECSR

EEPROM INTERRUPT

FALLING

EDGE

HIGH VOLTAGE

PUMP

IE LAT00000 PGM

EEPROMRESERVED

DETECTOR

EEPROM

MEMORY MATRIX

(1 ROW = 16 x 8 BITS)

ADDRESS

DECODER

DATA

MULTIPLEXER

16 x 8 BITS

DATA LATCHES

ROW

DECODER

DATA BUS

4

4

4

128128

ADDRESS BUS

ST72334J/N, ST72314J/N, ST72124J

18/125

DATA EEPROM (Cont’d)

2.6.3 Memory Access

The Data EEPROM memory read/write access

modes are controlled by the LAT bit of the EEPROM Control/Status register (EECSR). The flowchart inFigure 8 describes these different memory

access modes.

Read Operation (LAT=0)

The EEPROM canbe read as a normal ROM location when the LAT bit of the EECSR register is

cleared. Ina read cycle, the byte to be accessed is

put onthedatabusin less than 1CPUclock cycle.

This means that reading data from EEPROM

takes the same time as reading data from

EPROM, but this memory cannot be used to execute machine code.

Write Operation (LAT=1)

To access the write mode, the LAT bit has to be

set by software (the PGM bit remains cleared).

When a write access to the EEPROM area occurs,

the value is latched inside the 16 data latches according to its address.

When PGM bit is set by the software, all the previous bytes written in the data latches(up to16) are

programmed in the EEPROM cells. The effective

high address (row) is determined by the last EEPROM write sequence. To avoid wrong programming, the user must take care that all the bytes

written between two programming sequences

have the same high address: only the four Least

Significant Bits of the address can change.

At the end of the programming cycle, the PGM and

LAT bits are cleared simultaneously, and an interrupt is generated if the IE bitis set. The Data EEPROM interrupt request is cleared by hardware

when the Data EEPROM interrupt vector is

fetched.

Note: Care should be taken during the programming cycle. Writing to the same memory location

will over-program the memory (logical AND between the two write access data result) because

the data latches are only cleared at the end of the

programming cycle and by thefalling edge of LAT

bit.

It is not possible toread the latched data.

This note is ilustrated by the Figure 9.

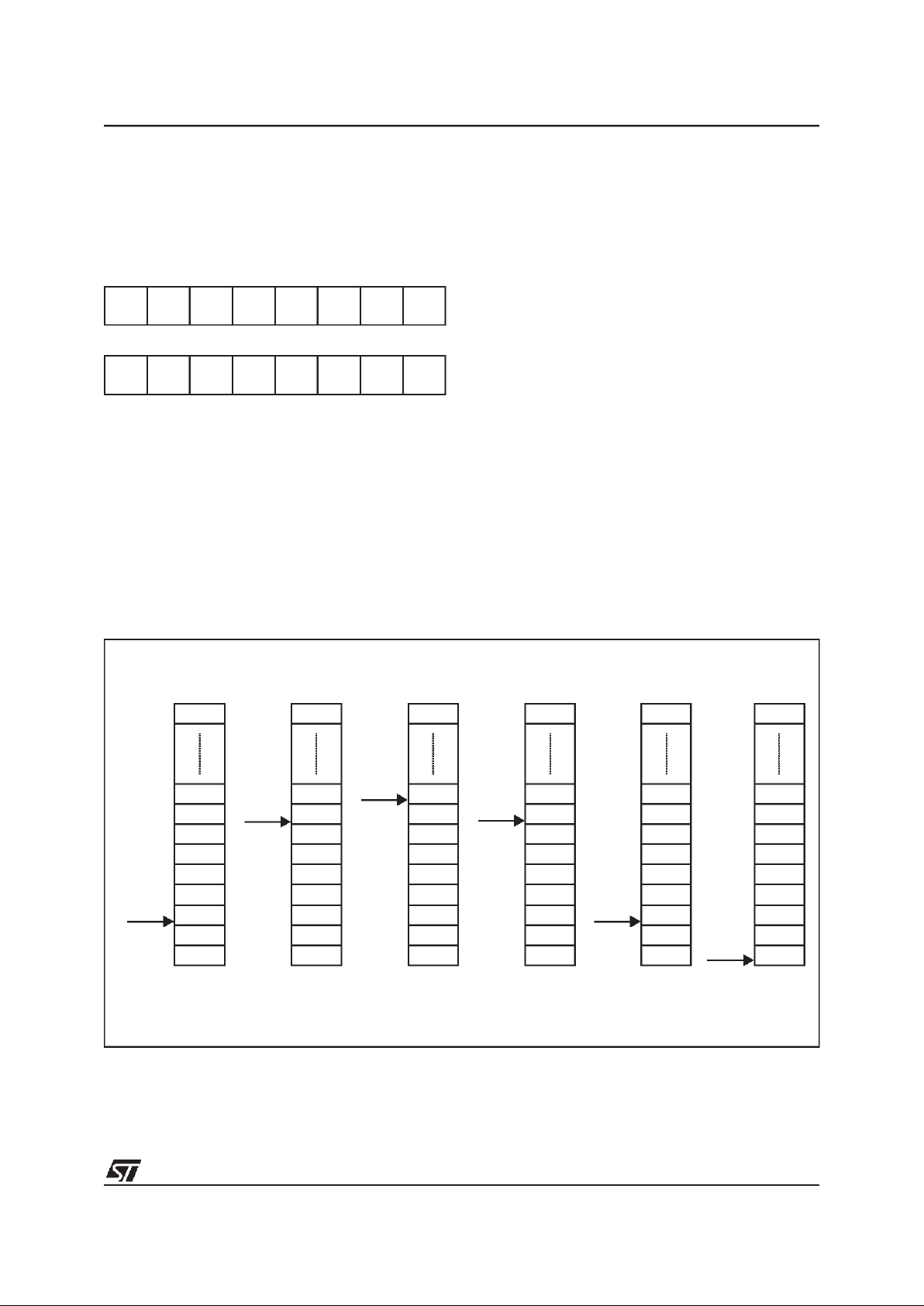

Figure 8. Data EEPROM ProgrammingFlowchart

READ MODE

LAT=0

PGM=0

WRITEMODE

LAT=1

PGM=0

READ BYTES

IN EEPROM AREA

WRITE UP TO 16 BYTES

IN EEPROM AREA

(with the same 12 MSB of the address)

START PROGRAMMING CYCLE

LAT=1

PGM=1 (set by software)

LAT

INTERRUPT GENERATION

IF IE=1 0 1

CLEARED BY HARDWARE

ST72334J/N, ST72314J/N, ST72124J

19/125

DATA EEPROM (Cont’d)

2.6.4 Data EEPROM and Power Saving Modes

Wait mode

The DATAEEPROMcan enter WAIT mode on execution of the WFI instruction of the microcontroller. The DATA EEPROM will immediately enter

this mode if there is no programming in progress,

otherwise the DATA EEPROM will finish the cycle

and then enter WAIT mode.

Halt mode

The DATA EEPROM immediatly enters HALT

mode if themicrocontroller executes the HALT instruction. Therefore the EEPROM will stop the

function in progress, and data may be corrupted.

2.6.5 Data EEPROM Access Error Handling

If a read access occurs while LAT=1, then the data

bus will not be driven.

If a write access occurs while LAT=0, then the

data on the bus will not be latched.

If a programming cycle is interrupted (by software/

RESET action), the memory data will not be guaranteed.

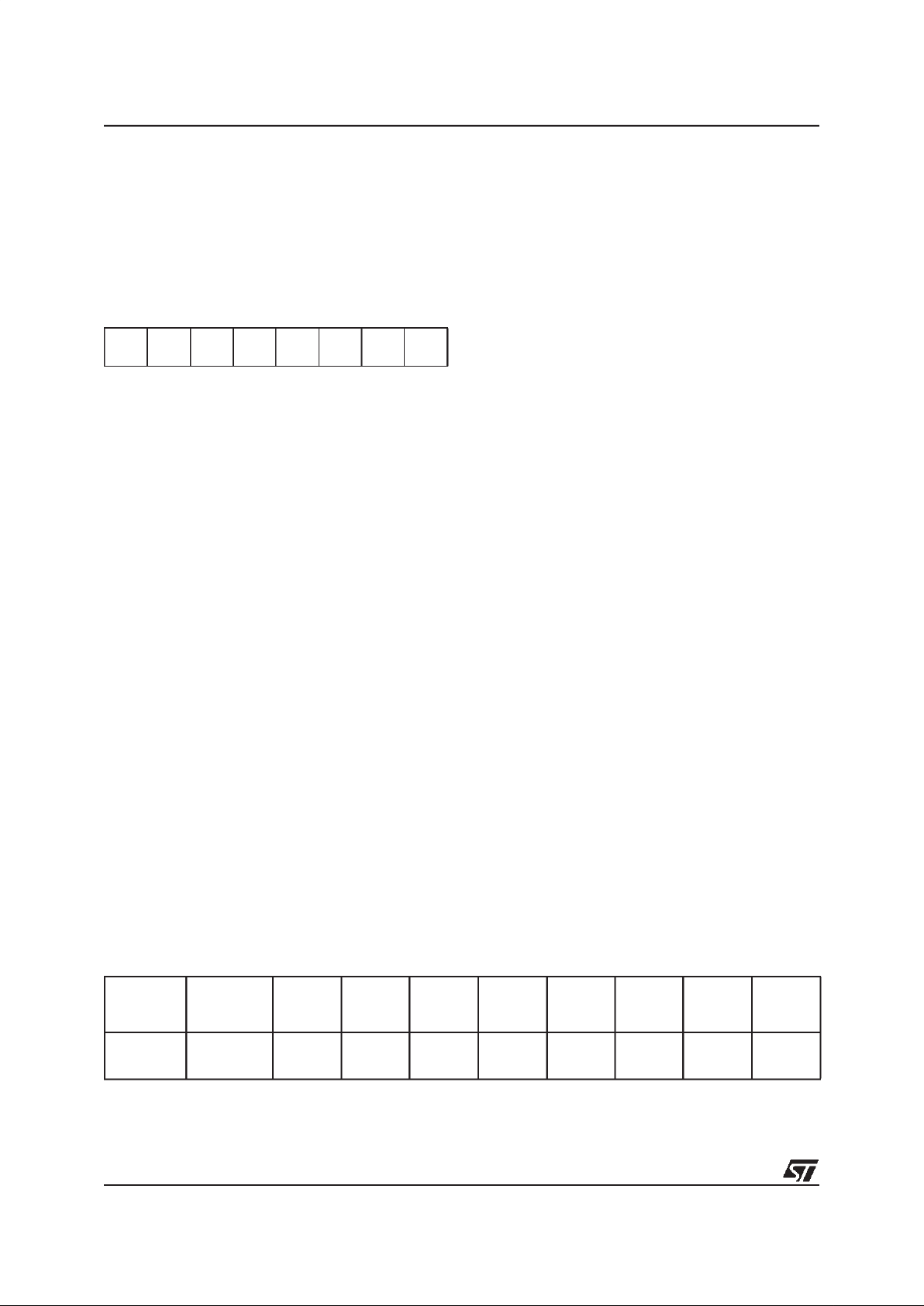

Figure 9. Data EEPROM ProgrammingCycle

LAT

ERASE CYCLE WRITE CYCLE

PGM

t

PROG

READ OPERATION NOT POSSIBLE

WRITE OF

DATA LATCHES

READ OPERATION POSSIBLE

INTERNAL

PROGRAMMING

VOLTAGE

EEPROM INTERRUPT

ST72334J/N, ST72314J/N, ST72124J

20/125

DATA EEPROM (Cont’d)

2.6.6 Register Description

CONTROL/STATUS REGISTER (CSR)

Read/Write

Reset Value: 0000 0000 (00h)

Bit 7:3 = Reserved, forced by hardware to 0.

Bit 2 = IE

Interrupt enable

Thisbitissetandclearedbysoftware.Itenables the

Data EEPROM interrupt capability when the PGM

bit iscleared by hardware. The interrupt request is

automatically cleared when thesoftware enters the

interrupt routine.

0: Interrupt disabled

1: Interrupt enabled

Bit 1 = LAT

Latch Access Transfer

This bit is set by software. It is cleared by hardware at the end of the programming cycle. It can

only be cleared by software if PGM bit is cleared.

0: Read mode

1: Write mode

Bit 0 = PGM

Programming control and status

This bitisset bysoftwaretobeginthe programming

cycle. At the end of theprogramming cycle, this bit

is clearedby hardwareand aninterruptisgenerated

if the ITE bit is set.

0: Programming finished or not yet started

1: Programming cycle is in progress

Note: ifthe PGM bit iscleared duringthe programming cycle, the memory data is not guaranteed.

Table 3. DATA EEPROM Register Map and Reset Values

70

00000IELATPGM

Address

(Hex.)

Register

Label

76543210

002Ch

EECSR

Reset Value

00000IE0

RWM

0

PGM

0

ST72334J/N, ST72314J/N, ST72124J

21/125

3 CENTRAL PROCESSING UNIT

3.1 INTRODUCTION

This CPU has a full 8-bit architecture and contains

six internal registers allowing efficient 8-bit data

manipulation.

3.2 MAIN FEATURES

■ 63 basic instructions

■ Fast 8-bit by 8-bit multiply

■ 17 main addressing modes

■ Two 8-bit index registers

■ 16-bit stack pointer

■ Low power modes

■ Maskable hardware interrupts

■ Non-maskable software interrupt

3.3 CPU REGISTERS

The 6 CPU registers shown in Figure 10 are not

present in the memory mapping and are accessed

by specific instructions.

Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the

arithmetic and logic calculations and to manipulate

data.

Index Registers (X and Y)

In indexed addressing modes, these 8-bitregisters

are used to create either effective addresses or

temporary storage areas for data manipulation.

(The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y registeris not affectedby the interrupt automatic procedures (notpushed to and popped from

the stack).

Program Counter (PC)

The program counter is a 16-bit register containing

the address of the next instruction to be executed

by the CPU. It is made of two 8-bit registers PCL

(Program Counter Low which is the LSB) andPCH

(Program CounterHigh which is the MSB).

Figure 10. CPU Registers

ACCUMULATOR

X INDEX REGISTER

Y INDEX REGISTER

STACK POINTER

CONDITION CODE REGISTER

PROGRAM COUNTER

70

1C11HI NZ

RESET VALUE = RESET VECTOR @ FFFEh-FFFFh

70

70

70

0

7

15 8

PCH

PCL

15

87 0

RESET VALUE = STACKHIGHER ADDRESS

RESET VALUE =

1X11X1XX

RESET VALUE = XXh

RESET VALUE = XXh

RESET VALUE= XXh

X = Undefined Value

ST72334J/N, ST72314J/N, ST72124J

22/125

CENTRAL PROCESSING UNIT (Cont’d)

CONDITION CODE REGISTER (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt mask and four flags representative of the

result ofthe instruction just executed. This register

can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

Bit 4 = H

Half carry

.

This bit is set by hardware whena carryoccursbetween bits 3 and 4 of the ALU during an ADD or

ADC instruction. It is reset by hardware during the

same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

Bit 3 = I

Interrupt mask

.

This bit is set by hardware when entering in interrupt or by software to disable all interrupts except

the TRAP software interrupt. This bit is cleared by

software.

0: Interrupts are enabled.

1: Interrupts are disabled.

This bit is controlledby the RIM, SIM and IRET instructions and is tested by the JRM and JRNM instructions.

Note: Interrupts requested while I is set are

latched and can be processed when I is cleared.

By default an interrupt routine is not interruptable

because the I bit is set by hardware when you enter it and resetby the IRETinstruction at the endof

the interrupt routine. If the I bit is cleared by software in the interrupt routine, pending interrupts are

serviced regardless of the priority level of the current interrupt routine.

Bit 2 = N

Negative

.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic,

logical or data manipulation. It is a copy of the 7

th

bit of the result.

0:Theresultof the last operation is positive or null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit isaccessed bythe JRMI andJRPL instructions.

Bit 1 = Z

Zero

.

This bit is set and cleared by hardware. Thisbit indicates that the result of the last arithmetic, logical

or data manipulation is zero.

0: The result of the last operation is different from

zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test

instructions.

Bit 0 = C

Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has

occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow hasoccurred.

This bit is driven by the SCF and RCF instructions

and tested by the JRC and JRNC instructions. It is

also affected by the “bit test and branch”, shift and

rotate instructions.

70

111HINZC

ST72334J/N, ST72314J/N, ST72124J

23/125

CENTRAL PROCESSING UNIT (Cont’d)

Stack Pointer (SP)

Read/Write

Reset Value: 01 FFh

The Stack Pointer is a 16-bit register which is always pointingto the next free location in the stack.

It isthen decremented after data has been pushed

onto the stack and incremented before data is

popped from the stack (see Figure 11).

Since the stack is 256 bytes deep, the 8th most

significant bits are forced by hardware. Following

an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits areset) which is the

stack higher address.

The least significant byte of the Stack Pointer

(called S) can be directly accessed by a LD instruction.

Note: When the lower limit is exceeded, the Stack

Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously

stored information is then overwritten and therefore lost. The stack also wrapsin case of anunderflow.

The stack is used to save the return address during a subroutine call and the CPU context during

an interrupt. The user may also directly manipulate

the stack by meansof the PUSH and POP instructions. In the case of an interrupt, the PCL is stored

at the first location pointed to by the SP. Then the

other registers are stored in the next locations as

shown in Figure 11.

– When an interrupt is received, the SP is decre-

mented and the context is pushed on the stack.

– On return from interrupt, the SP is incremented

and the context is popped from thestack.

A subroutine call occupies twolocations and an interrupt five locations in the stack area.

Figure 11. Stack Manipulation Example

15 8

00000001

70

SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0

PCH

PCL

SP

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

SP

Y

CALL

Subroutine

Interrupt

Event

PUSH Y POP Y IRET

RET

or RSP

@ 01FFh

@ 0100h

Stack Higher Address = 01FFh

Stack Lower Address =

0100h

ST72334J/N, ST72314J/N, ST72124J

24/125

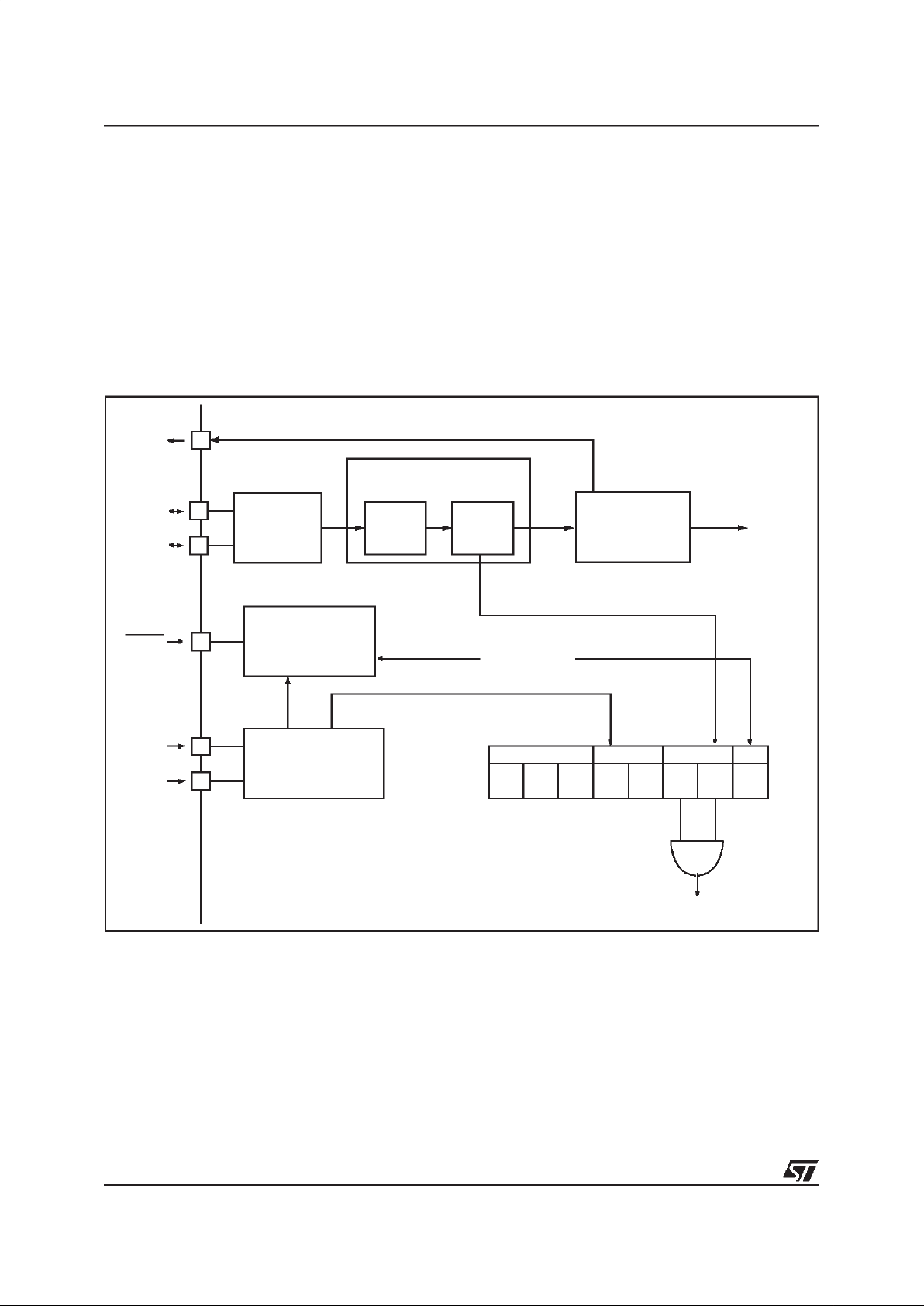

4 SUPPLY, RESET AND CLOCK MANAGEMENT

The ST72334J/N, ST72314J/N and ST72124J microcontrollers include a range of utility features for

securing the application in critical situations (for

example in case of a power brown-out), and reducing the number of external components. An

overview is shown in Figure 12.

Main Features

■ Supply Manager with Main supply Low voltage

detection (LVD)

■ Reset Sequence Manager (RSM)

■ Multi-Oscillator (MO)

– 4 Crystal/Ceramic resonator oscillators

– 1 External RC oscillator

– 1 Internal RC oscillator

■ Clock Security System (CSS)

– Clock Filter

– Backup Safe Oscillator

Figure 12. Clock, Reset and Supply Block Diagram

IE D00 0 0 RF RF

CRSR

CSS WDG

f

OSC

CSS INTERRUPT

LVD

LOW VOLTAGE

DETECTOR

(LVD)

MULTI-

OSCILLATOR

(MO)

FROM

WATCHDOG

PERIPHERAL

OSC1

RESET

VDD

VSS

RESET SEQUENCE

MANAGER

(RSM)

CLOCK

FILTER

SAFE

OSC

CLOCK SECURITYSYSTEM

(CSS)

MAIN CLOCK

CONTROLLER

(MCC)

MCO

f

CPU

OSC2

ST72334J/N, ST72314J/N, ST72124J

25/125

4.1 LOW VOLTAGE DETECTOR (LVD)

To allow the integration of power management

features in the application, the Low Voltage Detector function (LVD) generates a static reset when

the VDDsupply voltage is below a V

LVDf

reference

value. This means that it secures the power-up as

well as the power-down keeping the ST7 in reset.

The V

LVDf

reference value for a voltage drop is

lower than the V

LVDr

reference value for power-on

in order to avoid a parasitic reset when the MCU

starts running and sinks current on the supply

(hysteresis).

The LVD Reset circuitry generates a reset when

VDDis below:

–V

LVDr

when VDDis rising

–V

LVDf

when VDDis falling

The LVD function is illustrated in the Figure 13.

Provided the minimum VDDvalue (guaranteed for

the oscillator frequency) is below V

LVDf

, the MCU

can only be in two modes:

– under full software control

– in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During aLow Voltage Detector Reset, the RESET

pin is held low, thus permitting the MCU to reset

other devices.

Notes:

1) the LVD allows the device to be used without anyexternal RESET circuitry.

2) three different reference levels are selectable through

the OPTION BYTE according to the application requirement.

LVD application note

Application software can detect a reset caused by

the LVD by reading the LVDRF bit in the CRSR

register.

This bit is set by hardware when a LVD reset is

generated and cleared by software (writing zero).

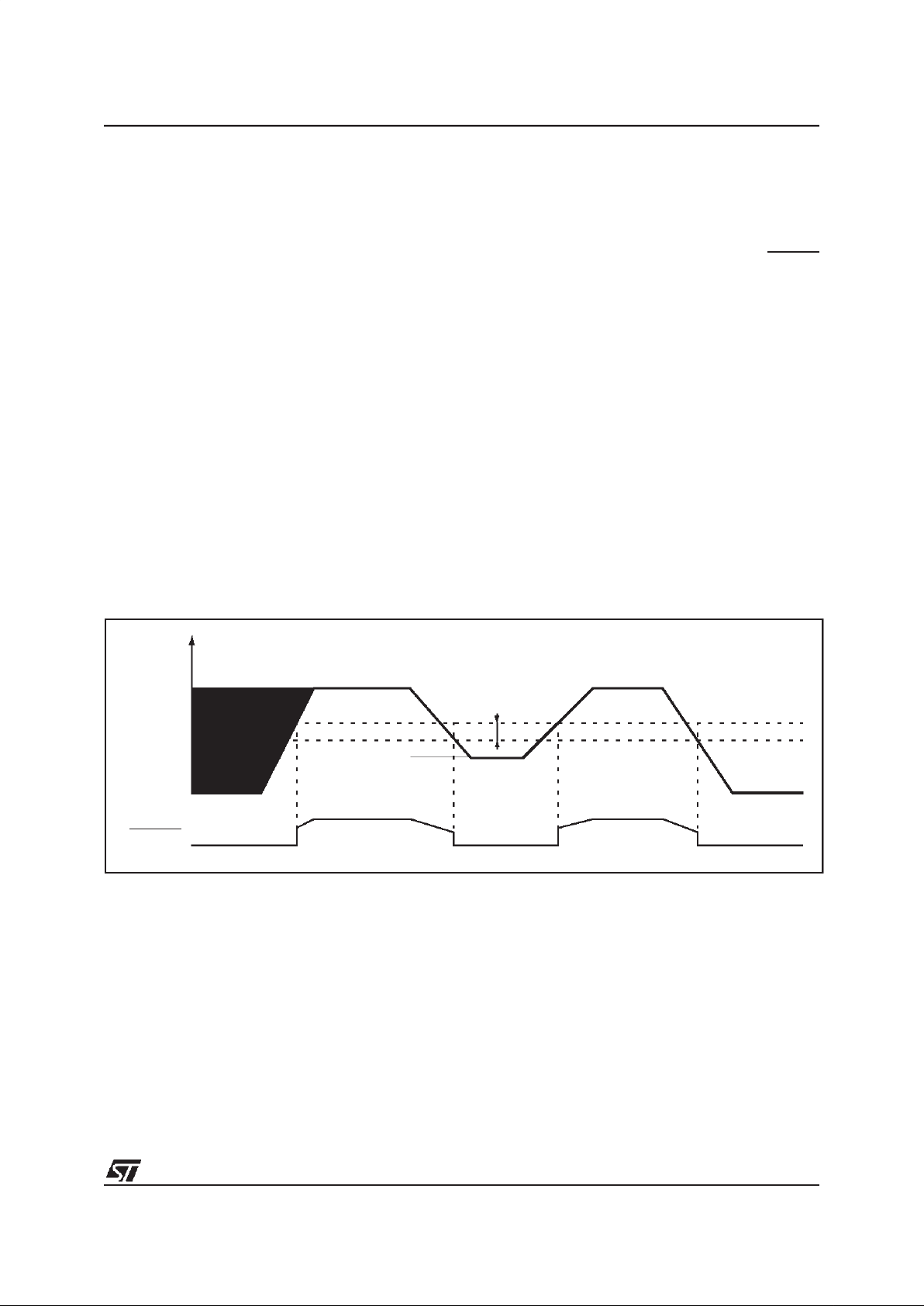

Figure 13. Low Voltage Detector vs Reset

V

DD

V

LVDr

RESET

V

LVDf

HYSTERESIS

V

LVDhyst

ST72334J/N, ST72314J/N, ST72124J

26/125

4.2 RESET SEQUENCE MANAGER (RSM)

The reset sequence manager includes three RESET sources as shown in Figure 15:

■ EXTERNAL RESETSOURCE pulse

■ Internal LVD RESET (Low Voltage Detection)

■ Internal WATCHDOG RESET

These sources act on the RESET PIN and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

The basic RESET sequence consists of 3 phases

as shown in Figure 14:

■ Delay depending on the RESET source

■ 4096 CPU clock cycle delay

■ RESET vector fetch

The 4096 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has

taken place from the Reset state.

The RESET vector fetch phase duration is 2 clock

cycles.

Figure 14. RESET Sequence Phases

Figure 15. Reset Block Diagram

RESET

DELAY

INTERNAL RESET

4096 CLOCK CYCLES

FETCH

VECTOR

f

CPU

COUNTER

RESET

R

ON

V

DD

WATCHDOG RESET

LVD RESET

INTERNAL

RESET

ST72334J/N, ST72314J/N, ST72124J

27/125

RESET SEQUENCE MANAGER (Cont’d)

External RESET pin

The RESETpin is both an input andan open-drain

output with integrated RONweak pull-up resistor.

This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled

low by external circuitry to reset the device.

A RESET signal originating from an external

source must have a duration of at least t

PULSE

in

order to be recognized. Two RESET sequences

can be associated with this RESET source as

shown in Figure 16.

Starting from the external RESET pulse recognition, the device RESET pin acts as an output that

is pulled low during at least t

DELAYmin

.

Figure 16. External RESET Sequences

RESET

RUN

DELAY

INTERNAL RESET

4096 CLOCK CYCLES

FETCH

VECTOR

RUN

RESET PIN

EXTERNAL RESET SOURCE

t

PULSE

V

DD

V

LVDf

V

DDnominal

WATCHDOG RESET

RESET

RUN

INTERNAL RESET

4096 CLOCK CYCLES

FETCH

VECTOR

RUN

RESET PIN

EXTERNAL RESET SOURCE

t

PULSE

WATCHDOG RESET

DELAY

V

DD

V

LVDf

V

DDnominal

SHORT PULSE ON RESET PINLONG PULSE ON RESET PIN

t

DELAYmin

ST72334J/N, ST72314J/N, ST72124J

28/125

RESET SEQUENCE MANAGER (Cont’d)

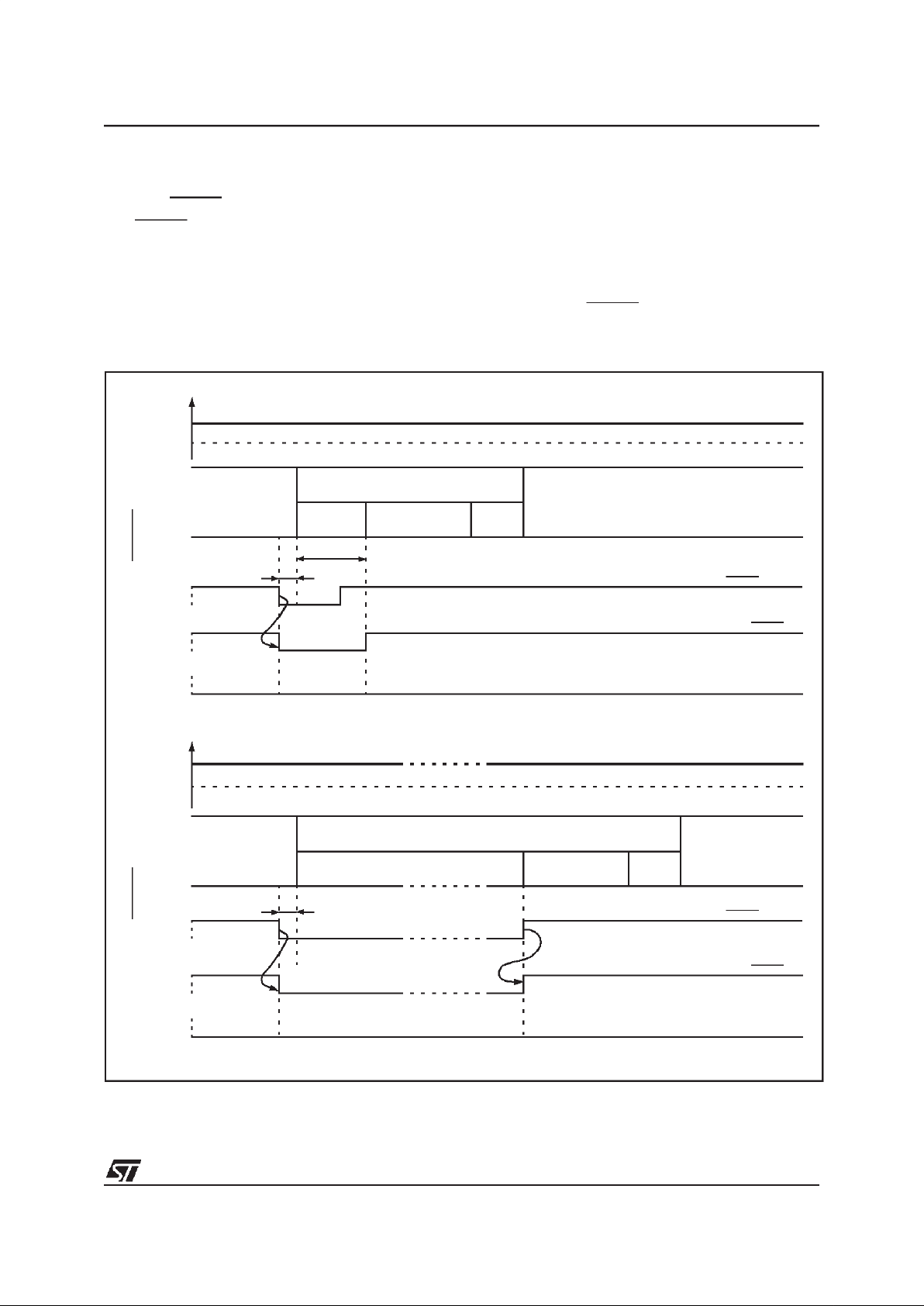

Internal Low Voltage Detection RESET

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

■ Power-On RESET

■ Voltage Drop RESET

The device RESET pin acts as an output that is

pulled low when VDD<V

LVDr

(rising edge) or

VDD<V

LVDf

(falling edge) as shown in Figure 9.

Figure 17. LVD RESET Sequences

RESET

RUN

INTERNAL RESET

4096 CLOCK CYCLES

FETCH

VECTOR

RESET PIN

EXTERNAL RESET SOURCE

WATCHDOG RESET

DELAY

RESET

RUN

INTERNAL RESET

4096 CLOCK CYCLES

FETCH

VECTOR

RUN

RESET PIN

EXTERNAL RESET SOURCE

V

DD

V

DDnominal

WATCHDOG RESET

DELAY

V

LVDr

V

LVDf

V

DD

V

DDnominal

V

LVDr

POWER-ON RESET

VOLTAGE DROP RESET

ST72334J/N, ST72314J/N, ST72124J

29/125

RESET SEQUENCE MANAGER (Cont’d)

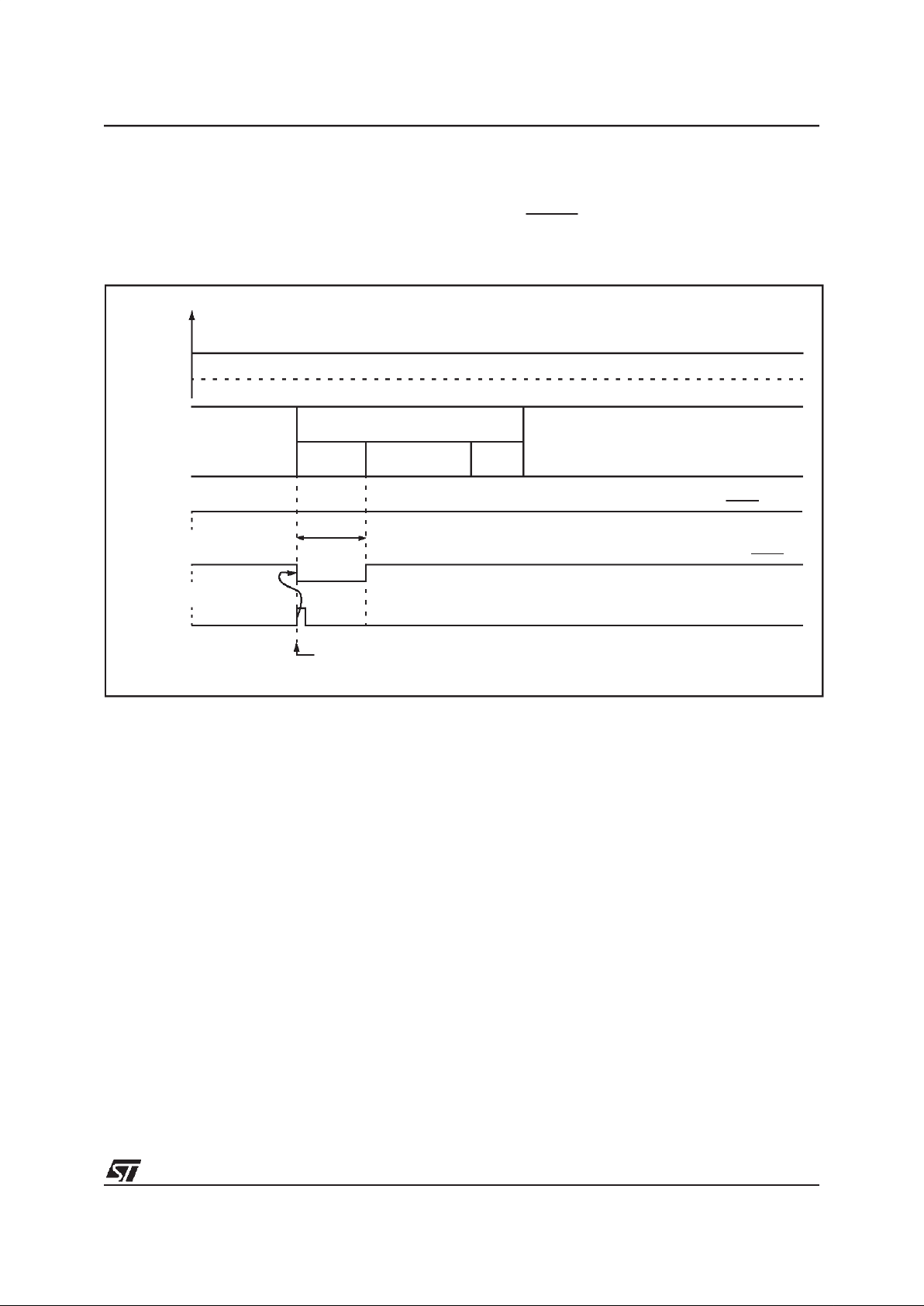

Internal Watchdog RESET

The RESET sequence generated by a internal

Watchdog counter overflow is shown in Figure 18.

Starting from the Watchdog counter underflow, the

device RESET pin acts as an output that is pulled

low during at least t

DELAYmin

.

Figure 18. Watchdog RESET Sequence

RESET

RUN

DELAY

INTERNAL RESET

4096 CLOCK CYCLES

FETCH

VECTOR

RUN

RESET PIN

EXTERNAL RESET SOURCE

V

DD

V

LVDf

V

DDnominal

WATCHDOG RESET

WATCHDOG UNDERFLOW

t

DELAYmin

ST72334J/N, ST72314J/N, ST72124J

30/125

MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by 7

different sources coming from the multi-oscillator

block:

■ an external source

■

4 crystal or ceramic resonator oscillators

■ 1 external RC oscillator

■ 1 internal high frequency RC oscillator

Each oscillator is optimized for a given frequency

range in terms of consumption and is selectable

through the OPTION BYTE.

External Clock Source

The default OPTION BYTE value selects the External Clock in the MO block. In this mode,a clock

signal (square, sinus or triangle) with ~50% duty

cycle has to drive the OSC1 pin while the OSC2

pin is tied to ground (see Figure 19).

Figure 19. MO External Clock

Crystal/Ceramic Oscillators

This family of oscillators has the advantage of producing a high accuracy on the main clock of the

ST7. The selection within a list of 4 oscillators with

different frequency ranges has to be done by OPTION BYTE in order toreduce the consumption. In

this mode of the MO block, the resonator and the

load capacitances have to be connected as shown

in Figure 20 and have to be mounted as close as

possible to the oscillator pins in order to minimize

output distortion and start-up stabilization time.

The loading capacitance values must be adjusted

according to the selected oscillator.

These oscillators, when selected via the OPTION

BYTE, are not stopped during the RESET phase

to avoid losing time in the oscillator start-up phase.

Figure 20. MO Crystal/Ceramic Resonator

OSC1 OSC2

EXTERNAL

ST7

SOURCE

OSC1 OSC2

LOAD

CAPACITANCES

ST7

C

L1

C

L0

ST72334J/N, ST72314J/N, ST72124J

31/125

MULTI-OSCILLATOR (Cont’d)

External RC Oscillator

This oscillator allows a low cost solution for the

main clockof the ST7 using only an external resistor and an external capacitor (see Figure 21). The

selection of the external RC oscillator has to be

done by OPTION BYTE.

The frequency of the external RC oscillator (in the

range of some MHz.) is fixed by the resistor and

the capacitor values:

The previousformula shows that in this MO mode,

the accuracy of the clock is directly linked to the

accuracy of the discrete components.

Figure 21. MO External RC

Internal RC Oscillator

The Internal RC oscillator mode is based on the

same principle as the External RC oscillator including the resistance and the capacitance of the

device. This mode is the most cost effective one

with the drawback of a lower frequency accuracy.

Its frequency is in the range of several MHz.

In this mode, the two oscillator pins have tobe tied

to ground as shownin Figure 22.

The selection of the internal RC oscillator has to

be done by OPTION BYTE.

Figure 22. MO InternalRC

Note:

1) This formula provides an approximation of the frequency with typical REXand CEXvalues at VDD=5V.

It is given only as design guidelines.

f

OSC

~

4

REX.C

EX

1)

OSC1 OSC2

ST7

C

EX

R

EX

OSC1 OSC2

ST7

ST72334J/N, ST72314J/N, ST72124J

32/125

4.3 CLOCK SECURITY SYSTEM (CSS)

The Clock Security System (CSS) protects the

ST7 against main clock problems. To allow the integration of the security features in the applications, itis based on a clock filter control and anInternal Safe Oscillator. The CSS can be disabled by

OPTION BYTE.

4.3.1 Clock Filter Control

The ClockFilter is based on a clock frequency limitation function.

This filter function is able to detect and filter high

frequency spikes on the ST7 main clock.

If the oscillator is not working properly (e.g. working at a harmonic frequency of the resonator), the

current active oscillator clock can be totally filtered, and then no clock signal is available for the

ST7 from this oscillator anymore. If the original

clock source recovers, the filtering is stopped automatically and the oscillator supplies the ST7

clock.

4.3.2 Safe Oscillator Control

The Safe Oscillator of the CSS block is a low frequency back-up clock source (see Figure 24).

If the clock signal disappears (due to a broken or

disconnected resonator...) during a Safe Oscillator

period, the Safe oscillator delivers a low frequency

clock signal which allows the ST7 to perform some

rescue operations.

Automatically, the ST7 clocksourceswitches back

from the Safe Oscillator if the original clocksource

recovers.

Limitation detection

The automatic Safe Oscillator selection is notified

by hardware setting the CSSD bit of the CRSR

register. An interrupt can be generated if the CSSIE bit has been previously set.

These two bits are described in the CRSR register

description.

Figure 23. Clock Filter Function

Figure 24. Safe Oscillator Function

MAIN

OSCILLATOR

CLOCK

INTERNAL

ST7

CLOCK

MAIN

OSCILLATOR

CLOCK

INTERNAL

ST7

CLOCK

SAFE

OSCILLATOR

CLOCK

ST72334J/N, ST72314J/N, ST72124J

33/125

4.4 SUPPLY, RESET AND CLOCK REGISTER DESCRIPTION

CLOCK RESET AND SUPPLY REGISTER

(CRSR)

Read/Write

Reset Value: 000x 000x (00h)

Bit 7:5 = Reserved, always read as 0.

Bit 4 = LVDRF

LVD reset flag

This bit indicates that the last Reset was generated bythe LVD block. It is set by hardware (LVDreset) and cleared by software (writing zero). See

WDGRF flag description for more details. When

the LVDis disabled by OPTIONBYTE,theLVDRF

bit value is undefined.

Bit 3 = Reserved, always read as 0.

Bit 2 = CSSIE

Clock security syst.interrupt enable

This bit enables the interrupt when a disturbance

is detected by the Clock Security System (CSSD

bit set). It is set and clearedby software.

0: Clock security system interrupt disabled

1: Clock security system interrupt enabled

When the CSS is disabled by OPTION BYTE, the

CSSIE bit has no effect.

Bit 1 = CSSD

Clock security system detection

This bit indicates that the safe oscillator of the

Clock Security System blockhas been selected by

hardware due to a disturbance on the main clock

signal (f

OSC

). It is set by hardware and cleared by

a read of the CRSR register when the original oscillator recovers.

0: Safe oscillator is not active

1: Safe oscillator has been activated

When the CSS is disabled by OPTION BYTE, the

CSSD bit value is forced to 0.

Bit 0 = WDGRF

Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software

(writing zero) or a LVD Reset (to ensure a stable

cleared state of the WDGRF flag when CPU

starts).

Combined with the LVDRF flag information, the

flag description is given by the following table.

Application notes

In case the LVDRF flag is not cleared upon another RESET type occurs (extern or watchdog), the

LVDRF flagremains set to keep trace of the original failure.

In this condition, a watchdog reset can be detected by the software while an external reset not.

Table 4. Clock, Reset and Supply Register Map and Reset Values

70

000

LVD

RF

0

CSSIECSSDWDG

RF

RESET Sources LVDRF WDGRF

External RESET pin 0 0

Watchdog 0 1

LVD 1 X

Address

(Hex.)

Register

Label

76543210

002Bh

CRSR

Reset Value 0 0 0

LVDRF

x0

CFIE

0

CSSD0WDGRF

x

ST72334J/N, ST72314J/N, ST72124J

34/125

4.5 MAIN CLOCK CONTROLLER (MCC)

The MCC block supplies the clock for the ST7

CPU and its internal peripherals. It allows to manage the power saving modes such as the SLOW

and ACTIVE-HALT modes. The whole functionality is managed by the Main Clock Control/Status

Register (MCCSR) and the Miscellaneous Register 1 (MISCR1).

The MCC block consists of:

– a programmable CPU clock prescaler

– a time base counter with interrupt capability

– a clock-out signalto supply external devices

The prescaler allows to select the main clock frequency and is controlled with three bits of the

MISCR1: CP1, CP0 and SMS.

The counterallows to generate an interrupt based

on a accurate real time clock. Four different time

bases depending directly on f

OSC

are available.

The wholefunctionality is controlled by four bits of

the MCCSR register: TB1, TB0, OIE and OIF.

The clock-out capability allowsto configure a dedicated I/O port pin as an f

OSC

/2 clock out to drive

external devices. It is controlled by the MCO bit in

the MISCR1 register.

When selected, the clock out pin suspends the

clock during ACTIVE-HALT mode.

Figure 25. Main Clock Controller (MCC) Block Diagram

DIV 2, 4, 8, 16

MCC INTERRUPT

DIV 2

SMSCP1 CP0

TB1 TB0 OIE OIF

CPU CLOCK

MISCR1

PROGRAMMABLE

DIVIDER

TO CPU AND

PERIPHERALS

f

OSC

f

CPU

MCO

PORT

FUNCTION

ALTERNATE

OSC2

OSC1

MCO ----

0000MCCSR

OSCILLATOR

MCC

f

OSC

/2

ST72334J/N, ST72314J/N, ST72124J

35/125

MAIN CLOCK CONTROLLER (Cont’d)

MISCELLANEOUS REGISTER 1 (MISCR1)

See section 6.2 on page 47.

MAIN CLOCK CONTROL/STATUS REGISTER

(MCCSR)

Read/Write

Reset Value: 0000 0001 (01h)

Bit 7:4 = Reserved, always read as 0.

Bit 3:2 = TB1-TB0

Time base control

These bits select the programmable divider time

base. They are set and cleared by software.

A modification of the time base is taken into account at the end of the current period (previously

set) to avoid unwanted time shift. This allows to

use this time base as a real time clock.

Bit 1 = OIE

Oscillator interrupt enable

This bit set and cleared by software.

0: Oscillator interrupt disabled

1: Oscillator interrupt enabled

This interrupt allows to exit from ACTIVE-HALT

mode.

When this bit is set,calling the ST7 software HALT

instruction enters theACTIVE-HALTpower saving

mode.

Bit 0 = OIF

Oscillator interrupt flag

This bit is set by hardware andcleared by software

reading the CSR register. It indicates when set

that the mainoscillator has measured the selected

elapsed time (TB1:0).

0: Timeout not reached

1: Timeout reached

Warning: The BRES and BSET instructions must

not be used on the MCCSR register to avoid unintentionally clearing the OIF bit.

Table 5. MCC Register Map and Reset Values

70

0000TB1TB0OIEOIF

Counter

Prescaler

Time Base

TB1 TB0

f

OSC

=8MHz f

OSC

=16MHz

32000 4ms 2ms 0 0

64000 8ms 4ms 0 1

160000 20ms 10ms 1 0

400000 50ms 25ms 1 1

Address

(Hex.)

Register

Label

76543210

0029h

MCCSR

Reset Value 0 0 0 0

TB1

0

TB0

0

OIE

0

OIF

1

ST72334J/N, ST72314J/N, ST72124J

36/125

5 INTERRUPTS & POWER SAVING MODES

5.1 INTERRUPTS

The ST7 core may be interruptedby one oftwo different methods: maskable hardware interrupts as

listed in the Interrupt Mapping Table and a nonmaskable software interrupt (TRAP). The Interrupt

processing flowchart is shown in Figure 26.

The maskableinterrupts must be enabled clearing

the I bit in order to be serviced. However, disabled

interrupts may be latched and processed when

they are enabled (see external interrupts subsection).

When an interrupt has to be serviced:

– Normal processing is suspended at the end of

the current instruction execution.

– The PC, X, A and CC registers are saved onto

the stack.

– The I bit of the CC register is set to prevent addi-

tional interrupts.

– ThePC isthenloaded with the interrupt vectorof

the interruptto service and the first instruction of

the interrupt service routine is fetched (refer to

the Interrupt Mapping Tablefor vector addresses).

The interrupt service routine should finish with the

IRET instruction which causes the contents of the

saved registers to be recovered from thestack.

Note: As a consequence of the IRET instruction,

the I bit will be cleared and the main program will

resume.

Priority management

By default, the interrupt being serviced cannot be

interrupted because the I bit is set by hardware

when entering an interrupt routine.

If several interrupts are simultaneously pending, a

hardware priority defines which one will be serviced first (see the Interrupt Mapping Table).

Non Maskable Software Interrupts

This interrupt is entered when the TRAP instruction is executed regardless of the stateof theI bit.

It will be serviced according to the flowchart on

Figure 26.

Interrupts and Low power mode

All interrupts allow the processor to leave the Wait

low power mode. Only external and specific mentioned interrupts allow the processor to leave the

Halt low power mode (refer to the “Exit from HALT“

column in the InterruptMapping Table).

External Interrupts

External interrupt vectors can be loaded in the PC

register if the corresponding external interrupt occurred and if the I bit is cleared. These interrupts

allow the processor to leave the Halt low power

mode.

The external interrupt polarity is selected through

the miscellaneous register or interrupt register (if

available).

External interrupt triggered on edge will be latched

and the interrupt request automatically cleared

upon entering the interrupt service routine.

If several input pins, connected to the same interrupt vector, are configured as interrupts, their signals are logically ANDed before entering the edge/

level detection block.

Warning: The type of sensitivity defined in the

Miscellaneous or Interrupt register (if available)

applies to the EI source. In case of an ANDed

source (as described on the I/O ports section), a

low level on an I/O pin configured as input with interrupt, masks the interrupt request even in case

of rising-edge sensitivity.

Peripheral Interrupts

Different peripheral interrupt flags in the status

register are able to cause an interrupt when they

are active if both:

– The I bit of the CC register is cleared.

– Thecorresponding enable bit is setin thecontrol

register.

If any of these two conditions is false, the interrupt

is latched and thus remains pending.

Clearing an interrupt request is done by:

– writing “0” to the corresponding bit in the status

register or

– an access to the status register while the flag is

set followed by a read or write of an associated

register.

Note: the clearing sequence resets the internal

latch. A pending interrupt (i.e. waiting for being enabled) will therefore be lost ifthe clear sequence is

executed.

ST72334J/N, ST72314J/N, ST72124J

37/125

INTERRUPTS (Cont’d)