SGS Thomson Microelectronics ST62T35BQ6, ST62T35BQ3, ST62P35BQ1, ST62P35BQ6, ST62P35BQ3 Datasheet

...

March 1998 1/82

R

Rev. 2.3

ST62T35B/E35B

8-BIT OTP/EPROM MCUs WITH A/D CONVERTER,

16-BIT AUTO-RELOAD TIMER, EEPROM, SPI AND UART

■ 3.0 to 6.0V Supply Operating Range

■ 8 MHz Maximum Clock Frequency

■

-40 to +125°C Operating Temperature Range

■

Run, Wait and Stop Modes

■ 5 Interrupt Vectors

■ Look-up Table capability in Program Memory

■

Data Storage in Program Memory:

User selectable size

■ Data RAM: 192 bytes

■ Data EEPROM: 128 bytes

■

User Programmable Options

■ 36 I/O pins, fully programmable as:

– Input with pull-up resistor

– Input without pull-up resistor

– Input with interrupt generation

– Open-drain or push-pull output

– Analog Input

■ 12 I/O lines can sink up to 20mA to drive LEDs

or TRIACs directly

■

8-bit Timer/Counter with 7-bit programmable

prescaler

■ 16-bit Auto-reload Timer with 7-bit

programmable prescaler (AR Timer)

■

Digital Watchdog

■ 8-bit A/D Converter with 24 analog inputs

■ 8-bit Synchronous Peripheral Interface (SPI)

■

8-bit Asynchronous Peripheral Interface

(UART)

■ On-chip Clockoscillatorcan bedriven byQuartz

Crystal or Ceramic resonator

■

Oscillator Safe Guard

■

One external Non-Maskable Interrupt

■ ST623x-EMU2 Emulation and Development

System (connects to an MS-DOS PC via a

parallel port).

DEVICE SUMMARY

(See end of Datasheet for Ordering Information)

PQFP52

CQFP52W

DEVICE

OTP

(Bytes)

EPROM

(Bytes)

I/O Pins

ST62T35B 7948 - 36

ST62E35B - 7948 36

1

2/82

Table of Contents

82

2

ST62T35B/E35B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

1 GENERAL DESCRIPTION . . . . . . . ...............................................5

1.1 INTRODUCTION .........................................................5

1.2 PIN DESCRIPTIONS . . . . . . . . . . ............................................7

1.3 MEMORYMAP ..........................................................8

1.3.1 Introduction . . . . . . . . ................................................8

1.3.2 Program Space . . . . . . . . . . . . . . . . . . . . . . . . . . . ..........................8

1.3.3 Data Space . . . . . . . . ...............................................10

1.3.4 Stack Space . . . . . . . . . . . . . . . . . ......................................10

1.3.5 Data Window Register (DWR) . . . . . . . . . . . . . . . . . . . . .....................11

1.3.6 Data RAM/EEPROM Bank Register (DRBR)..............................12

1.3.7 EEPROM Description ...............................................13

1.4 PROGRAMMING MODES .................................................15

1.4.1 Option Byte . . . . . . . . ...............................................15

1.4.2 Program Memory . . . . ...............................................15

1.4.3 EEPROM Data Memory . . .. . . . . . . . . ..................................15

1.4.4 EPROMErasing....................................................15

2 CENTRAL PROCESSING UNIT .................................................16

2.1 INTRODUCTION ........................................................16

2.2 CPU REGISTERS . . . . . . . . ...............................................16

3 CLOCKS, RESET, INTERRUPTS AND POWER SAVING MODES . . . . . . . ..............18

3.1 CLOCKSYSTEM........................................................18

3.1.1 Main Oscillator . . . . . . . . . . ...........................................18

3.1.2 Low Frequency Auxiliary Oscillator (LFAO) . . . . . . . . . . . . . . . ................19

3.1.3 Oscillator Safe Guard . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . ................19

3.2 RESETS...............................................................22

3.2.1 RESET Input ......................................................22

3.2.2 Power-on Reset . . . . . . . . . . . . . . . .....................................22

3.2.3 Watchdog Reset . . . . ...............................................23

3.2.4 Application Notes . . . . ...............................................23

3.2.5 MCU Initialization Sequence ..........................................23

3.3 INTERRUPTS . . . . ......................................................25

3.3.1 Interrupt request . . . . . . . . . . . . . . . .....................................25

3.3.2 Interrupt Procedure . . . ..............................................26

3.3.3 Interrupt Option Register (IOR) . . . . ....................................27

3.3.4 Interrupt sources . . . . ...............................................27

3.4 POWER SAVING MODES .................................................30

3.4.1 WAIT Mode . . . . . . . . ...............................................30

3.4.2 STOPMode.......................................................30

3.4.3 Exit from WAIT and STOP Modes . . . ...................................31

3/82

Table of Contents

3

4 ON-CHIP PERIPHERALS . . . ...................................................32

4.1 I/OPORTS.............................................................32

4.1.1 Operating Modes . . . . ...............................................33

4.1.2 Safe I/O State Switching Sequence . . . ..................................34

4.1.3 ARTimer alternate functions ..........................................36

4.1.4 SPI alternate functions . . . ............................................36

4.1.5 UART alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ................36

4.1.6 I/O Port Option Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ................38

4.1.7 I/O Port Data Direction Registers. . . ....................................38

4.1.8 I/O Port Data Registers . . . . ..........................................38

4.2 TIMER ................................................................39

4.2.1 Timer Operating Modes . . .. . . . . . . . . ..................................40

4.2.2 Timer Interrupt . . . . . . . . . . ...........................................40

4.2.3 Application Notes . . . . ...............................................41

4.2.4 Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .........................41

4.3 ARTIMER 16 . . . ........................................................42

4.3.1 CENTRAL COUNTER . . . ............................................43

4.3.2 SIGNAL GENERATION MODES . . . ....................................44

4.3.3 TIMINGS MEASUREMENT MODES. . ..................................46

4.3.4 INTERRUPT CAPABILITIES ..........................................48

4.3.5 CONTROL REGISTERS . . . ..........................................49

4.3.6 16-BIT REGISTERS . . . . . . . . ........................................51

4.4 A/D CONVERTER (ADC) . . . ..............................................53

4.4.1 Application Notes . . . . ...............................................53

4.5 U. A. R. T. (UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER). ..........55

4.5.1 PORTS INTERFACING . . . . . . . . . . . . ..................................55

4.5.2 CLOCK GENERATION . . . . ..........................................56

4.5.3 DATA TRANSMISSION . . .. . . . . . . . . ..................................56

4.5.4 DATA RECEPTION .................................................57

4.5.5 INTERRUPT CAPABILITIES ..........................................57

4.5.6 REGISTERS ......................................................57

4.6 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . ........................59

5SOFTWARE ................................................................61

5.1 ST6 ARCHITECTURE . . . . . . . . . . . . . . . .....................................61

5.2 ADDRESSING MODES . . . . ...............................................61

5.3 INSTRUCTION SET . . . ...................................................62

6 ELECTRICAL CHARACTERISTICS. . . . . . . . . . . . ..................................67

6.1 ABSOLUTE MAXIMUM RATINGS. ..........................................67

6.2 RECOMMENDED OPERATING CONDITIONS. . . ..............................68

6.3 DC ELECTRICAL CHARACTERISTICS ......................................69

6.4 AC ELECTRICAL CHARACTERISTICS ......................................70

6.5 A/D CONVERTER CHARACTERISTICS. . . ...................................70

6.6 TIMER CHARACTERISTICS . . . ............................................71

6.7 .SPI CHARACTERISTICS .................................................71

6.8 ARTIMER16 ELECTRICAL CHARACTERISTICS. . . . . . . . . . . . . . . ................71

4/82

Table of Contents

82

1

7 GENERAL INFORMATION . . . . . . . . . . ...........................................72

7.1 PACKAGE MECHANICAL DATA. . . . ........................................72

7.2 ORDERING INFORMATION ...............................................73

ST62P35B . ........................................75

1 GENERAL DESCRIPTION . . . . . . . ..............................................76

1.1 INTRODUCTION ........................................................76

1.2 ORDERING INFORMATION ...............................................76

1.2.1 Transfer of Customer Code . ..........................................76

1.2.2 Listing Generation and Verification . . . . . . . . . . ...........................76

ST6235B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

1 GENERAL DESCRIPTION . . . . . . . ..............................................80

1.1 INTRODUCTION ........................................................80

1.2 ROM READOUT PROTECTION . . . . . . . . . . . . . . . . . . . . ........................80

1.3 ORDERING INFORMATION ...............................................82

1.3.1 Transfer of Customer Code . ..........................................82

1.3.2 Listing Generation and Verification . . . . . . . . . . ...........................82

5/82

ST62T35B/E35B

1 GENERAL DESCRIPTION

1.1 INTRODUCTION

The ST62T35B and ST62E35B devices are low

cost members of the ST62xx 8-bit HCMOS family

of microcontrollers, which is targeted at low to medium complexity applications. All ST62xx devices

are based on a building block approach: a com-

mon core is surrounded by a number of on-chip

peripherals.

The ST62E35B is the erasable EPROM version of

the ST62T35B device, which may be used to emulate the ST62T35B device, aswell as the respective ST6235B ROM devices.

Figure 1. Block Diagram

TEST

NMI

INTERRUPT

PROGRAM

PC

STACK LEVEL 1

STACK LEVEL 2

STACK LEVEL 3

STACK LEVEL 4

STACK LEVEL 5

STACK LEVEL 6

POWER

SUPPLY

OSCILLATOR

RESET

DATA ROM

USER

SELECTABLE

DATA RAM

PORT A

PORT B

TIMER

DIGITAL

8 BIT CORE

TEST/V

PP

8-BIT

A/D CONVERTER

PA0..PA1 / 20 mA Sink

V

DDVSS

OSCin OSCout RESET

WATCHDOG

Memory

PORT C

SPI (SERIAL

PERIPHERAL

INTERFACE)

AUTORELOAD

TIMER

192 Bytes

7948 bytes

DATA EEPROM

128 Bytes

PA2/OVF/ 20 mA Sink

PA3/PWM/20 mA Sink

PA4/Ain/CP1

PA5/Ain/CP2

PB0..PB7/Ain

PC4..PC7/Ain

PORT D

PORT E

PD0,PD6,PD7/Ain

PD1/Ain/Scl

PD2/Ain/Sin

PD3/Ain/Sout

PD4/Ain/RXD1

PD5/Ain/TXD1

PE0...PE7

PA6...PA7/Ain

(VPP on EPROM/OTP versions only)

TIMER

VR01823E

UART

4

6/82

ST62T35B/E35B

INTRODUCTION (Cont’d)

OTP and EPROM devices are functionally identical. The ROM based versions offerthe same functionality selecting as ROM options the options defined in the programmable option byte of the

OTP/EPROM versions.OTP devices offer all the

advantages of user programmability at low cost,

which make them the ideal choice in a wide range

of applications where frequent code changes,

multiple code versions or last minute programmability are required.

These compact low-cost devices feature a Timer

comprising an 8-bit counter and a 7-bit programmable prescaler, an 16-bit Auto-Reload Timer,

with 2 input capture channels, EEPROM data capability, a serial synchronous port communication

interface (SPI), a serial asynchronous port interface (UART), an 8-bit A/D Converter with 24 analog inputs and a Digital Watchdog timer, making

them well suited for a wide range of automotive,

appliance and industrial applications.

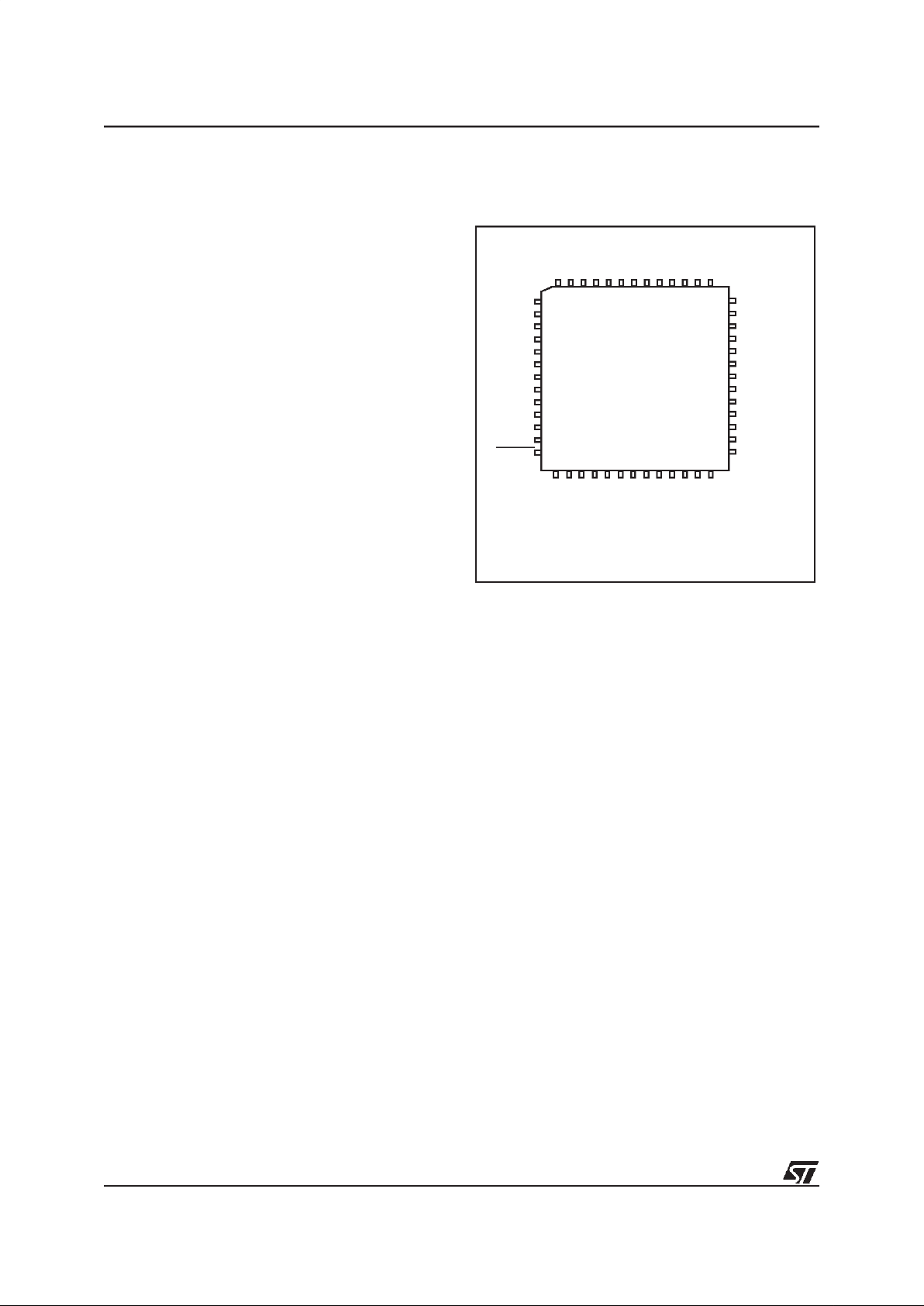

Figure 2. ST62T35B/E35B Pin Configuration

1

2

3

4

5

6

7

8

9

10

11

12

13

39

38

37

36

35

34

32

31

30

29

28

27

33

141516171819202122232425

26

52515049484746454443424140

NC

OSCin

OSCout

Ain/PC7

Ain/PC6

Ain/PC5

V

SSP

V

DDP

V

SS

V

DD

TEST/V

PP

(1)

RESET

PA4/Ain/CP1

PA5/Ain/CP2

PA6/Ain

PA7/Ain

TIMER

NMI

AV

SS

AV

DD

PD0/Ain

PD1/Ain/SCL

PD2/Ain/Sin

PD3/Ain/Sout

NC

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PA0

PA1

PA2/OVF

PA3/PWM

NC

Ain/PB7

Ain/PB6

Ain/PB5

Ain/PB4

Ain/PB3

Ain/PB0

Ain/PD7

Ain/PD6

Ain/PD5/TXD1

Ain/PD4/RXD1

NC

1. VPPon EPROM/OTP only

VR02008

Ain/PB2

Ain/PB1

Ain/PC4

5

7/82

ST62T35B/E35B

1.2 PIN DESCRIPTIONS

VDDand V

SS

. Power is supplied to the MCU via

these two pins. VDDis the power connection and

VSSis the ground connection.

V

DDp

and V

SSp

.

Power is supplied to the MCU

I/Os independently from the rest of the chip using

these two pins. These pins have to be connected

to the VDD and VSS pins. It is not allowed to leave

any of these pins unconnected or to apply different

potentials respectively to VDD/V

DDp

and

VSS/V

SSp

.

AVDDand AVSS. Power is supplied to the

MCUA/D converter independently from the rest of

the chip using these two pins.

OSCin and OSCout.

These pins are internally

connected to the on-chip oscillator circuit. A quartz

crystal, a ceramic resonator or an external clock

signal can be connected between these two pins.

The OSCin pin is the input pin, the OSCout pin is

the output pin.

RESET

. The active-low RESET pin is used to re-

start the microcontroller.

TEST/VPP. The TEST must be held at VSSfor nor-

mal operation. If TEST pin is connected to a

+12.5V level during the reset phase, the

EPROM/OTP programming Mode is entered.

NMI. The NMI pin provides the capability for asynchronous interruption, by applying an external non

maskable interrupt to the MCU.The NMI input is

falling edge sensitive withSchmitt trigger characteristics. The user can select as option the availability of an on-chip pull-up at this pin.

PA0-PA7. These 8 lines are organised as one I/O

port (A). Each line may be configured under software control as inputs with or without internal pullup resistors, interrupt generating inputs with pullup resistors, open-drain or push-pull outputs.

PA2/OVF, PA3/PWM, PA4/CP1 and PA5/CP2

can be used respectively as overflow output pin,

output compare pin, and as two input capture pins

for the embedded 16-bit Auto-Reload Timer.

In addition, PA4-PA5 can also be used as analog

inputs for the A/D converter whilePA0-PA3 can

sink 20mA for direct LED or TRIAC drive.

PB0...PB7

These 8 lines are organised as one I/O

port (B). Each line may be configured under software control as inputs with or without internal pullup resistors, interrupt generating inputs with pullup resistors, open-drain or push-pull outputs, analog inputs for the A/D converter.

PC4-PC7

. These 4 lines are organised as one I/O

port (C). Each line may be configured under software control as input with or without internal pullup resistor, interrupt generating input with pull-up

resistor, analog input for the A/D converter, opendrain or push-pull output.

PD0...PD7. These 8 lines are organised as one

I/O port (portD). Each line may be configured

under software control as input with or without internal pull-up resistor, interrupt generating input

with pull-up resistor, analog input open-drain or

push-pull output. In adition, the pins PD5/TXD1

and PD4/RXD1 can be used as UART output

(PD5/TXD1) or UART input (PD4/RXD1). The pins

PD3/Sout, PD2/Sin and PD1/SCL can also be

used respectively as data out, data in and Clock

pins for the on-chip SPI.

PE0...PE7. These 8 lines are organised as one I/O

port (PE). Each line may be configured under software control as input with or without internal pullup resistor, interrupt generation input with pull-up

resistor, open-drain or push-pull output. In output

mode, these lines can also sink 20mA for direct

LED and TRIAC driving.

TIMER. This is the TIMER 1 I/O pin. In input

mode, it is connected to the prescaler and acts as

external timer clock or as control gate for the internal timer clock. In output mode, the TIMER pin

outputs the data bit when a time-out occurs.The

user can select as option the availability of an onchip pull-up at this pin.

6

8/82

ST62T35B/E35B

1.3 MEMORY MAP

1.3.1 Introduction

The MCU operates in three separate memory

spaces: Program space, Data space, and Stack

space. Operation in these three memory spaces is

described in the following paragraphs.

Briefly, Program space contains user program

code in Program memory and user vectors; Data

space contains user data in RAM and in Program

memory, and Stack space accommodates six levels of stack for subroutine and interrupt service

routine nesting.

1.3.2 Program Space

Program Space comprises the instructions to be

executed, the data required for immediate addressing mode instructions, the reserved factory

test area and the user vectors. Program Space is

addressed via the 12-bit Program Counter register

(PC register).

Program Space is organised in four 2K pages.

Three of them are addressed in the 000h-7FFh locations of the Program Space by the Program

Counter and by writing the appropriate code in the

Program ROM Page Register (PRPR register). A

common (STATIC) 2K page is available all the

time for interrupt vectors and common subroutines, independently of the PRPR register content.

This “STATIC” page is directly addressed in the

0800h-0FFFh by the MSB of the Program Counter

register PC 11. Note this page can also be addressed in the 000-7FFh range. It is two different

ways of addressing the same physical memory.

Jump from a dynamic page to another dynamic

page is achieved by jumping back to the static

page, changing contents of PRPR and then jumping to the new dynamic page.

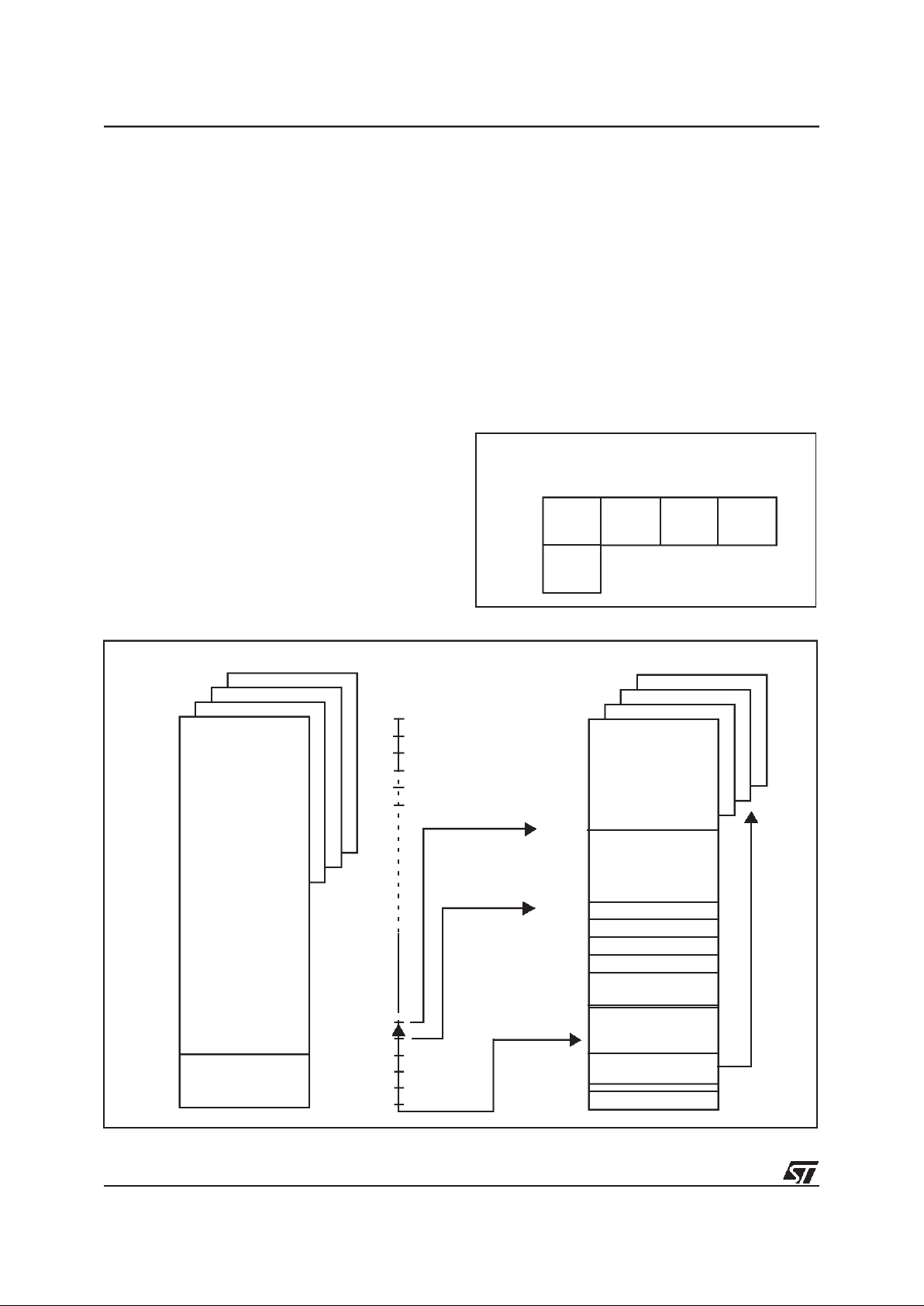

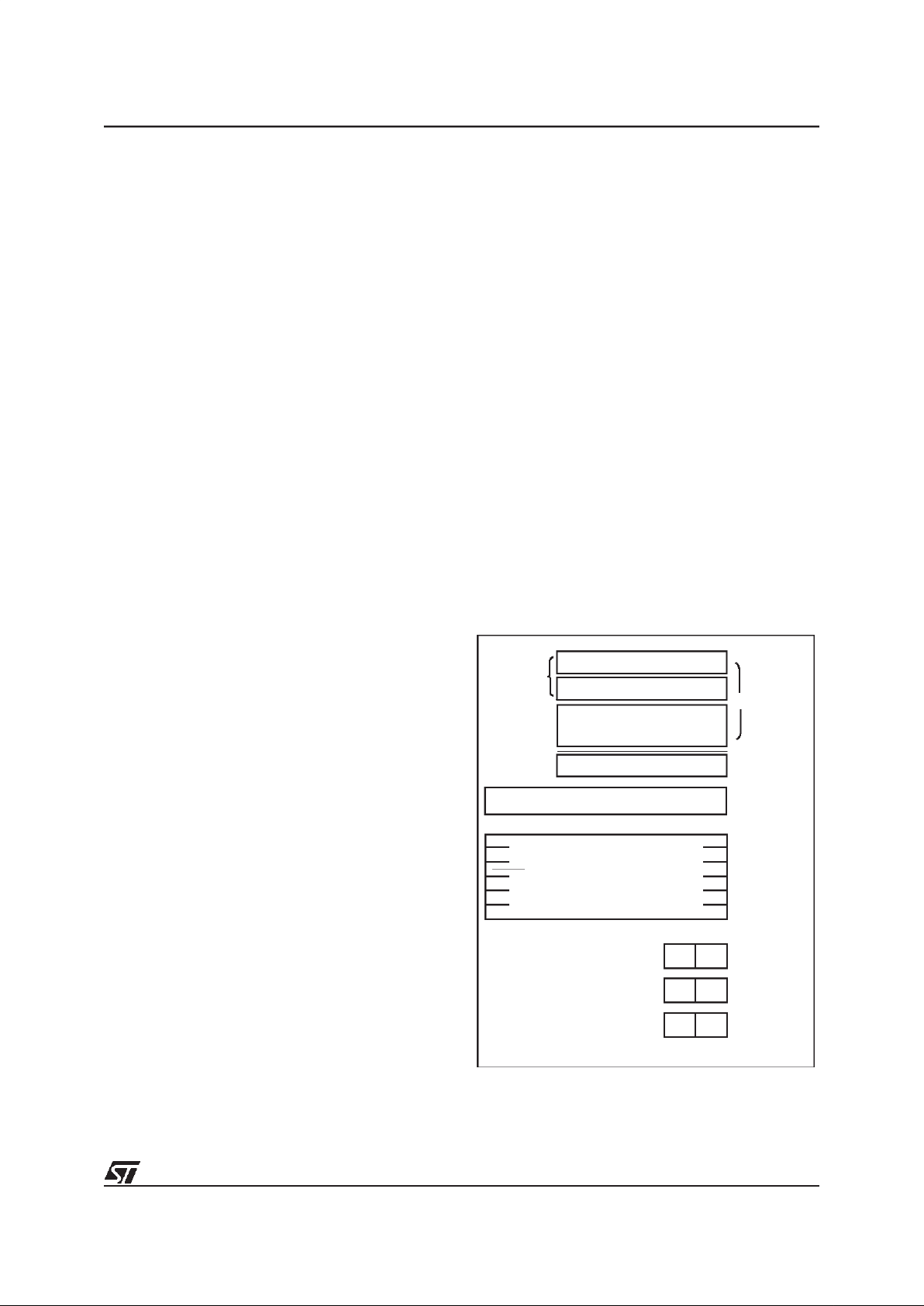

Figure 3. 8Kbytes Program Space Addressing

Figure 4. Memory Addressing Diagram

PC

SPACE

000h

7FFh

800h

FFFh

0000h

1FFFh

Page 0

Page 1

Static

Page

Page 2 Page 3

Page 1

Static

Page

ROM SPACE

PROGRAM SPACE

PROGRAM

INTERRUPT &

RESET VECTORS

ACCUMULATOR

DATA RAM

BANK SELECT

WINDOW SELECT

RAM

X REGISTER

Y REGISTER

V REGISTER

W REGISTER

DATA READ-ONLY

WINDOW

RAM / EEPROM

BANKING AREA

000h

03Fh

040h

07Fh

080h

081h

082h

083h

084h

0C0h

0FFh

0-63

DATA SPACE

0000h

0FF0h

0FFFh

MEMORY

MEMORY

DATA READ-ONLY

MEMORY

VR01568

7

9/82

ST62T35B/E35B

MEMORY MAP (Cont’d)

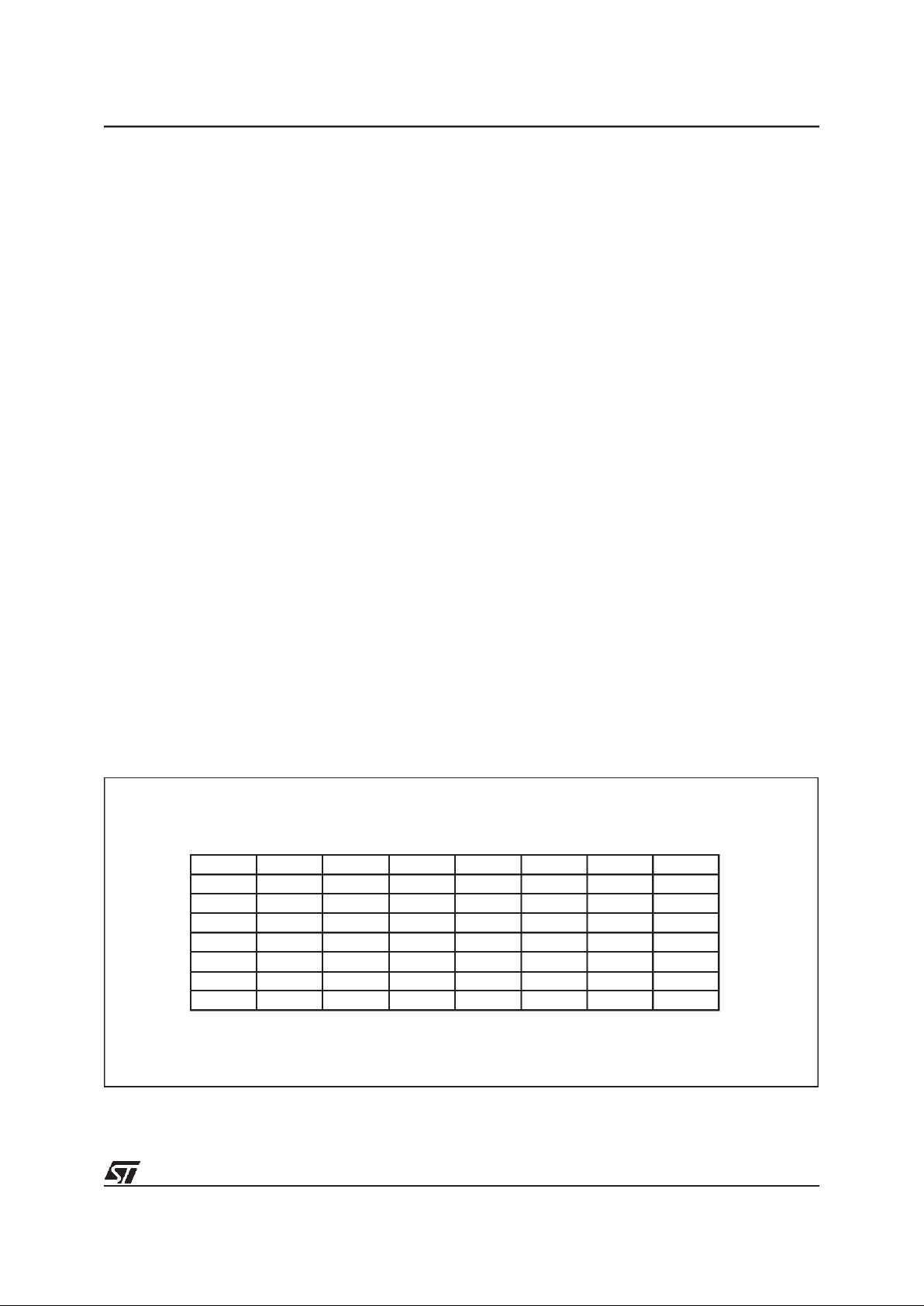

Table 1. ST62E35B/T35B Program Memory Map

Note: OTP/EPROM devices can be programmed

with the development tools available from

SGS-THOMSON (ST62E3X-EPB orST623X-KIT).

1.3.2.1 Program ROM Page Register (PRPR)

The PRPR register can be addressed like a RAM

location in the Data Space at the address CAh ;

nevertheless it is a write only register that cannot

be accessed with single-bit operations. This register is used to select the 2-Kbyte ROM bank of the

Program Space that will be addressed. The

number of the page has to be loaded in thePRPR

register. Refer to the Program Space description

for additional information concerning the use of

this register. The PRPR register is not modified

when an interrupt or a subroutine occurs.

Care is required when handling the PRPR register

as it is write only. For this reason, it is not allowed

to change the PRPR contents while executing interrupt service routine, as the service routine

cannot save and then restore its previous content.

This operation may be necessary if common routines and interrupt service routines take more than

2K bytes ; in this case it could be necessary to divide the interrupt service routine into a (minor) part

in the static page (start and end) and to a second

(major) part in one of the dynamic pages. If it is impossible to avoid the writing of this register in interrupt service routines, an image of this register

must be saved in a RAM location, and each time

the program writes to the PRPR it must write also

to the image register. The image register must be

written before PRPR, so if an interrpt occurs between the two instructions the PRPR is not affected.

Program ROM Page Register (PRPR)

Address: CAh — Write Only

Bits 2-7= Not used.

Bit 5-0 = PRPR1-PRPR0:

Program ROM Select.

These two bits select the corresponding page to

be addressed in the lower part of the 4K program

address space as specified inTable 2.

This register is undefined on Reset. Neither read

nor single bit instructions may be used to address

this register.

Table 2. 8Kbytes Program ROM Page Register

Coding

1.3.2.2 Program Memory Protection

The Program Memory in OTP or EPROM devices

can be protected against external readout of

memory by selecting the READOUT PROTECTION option in the option byte.

In the EPROM parts, READOUT PROTECTION

option can be disactivated only by U.V. erasure

that also results into the whole EPROM context

erasure.

Note: Once the Readout Protection is activated, it

is no longer possible, even for SGS-THOMSON,

to gain access to the Program memory contents.

Returned parts with a protection set can therefore

not be accepted.

ROM Page Device Address Description

Page 0

0000h-007Fh

0080h-07FFh

Reserved

User ROM

Page 1

“STATIC”

0800h-0F9Fh

0FA0h-0FEFh

0FF0h-0FF7h

0FF8h-0FFBh

0FFCh-0FFDh

0FFEh-0FFFh

User ROM

Reserved

Interrupt Vectors

Reserved

NMI Vector

Reset Vector

Page 2

0000h-000Fh

0010h-07FFh

Reserved

User ROM

Page 3

0000h-000Fh

0010h-07FFh

Reserved

User ROM

70

- - - - - - PRPR0 PRPR1

PRPR1 PRPR0 PC bit 11 Memory Page

X X 1 Static Page (Page 1)

0 0 0 Page 0

0 1 0 Page 1 (Static Page

1 0 0 Page 2

1 1 0 Page 3

8

10/82

ST62T35B/E35B

MEMORY MAP (Cont’d)

1.3.3 Data Space

Data Space accommodates allthe data necessary

for processing the user program. This space comprises the RAM resource, the processor core and

peripheral registers, as well as read-only data

such as constants and look-up tables in Program

memory.

1.3.3.1 Data ROM

All read-only data is physically stored in program

memory, which also accommodates the Program

Space. The program memory consequently contains the program code to be executed, as well as

the constants and look-up tables required by the

application.

The Data Space locations in which the different

constants and look-up tables are addressed by

the processor core may be thought of as a 64-byte

window through which it is possible to access the

read-only data stored in Program memory.

1.3.3.2 Data RAM/EEPROM

In ST6235B and ST62E35B devices, the data

space includes 60 bytes of RAM, the accumulator

(A), the indirect registers (X), (Y), the short direct

registers (V), (W), the I/O port registers, the peripheral data and control registers, the interrupt

option register and the Data ROM Window register (DRW register).

Additional RAM and EEPROM pages can also be

addressed using banks of 64 bytes located between addresses 00ST62T35B and ST62E35Bh

and 3Fh.

1.3.4 Stack Space

Stack space consists of six 12-bit registers which

are used to stack subroutine and interrupt return

addresses, as wellas the current program counter

contents.

Table 3. Additional RAM/EEPROM Banks.

Table 4. ST62T35B Data Memory Space

Device RAM EEPROM

ST62T35B 2 x 64 bytes 2 x 64 bytes

DATAand EEPROM

000h

03Fh

DATA ROM WINDOW AREA

040h

07Fh

X REGISTER 080h

Y REGISTER 081h

V REGISTER 082h

W REGISTER 083h

DATARAM

084h

0BFh

PORT A DATAREGISTER 0C0h

PORT B DATAREGISTER 0C1h

PORT C DATAREGISTER 0C2h

PORT D DATAREGISTER 0C3h

PORT A DIRECTION REGISTER 0C4h

PORT B DIRECTION REGISTER 0C5h

PORT C DIRECTION REGISTER 0C6h

PORT D DIRECTION REGISTER 0C7h

INTERRUPTOPTION REGISTER 0C8h*

DATA ROM WINDOW REGISTER 0C9h*

ROM BANK SELECT REGISTER 0CAh*

RAM/EEPROM BANK SELECT REGISTER 0CBh*

PORT A OPTION REGISTER 0CCh

PORT B OPTION REGISTER 0CDh

PORT C OPTION REGISTER 0CEh

PORT D OPTION REGISTER 0CFh

A/D DATAREGISTER 0D0h

A/D CONTROL REGISTER 0D1h

TIMER 1 PRESCALER REGISTER 0D2h

TIMER 1 COUNTER REGISTER 0D3h

TIMER 1 STATUS/CONTROLREGISTER 0D4h

RESERVED 0D5h

UARTDATA SHIFT REGISTER 0D6h

UARTSTATUSCONTROL REGISTER 0D7h

WATCHDOGREGISTER 0D8h

RESERVED 0D9h

I/O INTERRUPTPOLARITY REGISTER 0DAh

OSCILLATORCONTROL REGISTER 0DBh

SPI INTERRUPT DISABLE REGISTER 0DCh*

SPI DATAREGISTER 0DDh

RESERVED 0DEh

EEPROM CONTROL REGISTER 0DFh

ARTIM16 COMPARE MASK REG. LOW BYTE MASK 0E0h

ARTIM16 2ND STATUSCONTROL REGISTER SCR2 0E1h

ARTIM16 3RD STATUSCONTROL REGISTER SCR3 0E2h

ARTIM16 4TH STATUS CONTROL REGISTER SCR4 0E3h

ARTIM16 1ST STATUSCONTROL REGISTER SCR1 0E8h

ARTIM16 RELOAD CAPTURE REG. HIGH BYTE RLCP 0E9h

ARTIM16 RELOAD CAPTURE REG. LOW BYTE RLCP 0EAh

ARTIM16 CAPTURE REGISTER HIGH BYTE CP 0EBh

ARTIM16 CAPTURE REGISTER LOW BYTE CP 0ECh

ARTIM16COMPAREVALUEREGISTERHIGHBYTECMP 0EDh

ARTIM16 COMPAREVALUE REGISTERLOWBYTECMP 0EEh

ARTIM 16 COMPARE MASK REG. HIGH BYTE MASK 0EFh

RESERVED 0F0h

0FBh

PORT E DATA REGISTER OFCh

PORT E DIRECTION REGISTER 0FDh

PORT E OPTION REGISTER 0FEh

ACCUMULATOR OFFh

* WRITE ONLYREGISTER

9

11/82

ST62T35B/E35B

MEMORY MAP (Cont’d)

1.3.5 Data Window Register (DWR)

The Data read-only memory window is located

from address 0040h to address 007Fh in Data

space. It allows direct reading of 64 consecutive

bytes located anywhere in program memory, between address 0000h and 1FFFh (top memory address depends on thespecific device). All the program memory can therefore beused to store either

instructions or read-only data. Indeed, the window

can be moved in steps of 64 bytes along the programmemory by writingtheappropriate codein the

Data Window Register (DWR).

The DWR can be addressed like any RAM location in the Data Space, it is however a write-only

register and therefore cannot be accessed using

single-bit operations. This register is used to position the 64-byte read-only data window (from address 40h to address 7Fh of the Data space) in

program memory in 64-byte steps. The effective

address of the byte to be read as data in program

memory is obtained by concatenating the 6 least

significant bits of the register address given in the

instruction (as least significant bits) and the content of the DWR register (as most significant bits),

as illustrated in Figure 5 below. For instance,

when addressing location 0040h of the Data

Space, with 0 loaded in the DWR register, the

physical location addressed in program memory is

00h. The DWR register is not cleared on reset,

therefore it must be written to prior to the first access to the Data read-only memory window area.

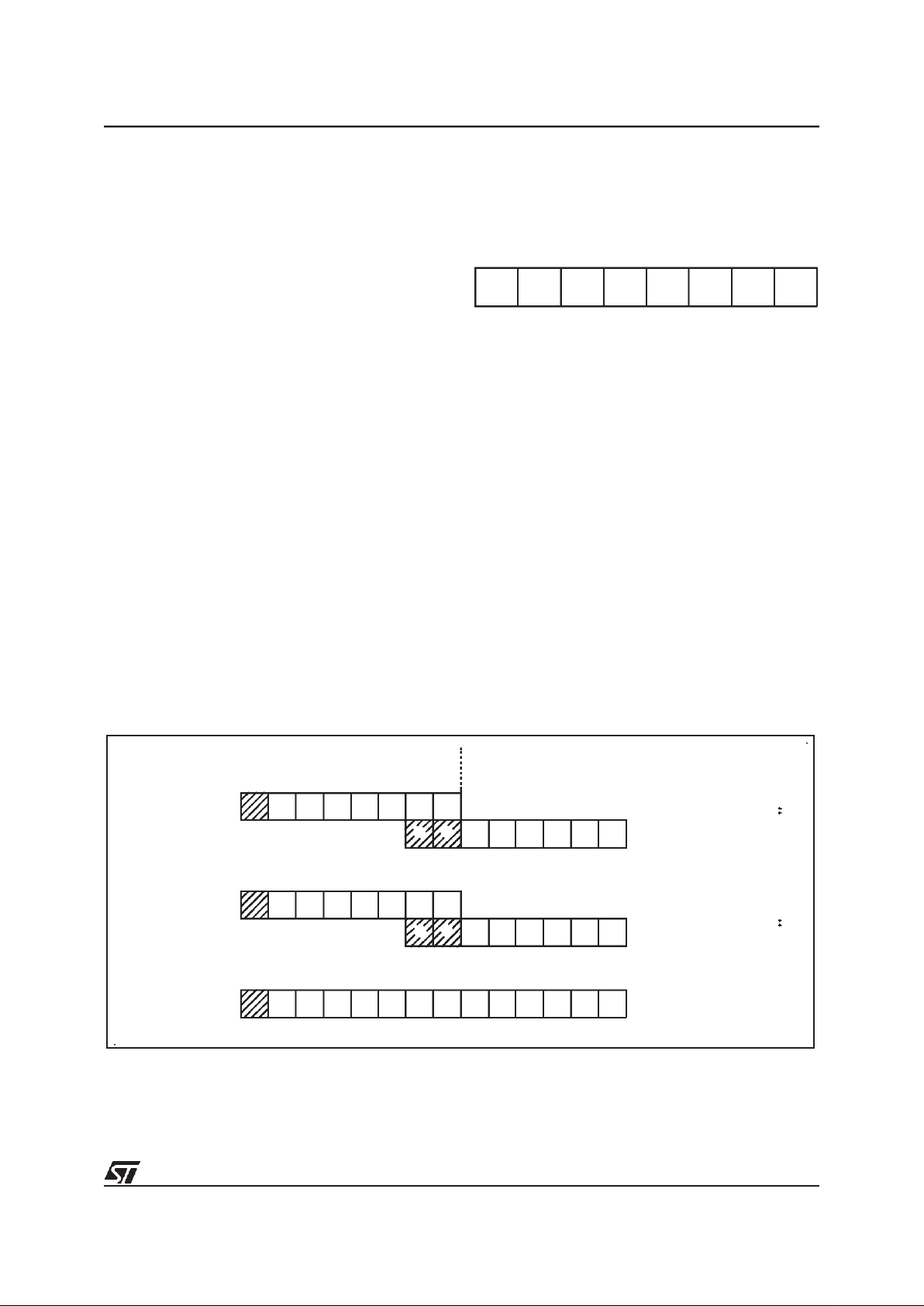

Data Window Register (DWR)

Address: 0C9h — Write Only

Bits 7 = Not used.

Bit 6-0 =

DWR5-DWR0:

Data read-only memory

Window Register Bits.

These are the Data readonly memory Window bits that correspond to the

upper bits of the data read-only memory space.

Caution:

This register is undefined on reset. Neither read nor single bit instructions may be used to

address this register.

Note:

Care is required when handling the DWR

register as it is write only. For this reason, the

DWR contents should not be changed while executing an interrupt service routine, as the service

routine cannot save and then restore the register’s

previous contents. If it is impossible to avoid writing to the DWR during the interrupt service routine, an image of the register must be saved in a

RAM location, and each time the program writes

to the DWR, it must also write to the image register. The image register must be written first so

that, if an interrupt occurs between the two instructions, the DWR is not affected.

Figure 5. Data read-only memory Window Memory Addressing

70

- DWR6 DWR5 DWR4 DWR3 DWR2 DWR1 DWR0

DATA ROM

WINDOW REGISTER

CONTENTS

DATA SPACE ADDRESS

40h-7Fh

IN INSTRUCTION

PROGRAM SPACE ADDRESS

765432 0

543210

543210

READ

1

67891011

0

1

VR0A1573

12

1

0

DATA SPACE ADDRESS

59h

0000

0

1

00

1

11

Example:

(DWR)

DWR=28h

11000000001

ROM

ADDRESS:A19h

11

13

01

10

12/82

ST62T35B/E35B

MEMORY MAP (Cont’d)

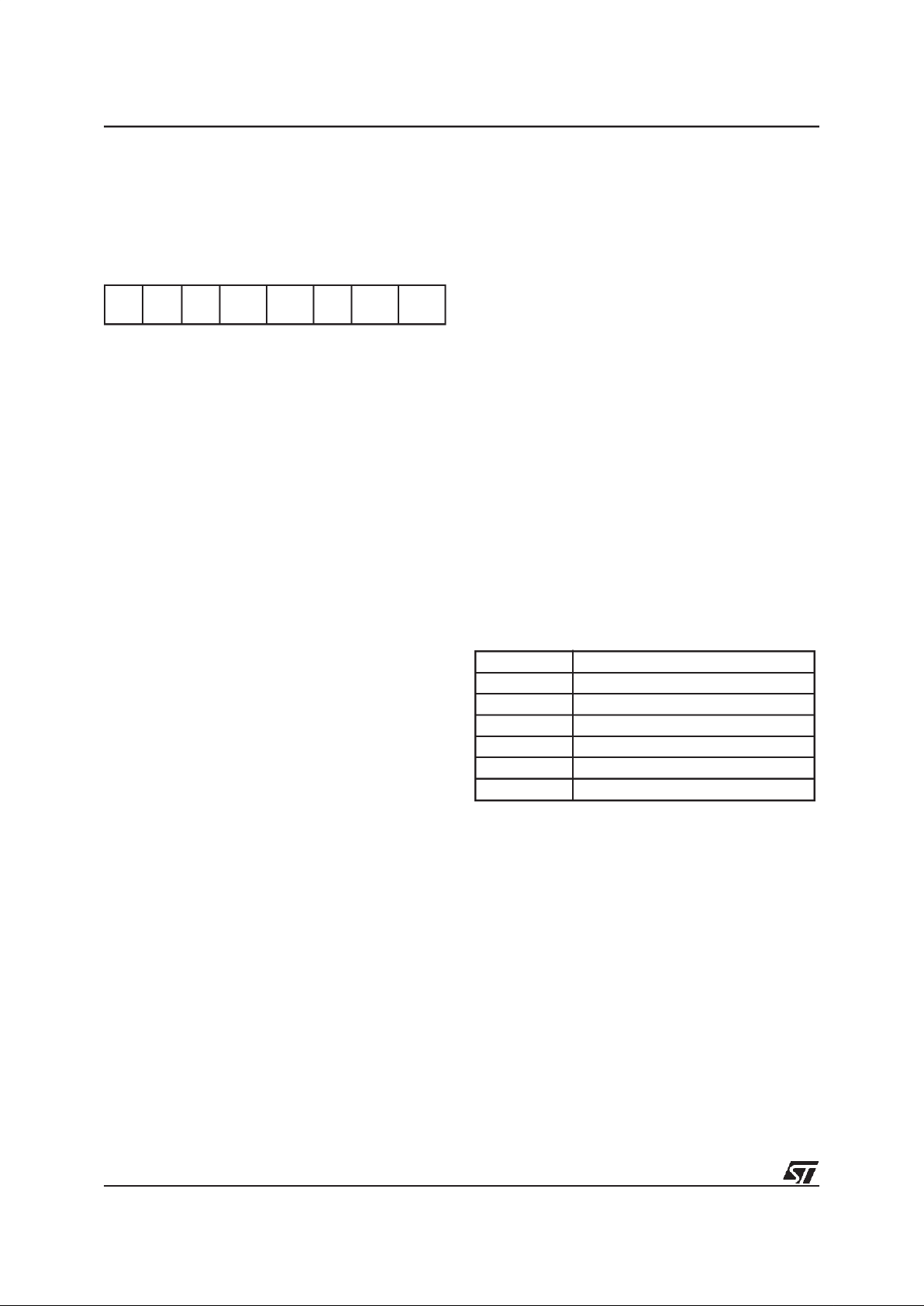

1.3.6 Data RAM/EEPROM Bank Register

(DRBR)

Address: CBh — Write only

Bit 7-5 = These bits are not used

Bit 4 - DRBR4. This bit, when set, selects RAM

Page 2.

Bit 3 - DRBR3. This bit, when set, selects RAM

Page 1.

Bit2. This bit is not used.

Bit 1 - DRBR1. This bit, when set, selects

EEPROM Page 1.

Bit 0 - DRBR0. This bit, when set, selects

EEPROM Page 0.

The selection of the bank is made by program-

ming the Data RAM Bank Switch register (DRBR

register) located at address CBh of the Data

Space according to Table 1. No more than one

bank should be set at a time.

The DRBR register can be addressed like a RAM

Data Space at the address CBh; nevertheless it is

a write only register that cannot be accessed with

single-bit operations. This register is used to select the desired 64-byte RAM/EEPROM bank of

the Data Space. The number of banks has to be

loaded in the DRBR register and the instruction

has to point to the selected location as if it was in

bank 0 (from 00h address to 3Fh address).

This register is not cleared during the MCU initialization, therefore it must be written before the first

access to the Data Space bank region. Refer to

the Data Space description for additional information. The DRBR register is not modified when an

interrupt or a subroutine occurs.

Notes :

Care is required when handling the DRBR register

as it is write only. For this reason, it is not allowed

to change the DRBR contents while executing interrupt service routine, as the service routine cannot save and then restore its previous content. If it

is impossible to avoid the writing of this register in

interrupt service routine, an image of this register

must be saved in a RAM location, and each time

the program writes to DRBR it must write also to

the image register. The image register must be

written first, so if an interrupt occurs between the

two instructions the DRBR is not affected.

In DRBR Register, only 1 bit must be set. Otherwise two or more pages are enabled in parallel,

producing errors.

Table 5. Data RAM Bank Register Set-up

70

- - - DRBR4 DRBR3 - DRBR1 DRBR0

DRBR ST62T35B

00 None

01 EEPROM Page 0

02 EEPROM Page 1

08 RAM Page 1

10h RAM Page 2

other Reserved

11

13/82

ST62T35B/E35B

MEMORY MAP (Cont’d)

1.3.7 EEPROM Description

EEPROM memory is located in 64-byte pages in

data space. This memory may be used bythe user

program for non-volatile data storage.

Data space from 00h to 3Fh is paged as described

in Table 6 . EEPROM locations are accessed directly by addressing these paged sections of data

space.

The EEPROM does not require dedicated instructions for reador writeaccess. Onceselected viathe

Data RAM Bank Register, the active EEPROM

page is controlled by the EEPROM Control Register (EECTL), which is described below.

BitE20FF oftheEECTL register must be reset prior

to any write or read access to the EEPROM. If no

bank has been selected, or if E2OFF isset, any access is meaningless.

Programming must be enabled by setting the

E2ENA bit of the EECTL register.

The E2BUSY bitof the EECTL register is set when

the EEPROM is performing a programming cycle.

Any access to the EEPROM when E2BUSY is set

is meaningless.

Provided E2OFF and E2BUSY are reset, an EEPROM location is read just like any other data location, also in terms of access time.

Writing to the EEPROM may be carried out in two

modes: Byte Mode (BMODE) and Parallel Mode

(PMODE). In BMODE, one byte is accessed at a

time, while in PMODE up to 8 bytes in the same

row are programmed simultaneously (with consequent speed and power consumption advantages,

the latter being particularly important in battery

powered circuits).

General Notes:

Data should be written directly to theintended ad-

dress in EEPROM space. There is no buffer memory between data RAM and the EEPROM space.

When the EEPROM is busy (E2BUSY = “1”)

EECTL cannot be accessed in write mode, it is

only possible to read the status of E2BUSY. This

implies that as long as the EEPROM is busy, it is

not possible to change the statusof the EEPROM

Control Register. EECTL bits 4 and 5 arereserved

and must never be set.

Care is required when dealing with the EECTL register, as some bits are write only. For this reason,

the EECTL contents must not be altered while executing an interrupt service routine.

If it is impossible to avoid writing to this register

within an interrupt service routine, an image of the

register must be saved in a RAM location, and

each time the program writes to EECTL it must

also write to the image register. The image register must be written to first so that, if an interrupt occurs between the two instructions, the EECTL will

not be affected.

Table 6. Row Arrangement for Parallel Writing of EEPROM Locations

Dataspace

addresses.

Banks 0 and 1.

Byte 01234567

ROW7 38h-3Fh

ROW6 30h-37h

ROW5 28h-2Fh

ROW4 20h-27h

ROW3 18h-1Fh

ROW2 10h-17h

ROW1 08h-0Fh

ROW0 00h-07h

Up to 8 bytes in each row may be programmed simultaneously in Parallel Write mode.

The number of available 64-byte banks (1 or 2) is device dependent.

12

14/82

ST62T35B/E35B

MEMORY MAP (Cont’d)

Additional Notes on Parallel Mode:

If the user wishes to perform parallel programming, the first step should be to set the E2PAR2

bit. From this time on, the EEPROM will be addressed in write mode, the ROW address will be

latched and it will be possible to change it only at

the end of the programming cycle, or by resetting

E2PAR2 without programming the EEPROM. After the ROW address is latched,the MCU can only

“see” the selected EEPROM row and any attempt

to write or read other rows will produce errors.

The EEPROM should not be read while E2PAR2

is set.

As soon as the E2PAR2 bit is set, the 8 volatile

ROW latches are cleared. From this moment on,

the user can load data in all or in part of theROW.

Setting E2PAR1 will modify the EEPROM registers corresponding to the ROW latches accessed

after E2PAR2. For example, if the software sets

E2PAR2 and accesses the EEPROM by writing to

addresses 18h, 1Ah and 1Bh, and then sets

E2PAR1, these three registers will be modified simultaneously; the remaining bytes in the row will

be unaffected.

Note that E2PAR2 is internally reset at the end of

the programming cycle. This implies that the user

must set the E2PAR2 bit between two parallel programming cycles. Note that if the user tries to set

E2PAR1 while E2PAR2 is not set, there will be no

programming cycle and the E2PAR1 bit will be unaffected. Consequently, the E2PAR1 bit cannot be

set if E2ENA is low. The E2PAR1 bit can be set by

the user, only if the E2ENA and E2PAR2 bits are

also set.

EEPROM Control Register (EECTL)

Address: DFh — Read/Write

Reset status: 00h

Bit 7 = D7:

Unused.

Bit6 =E2OFF:

Stand-by Enable Bit.

WRITE ONLY.

Ifthisbitis set the EEPROMisdisabled (anyaccess

will be meaningless) and the powerconsumption of

the EEPROM is reduced to its lowest value.

Bit 5-4 = D5-D4:

Reserved.

MUST be kept re set.

Bit 3 =

E2PAR1

:

Parallel Start Bit.

WRITE ONLY.

OnceinParallel Mode,assoonastheusersoftware

sets the E2PAR1 bit, parallel writing of the 8 adjacent registers willstart.This bitis internally resetat

the end of the programming procedure. Note that

less than 8 bytes can be written if required, the undefined bytes being unaffected by the parallel programming cycle; this is explained in greater detail

in the Additional Notes on Parallel Mode overleaf.

Bit 2 = E2PAR2:

Parallel Mode En. Bit.

WRITE

ONLY. This bit must be set by the user program in

order to perform parallel programming. If E2PAR2

is set and the parallel start bit (E2PAR1) is reset,

up to 8 adjacent bytes can be written simultaneously. These 8 adjacent bytes are considered as a

row, whose address lines A7, A6, A5, A4, A3 are

fixed while A2, A1 and A0 are the changing bits,

as illustrated in Table 6. E2PAR2 is automatically

reset at the end of any parallel programming procedure. Itcan be reset by the user software before

starting the programming procedure, thus leaving

the EEPROM registers unchanged.

Bit 1 = E2BUSY:

EEPROM Busy Bit.

READ ONLY. This bit is automatically set by the EEPROM

control logic when the EEPROM is in programming mode. The user program should test it before any EEPROM read or write operation; any attempt to access the EEPROM while the busy bit is

set will be aborted and the writing procedure in

progress will be completed.

Bit 0 =

E2ENA

:

EEPROM Enable Bit.

WRITE ONLY. This bit enables programming of the EEPROM

cells. It must be set before any write to the EEPROM register. Any attempt to write to the EEPROM when E2ENA is low is meaningless and will

not trigger a write cycle.

70

D7 E2OFF D5 D4 E2PAR1 E2PAR2 E2BUSY E2ENA

13

15/82

ST62T35B/E35B

1.4 PROGRAMMING MODES

1.4.1 Option Byte

The Option Byte allows configuration capability to

the MCUs. Option byte’s content is automatically

read, and the selected options enabled, when the

chip reset is activated.

It can only be accessed during the programming

mode. This access is made either automatically

(copy from a master device) or by selecting the

OPTION BYTE PROGRAMMING mode of the

programmer.

The option byte is located in a non-user map. No

address has to be specified.

EPROM Code Option Byte

Bit 7. Reserved.

Bit 6 =

PORT PULL

. This bit must be set high to

have pull-up input state at reset on the I/O port.

When this bit is low, I/O ports are in input without

pull-up (high impedance) state at reset

Bit 5 =

EXTCNTL

. This bit selects the External

STOP Mode capability. When EXTCNTL is high,

pin NMI controls if the STOP mode can be accessed when the watchdog is active. When

EXTCNTL is low, the STOP instruction is processed as a WAIT as soon as the watchdog is active.

Bit 4 = PROTECT. This bit allows the protection of

the software contents against piracy. When the bit

PROTECT is set high, readout of the OTP contents is prevented by hardware. No programming

equipment is able to gain access to the user program. When this bit is low, the user program can

be read.

Bit 3 =

TIM PULL.

This bit must be set high to configure the TIMER pin with a pull up resistor. When

it is low, no pull up is provided.

Bit 2 =NMI PULL. This bit must be set high to configure the NMI pin with a pull up resistor when it is

low, no pull up is provided.

Bit 1 = WDACT. This bit controls the watchdog activation. When it is high, hardware activation is selected. The software activation is selected when

WDACT is low.

Bit 0 = OSGEN.This bit must be set high to enable

the oscillator Safe Guard. When this bit is low, the

OSG is disabled.

The Option byte is written during programming either by using the PC menu (PC driven Mode) or

automatically (stand-alone mode)

1.4.2 Program Memory

EPROM/OTP programming mode is set by a

+12.5V voltage applied to the TEST/VPPpin. The

programming flow of the ST62T35B is described

in the User Manual of the EPROM Programming

Board.

The MCUs can be programmed with the

ST62E3xB EPROM programming tools available

from SGS-THOMSON.

1.4.3 EEPROM Data Memory

EEPROM data pages are supplied in the virgin

state FFh. Partial or total programming of EEPROM data memory can be performed either

through the application software, or through an external programmer. Any SGS-THOMSON tool

used for the program memory (OTP/EPROM) can

also be used to program the EEPROM data memory.

1.4.4 EPROM Erasing

The EPROM of the windowed package of the

MCUs may be erased by exposure to Ultra Violet

light. The erasure characteristic of the MCUs is

such that erasure begins when the memory is exposed to light with a wave lengths shorter than approximately 4000Å. It should be noted that sunlights and some types of fluorescent lamps have

wavelengths in the range 3000-4000Å.

It is thus recommended that the window of the

MCUs packages be coveredby an opaque label to

prevent unintentional erasure problems when testing the application in such an environment.

The recommended erasure procedure of the

MCUs EPROM is the exposure to short wave ultraviolet light which have a wave-length 2537A.

The integrated dose (i.e. U.V. intensity x exposure

time) for erasure should be a minimum of 15Wsec/cm2. The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet

lamp with 12000µW/cm2power rating. The

ST62E35B should be placed within 2.5cm (1Inch)

of the lamp tubes during erasure.

70

-

PORT

PULL

EXTCNTLPROTECT

TIM

PULL

NMI

PULL

WDACT OSGEN

14

16/82

ST62T35B/E35B

2 CENTRAL PROCESSING UNIT

2.1 INTRODUCTION

The CPU Core of ST6 devices is independent of

the I/O or Memory configuration. Assuch, itmay be

thought of as an independent central processor

communicating with on-chip I/O, Memory and Peripherals via internal address, data, and control

buses. In-core communication is arranged as

shown in Figure 6; the controller being externally

linked to both the Reset and Oscillator circuits,

while the core is linked tothe dedicated on-chip peripherals via the serial data bus and indirectly, for

interrupt purposes, through the control registers.

2.2 CPU REGISTERS

TheST6FamilyCPU core featuressixregisters and

three pairs of flags available to the programmer.

These are described in the following paragraphs.

Accumulator (A). The accumulator is an 8-bit

general purpose register used in all arithmetic calculations, logical operations, and data manipulations. The accumulator can be addressed in Data

space as a RAM location at address FFh. Thus

the ST6 can manipulate the accumulator just like

any other register in Data space.

Indirect Registers (X, Y).These two indirect registers are used as pointers to memory locations in

Data space. They are used in the register-indirect

addressing mode. These registers can be addressed in the data space as RAM locations at addresses 80h (X) and 81h (Y). They can also be accessed with the direct, short direct, or bit direct addressing modes. Accordingly, the ST6 instruction

set can use the indirect registers as any other register of the data space.

Short Direct Registers (V, W).

These two registers are used to save a byte in short direct addressing mode. They can be addressed in Data

space as RAM locations at addresses 82h (V) and

83h (W). They can also be accessed using the direct and bit direct addressing modes. Thus, the

ST6 instruction set can use the short direct registers as any other register of the data space.

Program Counter (PC). The program counter is a

12-bit register which contains the address of the

next ROM location to be processed by the core.

This ROM location may be an opcode, an operand, or the address of an operand. The 12-bit

length allows the direct addressing of 4096 bytes

in Program space.

Figure 6ST6 Core Block Diagram

PROGRAM

RESET

OPCODE

FLAG

VALUES

2

CONTROLLER

FLAGS

ALU

A-DATA

B-DATA

ADDRESS/READ LINE

DATA SPACE

INTERRUPTS

DATA

RAM/EEPROM

DATA

ROM/EPROM

RESULTS TO DATA SPACE(WRITE LINE)

ROM/EPROM

DEDICATIONS

ACCUMULATOR

CONTROL

SIGNALS

OSCin

OSCout

ADDRESS

DECODER

256

12

Program Counter

and

6 LAYER STACK

0,01 TO 8MHz

VR01811

15

17/82

ST62T35B/E35B

CPU REGISTERS(Cont’d)

However, if the program space contains more

than 4096 bytes, the additional memory in program space can be addressed by using the Program Bank Switch register.

The PC value is incremented after reading the address of the current instruction. To execute relative jumps, the PC and the offset are shifted

through the ALU, where they are added; the result

is then shifted back into the PC. The program

counter can be changed in the following ways:

- JP (Jump) instructionPC=Jump address

- CALL instructionPC= Call address

- Relative Branch Instruction.PC= PC +/- offset

- Interrupt PC=Interrupt vector

- ResetPC= Reset vector

- RET & RETI instructionsPC= Pop (stack)

- Normal instructionPC= PC + 1

Flags (C, Z). The ST6 CPU includes three pairs of

flags (Carry and Zero), each pair being associated

with one of the three normal modes of operation:

Normal mode, Interrupt mode and Non Maskable

Interrupt mode. Each pair consists of a CARRY

flag and a ZERO flag. One pair (CN, ZN) is used

during Normal operation, another pair is used during Interrupt mode (CI, ZI), and a third pair is used

in the Non Maskable Interrupt mode (CNMI, ZNMI).

The ST6 CPU uses the pair of flags associated

with the current mode: as soon as an interrupt (or

a Non Maskable Interrupt) is generated, the ST6

CPU uses the Interrupt flags (resp. the NMI flags)

instead of the Normal flags. When the RETI instruction is executed, the previously used set of

flags is restored. It should be noted that each flag

set can only be addressed in its own context (Non

Maskable Interrupt, Normal Interrupt or Main routine). The flags are not cleared during context

switching and thus retain their status.

The Carry flag is set when a carry or a borrow occurs during arithmetic operations; otherwise it is

cleared. The Carry flag is also set to the value of

the bit tested in a bit test instruction; it also participates in the rotate left instruction.

The Zero flag is set if theresult of the last arithmetic or logical operation was equal to zero; otherwise it is cleared.

Switching between the three sets of flags is performed automatically when an NMI, an interrupt or

a RETI instructions occurs. As the NMI mode is

automatically selected after the reset of the MCU,

the ST6 core uses at first the NMI flags.

Stack. The ST6 CPU includes a true LIFO hardware stack which eliminates the need for a stack

pointer. The stack consists of six separate 12-bit

RAM locations that do not belong to the data

space RAM area. When a subroutine call(or interrupt request) occurs, the contents of each level

are shifted into the next higher level, while the

content of the PC is shifted into the first level (the

original contents of the sixth stack level are lost).

When a subroutine or interrupt return occurs (RET

or RETI instructions), the first level register is shifted back into the PC and the value of each level is

popped back into the previous level. Since the accumulator, in common with all other data space

registers, is not stored in this stack, management

of these registers should be performed within the

subroutine. The stack will remain in its “deepest”

position if more than 6 nested calls or interrupts

are executed, and consequently the last return address will be lost. It will also remain in its highest

position if the stack is empty and a RET or RETI is

executed. In this case the next instruction will be

executed.

Figure 7ST6 CPU Programming Mode

l

SHORT

DIRECT

ADDRESSING

MODE

VREGISTER

W REGISTER

PROGRAM COUNTER

SIX LEVELS

STACK REGISTER

CZNORMAL FLAGS

INTERRUPTFLAGS

NMI FLAGS

INDEX

REGISTER

VA000423

b7

b7

b7

b7

b7

b0

b0

b0

b0

b0

b0b11

ACCUMUL ATOR

YREG.POINTER

XREG.POINTER

CZ

CZ

16

18/82

ST62T35B/E35B

3 CLOCKS, RESET, INTERRUPTS AND POWER SAVING MODES

3.1 CLOCK SYSTEM

The MCU features a Main Oscillator which can be

driven by an external clock, or used in conjunction

with an AT-cut parallel resonant crystal or a suitable ceramic resonator. In addition, a Low Frequency Auxiliary Oscillator (LFAO) can be switched in

for security reasons, to reduce power consumption, or to offer the benefits of a back-up clock system.

The Oscillator Safeguard (OSG) option filters

spikes from the oscillator lines, provides access to

the LFAO to provide a backup oscillator in the

event of main oscillator failure and also automatically limits the internal clock frequency (f

INT

)asa

function of VDD, in order to guarantee correct operation. These functions are illustrated inFigure

9., Figure 10., Figure 11.and Figure 12..

Figure 8.illustrates various possible oscillator con-

figurations using an external crystalorceramicresonator, anexternalclockinputorthelowest costsolution usingonly theLFAO. CL1anCL2should have

a capacitance in the range 12 to 22 pF for an oscillator frequency in the 4-8 MHz range.

The internal MCU clock frequency (f

INT

) is divided

by 12 to drive the Timer and the Watchdog timer,

and by 13 to drive the CPU core, while the A/D

converter is driven by f

INT

divided either by 6 or by

12 as may be seen inFigure 11..

With an 8MHz oscillator frequency, the fastest

machine cycle is therefore 1.625µs.

A machine cycle is thesmallest unit of timeneeded

toexecute anyoperation (forinstance, to increment

the Program Counter). An instruction may require

two, four, or five machine cycles for execution.

3.1.1 Main Oscillator

The main oscillator can be turned off (when the

OSG ENABLED option is selected) by setting the

OSCOFF bit of the OSCR Control Register. The

Low Frequency Auxiliary Oscillator is automatically started.

Figure 8. Oscillator Configurations

INTEGRATED CLOCK

OSG ENABLED option

OSC

in

OSC

out

C

L1n

C

L2

ST6xxx

CRYSTAL/RESON ATORCLOCK

OSC

in

OSC

out

ST6xxx

EXTERNALCLOCK

NC

OSC

in

OSC

out

ST6xxx

NC

VA0016

VA0015A

17

19/82

ST62T35B/E35B

CLOCK SYSTEM (Cont’d)

Turning on the main oscillator is achieved by resetting the OSCOFF bit of the OSCR Register or

by resetting the MCU. Restarting the main oscillator implies a delay comprising the oscillator start

up delay period plus the duration of the software

instruction at f

LFAO

clock frequency.

3.1.2 Low Frequency Auxiliary Oscillator

(LFAO)

The Low Frequency Auxiliary Oscillator has three

main purposes. Firstly, it can be used to reduce

power consumption in non timing critical routines.

Secondly, it offers a fully integrated system clock,

without any external components. Lastly, it acts as

a safety oscillator in case of main oscillator failure.

This oscillator is available when the OSG ENABLED option is selected. In this case, it automatically starts one of its periods after the first missing

edge from the main oscillator, whatever the reason (main oscillator defective, no clock circuitry

provided, main oscillator switched off...).

User code, normal interrupts, WAIT and STOP instructions, are processed as normal, at the reduced f

LFAO

frequency. The A/D converter accuracy is decreased, since the internal frequency is

below 1MHz.

At power on, the Low Frequency Auxiliary Oscillator starts faster than the Main Oscillator. It therefore feeds the on-chip counter generating the

POR delay until the Main Oscillator runs.

The Low Frequency Auxiliary Oscillator is automatically switched off as soon as the main oscillator starts.

OSCR

Address: 0DBh — Read/Write

Bit 7-1= These bits are not used and must be kept

cleared after reset.

Bit 0 =

OSCOFF

.

Main oscillator turn-off.

When

low, this bit enables main oscillator to run. The

main oscillator is switched off when OSCOFF is

high.

3.1.3 Oscillator Safe Guard

The Oscillator Safe Guard (OSG) affords drastically increased operational integrity in ST62xx devices. The OSG circuit provides three basic functions: it filters spikes from the oscillator lines which

would result in over frequency to the ST62 CPU; it

gives access to the Low Frequency Auxiliary Oscillator (LFAO), used to ensure minimum processing in case of main oscillator failure, to offer reduced power consumption or to provide a fixed

frequency low cost oscillator; finally, it automatically limits the internal clock frequency as a function of supply voltage, in order to ensure correct

operation even if the power supply should drop.

The OSG is enabled or disabled by choosing the

relevant OSG option. It may be viewed as a filter

whose cross-over frequency is device dependent.

Spikes on the oscillator lines result in an effectively increased internal clock frequency. In the absence of an OSG circuit, this may lead to an over

frequency for a given power supply voltage. The

OSG filters out such spikes (as illustrated inFigure 9.). In all cases, when the OSG is active, the

maximum internal clock frequency, f

INT

, is limited

to f

OSG

, which is supply voltage dependent. This

relationship is illustrated inFigure 12..

When the OSG is enabled, the Low Frequency

Auxiliary Oscillator may be accessed. This oscillator starts operating after the first missing edge of

the main oscillator (seeFigure 10.).

Over-frequency, at a given power supply level, is

seen by the OSG as spikes; it therefore filters out

some cycles in order that the internal clock frequency of the device is kept within the range the

particular device can stand (depending on VDD),

and below f

OSG

: the maximum authorised fre-

quency with OSG enabled.

Note. The OSG should be used wherever possi-

ble as it provides maximum safety. Care must be

taken, however, as it can increase power consumption and reduce the maximum operating frequency to f

OSG

.

70

-------

OSC

OFF

18

20/82

ST62T35B/E35B

CLOCK SYSTEM (Cont’d)

Figure 9. OSG Filtering Principle

Figure 10. OSG Emergency Oscillator Principle

(1)

VR001932

(3)

(2)

(4)

(1)

(2)

(3)

(4)

Maximum Frequency for the device to work correctly

Actual Quartz Crystal Frequency at OSCin pin

Noise from OSCin

Resulting Internal Frequency

Main

VR001933

Internal

Emergency

Oscillator

Frequency

Oscillator

19

21/82

ST62T35B/E35B

CLOCK SYSTEM (Cont’d)

Figure 11. Clock Circuit Block Diagram

Figure 12. Maximum Operating Frequency (f

MAX

) versus Supply Voltage (VDD)

Notes:

1. In this area, operation is guaranteed at the

quartz crystal frequency.

2. When the OSG is disabled, operation in this

area is guaranteed at the crystal frequency. When

the OSG is enabled, operation in this area is guaranteed at a frequency of at least f

OSG Min.

3. When the OSG is disabled, operation in this

area isguaranteed at the quartz crystal frequency.

When the OSG is enabled, access to this area is

prevented. The internal frequency is kept a f

OSG.

4. When the OSG is disabled, operation in this

area is not guaranteed

When the OSG is enabled, access to this area is

prevented. The internal frequency is kept at f

OSG.

MAIN

OSCILLATOR

OSG

LFAO

M

U

X

Core

:13

:12

:1

TIMER 1

Watchdog

POR

f

INT

Main Oscillator off

ADC

ARTIMER 16

:6

M

U

X

1

2.5

3.5 4 4.5 5 5.5 6

8

7

6

5

4

3

2

Maximum FREQUENCY (MHz)

SUPPLY VOLTAGE (V

DD

)

FUNCTIONALITY IS NOT

3

4

3

2

1

f

OSG

f

OSG

Min

GUARANTEED

IN THIS AREA

VR01807

20

22/82

ST62T35B/E35B

3.2 RESETS

The MCU can be reset in three ways:

– by the external Reset input being pulled low;

– by Power-on Reset;

– by the digital Watchdog peripheral timing out.

3.2.1 RESET Input

The RESET pin may be connected to a device of

the application board in order to reset the MCU if

required. The RESET pin may be pulled low in

RUN, WAIT or STOP mode. This input can be

used to reset the MCU internal state and ensure a

correct start-up procedure. The pin is active low

and features a Schmitt trigger input. The internal

Reset signal is generated by adding a delay to the

external signal. Therefore even short pulses on

the RESET pin are acceptable, provided VDDhas

completed its rising phase and that the oscillator is

running correctly (normal RUN or WAIT modes).

The MCU is kept in the Reset state as long as the

RESET pin is held low.

If RESET activation occurs in the RUN or WAIT

modes, processing of the user program is stopped

(RUN mode only), the Inputs and Outputsare configured as inputs with pull-up resistors and the

main Oscillator is restarted. When the level on the

RESET pin then goes high, the initialization sequence is executed following expiry of the internal

delay period.

If RESET pin activation occurs in the STOP mode,

the oscillator starts up and all Inputs and Outputs

are configured as inputs with pull-up resistors.

When the level of theRESET pin then goes high,

the initialization sequence is executed following

expiry of the internal delay period.

3.2.2 Power-on Reset

The function of the POR circuit consists in waking

up the MCU at an appropriate stage during the

power-on sequence. At the beginning of this sequence, the MCU is configured in the Reset state:

all I/O ports are configured as inputs with pull-up

resistors and no instruction isexecuted. When the

power supply voltage rises to a sufficient level, the

oscillator starts to operate, whereupon an internal

delay is initiated, in order to allow the oscillator to

fully stabilize before executing the first instruction.

The initialization sequence is executed immediately following the internal delay.

The internal delayisgenerated by anon-chip counter. The internal reset lineis released 2048 internal

clock cycles after release of the external reset.

Notes:

To ensure correct start-up, the user should take

care that the reset signal is not released before

the VDDlevel is sufficient to allow MCU operation

at the chosen frequency (see Recommended Operating Conditions).

A proper reset signal for a slow rising VDDsupply

can generally be provided by an external RC network connected to theRESET pin.

Figure 13. Reset and Interrupt Processing

INT LATCHCLEARED

NMI MASK SET

RESET

( IF PRESENT )

SELECT

NMI MODE FLAGS

IS RESET STILL

PRESENT?

YES

PUT FFEH

ON ADDRESS BUS

FROMRESET LOCATIONS

FFE/FFF

NO

FETCH INSTRUCTION

LOAD PC

VA000427

21

23/82

ST62T35B/E35B

RESETS (Cont’d)

3.2.3 Watchdog Reset

The MCU provides a Watchdog timer function in

order to ensure graceful recovery from software

upsets. If the Watchdog register is not refreshed

before an end-of-count condition is reached, the

internal reset will be activated. This, amongst other things, resets the watchdog counter.

The MCU restarts just as though the Reset had

been generated by the RESET pin, including the

built-in stabilisation delay period.

3.2.4 Application Notes

No external resistor is required between VDDand

the Reset pin, thanks to the built-in pull-up device.

The POR circuit operates dynamically, in that it

triggers MCU initialization on detecting the rising

edge of VDD. The typical threshold is in the region

of 2 volts, but the actual value of the detected

threshold depends on the way in which VDDrises.

The POR circuit is

NOT

designed to supervise

static, or slowly rising or falling VDD.

3.2.5 MCU Initialization Sequence

When a reset occurs the stack is reset, the PC is

loaded with the address of the Reset Vector (located in program ROM starting at address

0FFEh). A jump to the beginning of the user program must be coded at this address. Following a

Reset, the Interrupt flag is automatically set, so

that the CPU is in Non Maskable Interrupt mode;

this prevents the initialisation routine from being

interrupted. The initialisation routine should therefore be terminated by a RETI instruction, in order

to revert to normal mode and enable interrupts. If

no pending interrupt is present at the end of the initialisation routine, the MCU will continue by

processing the instruction immediately following

the RETI instruction. If, however, a pending interrupt is present, it will be serviced.

Figure 14. Reset and Interrupt Processing

Figure 15. Reset Block Diagram

RESET

RESET

VECTOR

JP

JP:2 BYTES/4 CYCLES

RETI

RETI: 1 BYTE/2 CYCLES

INITIALIZATION

ROUTINE

VA00181

V

DD

RESET

300kΩ

2.8kΩ

POWER

WATCHDOG RESET

CK

COUNTER

RESET

ST6

INTERNAL

RESET

f

OSC

RESET

ON RESET

VA0200B

22

24/82

ST62T35B/E35B

RESETS (Cont’d)

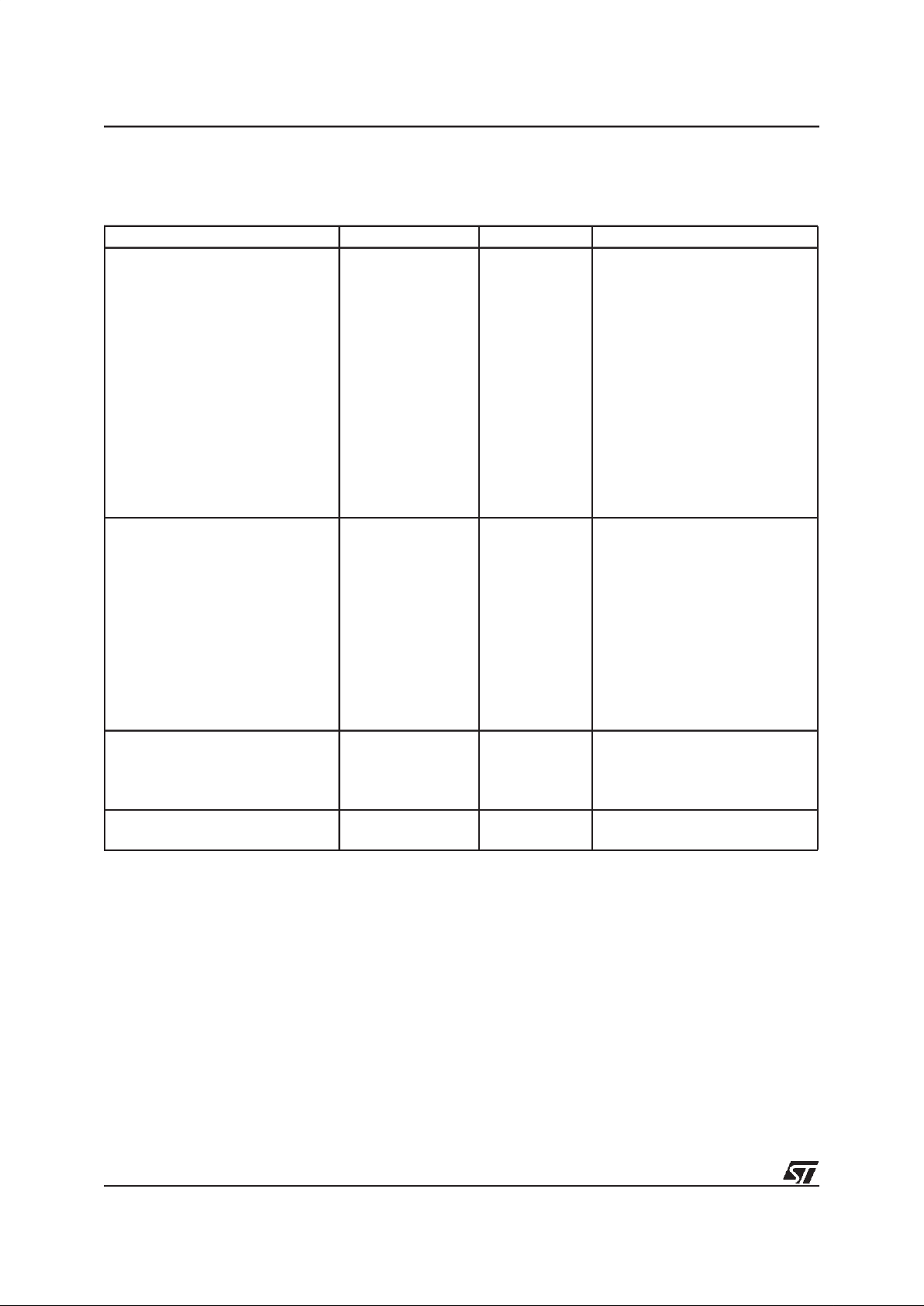

Table 7. Register Reset Status

Register Address(es) Status Comment

Oscillator Control Register

EEPROM Control Register

Port Data Registers

Port Direction Register

Port Option Register

Interrupt Option Register

TIMER Status/Control

AR TIMER Status/Control 1 Register

AR TIMER Status/Control 2 Register

AR TIMER Status/Control 3 Register

AR TIMER Status/Control 4 Register

SPI Registers

0DBh

0DFh

0C0h to 0C2h

0C4h to 0C6h

0CCh to 0CEh

0C8h

0D4h

0E8h

0E1h

0E2h

OE3h

0DCh to 0DDh

00h

Main oscillator on

EEPROM enabled

I/O are Input with or without pull-up

depending on PORTPULL option

Interrupt disabled

TIMER disabled

AR TIMER stopped

SPI disabled

X, Y,V, W, Register

Accumulator

Data RAM

Data RAM Page REgister

Data ROM Window Register

EEPROM

A/D Result Register

AR TIMER Capture Register

AR TIMER Reload/Capture Register

ARTIMER Mask Registers

ARTIMER Compare Registers

080H TO083H

0FFh

084h to 0BFh

0CBh

0C9h

00h to 03Fh

0D0h

0DBh

0D9h

OE0h-OEFh

OEDh-OEEh

Undefined As written if programmed

TIMER Counter Register

TIMER Prescaler Register

Watchdog Counter Register

A/D Control Register

0D3h

0D2h

0D8h

0D1h

FFh

7Fh

FEh

40h

Max count loaded

A/D in Standby

UART Control

UART Data Register

OD7h

OD6h

UART disabled

23

25/82

ST62T35B/E35B

3.3 INTERRUPTS

The CPU can manage four Maskable Interrupt

sources, in addition to a Non Maskable Interrupt

source (top priority interrupt). Each source is associated with a specific Interrupt Vector which

contains a Jump instruction to the associated interrupt service routine. These vectors are located

in Program space (seeTable 8 ).

When an interrupt source generates an interrupt

request, and interrupt processing is enabled, the

PC register is loaded with the address of the interrupt vector (i.e. of the Jump instruction), which

then causes a Jump to the relevant interrupt service routine, thus servicing the interrupt.

Interrupt sources are linked to events either on external pins, or on chip peripherals. Several events

can be ORed on the same interrupt source, and

relevant flags are available to determine which

event triggered the interrupt.

The Non Maskable Interrupt request has the highest priority and can interrupt any interrupt routine

at any time; the other four interrupts cannot interrupt each other. If more than one interrupt request

is pending, these are processed by the processor

core according to their priority level: source #1 has

the higher priority while source #4 the lower. The

priority of each interrupt source is fixed.

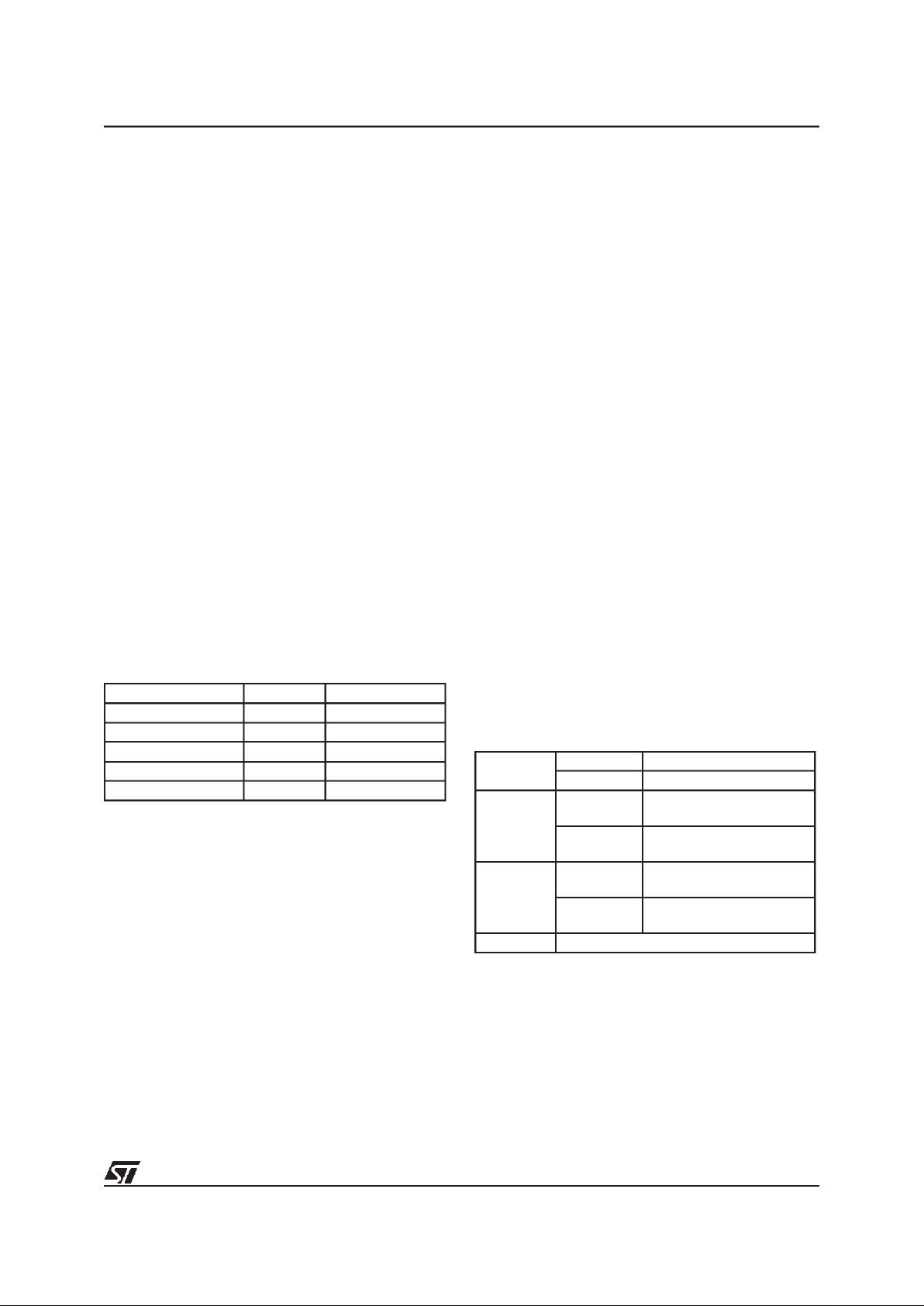

Table 8. Interrupt Vector Map

3.3.1 Interrupt request

All interrupt sources but the Non Maskable Interrupt source can be disabled by setting accordingly

the GEN bit of the Interrupt Option Register (IOR).

This GENbit also defines if an interrupt source, including the Non Maskable Interrupt source, can

restart the MCU from STOP/WAIT modes.

Interrupt request from the Non Maskable Interrupt

source #0 is latched by a flip flop which is auto-

matically reset by the core at the beginning of the

non-maskable interrupt service routine.

Interrupt request from source #1 can be configured either as edge or level sensitive by setting

accordingly the LES bit of the Interrupt Option

Register (IOR).

Interrupt request from source #2 are always edge

sensitive. The edge polarity can be configured by

setting accordingly the ESB bit of the Interrupt Option Register (IOR).

Interrupt request from sources #3 & #4 are level

sensitive.

In edge sensitive mode, a latch is set when a edge

occurs on the interrupt source line and is cleared

when the associated interrupt routine is started.

So, the occurrence of an interrupt can be stored,

until completion of the running interrupt routine before being processed. If several interrupt requests

occurs before completion of the running interrupt

routine, only the first request is stored.

Storage of interrupt requests is not available in

level sensitive mode. To be taken into account,

the low level must be present on the interrupt pin

when the MCU samples the line after instruction

execution.

At the end of every instruction, the MCU tests the

interrupt lines: if there is an interrupt request the

next instruction is not executed and the appropriate interrupt service routine is executed instead.

Table 9. Interrupt Option Register Description

Interrupt Source Priority Vector Address

Interrupt source #0 1 (FFCh-FFDh)

Interrupt source #1 2 (FF6h-FF7h)

Interrupt source #2 3 (FF4h-FF5h)

Interrupt source #3 4 (FF2h-FF3h)

Interrupt source #4 5 (FF0h-FF1h)

GEN

SET Enable all interrupts

CLEARED Disable all interrupts

ESB

SET

Rising edge mode on interrupt source #2

CLEARED

Falling edge mode on interrupt source #2

LES

SET

Level-sensitive mode on interrupt source #1

CLEARED

Falling edge mode on interrupt source #1

OTHERS NOT USED

24

Loading...

Loading...