SGS Thomson Microelectronics ST16SF48 Datasheet

®

2

2

2

2

■

8 BIT ARCHITECTURE CPU

■

16 KBytes of USER ROM, SECTOR

COMBINATIVE

■

1.5 KByte of SYSTEM R OM

■

384 Bytes of RAM

■

8176 Bytes of EEPROM, SECTOR

COMBINATIVE

– Highly reliable CMOS EEPROM technology

– 10 year data retention

– 300,000 Erase/Write cycle endurance

– Protected One Time Programmable block (32

or 64 bytes)

– 1 to 32 bytes block e ither Erase or Write in

single cycle programming

■

EXTENDED VOLTAGE OPERATION

Range: 2.7V to 5.5V

–V

CC

■

SERIAL ACCESS, ISO 7816-3 COMPATIBLE

■

POWER SAVING STANDBY MODE

■

UP TO 5 MHz I N TERNAL OPERATI N G

FREQUENCY

■

VERY HIGH SECURITY FEATURES

INCLUDING EEPROM FLASH ERASE

■

CONTACT ASSIGNMENT COMPATIBLE ISO

7816-2

■

ESD PROTECTION GREATER THAN 5000V

■

MEETS GSM 11.11 AND 11.12

SPECIFICATIONS

■

2 OPE RATING CONF IGURATIONS

–ISSUER

– USER

ST16SF48

Smar tcard MCU

With 8176 Bytes EEPROM

DATA BRIEFING

Micromodule (D4)

Wafer

BD.SF48/9809V5

This is Brief Data from STMicroelectronics. Details are subject to change without notice. For complete data, please contact

your nearest Sales Office or SmartCard Products Divison, Rousset, France. Fax: (+33) 4 42 25 87 29

1/2

ST16SF48

DESCRIPTION

The ST16SF48, a member of the standard ST16

device family, is a serial access microcontroller

especially designed for high volume and cost

competitive Smartcard applications where

firmware security algorithm must be implemented.

The ST16SF48 is based on 8 bit CPU core and includes on chip memories: 384 Bytes of RAM, 16

KBytes of USER ROM, 1.5 KByte of SYSTEM

ROM, and 8176 Bytes of EEPROM.

Both ROM and EEPROM memorie s can be configured into two sectors. Access rules from any

memory section or sector to any other are set-up

by the User’s defined Memory Access Control Matrix (M ACM) .

Reliabilit y data relat ed to the ST 16SF48 prod uct

manufactured using STMicroelectronics advanced CMOS EEPRO M te chnology confirm data

retention up to 10 years and endurance up to

300,000 Erase/Write cycles.

As all other ST16 family members, the ST16SF48

is fully compatible with the ISO standards for

Smartcard applications.

Software development (ROM code, options) can

be completed by the ST16-19HDS development

system.

The ST16SF48 can be delivered either in unsawn

or sawn wafers, 180 or 275 micron thickness as

well as in micromodule package.

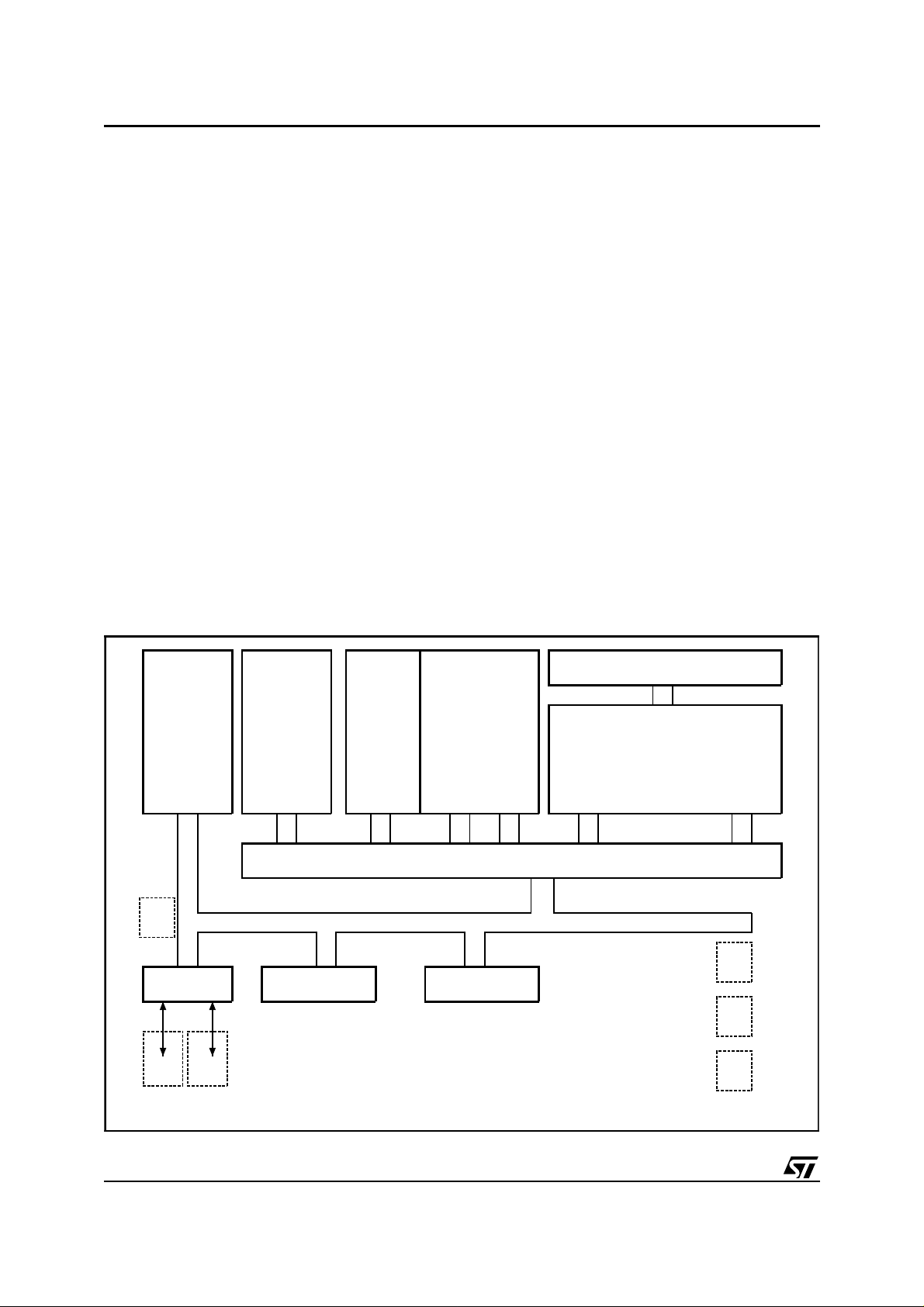

Figure 1. Bloc k D ia gram

8 BIT

CPU

CLK

SERIAL I/0's

INTERFACE

I/O1

I/O2

BYTES

RAM

384

NUMBER

GENERATOR

SYSTEM

ROM

1.5 KBtyt e

SECT.

S

V GENERATION

ROM

1615 KBytes

SECTORS

COMBIN.

SECT. ASECT.

B

MEMORY ACCESS CONTROL MATRIX

INTERNAL BUS

SECURITY

LOGIC

SECTOR

PP

EEPROM

8176 Bytes

SECTORS COMBINATIVE

A

SECTOR

B

RST

V

CC

GND

2/2

SCP 102b/DS

Loading...

Loading...