SGS Thomson Microelectronics M74HCT75 Datasheet

.HIGH SPEED

tPD= 15 ns(TYP.) AT VCC=5V

.LOWPOWER DISSIPATION

ICC=2 µA (MAX.) AT TA=25°C

.COMPATIBLE WITHTTL OUTPUTS

VIH= 2 V (MIN.) VIL= 0.8 V (MAX.)

.OUTPUT DRIVE CAPABILITY 10 LSTTL LOADS

.SYMMETRICALOUTPUT IMPEDANCE

IOH =IOL= 4 mA (MIN.)

.PIN AND FUNCTION COMPATIBLE WITH

54/74LS75

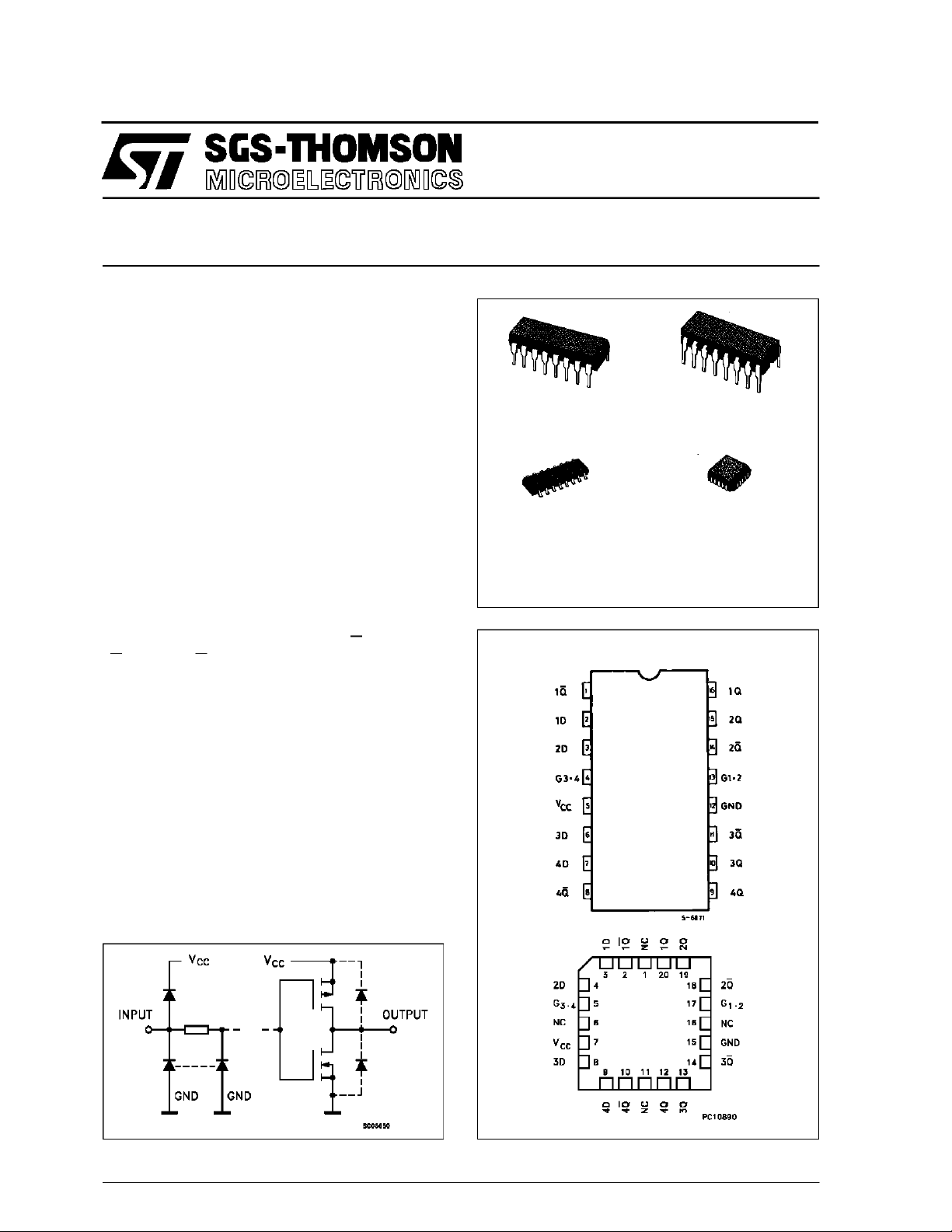

4 BIT D TYPE LATCH

B1R

(PlasticPackage)

M54HCT75

M74HCT75

F1R

(CeramicPackage)

DESCRIPTION

TheM54/74HCT7 5isahighspeedCMOS4-BITD-TYP E

LATCH fabricatedin silicongate C2MOStechnology. It

has the same high speed performa nce of LSTTL combined withtrueCMOS lowpower consumption. It contains

two groups of 2-bi t latches control led by an enable input

(G1 • 2orG3•4). These two latch groups can be used

indifferentcir cuits.Each latch has Qand Q outputs (1Q 4Qand1Q - 4Q).The dataapplied to thedata input is

transfere d to theQ and Q outputswhen theenable input

is taken high and the outputs will follow the data input as

long as the enab le input is kept high. When the enabl e

input is taken low,the information data applied to the data

input isretained at the outputs. Allinputs areequipped with

protection circuits against static discharge and transi ent

excessvoltage .Thisintegr atedcircu ithasinp utandoutput

characteris ticsthat arefullycompatiblewith54/74LSTTL

logic families. M54/74HCT devices are designed to directlyinterfac eHSC2MOSsystemswithTTLandNMOS

componen ts. They are also plug in replaceme n ts for

LSTTLdevices givinga reductionof powercons umptio n.

INPUT AND OUTPUT EQUIVALENT CIRCUIT

M1R

(MicroPackage)

ORDER CODES :

M54HC T75F1R M74H CT75M1R

M74HC T75B1R M74HCT75C1R

PIN CONNECTIONS(top view)

C1R

(Chip Carrier)

January 1993

NC =

No Internal

Connection

1/9

M54/M74HCT75

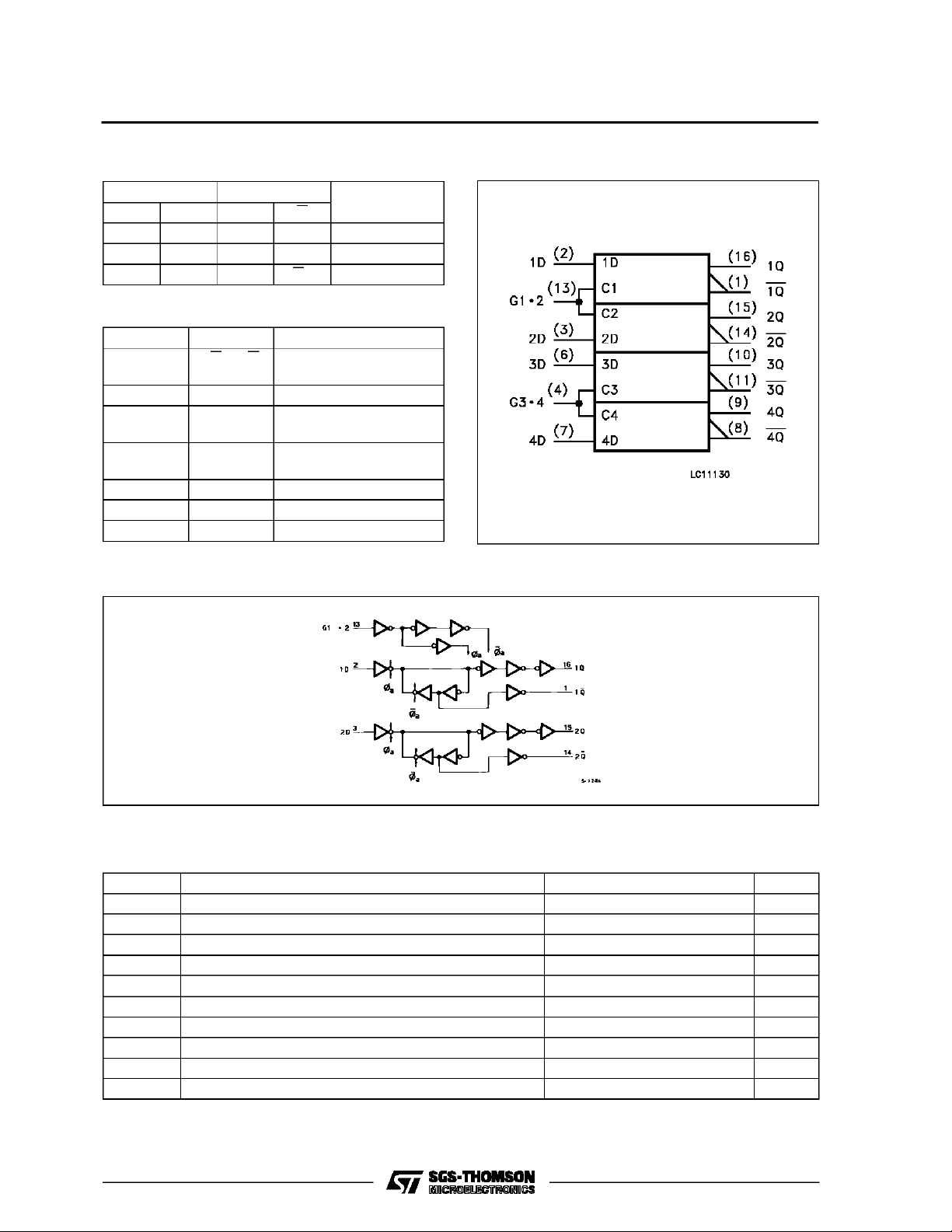

TRUTH TABLE

INPUTS OUTPUTS

DGQQ

LHLH

HHHL

X L Qn Qn LATCH

FUNCTION

PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

1, 4, 11, 8 1Q to 4Q Complementary Latch

Outputs

2, 3, 6, 7 1D to 4D Data Inputs

4G3•4 Latch Enable Input,

latches 3 and 4

13 G1 • 2 Latch Enable Input,

latches 1 and 2

15, 15, 10, 9 1Q to 4Q Latch Outputs

12 GND Ground (0V)

5V

CC

Positive Supply Voltage

SCHEM ATIC C I R CUI T

IEC LOGIC SYMBOL

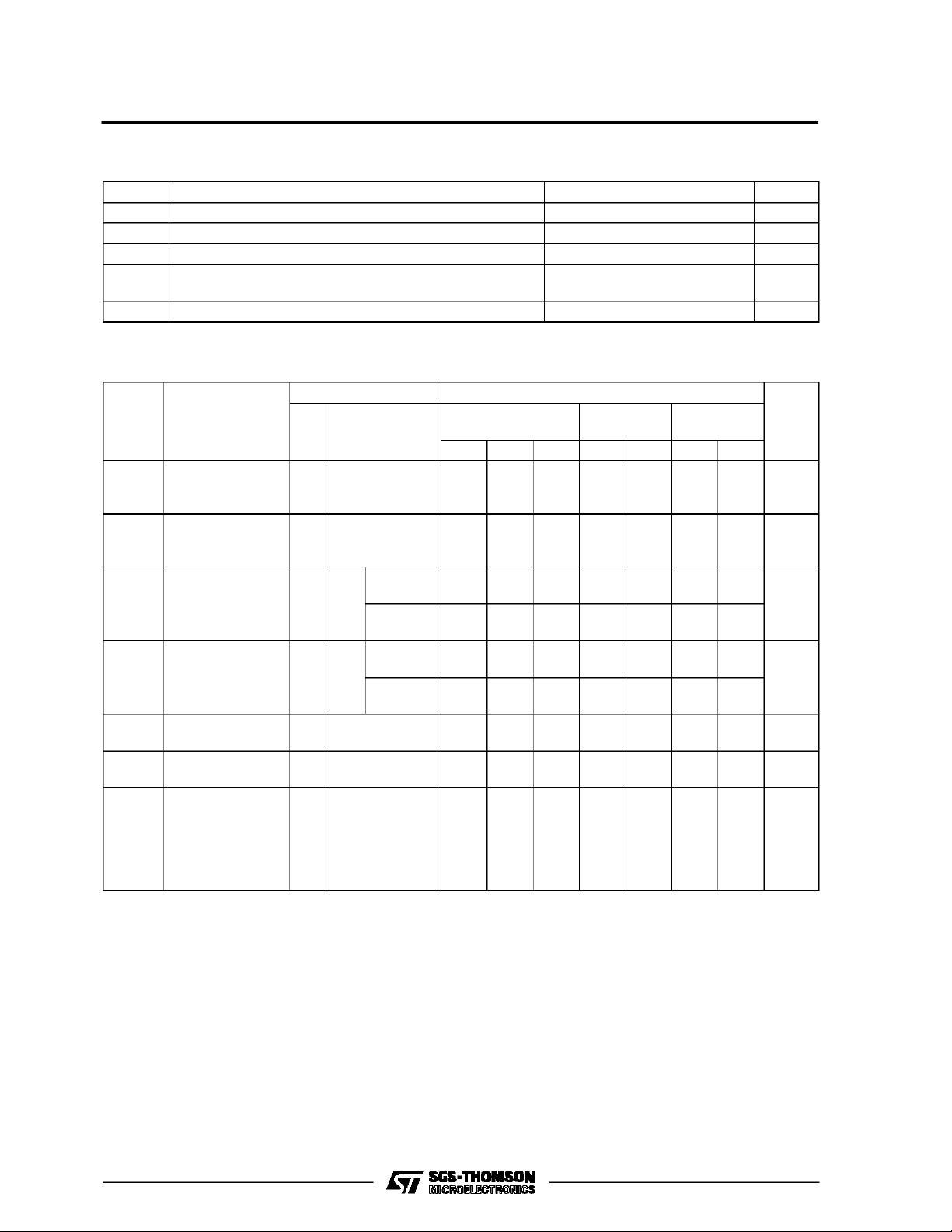

ABSOLU TE MAXIMU M RAT INGS

Symbol Parameter Value Unit

V

CC

V

V

O

I

IK

I

OK

I

O

or I

I

CC

P

D

T

stg

T

L

AbsoluteMaximumRatingsarethosevaluesbeyondwhichdamage tothedevicemayoccur. Functionaloperationunder theseconditionisnotimplied.

(*)500 mW: ≅ 65oC derateto300 mWby 10mW/oC: 65oCto85oC

2/9

Supply Voltage -0.5 to +7 V

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

DC Input Diode Current ± 20 mA

DC Output Diode Current ± 20 mA

DC Output Source Sink Current Per Output Pin ± 25 mA

DC VCCor Ground Current ± 50 mA

GND

Power Dissipation 500 (*) mW

Storage Temperature -65 to +150

Lead Temperature (10 sec) 300

o

C

o

C

M54/M74HCT75

RECO MM ENDED OPERATI N G C ONDI TIONS

Symbol Parameter Value Unit

V

V

V

T

t

r,tf

DC SPECIF ICATIO NS

Symbol Parameter

V

V

V

OH

V

OL

I

I

CC

∆I

Supply Voltage 4.5 to 5.5 V

CC

Input Voltage 0 to V

I

Output Voltage 0 to V

O

Operating Temperature: M54HC Series

op

M74HC Series

CC

CC

-55 to +125

-40 to +85

Input Rise and Fall Time (VCC= 4.5 to 5.5V) 0 to 500 ns

Test Conditions Value

T

High Level Input

IH

Voltage

V

(V)

4.5

=25oC

CC

A

54HC and 74HC

Min. Typ. Max. Min. Max. Min. Max.

2.0 2.0 2.0 V

to

-40 to 85oC

74HC

-55 to 125oC

5.5

Low Level Input

IL

Voltage

4.5

to

0.8 0.8 0.8 V

5.5

High Level

Output Voltage

Low Level Output

Voltage

Input Leakage

I

Current

Quiescent Supply

VI=

IO=-20 µA 4.4 4.5 4.4 4.4

V

IH

4.5

or

I

=-4.0 mA 4.18 4.31 4.13 4.10

O

V

IL

VI=

IO=20µA 0.0 0.1 0.1 0.1

V

IH

4.5

or

I

= 4.0 mA 0.17 0.26 0.33 0.4

O

V

IL

VI=VCCor GND ±0.1 ±1 ±1 µA

5.5

5.5 VI=VCCor GND 2 20 40 µA

Current

Additional worst

CC

case supply

current

5.5 Per Input pin

V

= 0.5V or

I

VI= 2.4V

2.0 2.9 3.0 mA

Other Inputs at

VCCor GND

IO=0

54HC

V

V

o

C

o

C

Unit

V

V

3/9

Loading...

Loading...