SGS Thomson Microelectronics M74HCT7259 Datasheet

8BIT ADDRESSABLE LATCH/DECODER/RELAIS

DRIVER (OPEN DRAIN,INVERTING OUTPUT)

■ LOW POW ERDISSIPATION

I

=4 µA (MAX.)AT TA=25°C

CC

■ COMPATIBLEWITHTTLOUTPUTS

=2V(MIN)VIL=0.8V(MAX)AT5V

V

IH

■ OUTPUTDRIVECAPABILITY

90LSTTLLOADS

■ HIGHCURRENTOPENDRAINOUTPUTUP

TO80 mA

The M74HCT7259 is a high speed CMOS 8 BIT

ADDRESSABLELATCH/DECODER fabricated in

silicon gate C2MOS technology. It has the same

high speed performanceof LSTTLcombined with

trueCMOS low powerconsumption.

The M74HCT7259 has single data input (D) 8

LATCH inverted OUTPUTS (Q0-Q7), 3 address

inputs (A, B and C), common enable input

(ENABLE) and a common CLEAR input. To

operatethis device as an addressablelatch, data

is held on the D input, and the address of the

latch into which the data is to be entered is held

on the A,B and C inputs.

When ENABLE is taken low the data flows

through to the address output. The data is stored

on the positive-going edge of the ENABLE pulse.

All unadressed latches will remain unaffected.

With ENABLE in the high state the device is

deselected and all latches remain in their

previous state, unaffected by changes on the

M74HCT7259

PRELIMINARY DATA

SOPDIP

ORDER CODES

PACK AG E TUBE T & R

DIP M74HCT7259B1R

SOP M74HCT7259M1R M74HCT7259M1RTR

data or address inputs. To eliminate the

possibility of entering erroneous data into the

latches, the ENABLE should be held high

(inactive) while the address lines are changing. If

ENABLE is held high and CLEAR is taken low all

eight latches are cleared to the HIGH (OFF)

state. If ENABLE is low all latches except the

addressed latch will be cleared. The address

latch will instead be the complement of the D

input,effectively implementing a 3 to 8 line

decoder. Internal clamp diodes protect the open

drain outputs against over voltages due to

inductiveloads.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

PIN CONNECTIONAND IEC LOGICSYMBOLS

February 2000

1/11

M74HCT7259

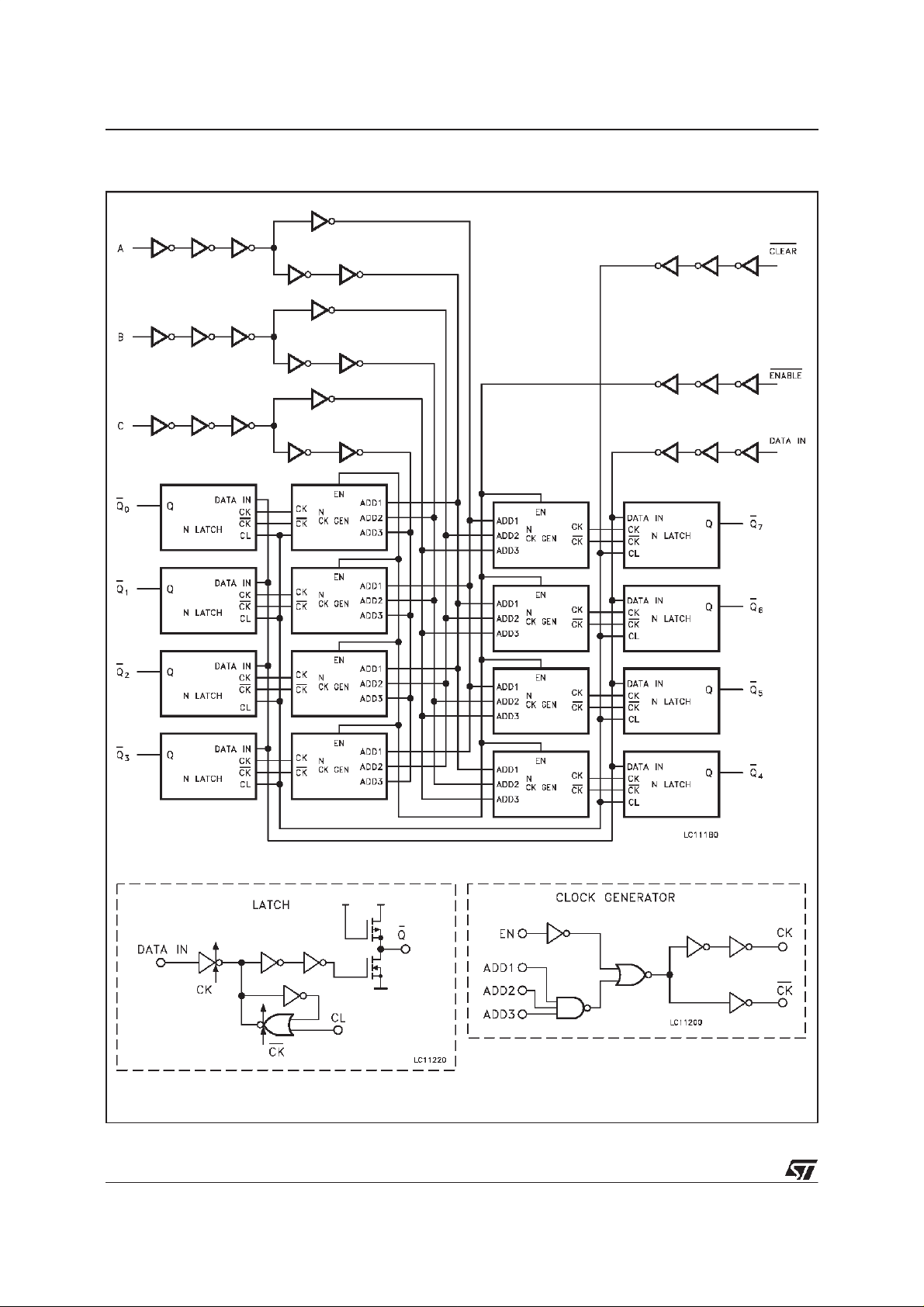

LOGICDIAGRAM

2/11

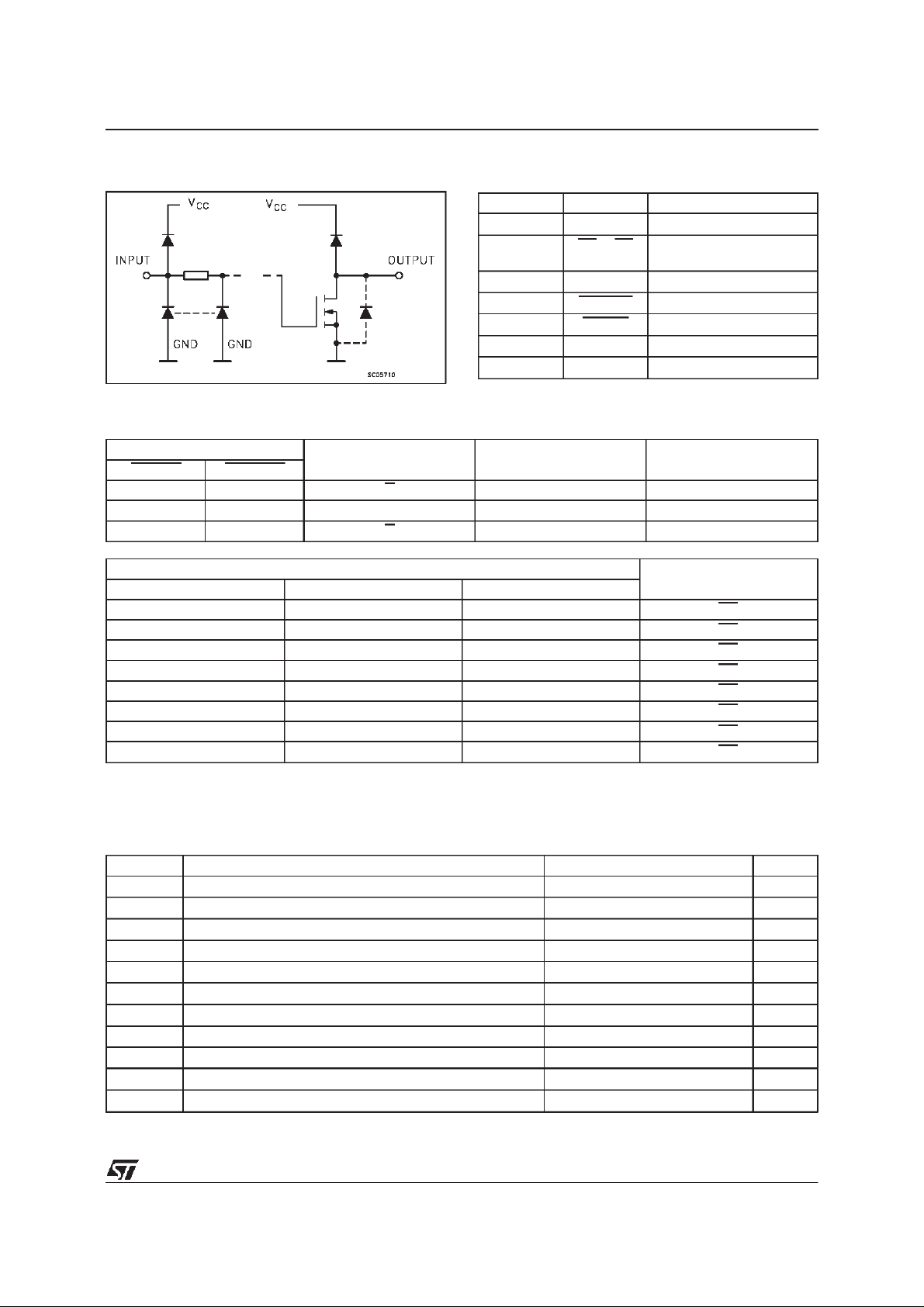

INPUT EQUIVALENTCIRCUIT PIN DESCRIPTION

PI N No SYMB OL NAME AND FUNCT IO N

1, 2, 3 A, B, C Latch Select

4, 5, 6, 7,9,

Q0 to Q7 latch Outputs

10, 11, 12

13 DATA IN Data Inputs

14 ENABLE Latch Enable Input

15 CLEAR Conditional Reset Input

8 GND Ground (0V)

16 V

TRUTH TABLE

CC

M74HCT7259

Positive Supply Voltage

INPUTS OUTPUTS OF

CLE AR ENABL E

ADDRESSED LA TCH

EAC H O THER O U T PUT FUNCTIO N

H L D QI0 ADDRESSABLE LATCH

H H Qi0 Qi0 MEMORY

L L D H 8-LINE DEMULTIPLEXER

SELE CT I NPUT S LAT CH ADDRESSED

CBA

LLLQ0

LLHQ1

LHLQ2

LHHQ3

HLLQ4

HLHQ5

HHLQ6

HHHQ7

D:The level atthedatainput

Qi0:The levelbeforetheindicate dsteady stateinpu tcond ition swereestablished ,(i = 0,1,....,7).

ABSOLUTE MAXIMUMRATINGS

Symb o l Para met er Val u e Uni t

V

V

V

I

I

OK

I

I

GND

I

CC

P

T

T

AbsoluteMaximumRatingsarethose values beyond whichdamageto thedevicemayoccur. Functionaloperation underthese condition isnotimplied.

(*)500mW:≅65

Supply Voltage -0.5 to +7.0 V

CC

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

O

DC Input Diode Current ± 20 mA

IK

DC Output Diode Current

DC Output Current Per Pin 100 mA

O

20 mA

±

Ground Current - 800 mA

DC VCCCurrent 50 mA

Power Dissipation 500 (*) mW

D

Storage Temperature -65 to +150

stg

Lead Temperature (10 sec) 300

L

o

Cderateto300mWby10mW/oC:65oCto85oC

o

C

o

C

3/11

M74HCT7259

RECOMMENDEDOPERATINGCONDITIONS

Symb o l Para met er Value Un it

V

V

V

T

dt/dv Input Rise and Fall Time 0 to 500 ns

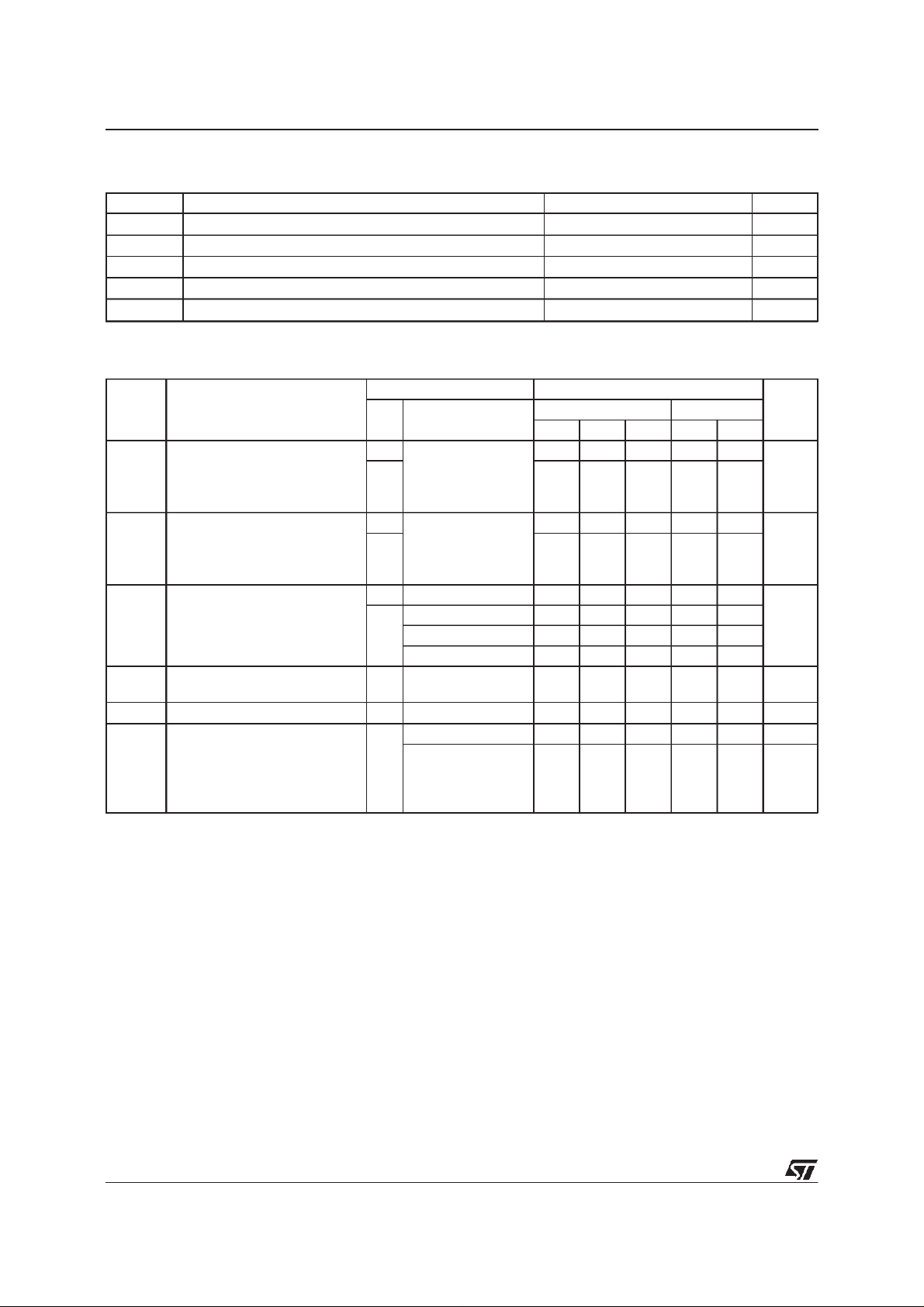

DC SPECIFICATIONS

Symbol Parameter Test Conditi ons Value Unit

V

IH

V

IL

V

OL

I

OZ

I

IN

I

CC

(*)VoltageRangeis3.3V±5%

Supply Voltage 3.3 to 5.5 V

CC

Input Voltage 0 to V

I

Output Voltage 0 to V

O

Operating Temperature -40 to +85

op

V

(V)

High Level Input Voltage 3.3

4.5

CC

(*)

T

A

Min. Typ. Max. Min. Max.

2.0 2.0

2.0 2.0

=25oC -40 to 85oC

CC

CC

to

5.5

4.5

(*)

0.5 0.5

0.8 0.8

Low Level Input Voltage 3.3

to

5.5

Low Level Output Voltage 3.3

Output Leackage Current

Input Leakage Current 5.5 VI=VCCorGND

Quiescent Supply Current

(*)

IO= 70 mA 0.4 0.5 0.6

=20µA 0.0 0.1 0.1

I

4.5

5.5

O

= 36 mA 0.17 0.26 0.33

I

O

= 80 mA 0.32 0.40 0.50

I

O

VI=VIHorV

V

OUT=VCC

IL

or GND

±5 ±50 µA

0.1

±

VI=VCCorGND 4 40

Each Input in Turn:

5.5

= 0.5 V or2.4 V

V

IN

All Other Inputs:

V

orGND

CC

3.0 3.9 mA

V

V

o

C

1

±

µ

µ

V

V

V

A

A

4/11

Loading...

Loading...