SGS Thomson Microelectronics M74HCT541, M74HCT540 Datasheet

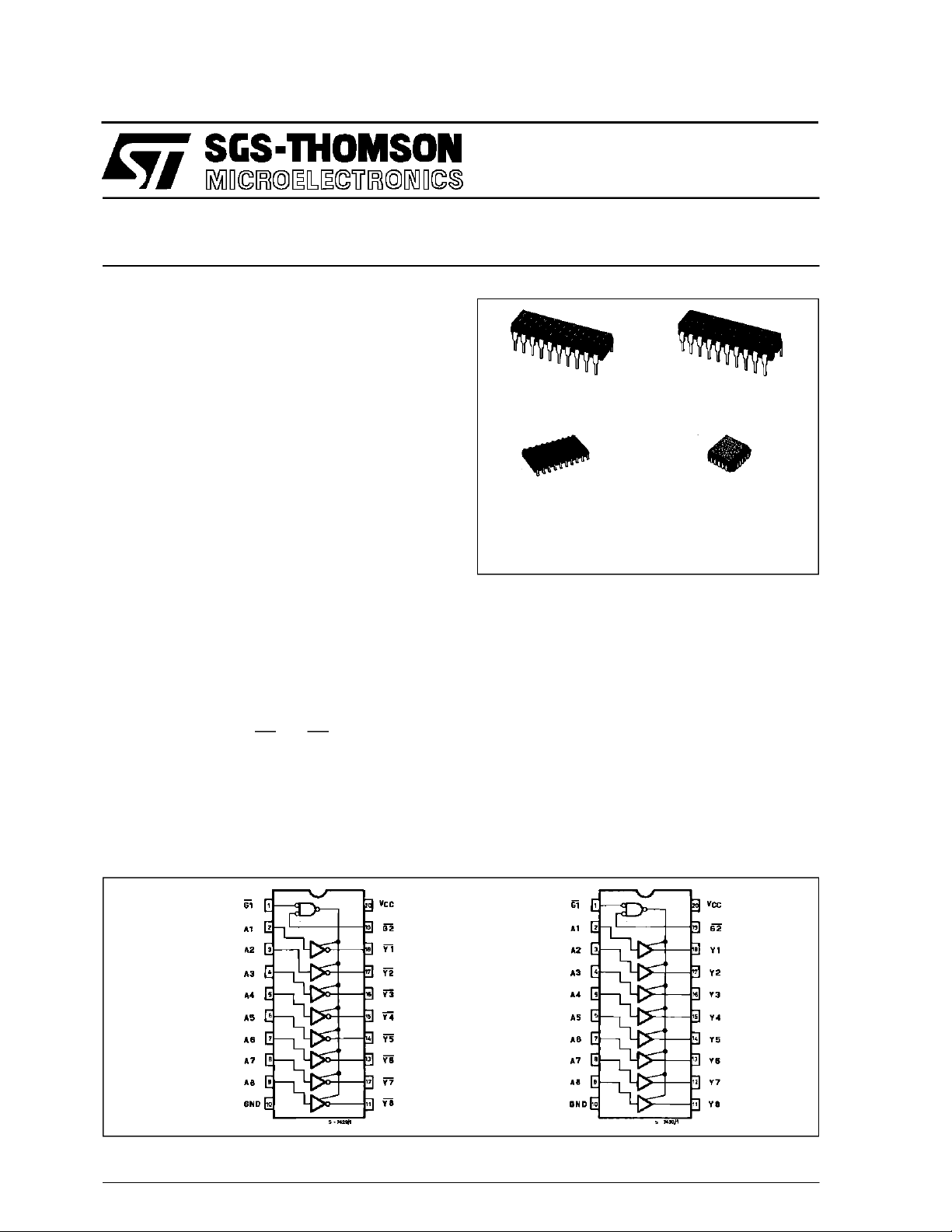

OCTAL BUS BU FFER WITH3 STATEOUTPUTS

HCT540: INVERTED - HCT541 NON INVERTED

.HIGH SPEED

tPD= 10 ns(TYP.) at VCC=5V

.LOWPOWER DISSIPATION

ICC=4µA (MAX.) at TA=25oC

.COMPATIBLE WITH TTL OUTPUTS

VIH= 2V (MIN.) VIL= 0.8V (MAX.)

.OUTPUTDRIVE CAPABILITY

15 LSTTL LOADS

.SYMMETRICALOUTPUT IMPEDANCE

|IOH|=IOL=6 mA (MIN)

.BALANCEDPROPAGATIONDELAYS

t

PLH=tPHL

.PIN AND FUNCTION COMPATIBLE

WITH 54/74LS540/541

DESCRIPTION

M54HCT540/541

M74HCT540/541

B1R

(PlasticPackage)

M1R

(MicroPackage)

ORDER CODE S :

M54HC TXXXF1R M74HC TXXXM1R

M74HC TXXXB1R M74HCT XXXC1R

F1R

(CeramicPackage)

C1R

(Chip Carrier)

The M54/74HCT540 and HCT541are high speed

CMOS OCTAL BUS BUFFERS (3-STATE)

fabricated in silicongate C2MOStechnology. They

have the same high speed performance of LSTTL

combined withtrue CMOS lowpower consumption.

The HCT540isaninverting bufferand HCT541 is a

non inverting buffer.

The 3 STATE control gate operates as a two input

AND suchthatifeither G1 andG2 are high,all eight

outputs are in thehigh impedance state. In order to

enhance PC board layout, the HCT540 and

HCT541 offers a pinout having inputs and outputs

on opposite sides of the package. All inputs are

equipped with protection circuits against static

PIN CONNECTION (top view)

discharge and transient excess voltage.

This integrated circuit has input and output

characteristics that are fully compatible with 54/74

LSTTL logic families. M54/74HCT devices are

designed to directly interface HSC2MOS systems

with TTL and NMOS components. They are also

plug in replacements for LSTTL devices giving a

reduction of power consumption.

IT IS PROHIBITEDTO APPLY A SIGNALTO BUS

TERMINAL WHEN IT IS IN OUTPUT MODE.

WHEN A BUS TERMINAL IS FLOATING (HIGH

IMPEDANCE STATE) IT IS REQUESTED TO FIX

THE INPUT LEVEL BY MEANS OF EXTERNAL

PULL DOWN OR PULL UP RESISTOR.

HCT541HCT540

October 1993

1/12

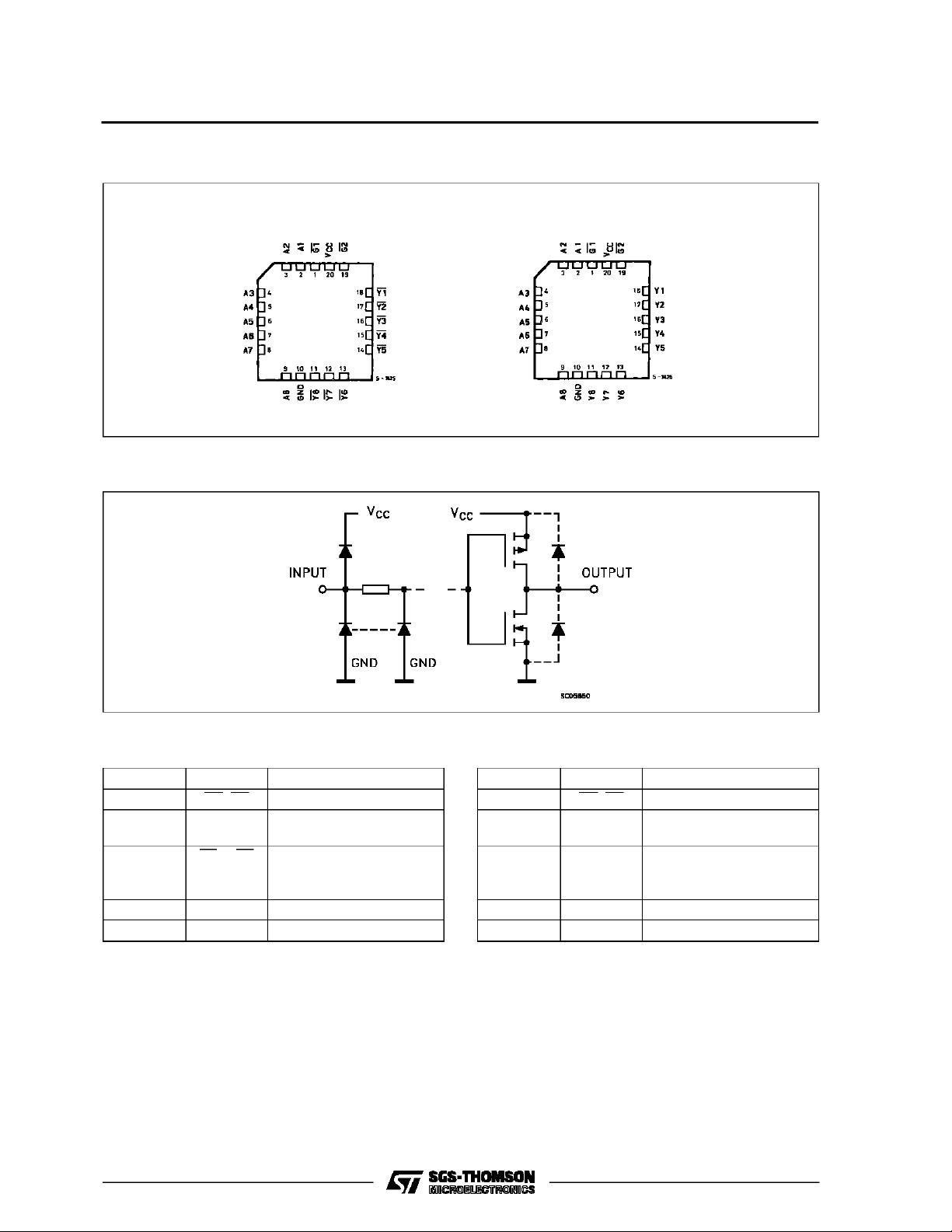

M54/M74HCT540/541

CHIP CARRIER

INPUT AND OUTPUT EQUIVALENT CIRCUIT

HCT541HCT540

PIN DESCRIPTIO N ( HCT 540)

PIN No SYMBOL NAME AND FUNCTION

1, 19 G1, G2 Output Enable Inputs

2, 3, 4, 5,

6, 7, 8, 9

18, 17, 16,

15, 14, 13,

11, 12

10 GND Ground (0V)

20 V

2/12

A1 to A8 Data Inputs

Y1 to Y8 Bus Outputs

CC

Positive Supply Voltage

PIN DESCRIPTION (HCT 541)

PIN No SYMBOL NAME AND FUNCTION

1, 19 G1, G2 Output Enable Inputs

2, 3, 4, 5,

6, 7, 8, 9

18, 17, 16,

15, 14, 13,

11, 12

10 GND Ground (0V)

20 V

A1 to A8 Data Inputs

Y1 to Y8 Bus Outputs

CC

Positive Supply Voltage

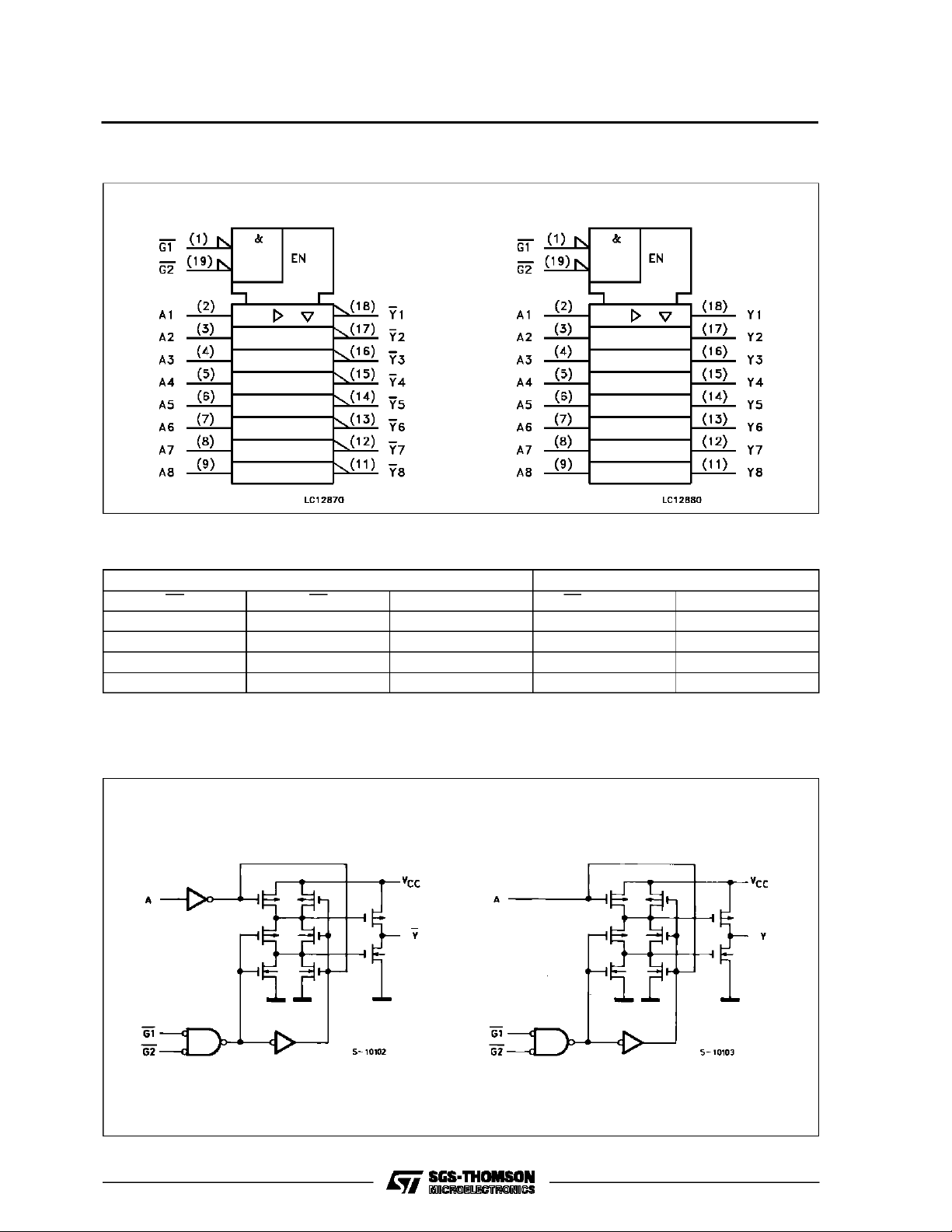

IEC LOGIC SYMBOLS

TRUTH TABLE

M54/M74HCT540/541

HCT541HCT540

INPUT OUTPUT

G1 G2 An Yn (HCT540) Yn (HCT541)

HXXZZ

XHXZZ

LLHLH

X: ”H” or ”L”

Z: Highimpedance

LLLHL

CIRCUIT SCHEMATIC (Per Circuit)

HCT540 HCT541

3/12

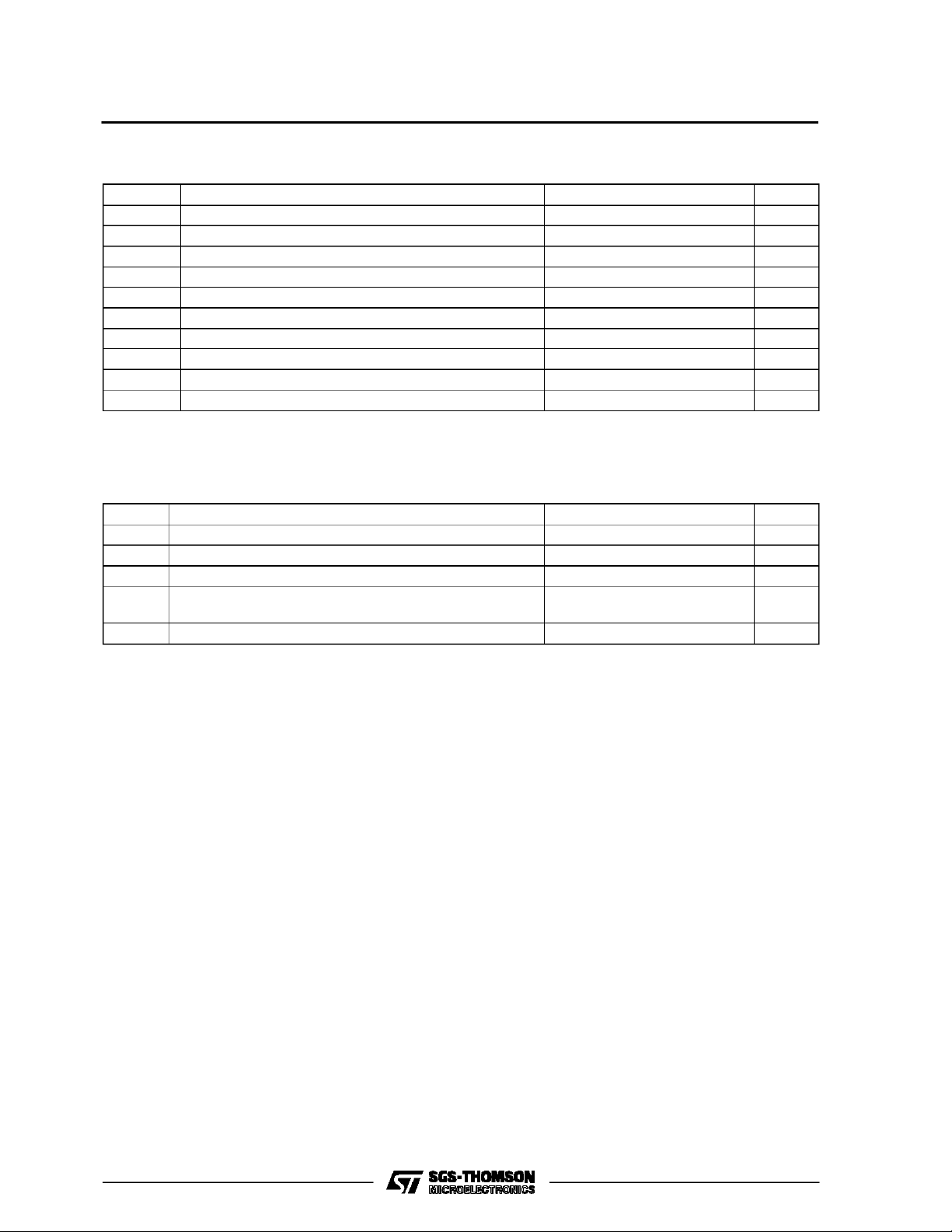

M54/M74HCT540/541

ABSOLU TE MAXI MUM R AT ING S

Symbol Parameter Value Unit

V

CC

V

V

O

I

IK

I

OK

I

O

I

or I

CC

P

D

T

stg

T

AbsoluteMaximum Ratings arethosevalues beyondwhichdamagetothedevicemayoccur.Functionaloperationundertheseconditionsisnot implied.

(*)500 mW:≅ 65oC derate to300 mW by 10mW/oC: 65oCto85oC

RECO MM ENDED OPERATI N G CONDITIONS

Symbol Parameter Value Unit

V

CC

V

I

V

O

T

op

t

r,tf

Supply Voltage -0.5 to +7 V

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

DC Input Diode Current ± 20 mA

DC Output Diode Current ± 20 mA

DC Output Source Sink Current Per Output Pin ± 35 mA

DC VCCor Ground Current ± 70 mA

GND

Power Dissipation 500 (*) mW

Storage Temperature -65 to +150

Lead Temperature (10 sec) 300

L

Supply Voltage 4.5 to 5.5 V

Input Voltage 0 to V

Output Voltage 0 to V

Operating Temperature: M54HC Series

M74HC Series

CC

CC

-55 to +125

-40 to +85

Input Rise and Fall Time (VCC= 4.5 to 5.5V) 0 to 500 ns

o

C

o

C

V

V

o

C

o

C

4/12

Loading...

Loading...