SGS Thomson Microelectronics M74HCT163, M74HCT162, M74HCT161, M74HCT160 Datasheet

SYNCHRONOUS PRESETTABLE 4-BIT COUNTER

.HIGH SPEED

f

= 50 MHz (TYP.) AT VCC=5V

MAX

.LOWPOWER DISSIPATION

ICC=4µA(MAX.) AT 25 °C

.OUTPUT DRIVE CAPABILITY

10 LSTTLLOADS

.BALANCEDPROPAGATION DELAYS

t

PLH=tPHL

.SYMMETRICALOUTPUT IMPEDANCE

IOH=IOL= 4 mA (MIN.)

.COMPATIBLE WITHTTL OUTPUTS

VIH= 2V(MIN.); VIL= 0.8V (MAX.)

.PIN AND FUNCTION COMPATIBLE

WITH 54/74LS160 ∼ 163

DESCRIPTION

M54/74HCT160 Decade, Asynchronous Clear

M54/74HCT161 Binary, Asynchronous Clear

M54/74HCT162 Decade, Synchronous Clear

M54/74HCT163 Binary, Synchronous Clear

The M54/74HCT160, 161, 162 and 163 are high

speed CMOS SYNCHRONOUS PRESETTABLE

COUNTERS fabricated with silicon gate C2MOS

technology. They have the same high speed operationsimilarto equivalent LSTTL while maintaining

the CMOS low power dissipation.

The M54/74HCT160/162 areBCDDecadecounters and the M54/74HCT161/163 are 4 bit binary

counters. The CLOCK input is active on the rising

edge. Both LOAD and CLEAR inputs are active

Low.

Presetting of all four IC’s is synchronous on the rising edge of the CLOCK. The function on the

M54/74HCT162/163 is synchronous to CLOCK,

whilethe M54/74HCT160/161 countersarecleared

asynchronously. Two enable inputs (TE and PE)

andCARRYoutputare providedtoenableeasycascadingof counters, which facilitieseasy implementationof N-bitcounterswithout using externalgates.

This integrated circuithas input and outputcharacteristicsthat are fully compatible with 54/74 LSTTL

logic families. M54/74HCT devices are designed to

directly interface HSC2MOSsystems with TTL and

NMOS components. They are also plug in replacements for LSTTL devices giving a reduction of

power consumption. All inputs are equipped with

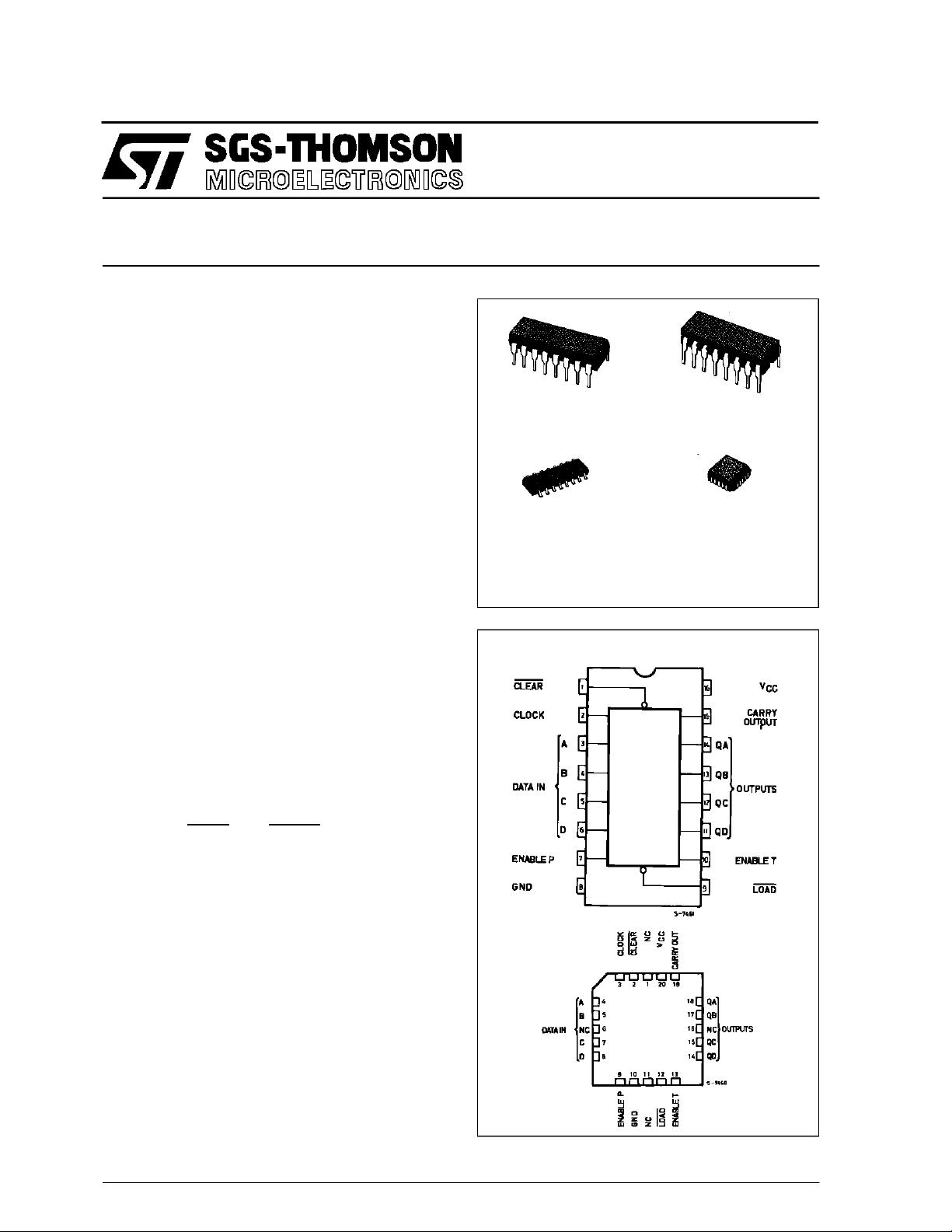

M54/74HCT160/161

M54/74HCT162/163

B1R

(PlasticPackage)

M1R

(MicroPackage)

ORDER CODES :

M54HC TXXXF1 R M74H CTXXXM1 R

M74HC TXXXB1R M74HCT XXXC1R

PIN CONNECTIONS (topview)

NC =

No InternalCon-

F1R

(CeramicPackage)

C1R

(Chip Carrier)

October 1993

1/16

M54/M74HCT160/161/162/163

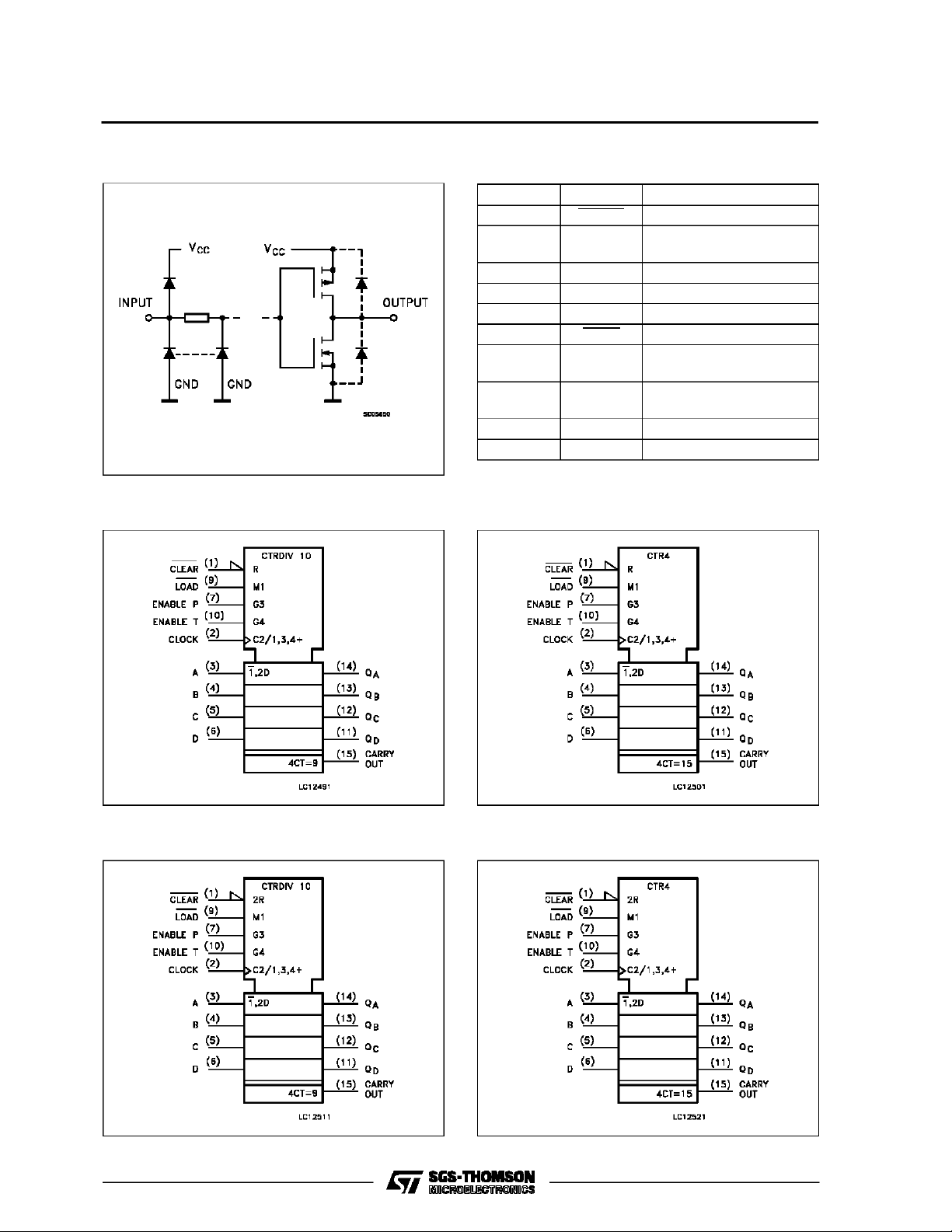

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

1 CLEAR Master Reset

2 CLOCK Clock Input (LOW to

HIGH, Edge-triggered)

3, 4, 5, 6 A, B, C, D Data Inputs

7 ENABLE P Count Enable Input

10 ENABLET Count Enable Carry Input

9 LOAD Parallel Enable Input

14, 13, 12,11QA to QD Flip Flop Outputs

15 CARRY

OUTPUT

8 GND Ground (0V)

16 V

CC

Terminal Count Output

Positive Supply Voltage

IEC LOGIC SYMBOL (HCT161)IEC LOGIC SYMBOL (HCT160)

IEC LOGIC SYMBOL (HCT162) IEC LOGIC SYMBOL (HCT163)

2/16

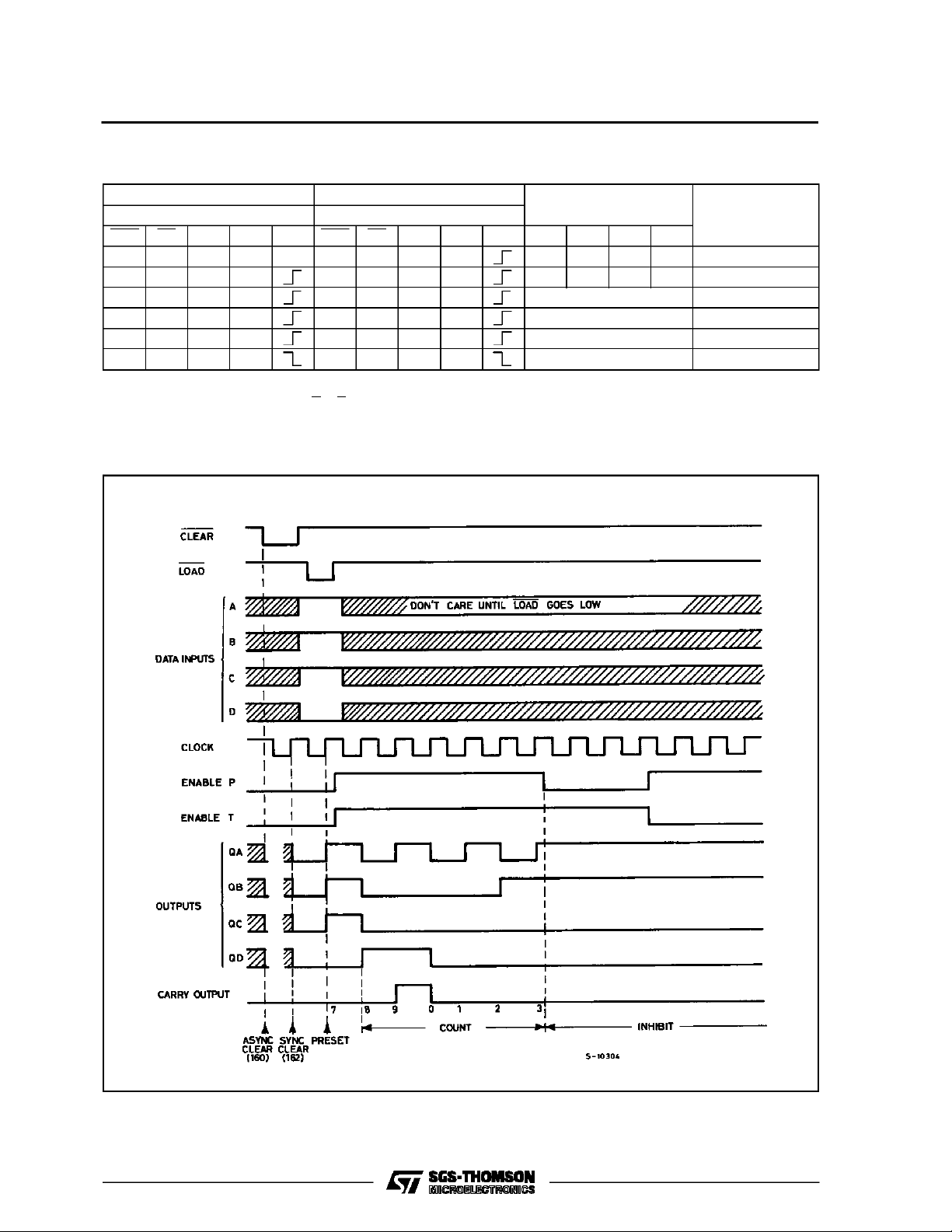

TRUTH TABLE

M54/M74HCT160/161/162/163

M54/74HCT160/161 M54/74HCT162/163

INPUTS INPUTS

CLR LD PE TE CK CLR LD PE TE CK QA QB QC QD

LXXXXLXXX LLLLRESET TO ”0”

H L X X H L X X A B C D PRESET DATA

H H X L H H X L NO CHANGE NO COUNT

H H L X H H L X NO CHANGE NO COUNT

HHHH HHHH COUNT UP COUNT

H X X X X X X X NO CHANGE NO COUNT

Note: X :Don’tCare

A, B, C, D : Logi level of data inputs

Carry : CARRY =TE • QA• QB• QC• QD............ (M54/74HCT160/162)

:CARRY = TE • QA• QB• QC• QD............ (M54/74HCT161/163)

OUTPUTS

FUNCTION

TIMING CHART (HCT160/162 : decade counter)

3/16

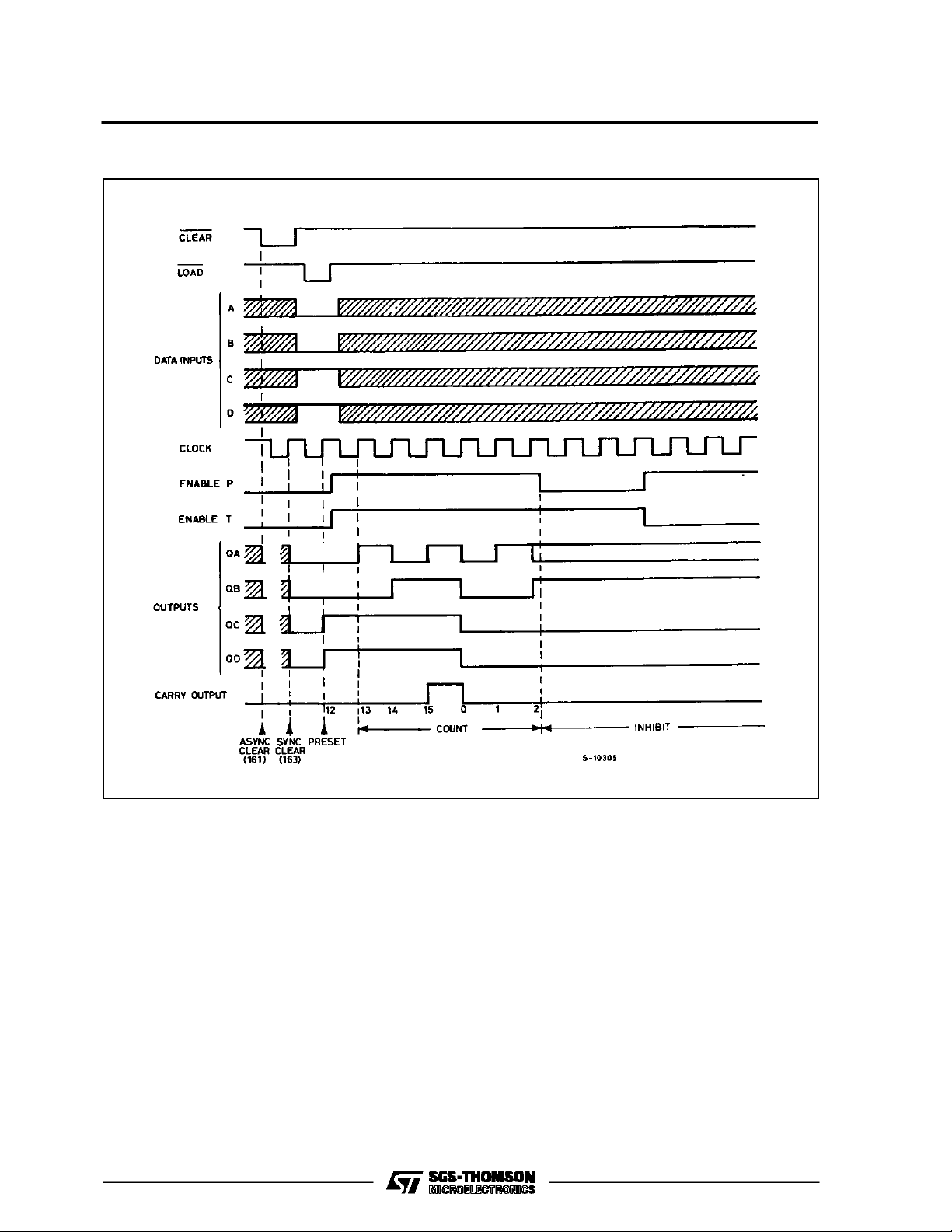

M54/M74HCT160/161/162/163

TIMING CHART (HCT161/163 : binary counter)

4/16

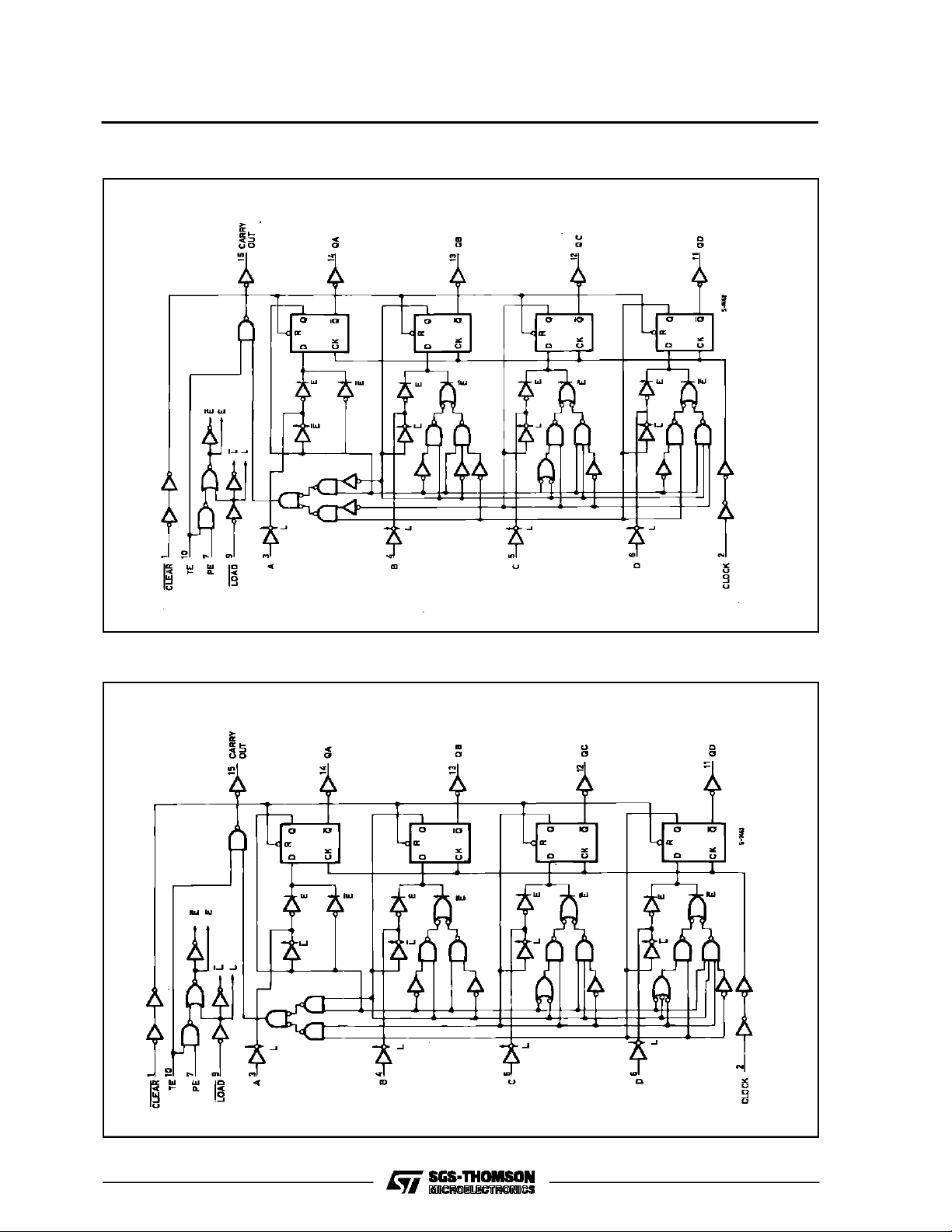

LOGIC DIAGRAM

HCT160

M54/M74HCT160/161/162/163

LOGIC DIAGRAM

HCT161

5/16

Loading...

Loading...