SGS Thomson Microelectronics M74HC73 Datasheet

DUAL J-K FLIP FLOP WITHPRESET AND CLEAR

.HIGH SPEED

f

= 75 MHz(TYP.) AT VCC=5V

MAX

.LOWPOWERDISSIPATION

ICC=2µA(MAX.) AT TA=25°C

.HIGH NOISEIMMUNITY

V

NIH=VNIL

=28%VCC(MIN.)

.OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

.SYMMETRICALOUTPUT IMPEDANCE

IOH =IOL= 4 mA (MIN.)

.BALANCEDPROPAGATION DELAYS

t

PLH=tPHL

.WIDE OPERATINGVOLTAGE RANGE

VCC(OPR)= 2V TO6 V

.PIN AND FUNCTION COMPATIBLE WITH

54/74LS73

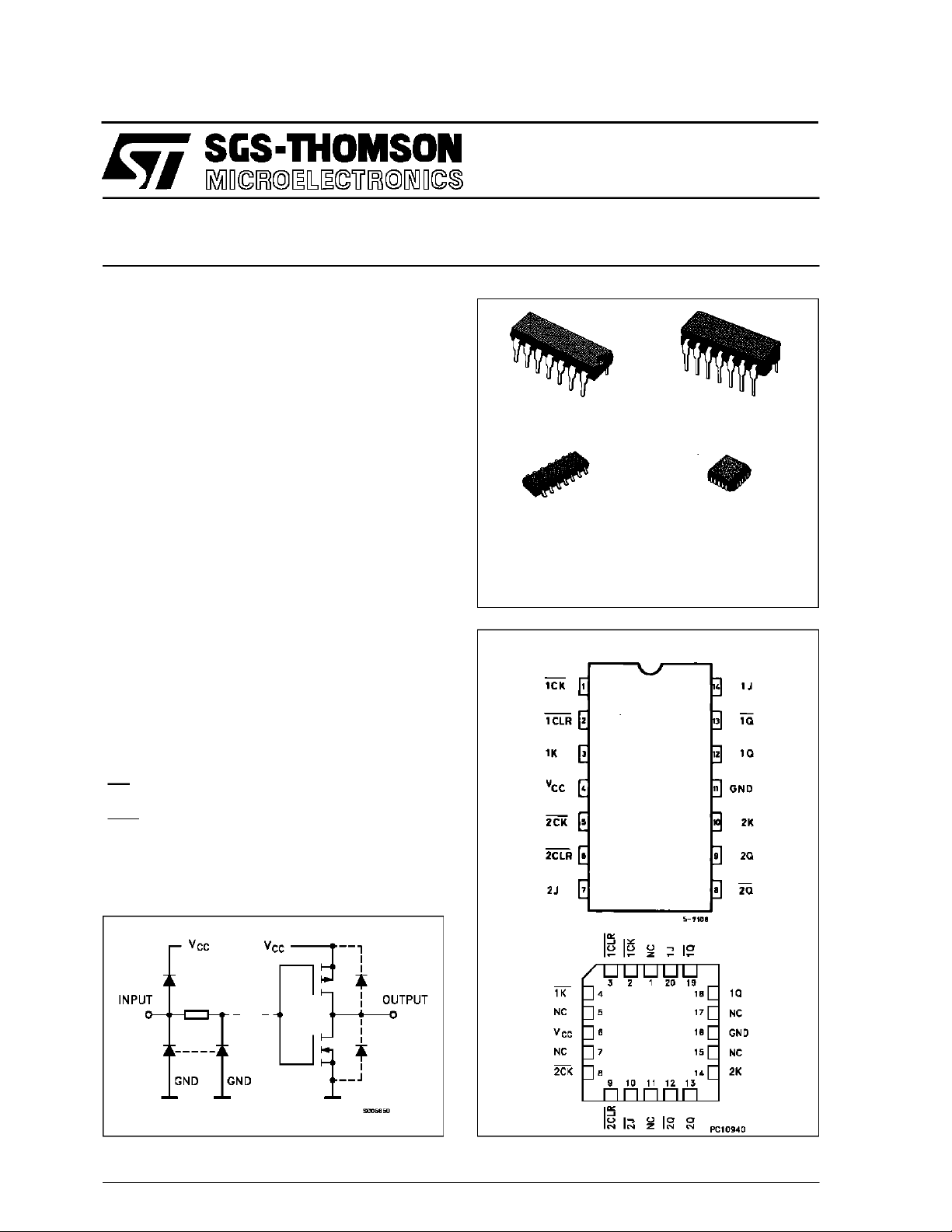

M54HC73

M74HC73

B1R

(PlasticPackage)

M1R

(MicroPackage)

ORDER CODES :

M54HC 73F1R M74H C73M1R

M74HC 73B1R M74HC7 3C1R

(CeramicPackage)

(Chip Carrier)

F1R

C1R

DESCRIPTION

The M54/74HC73is a high speedCMOSDUAL J-K

FLIP FLOPWITHCLEAR fabricated in silicongate

C2MOStechnology. Ithasthesamehighspeedperformance of LSTTL combined with trueCMOS low

power consumption. Depending on the logic level

applied toJand K inputs, this device changes state

on thenegative going transition ofclock input pulse

(CK). The clear function is accomplished independentlyoftheclockconditionwhen the clearinput

(CLR)is taken low. Allinputsare equippedwithprotectioncircuits againststaticdischarge and transient

excess voltage.

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN CONNECTIONS(top view)

NC =

No Internal

Connection

October 1992

1/11

M54/M74HC73

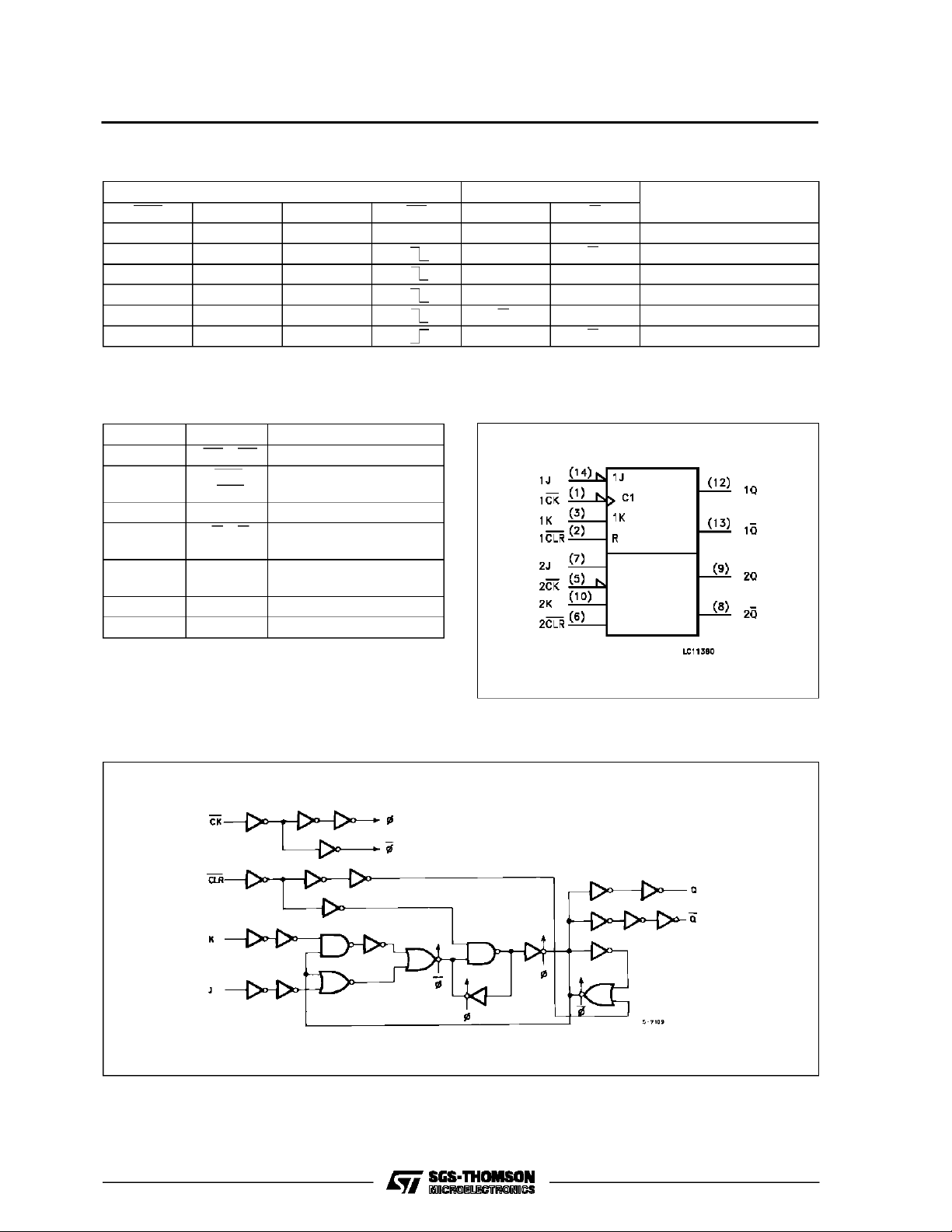

TRUTH TABLE

INPUTS OUTPUTS

CLR J K CK Q Q

FUNCTION

LXXXLH CLEAR

HLL Q

n

Q

n

NO CHANGE

HLH LH -HHL HL -HHH Q

HXX Q

X:Don’tCare

PIN DESCRIPTION

IEC LOGIC SYMBOL

n

n

Q

n

Q

n

TOGGLE

NO CHANGE

PIN No SYMBOL NAME AND FUNCTION

1, 5 1CK, 2CK Clock Input

2, 6 1CLR,

2CLR

Asyncronous Reset

Inputs

12, 9 1Q, 2Q True Flip-Flop Outputs

13, 8 1Q, 2Q Complement Flip-Flop

Outputs

14, 7, 3, 10 1J, 2J, 1K,2KSynchronous Inputs;

Flip-Flop 1 And 2

11 GND Ground (0V)

4V

CC

Positive Supply Voltage

LOGI C DI AG RAM

2/11

M54/M74HC73

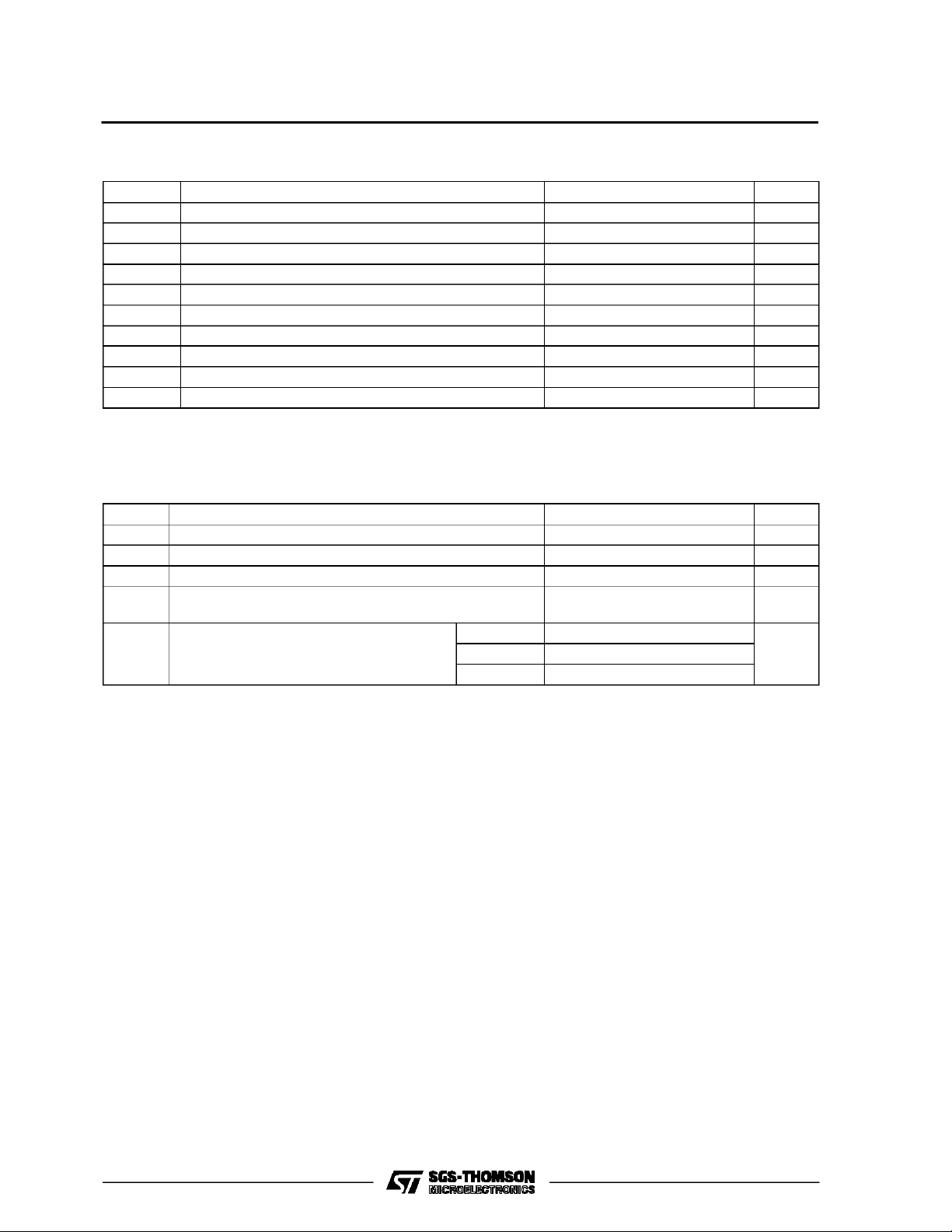

ABSOLU TE MAXI MU M RAT INGS

Symbol Parameter Value Unit

V

CC

V

V

O

I

IK

I

OK

I

O

I

or I

CC

P

D

T

stg

T

L

AbsoluteMaximumRatingsarethose values beyond whichdamage tothedevicemayoccur. Functional operation under these conditionisnotimplied.

(*)500 mW: ≅ 65oC derateto300mWby 10mW/oC: 65oCto85oC

RECO MM ENDED OPERATI N G CONDITIONS

Symbol Parameter Value Unit

V

CC

V

I

V

O

T

op

t

r,tf

Supply Voltage -0.5 to +7 V

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

DC Input Diode Current ± 20 mA

DC Output Diode Current ± 20 mA

DC Output Source Sink Current Per Output Pin ± 25 mA

DC VCCor Ground Current ± 50 mA

GND

Power Dissipation 500 (*) mW

Storage Temperature -65 to +150

Lead Temperature (10sec) 300

Supply Voltage 2 to 6 V

Input Voltage 0 to V

Output Voltage 0 to V

Operating Temperature: M54HC Series

M74HC Series

CC

CC

-55 to +125

-40 to +85

Input Rise and Fall Time VCC= 2 V 0 to 1000 ns

V

= 4.5 V 0 to 500

CC

V

= 6 V 0 to 400

CC

o

C

o

C

V

V

o

C

o

C

3/11

M54/M74HC73

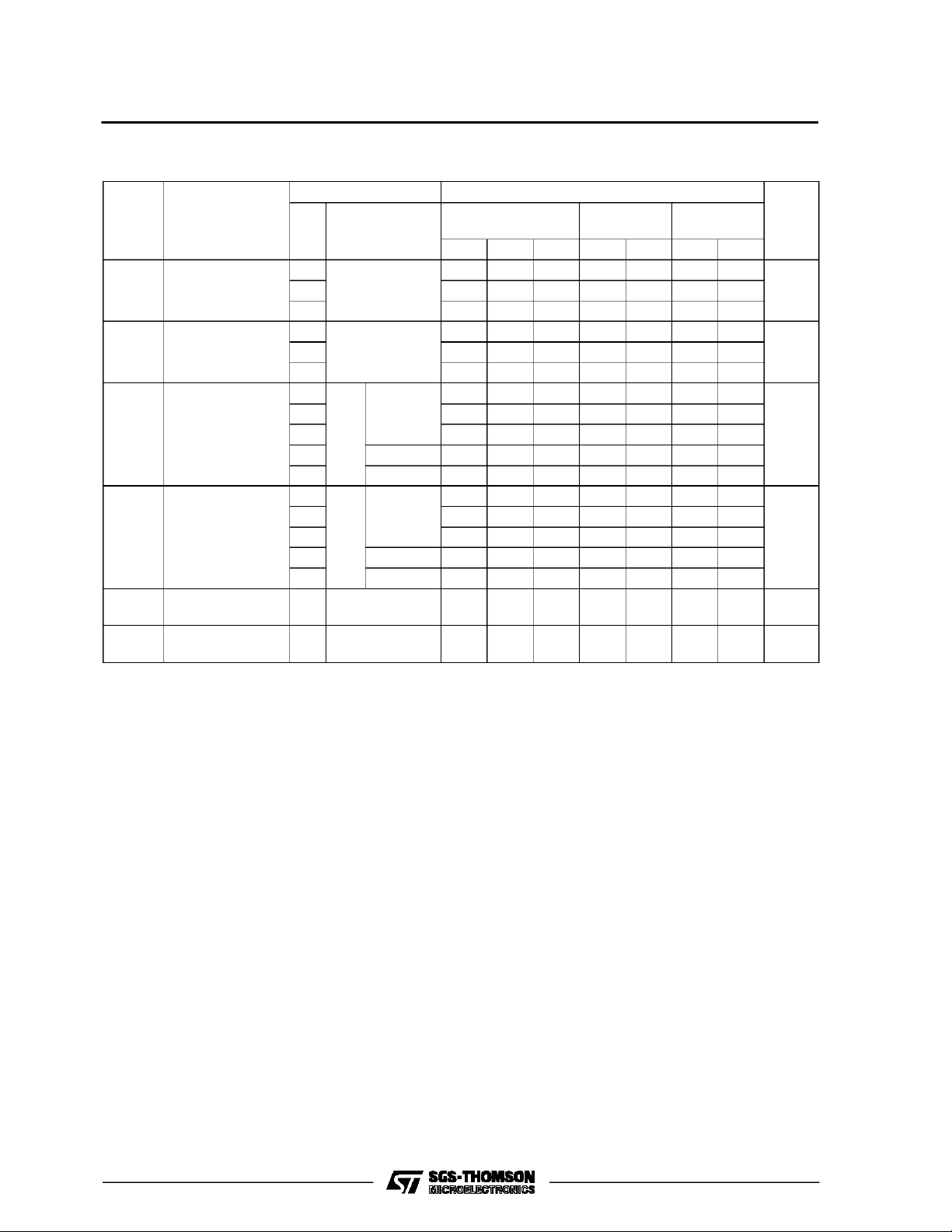

DC SPECIFICATIONS

Symbol Parameter

V

V

V

V

I

High Level Input

IH

Voltage

Low Level Input

IL

Voltage

High Level

OH

Output Voltage

Low Level Output

OL

Voltage

I

Input Leakage

I

Current

Quiescent Supply

CC

Current

Test Conditions Value

V

(V)

CC

=25oC

A

54HC and 74HC

Min. Typ. Max. Min. Max. Min. Max.

-40 to 85oC

74HC

-55 to 125oC

54HC

Unit

T

2.0 1.5 1.5 1.5

4.5 3.15 3.15 3.15

6.0 4.2 4.2 4.2

2.0 0.5 0.5 0.5

4.5 1.35 1.35 1.35

6.0 1.8 1.8 1.8

2.0

4.5 4.4 4.5 4.4 4.4

6.0 5.9 6.0 5.9 5.9

4.5 I

6.0 I

2.0

4.5 0.0 0.1 0.1 0.1

6.0 0.0 0.1 0.1 0.1

4.5 I

6.0 I

6.0

=

V

I

IO=-20 µA

V

IH

or

V

IL

=-4.0 mA 4.18 4.31 4.13 4.10

O

=-5.2 mA 5.68 5.8 5.63 5.60

O

V

=

I

IO=20µA

V

IH

or

V

IL

= 4.0 mA 0.17 0.26 0.33 0.40

O

= 5.2 mA 0.18 0.26 0.33 0.40

O

VI=VCCor GND ±0.1 ±1 ±1 µA

1.9 2.0 1.9 1.9

0.0 0.1 0.1 0.1

6.0 VI=VCCor GND 2 20 40 µA

V

V

V

V

4/11

Loading...

Loading...