SGS Thomson Microelectronics M74HC597 Datasheet

.HIGH SPEED

f

= 60 MHz(TYP.) AT VCC=5V

MAX

.LOWPOWERDISSIPATION

ICC=4µA(MAX.) AT TA=25°C

.HIGH NOISEIMMUNITY

V

NIH=VNIL

=28%VCC(MIN.)

.OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

.SYMMETRICALOUTPUT IMPEDANCE

IOH =IOL= 4 mA (MIN.)

.BALANCEDPROPAGATION DELAYS

t

PLH=tPHL

.WIDE OPERATINGVOLTAGE RANGE

VCC(OPR)= 2V TO6 V

.PIN ANDFUNCTION COMPATIBLE

WITH 54/74LS597

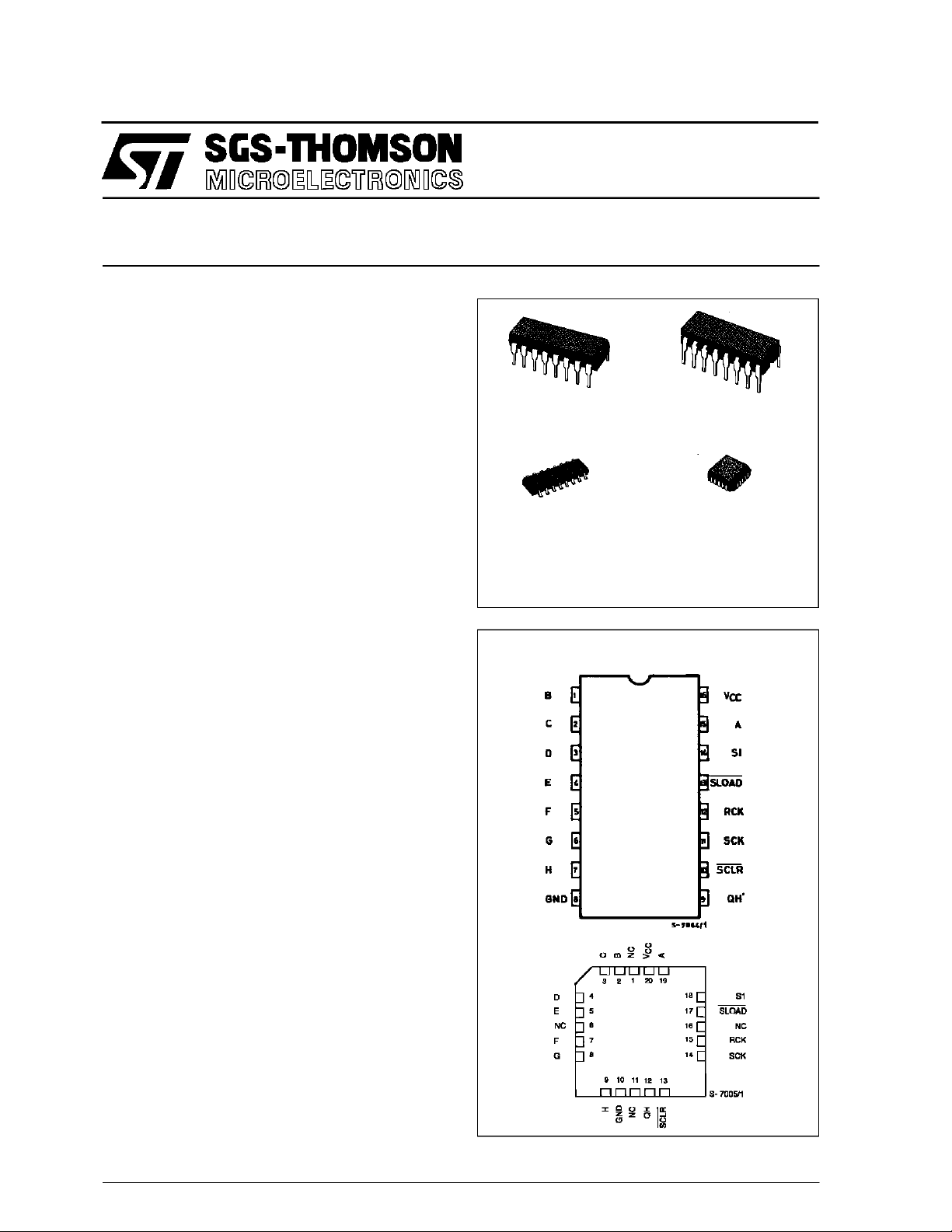

M54HC597

M74HC597

8 BIT LATCH/SHIFT REGISTER

B1R

(PlasticPackage)

M1R

(MicroPackage)

ORDER CODES :

M54HC 597F1R M74H C597M1R

M74HC 597B1R M74HC5 97C1R

F1R

(CeramicPackage)

C1R

(Chip Carrier)

DESCRIPTION

The M54/74HC597 is a high speed CMOS 8-BIT

LATCH/SHIFT REGISTER fabricated insilicongate

C2MOStechnology. Ithasthesamehighspeedperformance of LSTTL combined with true CMOS low

powerconsumption.

Thisdevicescomesina16-pinpackageand consist

of an 8-bit storage latch feedinga parallel-in, serialout 8-bitshiftregister. Both thestorageregisterand

shift register have positive-edge triggered clocks.

The shift register also hasdirectload (fromstorage)

and clearinputs.

All inputs are equipped with protection circuits

against static discharge and transient voltage excess.

PIN CONNECTIONS(top view)

NC =

No Internal

Connection

October 1992

1/13

M54/M74HC597

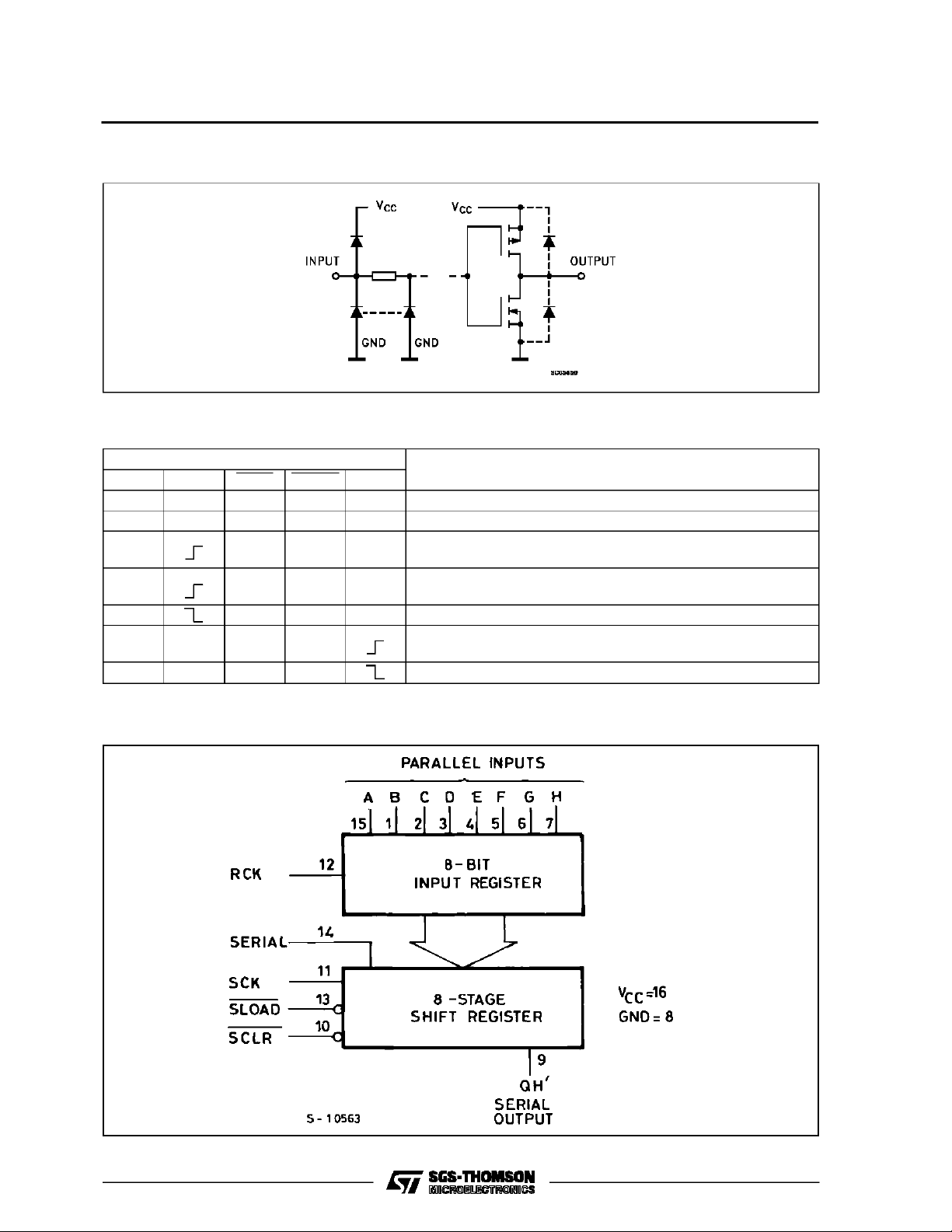

INPUT AND OUTPUT EQUIVALENT CIRCUIT

TRUTH TABLE

INPUTS

SI SCK SCLR SLOAD RCK

X X L H X S.R. IS CLEARED TO ”L”

X X H L X INPTU REGISTER DATA IS STORED INTO S.R.

L HHX

H HHX

X H H X STATE OF S.R IS NOT CHANGED

XXXX

X X X X STORAGE REGISTER STATE IS NOT CHANGED

X:DON’T CARE

FIRST STAGE OF S.R. BECOMES ”L” OTHER STAGES

STORE THE DATA OF PREVIOUS STAGE, RESPECTIVELY

FIRST STAGE OF S.R. BECOMES ”H” OTHER STAGES

STORE THE DATA OF PREVIOUS STAGE, RESPECTIVELY

INPUT DATA ON A ~ H LINE IS STORED INTO INPUT

REGISTER

OUTPUT

LOGIC DIAGRAM

2/13

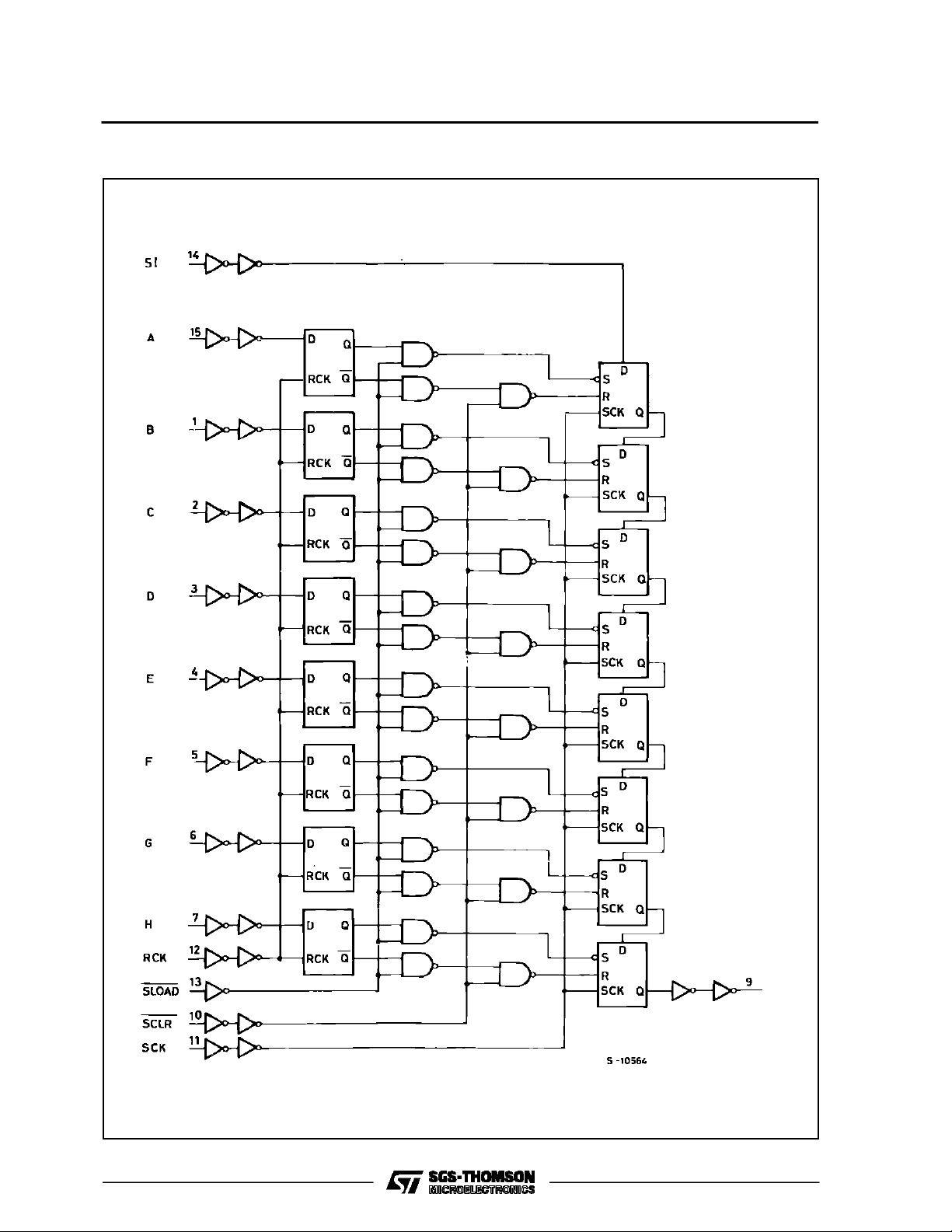

LOGIC DIAGRAM

M54/M74HC597

3/13

M54/M74HC597

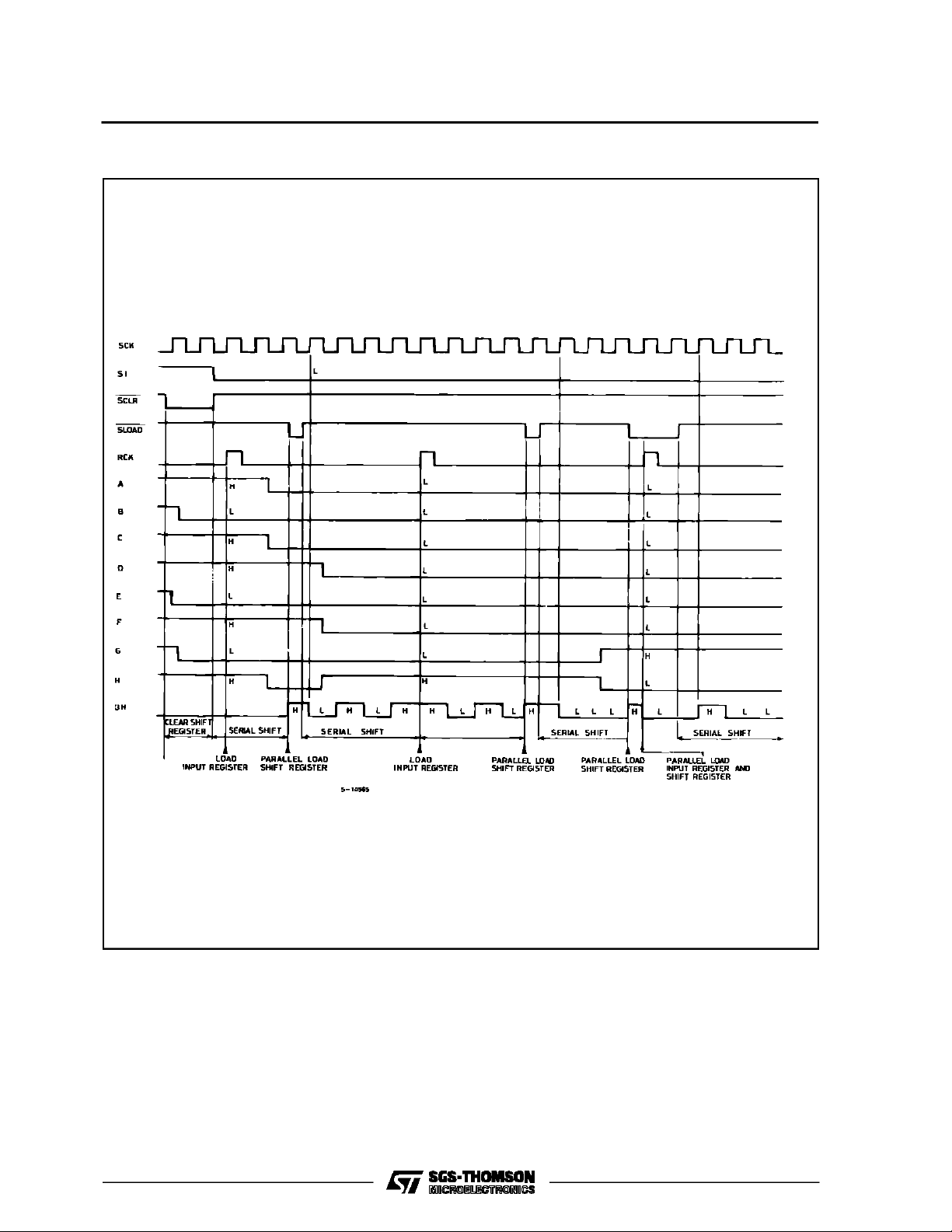

TIMING CHART

4/13

Loading...

Loading...